Page 1

Holtek 32-Bit Microcontroller with Arm® Cortex®-M3 Core

HT32F12345

User Manual

Revision: V1.10 Date: November 28, 2018

Page 2

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Table of Contents

1 Introduction ........................................................................................................... 27

Overview .............................................................................................................................. 27

Features ............................................................................................................................... 28

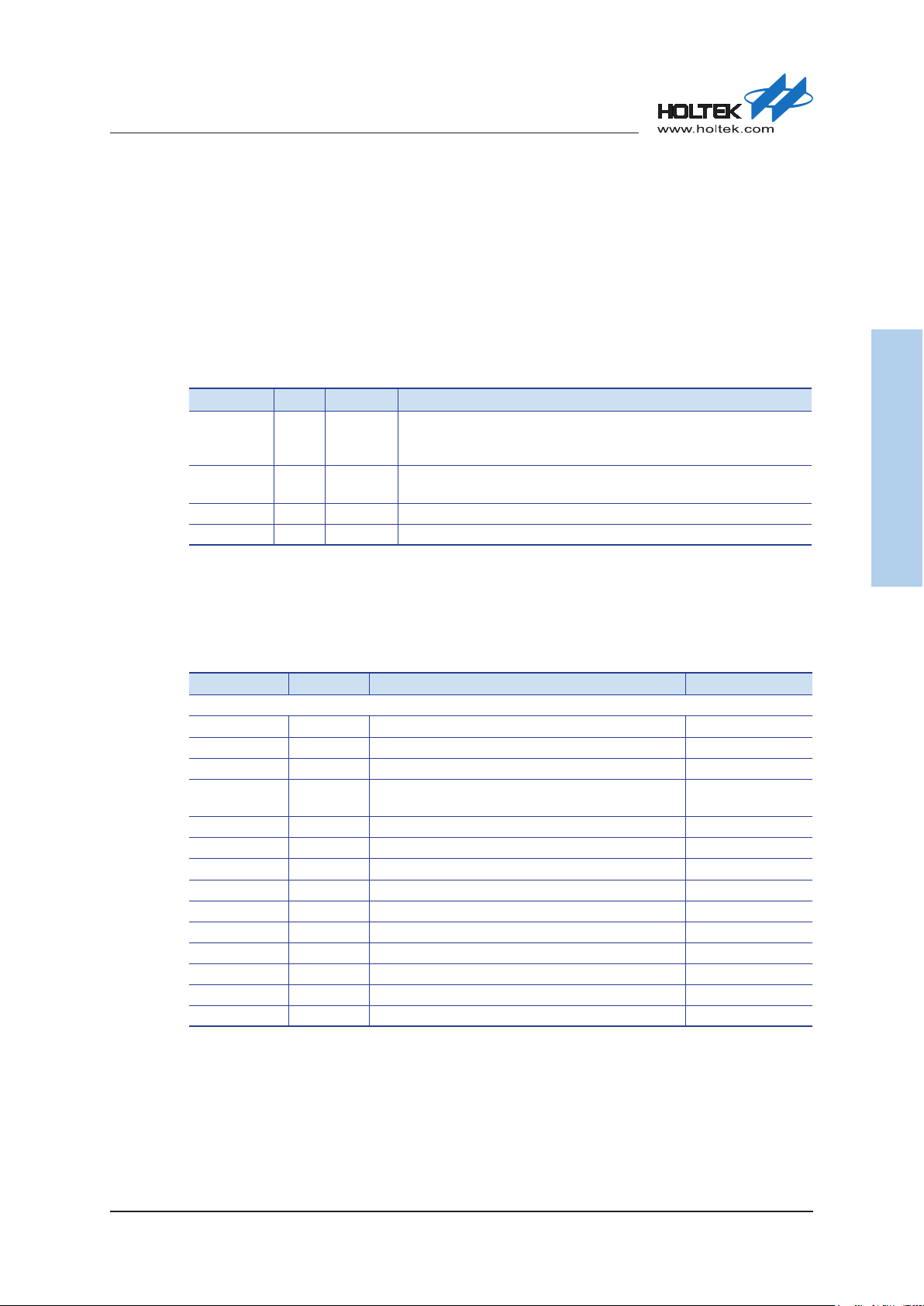

Device Information ............................................................................................................... 32

Block Diagram ..................................................................................................................... 33

2 Document Conventions ....................................................................................... 34

3 System Architecture ............................................................................................. 35

Arm® Cortex®-M3 Processor ................................................................................................ 35

Bus Architecture ................................................................................................................... 36

Memory Organization .......................................................................................................... 37

Memory Map ................................................................................................................................... 38

Embedded Flash Memory ............................................................................................................... 41

Embedded SRAM Memory ............................................................................................................. 41

AHB Peripherals ............................................................................................................................. 41

APB Peripherals ............................................................................................................................. 41

Table of Contents

4 Flash Memory Controller (FMC) .......................................................................... 42

Introduction .......................................................................................................................... 42

Features ............................................................................................................................... 42

Functional Descriptions ....................................................................................................... 43

Flash Memory Map ......................................................................................................................... 43

Flash Memory Architecture ............................................................................................................. 44

Wait State Setting ........................................................................................................................... 44

Booting Conguration ..................................................................................................................... 45

Page Erase ..................................................................................................................................... 46

Mass Erase ..................................................................................................................................... 47

Word Programming ......................................................................................................................... 48

Option Byte Description .................................................................................................................. 49

Page Erase / Program Protection ................................................................................................... 50

Security Protection .......................................................................................................................... 51

Register Map ....................................................................................................................... 52

Register Descriptions ........................................................................................................... 53

Flash Target Address Register – TADR .......................................................................................... 53

Flash Write Data Register – WRDR ............................................................................................... 54

Flash Operation Command Register – OCMR ............................................................................... 55

Flash Operation Control Register – OPCR ..................................................................................... 56

Flash Operation Interrupt Enable Register – OIER ........................................................................ 57

Flash Operation Interrupt and Status Register – OISR .................................................................. 58

Flash Page Erase / program Protection Status Register – PPSR .................................................. 59

Flash Security Protection Status Register – CPSR ........................................................................ 60

Rev. 1.10 2 of 590 November 28, 2018

Page 3

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Flash Vector Mapping Control Register – VMCR ........................................................................... 61

Flash Manufacturer and Device ID Register – MDID ...................................................................... 62

Flash Page Number Status Register – PNSR ................................................................................ 63

Flash Page Size Status Register – PSSR ...................................................................................... 64

Device ID Register – DID ................................................................................................................ 65

Flash Pre-fetch Control Register – CFCR ...................................................................................... 66

SRAM Booting Vector Register n – SBVTn, n = 0 ~ 3 .................................................................... 67

Custom ID Register n – CIDRn, n = 0 ~ 3 ...................................................................................... 68

5 Power Control Unit (PWRCU) .............................................................................. 69

Introduction .......................................................................................................................... 69

Features ............................................................................................................................... 70

Functional Descriptions ....................................................................................................... 70

Backup Domain .............................................................................................................................. 70

VDD Power Domain .......................................................................................................................... 71

1.5 V Power Domain ....................................................................................................................... 73

Operation Modes ............................................................................................................................ 73

Register Map ....................................................................................................................... 75

Register Descriptions ........................................................................................................... 76

Backup Domain Status Register – BAKSR ..................................................................................... 76

Backup Domain Control Register – BAKCR ................................................................................... 77

Backup Domain Test Register – BAKTEST .................................................................................... 79

Low Voltage / Brown Out Detect Control and Status Register – LVDCSR ..................................... 79

Backup Register n – BAKREGn, n = 0 ~ 9 ..................................................................................... 81

Table of Contents

6 Clock Control Unit (CKCU) .................................................................................. 82

Introduction .......................................................................................................................... 82

Features ............................................................................................................................... 82

Functional Descriptions ....................................................................................................... 84

High Speed External Crystal Oscillator (HSE) ................................................................................ 84

High Speed Internal RC Oscillator (HSI) ........................................................................................ 85

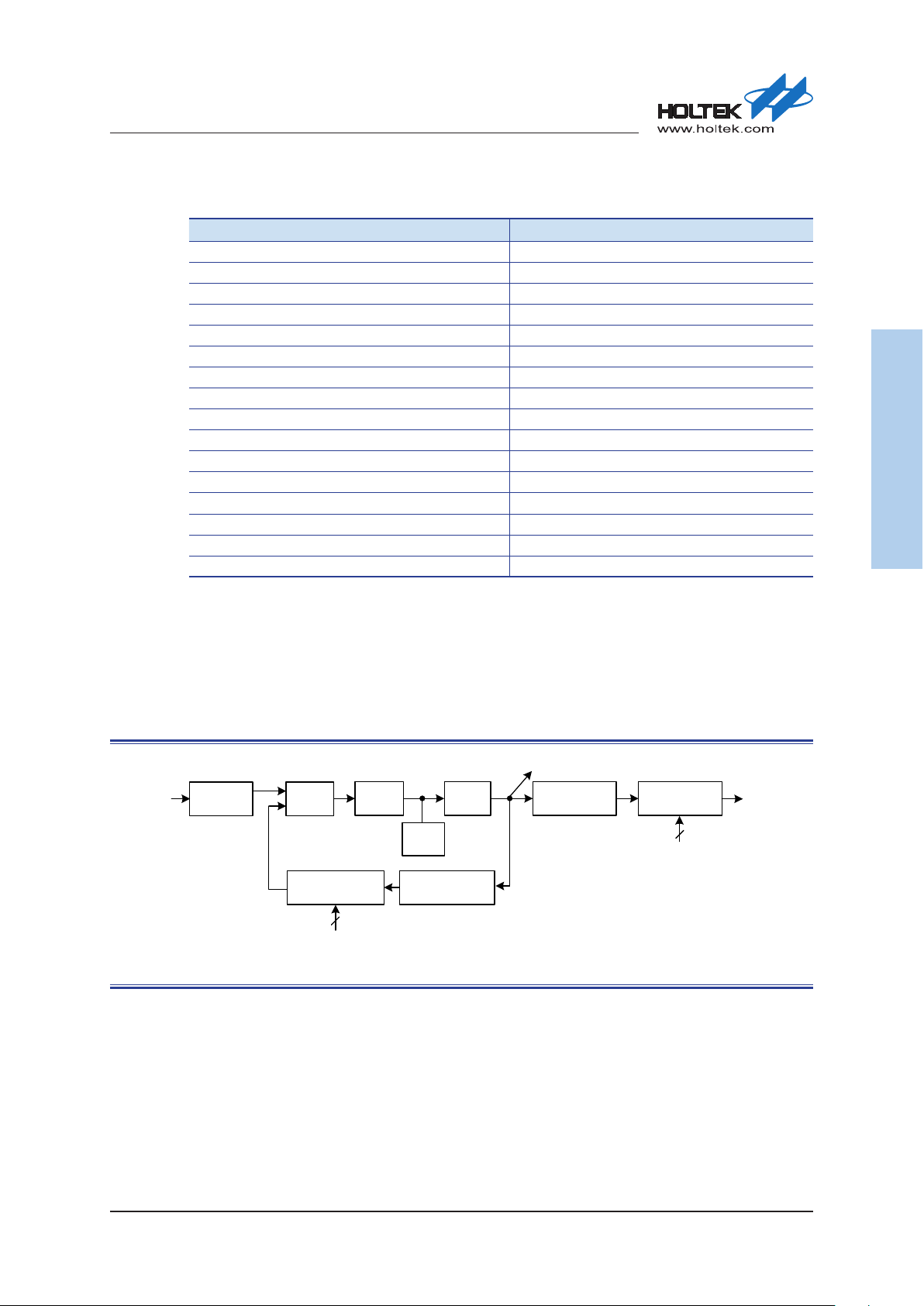

Auto Trimming of High Speed Internal RC Oscillator (HSI) ............................................................ 85

Phase Locked Loop – PLL .............................................................................................................. 87

USB Phase Locked Loop – USB PLL ............................................................................................. 88

Low Speed External Crystal Oscillator – LSE ................................................................................. 90

Low Speed Internal RC Oscillator – LSI ......................................................................................... 90

Clock Ready Flag ........................................................................................................................... 90

System Clock (CK_SYS) Selection ................................................................................................ 91

HSE Clock Monitor ......................................................................................................................... 91

Clock Output Capability .................................................................................................................. 92

Register Map ....................................................................................................................... 92

Register Descriptions ........................................................................................................... 93

Global Clock Conguration Register – GCFGR .............................................................................. 93

Global Clock Control Register – GCCR .......................................................................................... 94

Rev. 1.10 3 of 590 November 28, 2018

Page 4

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Global Clock Status Register – GCSR ........................................................................................... 96

Global Clock Interrupt Register – GCIR .......................................................................................... 97

PLL Conguration Register – PLLCFGR ........................................................................................ 99

PLL Control Register – PLLCR ..................................................................................................... 100

AHB Conguration Register – AHBCFGR .................................................................................... 101

AHB Clock Control Register – AHBCCR ..................................................................................... 102

APB Conguration Register – APBCFGR ..................................................................................... 104

APB Clock Control Register 0 – APBCCR0 .................................................................................. 105

APB Clock Control Register 1 – APBCCR1 .................................................................................. 106

Clock Source Status Register – CKST ......................................................................................... 108

APB Peripheral Clock Selection Register 0 – APBPCSR0 .......................................................... 109

APB Peripheral Clock Selection Register 1 – APBPCSR1 ...........................................................111

HSI Control Register – HSICR ......................................................................................................112

HSI Auto Trimming Counter Register – HSIATCR ........................................................................113

Low Power Control Register – LPCR ..........................................................................................114

MCU Debug Control Register – MCUDBGCR ..............................................................................115

Table of Contents

7 Reset Control Unit (RSTCU) .............................................................................. 117

Introduction ........................................................................................................................ 117

Functional Descriptions ..................................................................................................... 117

Power On Reset ............................................................................................................................117

System Reset ................................................................................................................................118

AHB and APB Unit Reset ...............................................................................................................118

Register Map ..................................................................................................................... 118

Register Descriptions ......................................................................................................... 119

Global Reset Status Register – GRSR ..........................................................................................119

AHB Peripheral Reset Register – AHBPRSTR ............................................................................. 120

APB Peripheral Reset Register 0 – APBPRSTR0 ........................................................................ 121

APB Peripheral Reset Register 1 – APBPRSTR1 ........................................................................ 122

8 General Purpose I/O (GPIO) ............................................................................... 124

Introduction ........................................................................................................................ 124

Features ............................................................................................................................. 125

Functional Descriptions ..................................................................................................... 125

Default GPIO Pin Conguration .................................................................................................... 125

General Purpose I/O – GPIO ........................................................................................................ 125

GPIO Locking Mechanism ............................................................................................................ 127

Register Map ..................................................................................................................... 127

Register Descriptions ......................................................................................................... 128

Port A Data Direction Control Register – PADIRCR ..................................................................... 128

Port A Input Function Enable Control Register – PAINER ............................................................ 129

Port A Pull-Up Selection Register – PAPUR ................................................................................. 129

Port A Pull-Down Selection Register – PAPDR ............................................................................ 130

Port A Open Drain Selection Register – PAODR .......................................................................... 131

Rev. 1.10 4 of 590 November 28, 2018

Page 5

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Port A Output Current Drive Selection Register – PADRVR ......................................................... 131

Port A Lock Register – PALOCKR ................................................................................................ 132

Port A Data Input Register – PADINR ........................................................................................... 133

Port A Output Data Register – PADOUTR .................................................................................... 133

Port A Output Set / Reset Control Register – PASRR .................................................................. 134

Port A Output Reset Register – PARR .......................................................................................... 135

Port B Data Direction Control Register – PBDIRCR ..................................................................... 135

Port B Input Function Enable Control Register – PBINER ........................................................... 136

Port B Pull-Up Selection Register – PBPUR ................................................................................ 136

Port B Pull-Down Selection Register – PBPDR ............................................................................ 137

Port B Open Drain Selection Register – PBODR ......................................................................... 137

Port B Output Current Drive Selection Register – PBDRVR ........................................................ 138

Port B Lock Register – PBLOCKR ................................................................................................ 138

Port B Data Input Register – PBDINR .......................................................................................... 139

Port B Output Data Register – PBDOUTR ................................................................................... 140

Port B Output Set / Reset Control Register – PBSRR .................................................................. 141

Port B Output Reset Register – PBRR ......................................................................................... 142

Port C Data Direction Control Register – PCDIRCR .................................................................... 142

Port C Input Function Enable Control Register – PCINER ........................................................... 143

Port C Pull-Up Selection Register – PCPUR ................................................................................ 143

Port C Pull-Down Selection Register – PCPDR ........................................................................... 144

Port C Open Drain Selection Register – PCODR ......................................................................... 145

Port C Output Current Drive Selection Register – PCDRVR ........................................................ 145

Port C Lock Register – PCLOCKR ............................................................................................... 146

Port C Data Input Register – PCDINR .......................................................................................... 147

Port C Output Data Register – PCDOUTR ................................................................................... 148

Port C Output Set / Reset Control Register – PCSRR ................................................................. 149

Port C Output Reset Register – PCRR ......................................................................................... 150

Port D Data Direction Control Register – PDDIRCR .................................................................... 150

Port D Input Function Enable Control Register – PDINER ........................................................... 151

Port D Pull-Up Selection Register – PDPUR ................................................................................ 152

Port D Pull-Down Selection Register – PDPDR ........................................................................... 153

Port D Open Drain Selection Register – PDODR ......................................................................... 154

Port D Output Current Drive Selection Register – PDDRVR ........................................................ 154

Port D Lock Register – PDLOCKR ............................................................................................... 155

Port D Data Input Register – PDDINR .......................................................................................... 156

Port D Output Data Register – PDDOUTR ................................................................................... 156

Port D Output Set / Reset Control Register – PDSRR ................................................................. 157

Port D Output Reset Register – PDRR ......................................................................................... 158

Table of Contents

9 Alternate Function Input / Output Control Unit (AFIO) .................................... 159

Introduction ........................................................................................................................ 159

Features ............................................................................................................................. 160

Functional Descriptions ..................................................................................................... 160

External Interrupt Pin Selection .................................................................................................... 160

Rev. 1.10 5 of 590 November 28, 2018

Page 6

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Alternate Function ......................................................................................................................... 161

Lock Mechanism .......................................................................................................................... 161

Register Map ..................................................................................................................... 161

Register Descriptions ......................................................................................................... 162

EXTI Source Selection Register 0 – ESSR0 ................................................................................ 162

EXTI Source Selection Register 1 – ESSR1 ................................................................................ 163

GPIO x Conguration Low Register – GPxCFGLR, x = A, B, C, D ............................................... 164

GPIO x Conguration High Register – GPxCFGHR, x = A, B, C, D ............................................. 165

10 Nested Vectored Interrupt Controller (NVIC) .................................................. 166

Introduction ........................................................................................................................ 166

Features ............................................................................................................................. 169

Functional Descriptions ..................................................................................................... 169

SysTick Calibration ....................................................................................................................... 169

Register Map ..................................................................................................................... 169

Table of Contents

11 External Interrupt / Event Controller (EXTI) .................................................... 171

Introduction ........................................................................................................................ 171

Features ............................................................................................................................. 171

Functional Descriptions ..................................................................................................... 172

Wakeup Event Management......................................................................................................... 172

External Interrupt / Event Line Mapping ....................................................................................... 173

Interrupt and De-bounce ............................................................................................................... 173

Register Map ..................................................................................................................... 174

Register Descriptions ......................................................................................................... 175

EXTI Interrupt Conguration Register n – EXTICFGRn, n = 0 ~ 15 ............................................. 175

EXTI Interrupt Control Register – EXTICR ................................................................................... 176

EXTI Interrupt Edge Flag Register – EXTIEDGEFLGR ................................................................ 176

EXTI Interrupt Edge Status Register – EXTIEDGESR ................................................................. 177

EXTI Interrupt Software Set Command Register – EXTISSCR .................................................... 177

EXTI Interrupt Wakeup Control Register – EXTIWAKUPCR ........................................................ 178

EXTI Interrupt Wakeup Polarity Register – EXTIWAKUPPOLR ................................................... 179

EXTI Interrupt Wakeup Flag Register – EXTIWAKUPFLG ........................................................... 179

12 Analog to Digital Converter (ADC) .................................................................. 180

Introduction ........................................................................................................................ 180

Features ............................................................................................................................. 181

Functional Descriptions ..................................................................................................... 182

ADC Clock Setup .......................................................................................................................... 182

Regular and High Priority Channel Selection ............................................................................... 182

Conversion Modes ........................................................................................................................ 182

Start Conversion on External Event .............................................................................................. 187

High Priority Group Management ................................................................................................. 188

Sampling Time Setting .................................................................................................................. 188

Rev. 1.10 6 of 590 November 28, 2018

Page 7

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Data Format and Alignment .......................................................................................................... 190

Analog Watchdog.......................................................................................................................... 190

Interrupts ....................................................................................................................................... 190

PDMA Request ............................................................................................................................ 191

Register Map ..................................................................................................................... 191

Register Descriptions ......................................................................................................... 193

ADC Reset Register – ADCRST ................................................................................................... 193

ADC Regular Conversion Mode Register – ADCCONV ............................................................... 194

ADC High Priority Conversion Mode Register – ADCHCONV ...................................................... 195

ADC Regular Conversion List Register 0 – ADCLST0 ................................................................. 196

ADC Regular Conversion List Register 1 – ADCLST1 ................................................................. 197

ADC Regular Conversion List Register 2 – ADCLST2 ................................................................. 198

ADC High Priority Conversion List Register – ADCHLST ............................................................. 199

ADC Input Offset Register n – ADCOFRn, n = 0 ~ 11 .................................................................. 200

ADC Input Sampling Time Register n – ADCSTRn, n = 0 ~ 11 .................................................... 201

ADC Regular Conversion Data Register y – ADCDRy, y = 0 ~ 11 ................................................ 201

ADC High Priority Conversion Data Register y – ADCHDRy, y = 0 ~ 3 ........................................ 202

ADC Regular Trigger Control Register – ADCTCR ....................................................................... 203

ADC Regular Trigger Source Register – ADCTSR ....................................................................... 204

ADC High Priority Trigger Control Register – ADCHTCR ............................................................. 205

ADC High Priority Trigger Source Register – ADCHTSR ............................................................. 206

ADC Watchdog Control Register – ADCWCR .............................................................................. 207

ADC Watchdog Lower Threshold Register – ADCLTR ................................................................. 208

ADC Watchdog Upper Threshold Register – ADCUTR ................................................................ 208

ADC Interrupt Enable Register – ADCIER .................................................................................... 209

ADC Interrupt Raw Status Register – ADCIRAW ......................................................................... 210

ADC Interrupt Status Register – ADCISR ......................................................................................211

ADC Interrupt Clear Register – ADCICLR .................................................................................... 213

ADC DMA Request Register – ADCDMAR ................................................................................... 214

Table of Contents

13 Comparator (CMP) ............................................................................................ 215

Introduction ........................................................................................................................ 215

Features ............................................................................................................................. 215

Functional Descriptions ..................................................................................................... 216

Comparator Inputs and Output ..................................................................................................... 216

Comparator Reference Voltage .................................................................................................... 216

Interrupts and Wakeup.................................................................................................................. 217

Power Mode and Hysteresis ......................................................................................................... 218

Comparator Write-Protected mechanism ..................................................................................... 218

Register Map ..................................................................................................................... 218

Register Descriptions ......................................................................................................... 219

Comparator Control Register n – CMPCRn, n = 0 ~ 1 ................................................................. 219

Comparator Voltage Reference Value Register n – CVRVALRn, n = 0 ~ 1 .................................. 221

Comparator Interrupt Enable Register n – CMPIERn, n = 0 ~ 1 ................................................... 222

Comparator Transition Flag Register n – CMPTFRn, n = 0 ~ 1 .................................................... 223

Rev. 1.10 7 of 590 November 28, 2018

Page 8

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

14 General-Purpose Timer (GPTM) ...................................................................... 224

Introduction ........................................................................................................................ 224

Features ............................................................................................................................. 225

Functional Descriptions ..................................................................................................... 225

Counter Mode ............................................................................................................................... 225

Clock Controller ............................................................................................................................ 227

Trigger Controller .......................................................................................................................... 228

Slave Controller ............................................................................................................................ 230

Master Controller .......................................................................................................................... 232

Channel Controller ........................................................................................................................ 232

Input Stage ................................................................................................................................... 235

Output Stage ................................................................................................................................. 236

Update Management .................................................................................................................... 240

Quadrature Decoder ..................................................................................................................... 240

Digital Filter ................................................................................................................................... 242

Clearing the CHxOREF when ETIF is high ................................................................................... 243

Single Pulse Mode ........................................................................................................................ 244

Asymmetric PWM Mode ............................................................................................................... 246

Time Interconnection .................................................................................................................... 246

Trigger ADC Start.......................................................................................................................... 249

PDMA Request ............................................................................................................................. 249

Register Map ..................................................................................................................... 250

Register Descriptions ......................................................................................................... 251

Timer Counter Conguration Register – CNTCFR ....................................................................... 251

Timer Mode Conguration Register – MDCFR ............................................................................. 252

Timer Trigger Conguration Register – TRCFR ............................................................................ 255

Timer Counter Register – CTR ..................................................................................................... 257

Channel 0 Input Conguration Register – CH0ICFR .................................................................... 258

Channel 1 Input Conguration Register – CH1ICFR .................................................................... 259

Channel 2 Input Conguration Register – CH2ICFR .................................................................... 260

Channel 3 Input Conguration Register – CH3ICFR .................................................................... 262

Channel 0 Output Conguration Register – CH0OCFR ............................................................... 263

Channel 1 Output Conguration Register – CH1OCFR ............................................................... 265

Channel 2 Output Conguration Register – CH2OCFR ............................................................... 266

Channel 3 Output Conguration Register – CH3OCFR ............................................................... 268

Channel Control Register – CHCTR ............................................................................................. 270

Channel Polarity Conguration Register – CHPOLR .................................................................... 271

Timer PDMA/Interrupt Control Register – DICTR ......................................................................... 272

Timer Event Generator Register – EVGR ..................................................................................... 273

Timer Interrupt Status Register – INTSR ...................................................................................... 275

Timer Counter Register – CNTR................................................................................................... 277

Timer Prescaler Register – PSCR ................................................................................................ 277

Timer Counter Reload Register – CRR ........................................................................................ 278

Channel 0 Capture / Compare Register – CH0CCR .................................................................... 278

Table of Contents

Rev. 1.10 8 of 590 November 28, 2018

Page 9

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Channel 1 Capture / Compare Register – CH1CCR .................................................................... 279

Channel 2 Capture / Compare Register – CH2CCR .................................................................... 280

Channel 3 Capture / Compare Register – CH3CCR .................................................................... 281

Channel 0 Asymmetric Compare Register – CH0ACR ................................................................. 282

Channel 1 Asymmetric Compare Register – CH1ACR ................................................................. 282

Channel 2 Asymmetric Compare Register – CH2ACR ................................................................. 283

Channel 3 Asymmetric Compare Register – CH3ACR ................................................................. 283

15 Basic Function Timer (BFTM) .......................................................................... 284

Introduction ........................................................................................................................ 284

Features ............................................................................................................................. 284

Functional Description ....................................................................................................... 285

Repetitive Mode ............................................................................................................................ 285

One Shot Mode ............................................................................................................................. 286

Trigger ADC Start.......................................................................................................................... 287

Register Map ..................................................................................................................... 287

Register Descriptions ......................................................................................................... 288

BFTM Control Register – BFTMCR .............................................................................................. 288

BFTM Status Register – BFTMSR ................................................................................................ 289

BFTM Counter Register – BFTMCNTR ........................................................................................ 289

BFTM Compare Value Register – BFTMCMPR ........................................................................... 290

Table of Contents

16 Motor Control Timer (MCTM) ........................................................................... 291

Introduction ........................................................................................................................ 291

Features ............................................................................................................................. 292

Functional Descriptions ..................................................................................................... 293

Counter Mode ............................................................................................................................... 293

Clock Controller ............................................................................................................................ 296

Trigger Controller .......................................................................................................................... 297

Slave Controller ............................................................................................................................ 298

Master Controller .......................................................................................................................... 300

Channel Controller ........................................................................................................................ 301

Input Stage ................................................................................................................................... 303

Output Stage ................................................................................................................................. 304

Update Management .................................................................................................................... 313

Quadrature Decoder ..................................................................................................................... 315

Digital Filter ................................................................................................................................... 317

Clearing CHxOREF when ETIF is high ......................................................................................... 317

Single Pulse Mode ........................................................................................................................ 318

Asymmetric PWM Mode ............................................................................................................... 320

Timer Interconnection ................................................................................................................... 320

Trigger ADC Start.......................................................................................................................... 324

Lock Level Table ........................................................................................................................... 324

PDMA Request ............................................................................................................................. 325

Rev. 1.10 9 of 590 November 28, 2018

Page 10

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Register Map ..................................................................................................................... 326

Register Descriptions ......................................................................................................... 327

Timer Counter Conguration Register – CNTCFR ....................................................................... 327

Timer Mode Conguration Register – MDCFR ............................................................................. 328

Timer Trigger Conguration Register – TRCFR ............................................................................ 331

Timer Counter Register – CTR ..................................................................................................... 333

Channel 0 Input Conguration Register – CH0ICFR .................................................................... 334

Channel 1 Input Conguration Register – CH1ICFR .................................................................... 335

Channel 2 Input Conguration Register – CH2ICFR .................................................................... 336

Channel 3 Input Conguration Register – CH3ICFR .................................................................... 338

Channel 0 Output Conguration Register – CH0OCFR ............................................................... 339

Channel 1 Output Conguration Register – CH1OCFR ............................................................... 341

Channel 2 Output Conguration Register – CH2OCFR ............................................................... 342

Channel 3 Output Conguration Register – CH3OCFR ............................................................... 344

Channel Control Register – CHCTR ............................................................................................. 345

Channel Polarity Conguration Register – CHPOLR .................................................................... 347

Channel Break Conguration Register – CHBRKCFR ................................................................. 348

Channel Break Control Register – CHBRKCTR ........................................................................... 349

Timer PDMA / Interrupt Control Register – DICTR ....................................................................... 352

Timer Event Generator Register – EVGR ..................................................................................... 353

Timer Interrupt Status Register – INTSR ...................................................................................... 355

Timer Counter Register – CNTR................................................................................................... 357

Timer Prescaler Register – PSCR ................................................................................................ 358

Timer Counter Reload Register – CRR ........................................................................................ 358

Timer Repetition Register – REPR ............................................................................................... 359

Channel 0 Capture / Compare Register – CH0CCR .................................................................... 359

Channel 1 Capture / Compare Register – CH1CCR .................................................................... 360

Channel 2 Capture / Compare Register – CH2CCR .................................................................... 361

Channel 3 Capture / Compare Register – CH3CCR .................................................................... 362

Channel 0 Asymmetric Compare Register – CH0ACR ................................................................. 363

Channel 1 Asymmetric Compare Register – CH1ACR ................................................................. 363

Channel 2 Asymmetric Compare Register – CH2ACR ................................................................. 364

Channel 3 Asymmetric Compare Register – CH3ACR ................................................................. 364

Table of Contents

17 Real Time Clock (RTC) ..................................................................................... 365

Introduction ........................................................................................................................ 365

Features ............................................................................................................................. 365

Functional Descriptions ..................................................................................................... 366

RTC Related Register Reset ........................................................................................................ 366

Reading RTC Register .................................................................................................................. 366

Low Speed Clock Conguration ................................................................................................... 366

RTC Counter Operation ................................................................................................................ 366

Interrupt and Wakeup Control ....................................................................................................... 367

RTCOUT Output Pin Conguration............................................................................................... 367

Rev. 1.10 10 of 590 November 28, 2018

Page 11

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Register Map ..................................................................................................................... 368

Register Descriptions ......................................................................................................... 369

RTC Counter Register – RTCCNT ................................................................................................ 369

RTC Compare Register – RTCCMP ............................................................................................. 370

RTC Control Register – RTCCR ................................................................................................... 371

RTC Status Register – RTCSR..................................................................................................... 373

RTC Interrupt and Wakeup Enable Register – RTCIWEN ............................................................ 374

18 Watchdog Timer (WDT) .................................................................................... 375

Introduction ........................................................................................................................ 375

Features ............................................................................................................................. 375

Functional Description ....................................................................................................... 376

Register Map ..................................................................................................................... 377

Register Descriptions ......................................................................................................... 378

Watchdog Timer Control Register – WDTCR ............................................................................... 378

Watchdog Timer Mode Register 0 – WDTMR0............................................................................. 379

Watchdog Timer Mode Register 1 – WDTMR1............................................................................. 380

Watchdog Timer Status Register – WDTSR ................................................................................. 381

Watchdog Timer Protection Register – WDTPR ........................................................................... 382

Watchdog Timer Clock Selection Register – WDTCSR ................................................................ 383

Table of Contents

19 Inter-Integrated Circuit (I2C) ............................................................................ 384

Introduction ........................................................................................................................ 384

Features ............................................................................................................................. 385

Functional Descriptions ..................................................................................................... 385

Two Wire Serial Interface .............................................................................................................. 385

START and STOP Conditions ....................................................................................................... 385

Data Validity .................................................................................................................................. 386

Addressing Format ....................................................................................................................... 386

7-bits Address Format ................................................................................................................... 386

10-bits Address Format ................................................................................................................. 387

Data Transfer and Acknowledge ................................................................................................... 388

Clock Synchronization .................................................................................................................. 389

Arbitration ..................................................................................................................................... 389

General Call Address .................................................................................................................... 390

Bus Error ....................................................................................................................................... 390

Address Mask Enable ................................................................................................................... 390

Address Snoop ............................................................................................................................. 390

Operation Mode ............................................................................................................................ 390

Conditions of Holding SCL Line .................................................................................................... 395

I2C Timeout Function .................................................................................................................... 396

PDMA Interface ............................................................................................................................. 396

Rev. 1.10 11 of 590 November 28, 2018

Page 12

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Register Map ..................................................................................................................... 397

Register Descriptions ......................................................................................................... 398

I2C Control Register – I2CCR ....................................................................................................... 398

I2C Interrupt Enable Register – I2CIER ........................................................................................ 400

I2C Address Register – I2CADDR ................................................................................................. 402

I2C Status Register – I2CSR ......................................................................................................... 402

I2C SCL High Period Generation Register – I2CSHPGR .............................................................. 405

I2C SCL Low Period Generation Register – I2CSLPGR ............................................................... 406

I2C Data Register – I2CDR ........................................................................................................... 407

I2C Target Register – I2CTAR ....................................................................................................... 408

I2C Address Mask Register – I2CADDMR .................................................................................... 409

I2C Address Snoop Register – I2CADDSR ................................................................................... 409

I2C Timeout Register – I2CTOUT.................................................................................................. 410

20 Serial Peripheral Interface (SPI) ...................................................................... 411

Introduction ........................................................................................................................ 411

Features ............................................................................................................................. 412

Functional Descriptions ..................................................................................................... 412

Master Mode ................................................................................................................................. 412

Slave Mode ................................................................................................................................... 412

SPI Serial Frame Format .............................................................................................................. 413

Status Flags .................................................................................................................................. 417

Register Map ..................................................................................................................... 420

Register Descriptions ......................................................................................................... 421

SPI Control Register 0 – SPICR0 ................................................................................................. 421

SPI Control Register 1 – SPICR1 ................................................................................................. 422

SPI Interrupt Enable Register – SPIIER ....................................................................................... 424

SPI Clock Prescaler Register – SPICPR ...................................................................................... 425

SPI Data Register – SPIDR .......................................................................................................... 426

SPI Status Register – SPISR ........................................................................................................ 426

SPI FIFO Control Register – SPIFCR ........................................................................................... 428

SPI FIFO Status Register – SPIFSR ............................................................................................ 429

SPI FIFO Time Out Counter Register – SPIFTOCR ..................................................................... 430

Table of Contents

21 Universal Synchronous Asynchronous Receiver Transmitter (USART) ..... 431

Introduction ........................................................................................................................ 431

Features ............................................................................................................................. 432

Functional Descriptions ..................................................................................................... 432

Serial Data Format ........................................................................................................................ 432

Baud Rate Generation .................................................................................................................. 433

Hardware Flow Control ................................................................................................................. 434

IrDA ............................................................................................................................................... 436

RS485 Mode ................................................................................................................................. 438

Synchronous Master Mode ........................................................................................................... 439

Rev. 1.10 12 of 590 November 28, 2018

Page 13

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Interrupts and Status .................................................................................................................... 441

PDMA Interface ............................................................................................................................. 441

Register Map ..................................................................................................................... 441

Register Descriptions ......................................................................................................... 442

USART Data Register – USRDR .................................................................................................. 442

USART Control Register – USRCR .............................................................................................. 443

USART FIFO Control Register – USRFCR................................................................................... 444

USART Interrupt Enable Register – USRIER ............................................................................... 446

USART Status & Interrupt Flag Register – USRSIFR................................................................... 447

USART Timing Parameter Register – USRTPR ........................................................................... 449

USART IrDA Control Register – IrDACR ...................................................................................... 450

USART RS485 Control Register – RS485CR............................................................................... 451

USART Synchronous Control Register – SYNCR ........................................................................ 452

USART Divider Latch Register – USRDLR................................................................................... 453

USART Test Register – USRTSTR ............................................................................................... 454

Table of Contents

22 Universal Asynchronous Receiver Transmitter (UART) ................................ 455

Introduction ........................................................................................................................ 455

Features ............................................................................................................................. 456

Functional Descriptions ..................................................................................................... 456

Serial Data Format ........................................................................................................................ 456

Baud Rate Generation .................................................................................................................. 457

Interrupts and Status .................................................................................................................... 458

PDMA Interface ............................................................................................................................. 459

Register Map ..................................................................................................................... 459

Register Descriptions ......................................................................................................... 460

UART Data Register – URDR ....................................................................................................... 460

UART Control Register – URCR ................................................................................................... 461

UART Interrupt Enable Register – URIER .................................................................................... 462

UART Status & Interrupt Flag Register – URSIFR ....................................................................... 463

UART Divider Latch Register – URDLR ....................................................................................... 465

UART Test Register – URTSTR .................................................................................................... 466

23 USB Device Controller (USB) .......................................................................... 467

Introduction ........................................................................................................................ 467

Features ............................................................................................................................. 467

Functional Descriptions ..................................................................................................... 468

Endpoints ...................................................................................................................................... 468

EP_SRAM ..................................................................................................................................... 468

Serial Interface Engine – SIE ........................................................................................................ 469

Double-Buffering ........................................................................................................................... 469

Suspend Mode and Wake-up ....................................................................................................... 471

Remote Wake-up .......................................................................................................................... 471

Rev. 1.10 13 of 590 November 28, 2018

Page 14

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

Register Map ..................................................................................................................... 471

Register Descriptions ......................................................................................................... 473

USB Control and Status Register – USBCSR .............................................................................. 473

USB Interrupt Enable Register – USBIER .................................................................................... 475

USB Interrupt Status Register – USBISR ..................................................................................... 476

USB Frame Count Register – USBFCR ....................................................................................... 477

USB Device Address Register – USBDEVAR .............................................................................. 478

USB Endpoint 0 Control and Status Register – USBEP0CSR ..................................................... 479

USB Endpoint 0 Interrupt Enable Register – USBEP0IER ........................................................... 480

USB Endpoint 0 Interrupt Status Register – USBEP0ISR ............................................................ 481

USB Endpoint 0 Transfer Count Register – USBEP0TCR ........................................................... 483

USB Endpoint 0 Conguration Register – USBEP0CFGR ........................................................... 484

USB Endpoint 1 ~ 3 Control and Status Register – USBEPnCSR, n = 1 ~ 3 ............................... 485

USB Endpoint 1 ~ 3 Interrupt Enable Register – USBEPnIER, n = 1 ~ 3 ..................................... 486

USB Endpoint 1 ~ 3 Interrupt Status Register – USBEPnISR, n = 1 ~ 3 ...................................... 487

USB Endpoint 1 ~ 3 Transfer Count Register – USBEPnTCR, n = 1 ~ 3 ..................................... 488

USB Endpoint 1 ~ 3 Conguration Register – USBEPnCFGR, n = 1 ~ 3 ..................................... 489

USB Endpoint 4 ~ 7 Control and Status Register – USBEPnCSR, n = 4 ~ 7 ............................... 490

USB Endpoint 4 ~ 7 Interrupt Enable Register – USBEPnIER, n = 4 ~ 7 ..................................... 492

USB Endpoint 4 ~ 7 Interrupt Status Register – USBEPnISR, n = 4 ~ 7 ...................................... 493

USB Endpoint 4 ~ 7 Transfer Count Register – USBEPnTCR, n = 4 ~ 7 ..................................... 494

USB Endpoint 4 ~ 7 Conguration Register – USBEPnCFGR, n = 4 ~ 7 ..................................... 495

Table of Contents

24 Peripheral Direct Memory Access (PDMA) ..................................................... 496

Introduction ........................................................................................................................ 496

Features ............................................................................................................................. 496

Functional Description ....................................................................................................... 497

AHB Master .................................................................................................................................. 497

PDMA Channel ............................................................................................................................. 497

PDMA Request Mapping .............................................................................................................. 497

Channel transfer ........................................................................................................................... 498

Channel Priority ............................................................................................................................ 498

Transfer Request .......................................................................................................................... 499

Address Mode ............................................................................................................................... 499

Auto-Reload .................................................................................................................................. 500

Transfer Interrupt .......................................................................................................................... 500

Register Map ..................................................................................................................... 500

Register Descriptions ......................................................................................................... 503

PDMA Channel n Control Register – PDMACHnCR, n = 0 ~ 11 .................................................. 503

PDMA Channel n Source Address Register – PDMACHnSADR, n = 0 ~ 11 ................................ 505

PDMA Channel n Destination Address Register – PDMACHnDADR, n = 0 ~ 11 ......................... 505

PDMA Channel n Transfer Size Register – PDMACHnTSR, n = 0 ~ 11 ...................................... 506

PDMA Channel n Current Transfer Size Register – PDMACHnCTSR, n = 0 ~ 11 ....................... 507

PDMA Interrupt Status Register 0 – PDMAISR0 .......................................................................... 508

Rev. 1.10 14 of 590 November 28, 2018

Page 15

32-Bit Arm® Cortex®-M3 MCU

HT32F12345

PDMA Interrupt Status Register 1 – PDMAISR1 .......................................................................... 509

PDMA Interrupt Status Clear Register 0 – PDMAISCR0 .............................................................. 510

PDMA Interrupt Status Clear Register 1 – PDMAISCR1 ...............................................................511

PDMA Interrupt Enable Register 0 – PDMAIER0 ......................................................................... 512

PDMA Interrupt Enable Register 1 – PDMAIER1 ......................................................................... 513

25 Extend Bus Interface (EBI) ............................................................................... 514

Introduction ........................................................................................................................ 514

Features ............................................................................................................................. 514

Functional Descriptions ..................................................................................................... 515

Non-multiplexed 8-bit Data 8-bit Address Mode ........................................................................... 516

Non-multiplexed 16-bit Data N-bit Address Mode ......................................................................... 517

Multiplexed 16-bit Data, 16-bit Address Mode .............................................................................. 518

Multiplexed 8-bit Data, 24-bit Address Mode ................................................................................ 519

Page Read Operation ................................................................................................................... 520

Write Buffer and EBI Status .......................................................................................................... 523

Bus Turn-around and Idle Cycles ................................................................................................. 523

AHB Transaction Width Conversion ............................................................................................. 524

EBI Bank Access .......................................................................................................................... 525

EBI Ready ..................................................................................................................................... 526

PDMA Request ............................................................................................................................. 527

Register Map ..................................................................................................................... 527

Register Descriptions ......................................................................................................... 528

EBI Control Register – EBICR ...................................................................................................... 528

EBI Page Control Register – EBIPCR .......................................................................................... 531

EBI Status Register – EBISR ........................................................................................................ 532

EBI Address Timing Register n – EBIATRn, n = 0 ~ 3 .................................................................. 533

EBI Read Timing Register n – EBIRTRn, n = 0 ~ 3 ...................................................................... 534

EBI Write Timing Register n – EBIWTRn, n = 0 ~ 3 ..................................................................... 535