January2001

HI-8787,HI-8788

DESCRIPTION

TheHI-8787andHI-8788aresystemcomponentsfor

interfacing16bitparalleldatatoanARINC429bus.They

combinelogicandlinedriverononechip.TheHI-8787has

anoutputresistanceof37.5ohms,andtheHI-8788has

outputresistanceof10ohmstofacilitateexternallightning

protectioncircuitry. Thetechnologyisanalog/digital

CMOS.

Bothproductsofferhighspeeddatabustransactionsintoa

bufferregister.Afterloading216-bitwords,datais

automaticallytransferredandtransmitted.Thedatarateis

equaltotheclockrate.Paritycanbeenabledinthe32nd

bit.Resetisusedtoinitializethelogicuponstartup.Word

gapsareautomaticallysent.

Thepartrequires+/-10voltsuppliesinadditiontoa5volt

supply.

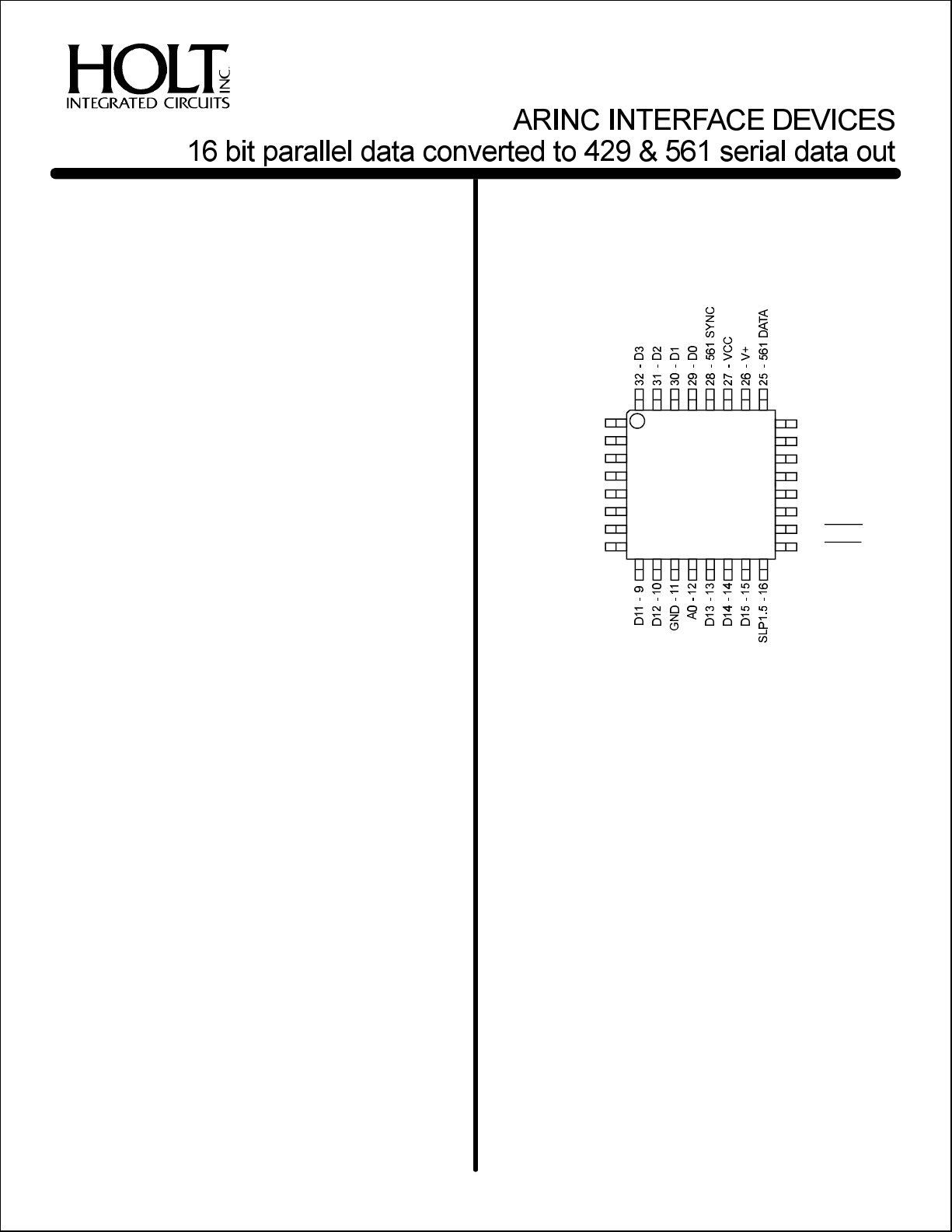

PINCONFIGURATION

D4-1

N/C-2

D5-3

D6-4

D7-5

D8-6

D9-7

D10-8

HI-8787PQI

HI-8787PQT

HI-8788PQI

&

HI-8788PQT

24-TXBOUT

23-TXAOUT

22-V21-PARITYENB

20-XMTRDY

19-XMITCLK

18-

RESET

17-

WRITE

FEATURES

l

l

l

l

l

Automaticallyconverts16bitparalleldata

toARINC429or561data

Highspeeddatabusinterface

On-chiplinedriver

AvailableinsmallTQFPpackage

Militaryprocessingoptions

32-PinPlasticTQFPpackage

HOLTINTEGRATEDCIRCUITS

(DS8787Rev.B)01/01

1

HI-8787,HI-8788

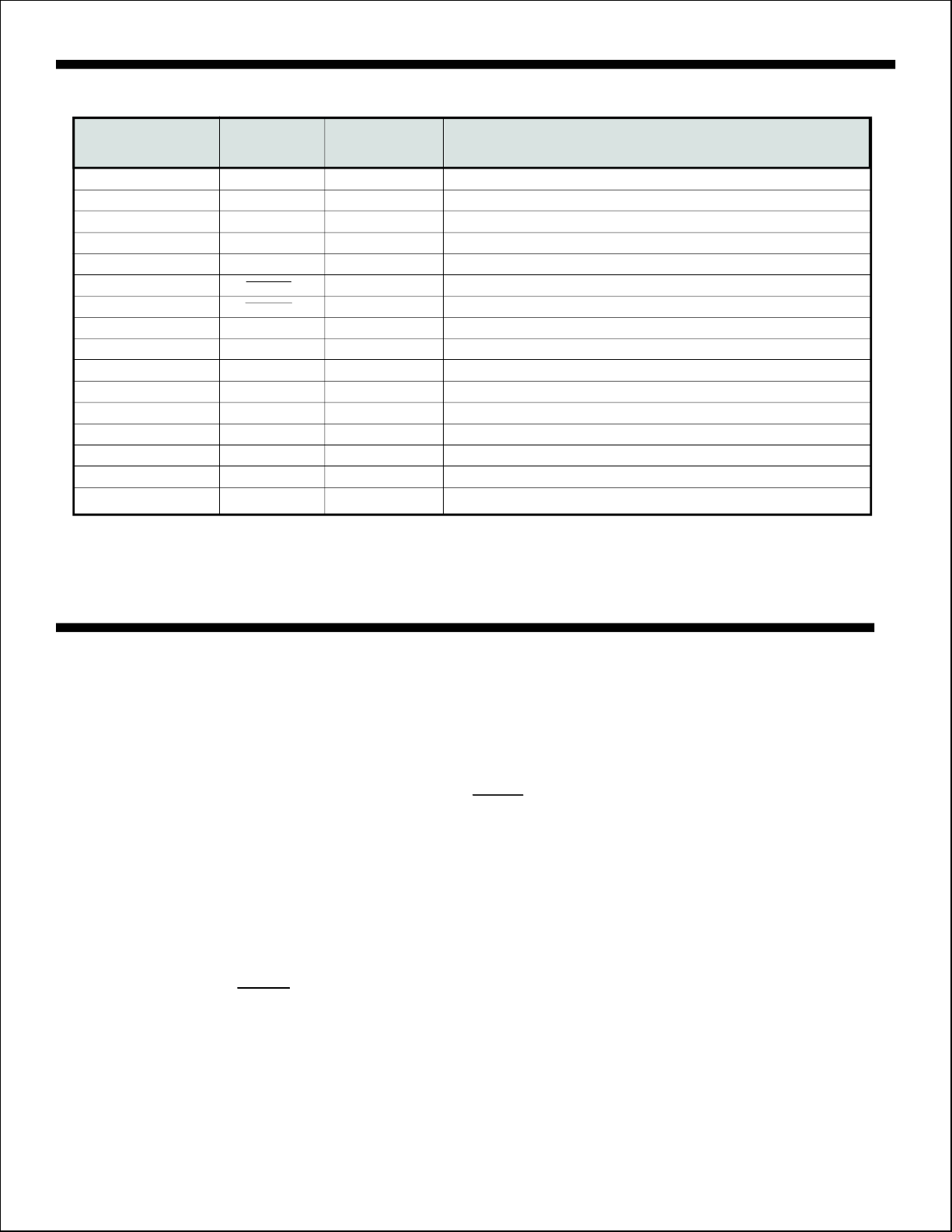

PINDESCRIPTIONS

PINSYMBOLFUNCTIONDESCRIPTION

28561SYNCdigitaloutputARINC561Syncsignal

1,3-10,13-15,29-32DndigitalinputsParallel16bitbusinput

11GNDpowersupplyGround

12A0digitalinputLoadaddress,A0=0for1stdataload,A0=1for2nddataload

16SLP1.5digitalinputSelectstheslopeofthelinedriver.High=1.5us

17digitalinputWritestrobe.Loadsdataonrisingedge.

18digitalinputRegistersandsequencinglogicinitializedwhenlow

19XMITCLKdigitalinputClockinputforthetransmitter

20XMTRDYdigitaloutputGoeshighifthebufferregisterisempty

21PARITYENBdigitalinputWhenhighthe32ndbitoutputi soddparity

22V-powersupply-10voltrail

23TXAOUTanalogoutputLinedriveroutput-Aside

24TXBOUTanalogoutputLinedriveroutput-Bside

25561DATAdigitaloutputSerialoutputforARINC561data

26V+powersupply+10voltrail

27VCCpowersupply+5voltrail,“one”leveloutoflinedriver,invertedfor“zero”

WRITE

RESET

FUNCTIONALDESCRIPTION

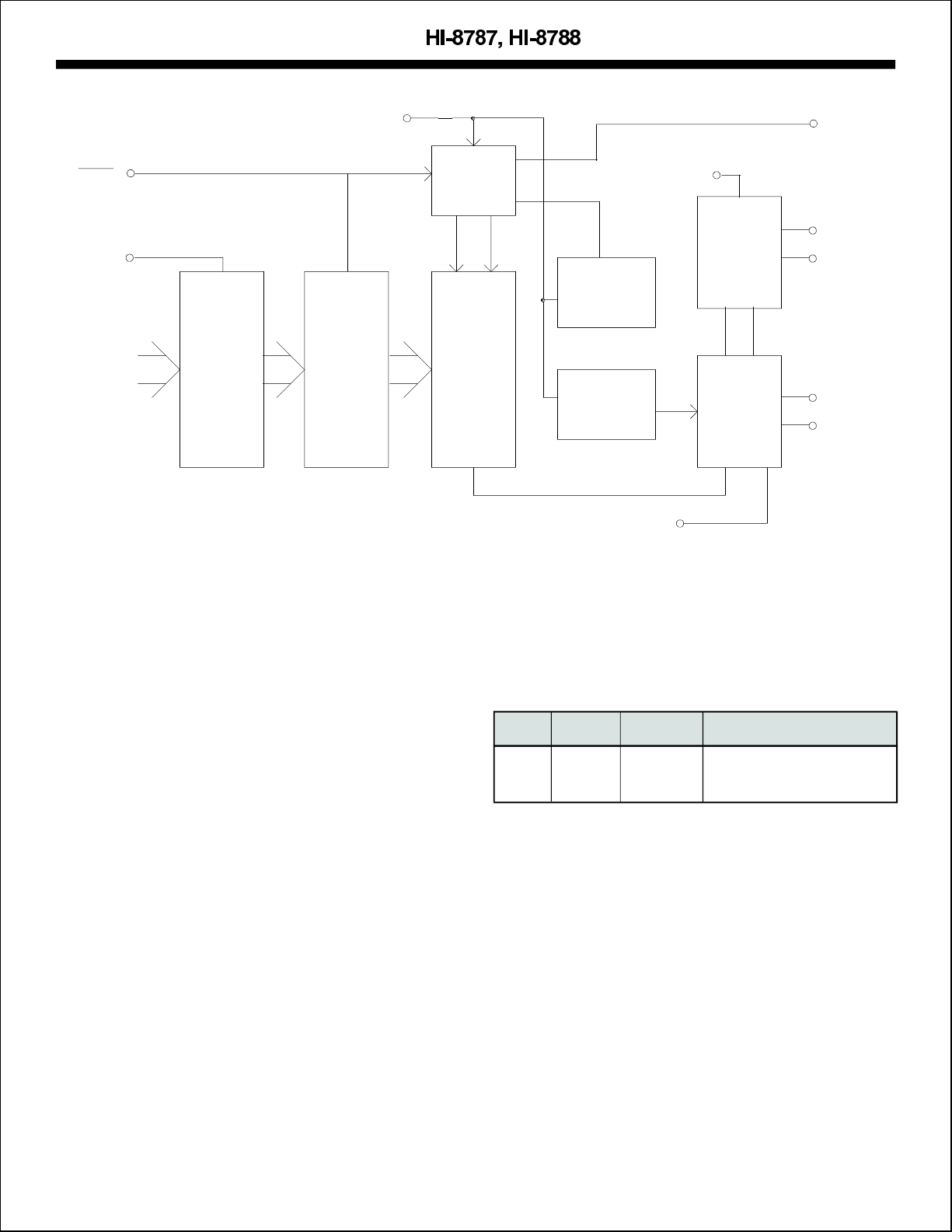

TheHI-8787isaparalleltoserialconverter,whichwhen

loadedwithtwo16bitparallelwords,outputsthedataasa

32bitserialword.Timingcircuitryinsertsa4bitgapatthe

endofeach32bitword.Aninputbufferregisterallowsload

operationstotakeplacewhilethepreviouslyloadedword

isbeingtransmitted.

IfthePARITYENBpinishigh,the32ndbitwillbeaparity

bit,insertedsoastomakethe32bitwordhaveoddparity.If

thePARITYENBpinislow,the32ndbitwillbetheD15bit

ofthe2ndwordloaded.

OutputsareprovidedforbothARINC429(TXAOUTand

TXBOUTpins),andARINC561(561DA TAand561SYNC

pins)typedata.

AlowsignalappliedtothepinresetstheHI-8787’s

internallogicsothatspurioustransmissiondoesnottake

placeduringpower-up.Theregistersareclearedsothata

continuousgapwillbetransmitteduntilthefirstwordis

loadedintothetransmitter.

TheXMITCLKfrequencyisthesameasthedatarate.

RESET

InputdatacanbeloadedwhentheXMTRDYsignalis

high,whichindicatestheinputbufferregisterisempty.The

first16bitwordisloadedwiththeA0inputhigh.ThesecondwordisloadedwithA0inthelowstate.Eachdataword

isloadedintotheinputbufferregisterbyalowpulseonthe

WRITE

input.(Seefigure1).Afterthesecondwordhas

beenloaded,theXMTRDYoutputgoeslow.Thecontents

oftheinputbufferregisteraretransferredtotheoutputregisterduringthefourthbitperiodofthegap.Ifthefourthgap

bitperiodofthepreviouswordhasalreadybeentransmitted,thecontentsoftheinp utbufferregisterwillbetransferredtotheoutputshiftregisterduringthefirstbitperiodaftertheseconddataload,andtheXMTRDYoutputgoes

high.

Aftertheoutputshiftregisterisloaded,thedataisshifted

outtotheoutputlogicintheordershowninfigure2.

The561SYNCoutputpulseslowwhentheXMITCLKis

lowduringthe8thbitoftheARINCtransmission.

HOLTINTEGRATEDCIRCUITS

HOLTINTEGRATEDCIRCUITS

2

2

XMITCLK

XMTRDY

WRITE

DATA

BUS

status&

control

logic

A0

wordgap

counter

16

16to32bit

mux

32 32

32bit

buffer

register

32bit

shift

register

bit

counter

PARITYENB

SLP1.5

line

driver

output

logic

TXAOUT

TXBOUT

561SYNC

561DATA

Figure1.BlockDiagram

FUNCTIONALDESCRIPTION(Cont.)

TheHI-8787andHI-8788haveanon-chiplinedriverdesignedtodirectlydrivetheARINC429bus.ThetwoARINC

outputs(TXAOUTandTXBOUT)provideadifferentialvoltagetoproducea+10voltOne,a-10voltZero,anda0volt

Null.TheslopeoftheARINCoutputsiscontrolledbythe

SLP1.5pin.IfSLP1.5ishigh,theoutputriseandfalltimeis

nominally1.5s..IfSLP1.5issetlow,theriseandfalltimes

are10s.

µ

TheHI-8787has37.5ohmsinserieswitheachlinedriver

output.TheHI-8788has10.0ohmsinseries.TheHI-8788

isforapplicationswhereexternalseriesresistanceis

needed,typical lyforlightningprotectiondevices.

µ

A0LoadDataBusARINCBits

1Word1D0-D15ARINC1-ARINC16

0Word2D0-D15ARINC17-ARINC32

Figure2.Orderoftransmitteddata

HOLTINTEGRATEDCIRCUITS

3

Loading...

Loading...