Datasheet HI-8583CJI, HI-8582PQT-10, HI-8582PQT, HI-8582PQI-10, HI-8582PQI Datasheet (HOLT)

...

HI-8582,HI-8583

June2001

GENERALDESCRIPTION

TheHI-8582fromHoltIntegratedCircuitsisasilicongate

CMOSdeviceforinterfacinga16-bitparalleldatabus

directlytotheARINC429serialbus.TheHI-8582design

offersmanyenhancementstotheindustrystandardHI8282architecture.Thedeviceprovidestworeceiverseach

withlabelrecognition,32by32FIFO,andanalogline

receiver.Upto16labelsmaybeprogrammedforeach

receiver.Theindependenttransmitterhasa32by32FIFO

andabuilt-inlinedriver.ThestatusofallthreeFIFOscan

bemonitoredusingtheexternalstatuspins,orbypolling

theHI-8582’sstatusregister.Othernewfeaturesincludea

programmableoptionofdataorparityinthe32ndbit,and

theabilitytounscramblethe32bitword.Also,versions

areavailablewithdifferentvaluesofinputresistanceand

outputresistancetoallowuserstomoreeasilyaddexternal

lightningprotectioncircuitry.Thedevicecanbeusedat

nonstandarddatarateswhenanoptionpin,,is

invoked.

NFD

ARINC429SystemonaChip

FEATURES

!

ARINCspecification429compatible

!

Dualreceiverandtransmitterinterface

!

Analoglinedriverandreceiversconnect

directlytoARINCbus

!

Programmablelabelrecognition

!

On-chip16labelmemoryforeachreceiver

!

32x32FIFOseachreceiverandtransmitter

!

Independentdatarateselectionfor

transmitterandeachreceiver

!

Statusregister

!

Datascramblecontrol

!

32ndtransmitbitcanbedataorparity

!

Selftestmode

!

Lowpower

The16-bitparalleldatabusexchangesthe32-bitARINC

datawordintwostepswheneitherloadingthetransmitter

orinterrogatingthereceivers.Thedatabus,andallcontrol

signalsareCMOSandTTLcompatible.

TheHI-8582appliestheARINCprotocoltothereceivers

andtransmitter.Timingisbasedona1Megahertzclock.

Althoughthelinedriversharesacommonsubstratewith

thereceivers,thedesignofthephysicalisolationdoesnot

allowparasiticcrosstalk,andtherebyachievesthesame

isolationascommonhybridlayouts.

APPLICATIONS

!

Avionicsdatacommunication

!

Serialtoparallelconversion

!

Paralleltoserialconversion

!

Industrial&fullmilitarytemperatureranges

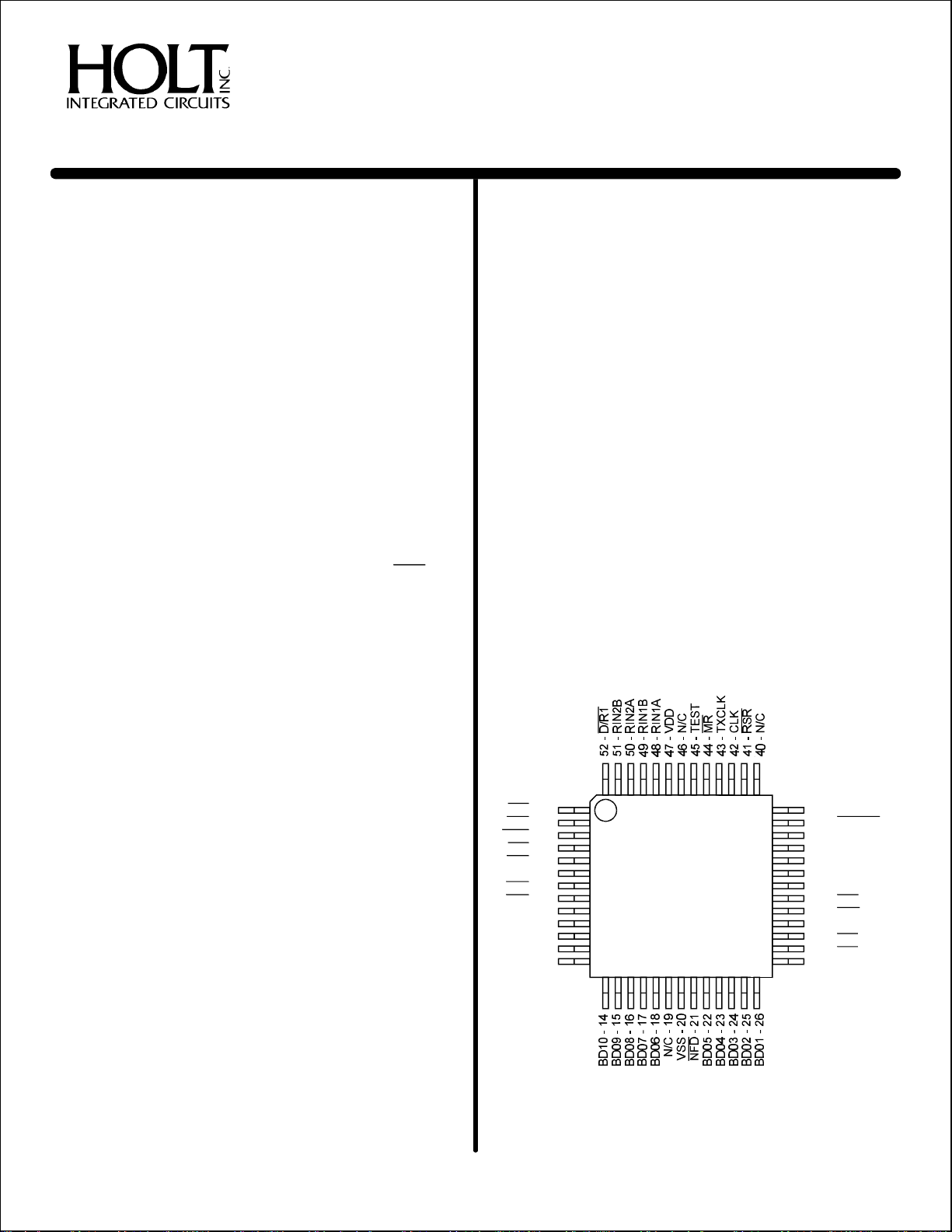

PINCONFIGURATION (TopView)

FF1

-1

HF1

-2

D/R2

-3

FF2

-4

HF2

-5

SEL-6

EN1

-7

EN2

-8

BD15-9

BD14-10

BD13-11

BD12-12

BD11-13

HI-8582PQI

&

HI-8582PQT

39-N/C

38-

CWSTR

37-ENTX

36-V+

35-TXBOUT

34-TXAOUT

33-V32-

FFT

31-

HFT

30-TX/R

29-

PL2

28-

PL1

27-BD00

52-PinPlasticQuadFlatPack(PQFP)

(Seepage14foradditionalpinconfiguration)

HOLTINTEGRATEDCIRCUITS

1(DS8582Rev.H)06/01

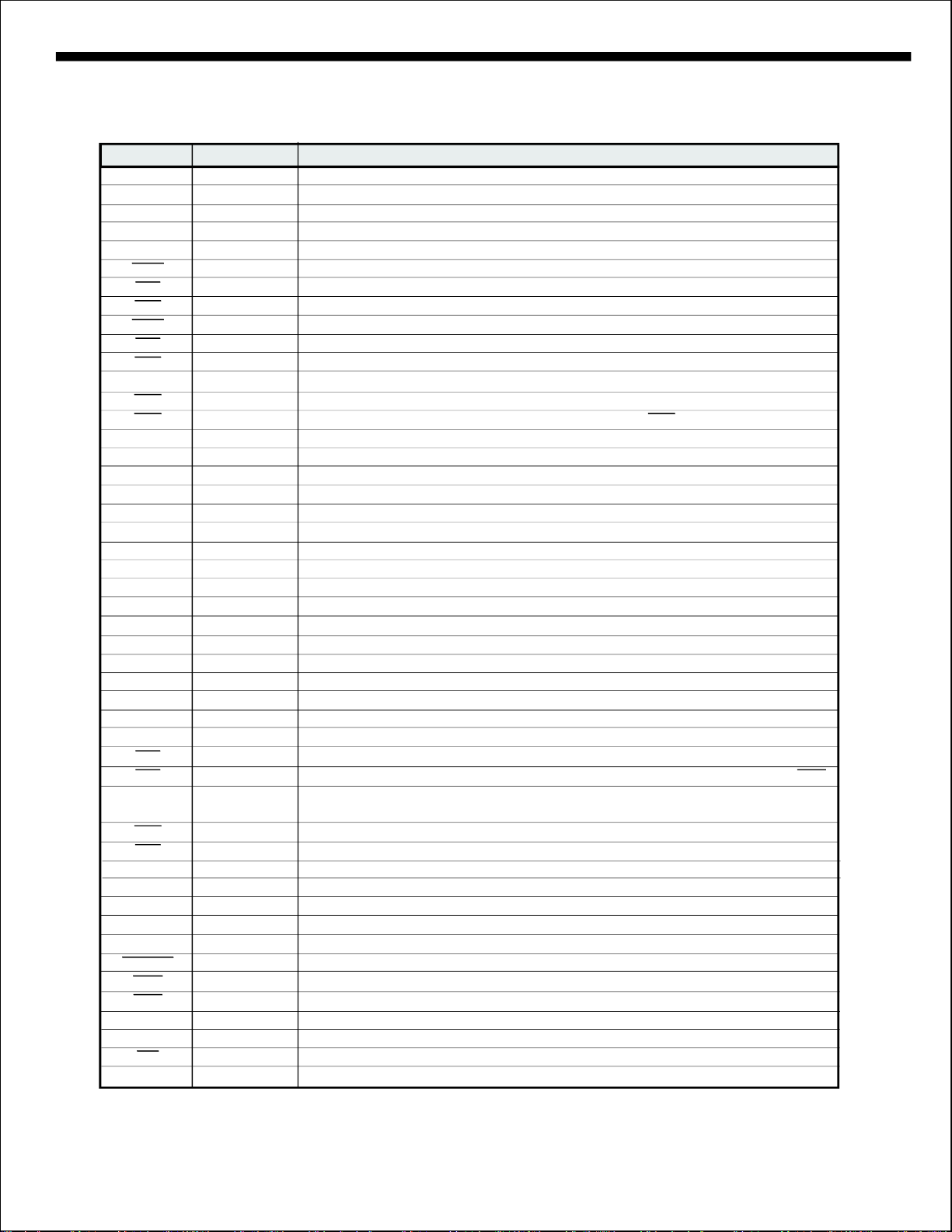

PINDESCRIPTIONS

SIGNALFUNCTIONDESCRIPTION

VDDPOWER+5V±%

RIN1AINPUTARINCreceiver1positiveinput

RIN1BINPUTARINCreceiver1negativeinput

RIN2AINPUTARINCreceiver2positiveinput

RIN2BINPUTARINCreceiver2negativeinput

D/R1

FF1

HF1

D/R2

FF2

HF2

SELINPUTReceiverdatabyteselection(0=BYTE1)(1=BYTE2)

EN1

EN2EN1

BD15I/ODataBus

BD14I/ODataBus

BD13I/ODataBus

BD12I/ODataBus

BD11I/ODataBus

BD10I/ODataBus

BD09I/ODataBus

BD08I/ODataBus

BD07I/ODataBus

BD06I/ODataBus

GNDPOWER0V

BD05I/ODataBus

BD04I/ODataBus

BD03I/ODataBus

BD02I/ODataBus

BD01I/ODataBus

BD00I/ODataBus

PL1

PL2PL1.

TX/ROUTPUTTransmitterreadyflag.GoeslowwhenARINCwordloadedintoFIFO.Goeshigh

HFT

FFT

V-POWER-9.5Vto-12.6V

TXAOUTOUTPUTLinedriveroutput-Aside

TXBOUTOUTPUTLine driveroutput-Bside

V+POWER+9.5Vto+12.6V

ENTXINPUTEnableTransmission

CWSTR

RSR

NFD

CLKINPUTMasterClockinput

TXCLKOUTPUTTransmitterClockequaltoMasterClock(CLK),dividedbyeither10or80.

MR

TESTINPUTDisableTransmitteroutputifhigh(pull-down)

OUTPUTReceiver1datareadyflag

OUTPUTFIFOfullReceiver1

OUTPUTFIFOHalffull,Receiver1

OUTPUTReceiver2datareadyflag

OUTPUTFIFOfullReceiver2

OUTPUTFIFOHalffull,Receiver2

INPUTDataBuscontrol,enablesreceiver1datatooutputs

INPUTDataBuscontrol,enablesreceiver2datatooutputsifishigh

INPUTLatchenableforbyte1enteredfromdatabustotransmitterFIFO.

INPUTLatchenableforbyte2enteredfromdatabustotransmitterFIFO.Mustfollow

OUTPUTTransmitterFIFOHalfFull

OUTPUTTransmitterFIFOFull

INPUTClockforcontrolwordregister

INPUTReadStatusRegisterifSEL=0,readControlRegisterifSEL=1

INPUTNofrequencydiscriminationiflow(pull-up)

INPUTMasterReset,activelow

HI-8582,HI-8583

5

aftertransmissionandFIFOempty.

HOLTINTEGRATEDCIRCUITS

2

FUNCTIONALDESCRIPTION

CONTROLWORDREGISTER

HI-8582,HI-8583

STATUSREGISTER

TheHI-8582containsa16-bitcontrolregisterwhichisusedto

configurethedevice.ThecontrolregisterbitsCR0-CR15are

loadedfromBD00-BD15whenispulsedlow.Thecontrol

registercontentsareoutputonthedatabuswhenSEL=1and

CWSTR

RSR

ispulsedlow.Eachbitofthecontrolregisterhasthefollowing

function:

CR

BitFUNCTIONSTATEDESCRIPTION

CR0Receiver10Datarate=CLK/10

CR1LabelMemory0Normaloperation

CR2EnableLabel0Disablelabelrecognition

CR3EnableLabel0DisableLabelRecognition

CR4Enable0Transmitter32ndbitisdata

CR5SelfTest0Aninternalconnectionismade

CR6Receiver10Receiver1decoderdisabled

CR7--Ifreceiver1decoderisenabled,

CR8--Ifreceiver1decoderisenabled,

CR9Receiver20Receiver2decoderdisabled

CR10--Ifreceiver2decoderisenabled,

CR11--Ifreceiver2decoderisenabled,

CR12Invert0Transmitter32ndbitisOddparity

CR13Transmitter0Datarate=CLK/10,O/Pslope=1.5us

CR14Receiver20Datarate=CLK/10

Dataclock

select1Datarate=CLK/80

Read/Write

Recognition

(Receiver1)1Enablelabelrecognition

Recognition

(Receiver2)1EnableLabelrecognition

32ndbit

asparity1Transmitter32ndbitisparity

decoder

Decoder

Transmitter

parity1Transmitter32ndbitisEvenparity

dataclock

select1Datarate=CLK/80,O/Pslope=10us

dataclock

select1Datarate=CLK/80

1Load16labelsusing/

Read16labelsusing/

passingTXAOUTandTXBOUT

tothereceiverinputs

1Normaloperation

1ARINCbits9and10mustmatch

CR7andCR8

theARINCbit9mustmatchthisbit

theARINCbit10mustmatchthisbit

1ARINCbits9and10mustmatch

CR10andCR11

theARINCbit9mustmatchthisbit

theARINCbit10mustmatchthisbit

PL1PL2

EN1EN2

TheHI-8582containsa9-bitstatusregisterwhichcanbe

interrogatedtodeterminethestatusoftheARINCreceivers,data

FIFOsandtransmitter.Thecontentsofthestatusregisterareoutput

onBD00-BD08whenthepinistakenlowandSEL=0.Unused

RSR

bitsareoutputaszeros.Thefollowingtabledefinesthestatus

registerbits.

SR

BitFUNCTIONSTATEDESCRIPTION

SR0Dataready0Receiver1FIFOempty

(Receiver1)

SR1FIFOhalffull0Receiver1FIFOholdslessthan16

(Receiver1)words

SR2FIFOfull0Receiver1FIFOnotfull

(Receiver1)

SR3Dataready0Receiver2FIFOempty

(Receiver2)

SR4FIFOhalffull0Receiver2FIFOholdslessthan16

(Receiver2)words

SR5FIFOfull0Receiver2FIFOnotfull

(Receiver2)

SR6TransmitterFIFO0TransmitterFIFOnotempty

empty

SR7TransmitterFIFO0TransmitterFIFOnotfull

full

SR8TransmitterFIFO0TransmitterFIFOcontainslessthan

halffull16words

1Receiver1FIFOcontainsvaliddata

Resetstozerowhenalldatahas

beenread.pinistheinverseof

thisbit

1Receiver1FIFOholdsatleast16

words.pinistheinverseof

thisbit.

1Receiver1FIFOfull.Toavoiddata

loss,theFIFOmustbereadwithin

oneARINCwordperiod.pinis

theinverseofthisbit

1Receiver2FIFOcontainsvaliddata

Resetstozerowhenalldatahas

beenread.pinistheinverseof

thisbit

1Receiver2FIFOholdsatleast16

words. pinistheinverseof

thisbit.

1Receiver2FIFOfull.Toavoiddata

loss,theFIFOmustbereadwithin

oneARINCwordperiod.pinis

theinverseofthisbit

1TransmitterFIFOempty.

1TransmitterFIFOfull.pinisthe

inverseofthisbit.

1TransmitterFIFOcontainsatleast

16words.pinisthe

inverseofthisbit.

D/R1

HF1

FF1

D/R2

HF2

FF2

FFT

HFT

CR15Data0ScrambleARINCdata

format

1UnscrambleARINCdata

HOLTINTEGRATEDCIRCUITS

3

HI-8582,HI-8583

FUNCTIONALDESCRIPTION(cont.)

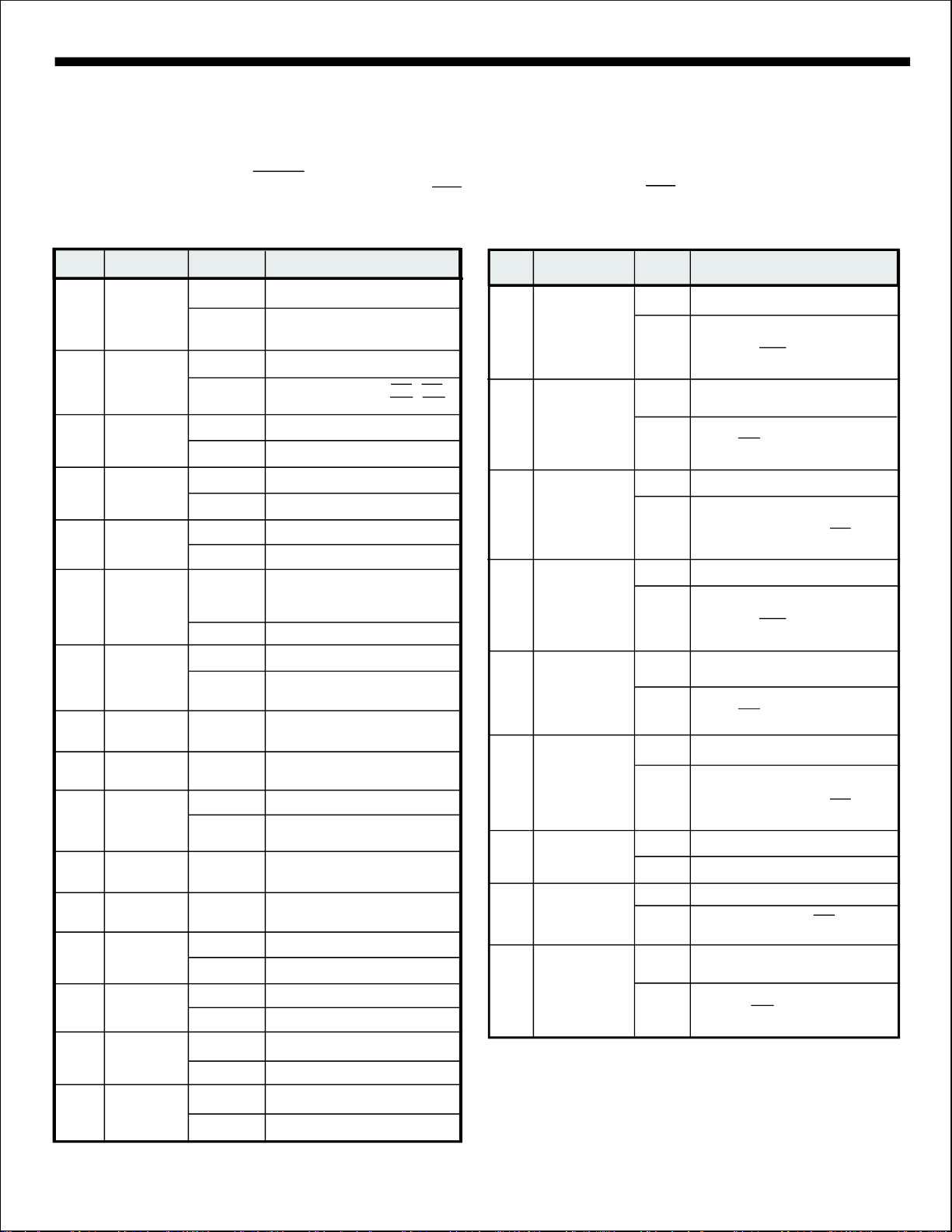

ARINC429DATAFORMAT

ControlregisterbitCR15isusedtocontrolhowindividualbitsinthe

receivedortransmittedARINCwordaremappedtotheHI-8582data

busduringdatareadorwriteoperations.Thefollowingtable

describesthismapping:

BYTE1

DATABDBDBDBDBDBDBDBDBDBDBDBDBDBDBDBD

BUS15141312111009080706050403020100

ARINC13121110931303212345678

BIT

CR15=0

ARINC16151413121110987654321

BIT

CR15=1

BYTE2

DATABDBDBDBDBDBDBDBDBDBDBDBDBDBDBDBD

BUS15141312111009080706050403020100

ARINC29282726252423222120191817161514

BIT

CR15=0

ARINC32313029282726252423222120191817

CR15=1

TheHI-8582guaranteesrecognitionoftheselevelswithacommon

modeVoltagewithrespecttoGNDlessthan±5Vfortheworstcase

condition(4.75Vsupplyand13Vsignallevel).

Thetolerancesinthedesignguaranteedetectionoftheabove

levels,sotheactualacceptancerangesareslightlylarger.Ifthe

ARINCsignalisoutoftheactualacceptanceranges,includingthe

nulls,thechiprejectsthedata.

RECEIVERLOGICOPERATION

Figure2showsablockdiagramofthelogicsectionofeachreceiver.

BITTIMING

TheARINC429specificationcontainsthefollowingtimingspecificationforthereceiveddata:

HIGHSPEEDLOWSPEED

BITRATE

PULSERISETIME

PULSEFALLTIME

PULSEWIDTH

Ifthepinishigh,theHI-8582acceptssignalsthatmeetthese

NFD

100KBPS±1%12K-14.5KBPS

1.5±0.5µsec10±5µsec

1.5±0.5µsec10±5µsec

5µsec±5%34.5to41.7µsec

specificationsandrejectsoutsidethetolerances.Thewaythelogic

operationachievesthisisdescribedbelow:

THERECEIVERS

ARINCBUSINTERFACE

Figure1showstheinputcircuitforeachreceiver.TheARINC429

specificationrequiresthefollowingdetectionlevels:

STATEDIFFERENTIALVOLTAGE

ONE+6.5Voltsto+13Volts

NULL+2.5Voltsto-2.5Volts

ZERO-6.5Voltsto-13Volts

FIGURE1.ARINCRECEIVERINPUT

1.Keytotheperformanceofthetimingcheckinglogicisanaccurate1MHzclocksource.Lessthan0.1%errorisrecommended.

2.Thesamplingshiftregistersare10bitslongandmustshow

threeconsecutiveOnes,ZerosorNullstobeconsideredvalid

data.Additionally,fordatabits,theOneorZerointheupper

bitsofthesamplingshiftregistersmustbefollowedbyaNullin

thelowerbitswithinthedatabittime.ForaNullinthewordgap,

threeconsecutiveNullsmustbefoundinboththeupperand

lowerbitsofthesamplingshiftregister.Inthismannertheminimumpulsewidthisguaranteed.

3.Eachdatabitmustfollowitspredecessorbynotlessthan8

samplesandnomorethan12samples.Inthismannerthebit

rateischecked.Withexactly1MHzinputclockfrequency,the

acceptabledatabitratesareasfollows:

HIGHSPEEDLOWSPEED

DATABITRATEMIN

DATABITRATEMAX

83KBPS10.4KBPS

125KBPS15.6KBPS

4.TheWordGaptimersamplestheNullshiftregisterevery10

inputclocks(80forlowspeed)afterthelastdatabitofavalid

reception.IftheNullispresent,theWordGapcounteris

incremented.Acountof3willenablethenextreception.

Ifisheldlow,frequencydiscriminationisdisabledandany

NFD

datastreamtotaling32bitsisacceptedevenwithgapsbetween

bits.Theprotocolstillrequiresawordgapasdefinedin4.above.

HOLTINTEGRATEDCIRCUITS

4

HI-8582,HI-8583

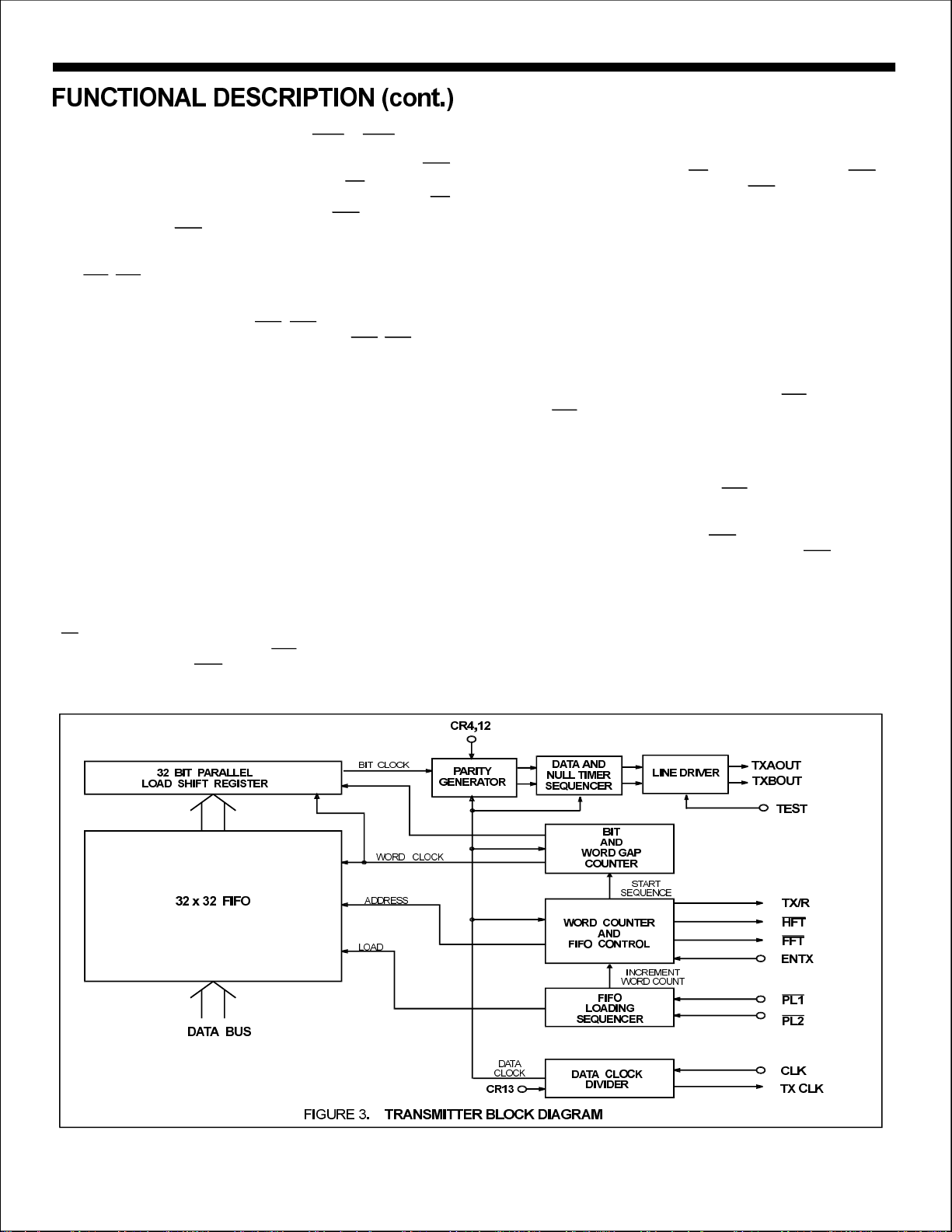

FUNCTIONALDESCRIPTION(cont.)

RECEIVERPARITY

Thereceiverparitycircuitcountsonesreceived,includingthe

paritybit.Iftheresultisodd,then"0"willappearinthe32ndbit.

RETRIEVINGDATA

Once32validbitsarerecognized,thereceiverlogicgeneratesan

EndofSequence(EOS).Dependinguponthestateofcontrol

registerbitsCR2-CR11,thereceivedARINC32-bitwordisthen

checkedforcorrectdecodingandlabelmatchingbeforebeing

loadedintothe32x32receiveFIFO.ARINCwordswhichdonot

meetthenecessary9thand10thARINCbitorlabelmatchingare

ignoredandarenotloadedintothereceiveFIFO.Thefollowing

tabledescribesthisoperation.

TOPINS

SEL

EN

HF

FF

D/R

MUX

CONTROL

FIFO

LOAD

CONTROL

32TO16DRIVER

32X32

FIFO

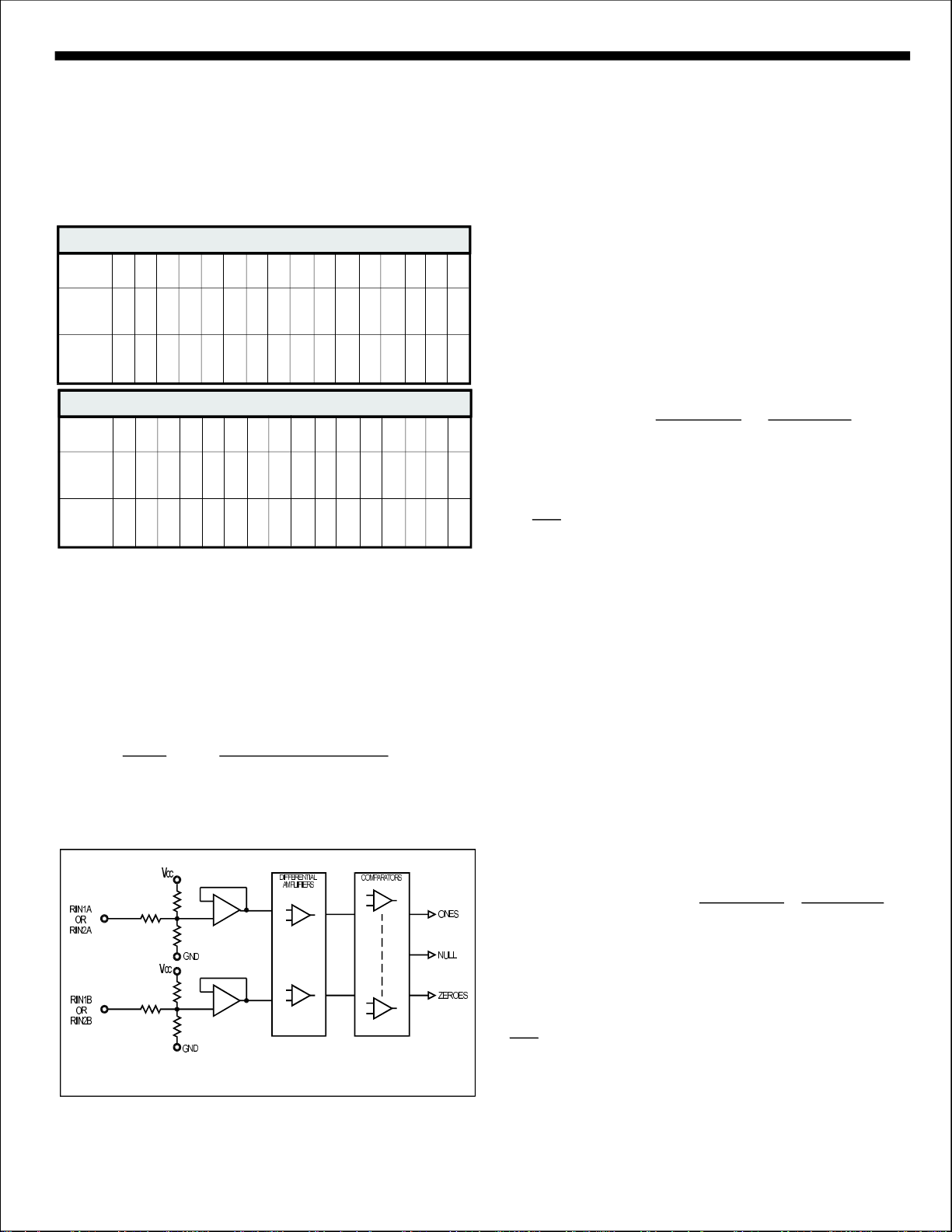

CR2(3)ARINCwordCR6(9)ARINCwordFIFO

matchesbits9,10

labelmatch

CR7,8(10,11)

0X0XLoadFIFO

1No0XIgnoredata

1Yes0XLoadFIFO

0X1NoIgnoredata

0X1YesLoadFIFO

1Yes1NoIgnoredata

1No1YesIgnoredata

1No1NoIgnoredata

1Yes1YesLoadFIFO

R/W

CONTROL

CONTROL

BITS

CONTROL

BIT

ONES

NULL

ZEROS

16x8

LABEL

MEMORY

EOS

LABEL/

DECODE

/

COMPARE

SHIFTREGISTER

SHIFTREGISTER

SHIFTREGISTER

FIGURE2. RECEIVERBLOCKDIAGRAM

32BITSHIFTREGISTER

CONTROLBITS

DATA

BITCLOCK

WORDGAP

START

CR0,CR14

PARITY

CHECK

WORDGAP

SEQUENCE

CONTROL

DETECTION

TIMER

ERROR

32ND

BIT

CLOCK

OPTION

BIT

COUNTER

AND

ENDOF

SEQUENCE

BITCLOCK

END

ERROR

CLOCK

CLK

CLOCK

HOLTINTEGRATEDCIRCUITS

5

HI-8582,HI-8583

OnceavalidARINCwordisloadedintotheFIFO,thenEOS

clocksthedatareadyflagflipfloptoa"1",or(orboth)

willgolow.Thedataflagforareceiverwillremainlowuntil

ARINCbytesfromthatreceiverareretrievedandtheFIFOis

empty.ThisisaccomplishedbyfirstactivatingwithSEL,the

byteselector,lowtoretrievethefirstbyteandthenactivating

withSELhightoretrievethesecondbyte.retrievesdata

fromreceiver1andretrievesdatafromreceiver2.

Upto32ARINCwordsmaybeloadedintoeachreceiver’sFIFO.

The()pinwillgolowwhenthereceiver1(2)FIFOisfull.

FF1FF2

FailuretoretrievedatafromafullFIFOwillcausethenextvalid

ARINCwordreceivedtooverwritetheexistingdatainFIFO

location32.AFIFOhalffullflag()goeslowiftheFIFO

contains16ormorereceivedARINCwords.The()pinis

intendedtoactasaninterruptflagtothesystem’sexternal

microprocessor,allowinga16worddataretrievalroutinetobe

performed,withouttheuserneedingtocontinuallypolltheHI8582’sstatusregisterbits.

EN2

HF1HF2

D/R1D/R2

both

EN

EN

EN1

HF1HF2

LABELRECOGNITION

Thechipcomparestheincominglabeltothestoredlabelsiflabel

recognitionisenabled.Ifamatchisfound,thedataisprocessed.

Ifamatchisnotfound,noindicatorsofreceivingARINCdataare

presented.Notethat00(Hex)istreatedinthesamewayasany

otherlabelvalue.Labelbitsignificanceisnotchangedbythe

statusofcontrolregisterbitCR15.LabelbitsBD00-BD07are

alwayscomparedtoreceivedARINCbits1-8respectively.

LOADINGLABELS

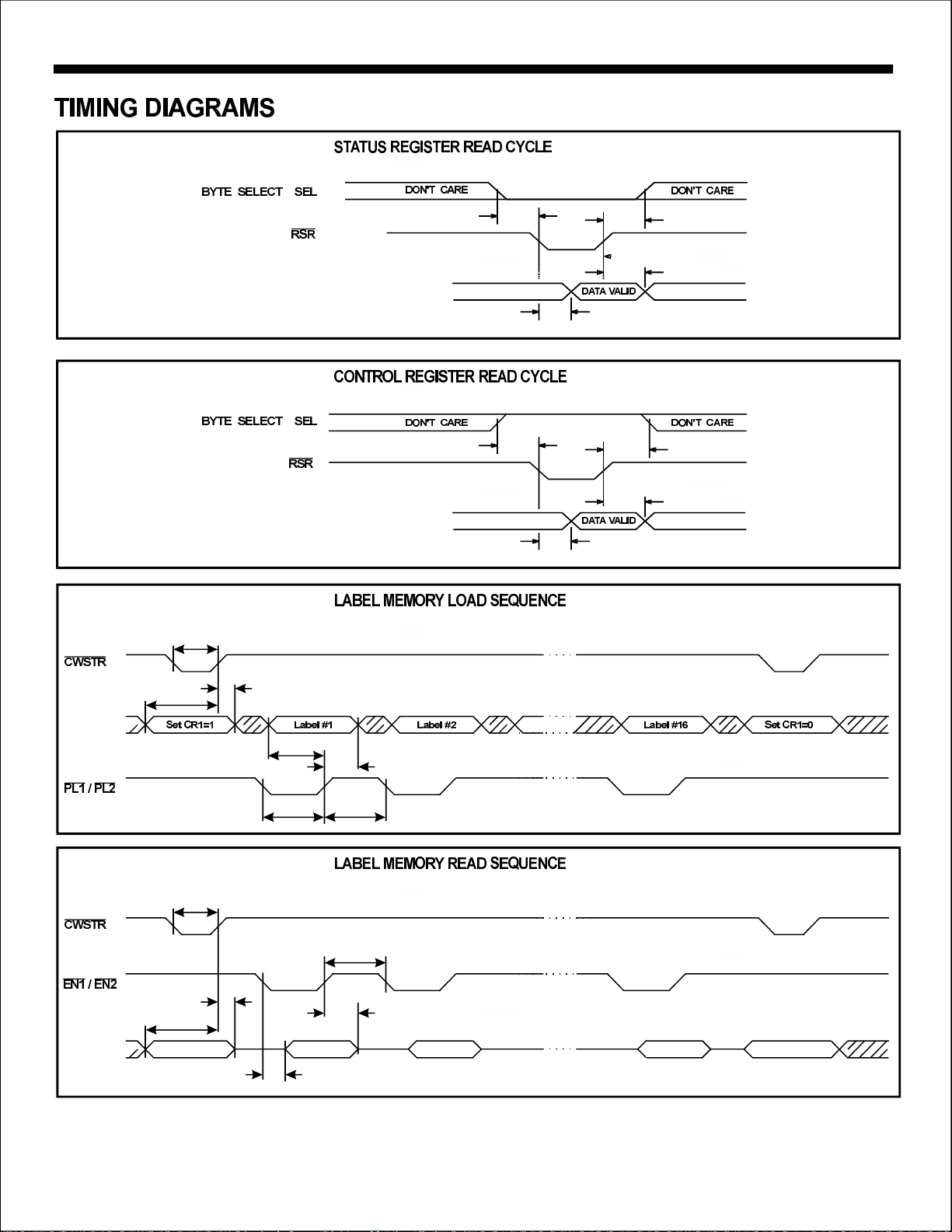

READINGLABELS

AfterthewritethatchangesCR1from0to1,thenext16data

readsoftheselectedreceiver(takenlow)arelabels.is

usedtoreadlabelsforreceiver1,andtoreadlabelsfor

receiver2.LabeldataispresentedonDB0-DB7.

Whenwritingto,orreadingfromthelabelmemory,SELmustbea

one,all16locationsshouldbeaccessed,andCR1mustbe

writtentozerobeforereturningtonormaloperation.Label

recognitionmustbedisabled(CR2/3=0)duringthelabelread

sequence.

ENEN1

EN2

TRANSMITTER

FIFOOPERATION

TheFIFOisloadedsequentiallybyfirstpulsingtoloadbyte1

andthentoloadbyte2.Thecontrollogicautomaticallyloads

the31bitword(or32bitwordifCR4=0)inthenextavailable

positionoftheFIFO.IfTX/R,thetransmitterreadyflagishigh

(FIFOempty),thenupto32words,each31or32bitslong,may

beloaded.IfTX/Rislow,thenonlytheavailablepositionsmaybe

loaded.Ifall32positionsarefull,theflagisassertedandthe

FIFOignoresfurtherattemptstoloaddata.

AtransmitterFIFOhalf-fullflagisprovided.Whenthe

transmitFIFOcontainslessthan16words,ishigh,

indicatingtothesystemmicroprocessorthata16ARINCword

blockwritesequencecanbeinitiated.

PL2

FFT

HFT

PL1

HFT

AfterawritethattakesCR1from0to1,thenext16writesofdata

(pulsedlow)loadlabeldataintoeachlocationofthelabel

PL

memoryfromtheBD0-7pins.Thepinisusedtowritelabel

dataforreceiver1andforreceiver2.

receptionissuspendedduringthelabelmemorywritesequence.

PL2 NotethatARINCword

PL1

Innormaloperation(CR4=1),the32ndbittransmittedisaparity

bit.Oddorevenparityisselectedbyprogrammingcontrol

registerbitCR12toazeroorone.IfCR4isprogrammedtoa0,

thenall32-bitsofdataloadedintothetransmitterFIFOare

treatedasdataandaretransmitted.

HOLTINTEGRATEDCIRCUITS

6

HI-8582,HI-8583

DATATRANSMISSION

WhenENTXgoeshigh,enablingtransmission,theFIFO

positionsareincrementedwiththetopregisterloadingintothe

datatransmissionshiftregister.Within2.5dataclocksthefirst

databitappearsatTXAOUTandTXBOUT.The31or32bitsin

thedatatransmissionshiftregisterarepresentedsequentiallyto

theoutputsintheARINC429formatwiththefollowingtiming:

HIGHSPEEDLOWSPEED

ARINCDATABITTIME10Clocks80Clocks

DATABITTIME5Clocks40Clocks

NULLBITTIME5Clocks40Clocks

WORDGAPTIME40Clocks320Clocks

Thewordcounterdetectswhenallloadedpositionshavebeen

transmittedandsetsthetransmitterreadyflag,TX/R,high.

TRANSMITTERPARITY

Theparitygeneratorcountsthe“1”sinthe31-bitword.Ifcontrol

registerbitCR12issetlow,the 32ndbittransmittedwillmake

parityodd.Ifthecontrolbitishigh,theparityiseven.Setting

CR4toazerobypassestheparitygenerator,andallows32bitsof

datatobetransmitted.

SELFTEST

IfcontrolregisterbitCR5issetlow,thetransmitterserialoutput

dataareinternallyconnectedtoeachofthetworeceivers,

bypassingtheanaloginterfacecircuitry.Dataispassed

unmodifiedtoreceiver1,andinvertedtoreceiver2.TakingTEST

highforcesTXAOUTandTXBOUTintothenullstateregardless

ofthestateofCR5.

SYSTEMOPERATION

Thetworeceiversareindependentofthetransmitter.

Therefore,controlofdataexchangesisstrictlyattheoptionof

theuser.Theonlyrestrictionsare:

1.ThereceiveddatawillbeoverwrittenifthereceiverFIFO

isfullandatleastonelocationisnotretrievedbeforethenext

completeARINCwordisreceived.

2.ThetransmitterFIFOcanstore32wordsmaximumand

ignoresattemptstoloadadditionaldataiffull.

LINEDRIVEROPERATION

ThelinedriverintheHI-8582isdesignedtodirectlydrivetheARINC

429bus.ThetwoARINCoutputs(TXAOUTandTXBOUT)provide

adifferentialvoltagetoproducea+10voltOne,a-10voltZero,

anda0voltNull.ControlregisterbitCR13controlsboththe

transmitterdatarate,andtheslopeofthedifferentialoutputsignal.

Noadditionalhardwareisrequiredtocontroltheslope.

ProgrammingCR13tozerocausesa100kbits/sdatarateanda

slopeof1.5sontheARINCoutputs;aoneonCR13causesa

12.5kbit/sdatarateandaslopeof10s.Timingissetbyon-chip

resistorandcapacitorandtestedtobewithinARINCrequirements.

TheHI-8582has37.5ohmsinserieswitheachlinedriveroutput.

The8583has10ohmsinseries.TheHI-8583isforapplications

whereexternalseriesresistanceisneeded,typicallyforlightning

protectiondevices.

µ

µ

REPEATEROPERATION

Repeatermodeofoperationallowsadatawordthathasbeen

receivedbytheHI-8582tobeplaceddirectlyintothetransmitter

FIFO.Repeateroperationissimilartonormalreceiveroperation.

Innormaloperation,eitherbyteofareceiveddatawordmaybe

readfromthereceiverlatchesfirstbyuseofSELinput.During

repeateroperationhowever,thelowerbyteofthedataword must

bereadfirst.Thisisnecessarybecause,asthedataisbeingread,

itisalsobeingloadedintotransmitterFIFOwhichisalwaysloaded

withthelowerbyteofthedatawordfirst.Signalflowforrepeater

operationisshownintheTimingDiagramssection.

HI-8582-10

TheHI-8582-10optionissimilartotheHI-8582withtheexception

thatitallowsanexternal10Kohmresistortobeaddedinseries

witheachARINCinputwithoutaffectingtheARINCinputthresholds.Thisoptionisespeciallyusefulinapplicationswherelightning

protectioncircuitryisalsorequired.

EachsideoftheARINCbusmustbeconnectedthrougha

10Kohmseriesresistorinorderforthechiptodetectthecorrect

ARINClevels.Thetypical10voltdifferentialsignalistranslated

andinputtoawindowcomparatorandlatch.Thecomparatorlevelsaresetsothatwiththeexternal10 Kohmresistors,theyare

justbelowthestandard6.5voltminimumARINCdatathreshold

andjustabovethestandard2.5VmaximumARINCnullthreshold.

HIGHSPEEDOPERATION

TheHI-8582maybeoperatedatclockfrequenciesbeyondthat

requiredforARINCcompliantoperation.ForoperationatMaster

Clock(CLK)frequenciesupto5MHz,pleasecontactHolt

applicationsengineering.

HOLTINTEGRATEDCIRCUITS

7

TXAOUT

TXBOUT

DATA

ARINCBIT

BIT30

NULL

DATA

BIT31

HI-8582,HI-8583

NULL

DATA

BIT32

NULL

WORDGAP

BIT1

NEXTWORD

DATABUS

DATABUS

PL1

PL2

TX/R,,HFTFFT

SELEN

t

END/R

t

t

PL

EN

t

ENSEL

BYTE2VALID

t

DWSET

t

DWHLD

t

TX/R

t

READEN

t

DATAEN

t

PL12

t

SELEN

t

ENDATA

t

D/R

t

t

ENDATA

t

SELEN

D/REN

t

DWSET

t

PL

t

ENSEL

BYTE1VALID

t

DWHLD

t

PL12

t

ENEN

t

DATAEN

t

ENDATA

t

DATABUS

CWSTR

VALID

t

CWSTR

t

CWSET

t

CWHLD

HOLTINTEGRATEDCIRCUITS

8

DATABUS

HI-8582,HI-8583

t

SELEN

t

ENDATA

t

SELEN

t

ENSEL

t

ENSEL

t

DATAEN

DATABUS

t

CWSTR

t

CWSET

t

CWSTR

DATABUS

t

CWHLD

t

DWSET

t

PL

t

LABEL

t

READEN

t

DWHLD

t

ENDATA

t

DATAEN

DATABUS

t

CWHLD

t

CWSET

SetCR1=1 Label#1 Label#16 SetCR1=0

t

ENDATA

t

DATAEN

Label#2

HOLTINTEGRATEDCIRCUITS

9

PL2

TXR

t

PL2EN

HI-8582,HI-8583

t

DTX/R

t

ENTX/R

ENTX

TXAOUT

TXBOUT

V

DIFF

(TXAOUT)-TXBOUT)

RIN

D/R

EN

BIT32

t

D/R

onelevel

t

D/REN

t

ENDAT

10%

ARINCBIT

DATA

BIT1

+5V

-5V

t

+10V

90%

t

rx

t

EN

fx

zerolevel

t

ENEN

t

END/R

10%

90%

t

fx

ARINCBIT

DATA

BIT2

-5V

+5V

t

-10V

t

EN

ARINCBIT

DATA

BIT32

+5V

-5V

+10V

rx

nulllevel

SEL

PL1

PL2

TXR

ENTX

TXAOUT

TXBOUT

t

SELEN

DON'TCARE

t

ENPL

t

ENSEL

t

t

PLEN

t

ENPL

SELEN

t

TX/REN

t

PLEN

t

TX/R

HOLTINTEGRATEDCIRCUITS

10

t

ENSEL

t

ENDAT

DON'TCARE

BIT1 BIT32

t

t

DTX/R

ENTX/R

t

NULL

HI-8582,HI-8583

SupplyVoltagesV...........................................-0.3Vto+7V

DD

V+......................................................+13.0V

V-......................................................-13.0V

VoltageatpinsRIN1A,RIN1B,RIN2A,RIN2B.....-29Vto+29V

Voltageatanyotherpin...............................-0.3VtoV+0.3V

Soldertemperature(Leads)....................280for10seconds

°C

DD

(Package)..........................................220

NOTE:Stressesabovethoselistedunder"AbsoluteMaximumRatings"maycausepermanentdamagetothedevice.Thesearestressratingsonly.

Functionaloperationofthedeviceattheseoranyotherconditionsabovethoseindicatedintheoperationalsectionsofthespecificationsisnotimplied.

Exposuretoabsolutemaximumratingconditionsforextendedperiodsmayaffectdevicereliability.

PowerDissipationat25°C

PlasticQuadFlatPack..................1.5W,derate10mW/C

CeramicJ-LEADCERQUAD......1.0W,derate7mW/

DCCurrentDrainperpin..............................................±10mA

StorageTemperatureRange........................-65°Cto+150°C

OperatingTemperatureRange(Industrial):....-40°Cto+85°C

°C

(Military):.....-55°Cto+125°C

°

°C

HOLTINTEGRATEDCIRCUITS

11

InputVoltage:InputVoltageHIV2.0V

InputVoltage:InputVoltageHIV2.0V

putSourceI-1.5A

V=5V,GND=0V,TA=OperatingTemperatureRange(unlessotherwisespecified).DD V+=10V,V-=-10V,

OutputVoltage:Logic"1"OutputVoltageVI=-1.5mA2.7V

HI-8582,HI-8583

PARAMETERCONDITIONSUNITSYMBOL

ARINCINPUTS-PinsRIN1A,RIN1B,RIN2A,RIN2B

DifferentialInputVoltage:ONEVPins2to3,4to5:Common6.510.013.0V

ZEROVmodevoltagelessthan±5V-13.0-10.0-6.5V

NULLVwithrespecttoGND-2.502.5V

InputResistance:DifferentialR1246K

ToGNDR1238K

ToVR1238K

DDH

InputCurrent:InputSinkI200µA

InputSourceI-450µA

InputCapacitance:DifferentialCPins2to3,4to520pF

(Guaranteedbutnottested)ToGNDC20pF

ToVC20pF

DDH

BI-DIRECTIONALINPUTS-PinsDB0-DB15

InputVoltageLOV0.8V

InputCurrent:InputSinkI1.5µA

InputSourceI-1.5µA

OTHERINPUTS

InputVoltageLOV0.8V

IH

IL

NUL

I

G

IH

IL

I

G

IH

IL

IH

IL

IH

IL

MINTYPMAX

W

W

W

LIMITS

InputCurrent:InputSinkI1.5µA

In

Pull-upcurrent(Pin)I-150-50

NFD

PU

IH

IL

µ

µA

Pull-downCurrent(TESTPin)I50150µAPD

ARINCOUTPUTS-PinsTXAOUT,TXBOUT

ARINCoutputvoltage(Ref.ToGND)OneorzeroVNoloadandmagnitudeatpin,4.505.005.50V

NullVV=5.0V-0.250.25V

ARINCoutputvoltage(Differential)OneorzeroVNoloadandmagnitudeatpin,9.010.011.0V

NullVV=5.0V-0.50.5V

ARINCoutputcurrentI80mA

DOUT

NOUTDD

DDIF

NDIFDD

OUT

OTHEROUTPUTS

Logic"0"OutputVoltageVI=1.6mA0.4V

OutputCurrent:OutputSinkIV=0.4V1.6mA

(AllOutputs&Bi-directionalPins)OutputSourceIV=V-0.4V-1.0mA

OutputCapacitance:C15pF

OHOH

OLOL

OLOUT

OHOUTDD

O

OperatingVoltageRange

VDD4.755.25V

V+9.512.6V

V--9.5-12.6V

OperatingSupplyCurrent

VDDI420mA

V+I3.216mA

V-I3.216mA

DD1

DD2

EE1

HOLTINTEGRATEDCIRCUITS

12

HI-8582,HI-8583

VDD=5V,V+=10V,V-=-10V,GND=0V,TA=Oper.Temp.Rangeandfclk=1MHz0.1%with60/40dutycycle+

PARAMETERSYMBOLUNITS

LIMITS

MINTYPMAX

CONTROLWORDTIMING

Setup-DATABUSValidtoHIGHt50ns

PulseWidth-t50ns

Hold-HIGHtoDATABUSHi-Zt0ns

CWSTR

RECEIVERFIFOANDLABELREADTIMING

Delay-StartARINC32ndBittoLOW:HighSpeedt16µs

D/R

Delay-LOWtoL0Wt0ns

Delay-LOWtoHIGHt250350ns

D/REN

END/R

Setup-SELtoL0Wt0ns

Hold-SELtoHIGHt0ns

Delay-L0WtoDATABUSValidt60100ns

EN

Delay-HIGHtoDATABUSHi-Zt5080ns

EN

PulseWidth-ort60ns

Spacing-HIGHtonextL0W(SameARINCWord)t60ns

Spacing-HIGHtonextLOW(NextARINCWord)t200ns

ENEN

ENEN

TRANSMITTERFIFOANDLABELWRITETIMING

PulseWidth-ort50ns

Setup-DATABUSValidtoHIGHt50ns

Hold-HIGHtoDATABUSHi-Zt0ns

PL

SpacingbetweenLabelWritepulsest200ns

Delay-HIGHtoTX/RLOWt300ns

Spacing-ort85ns

PL2

TRANSMISSIONTIMING

Spacing-HIGHtoENTXHIGHt0µs

PL2

Delay-32ndARINCBittoTX/RHIGHt50ns

Spacing-TX/RHIGHtoENTXL0Wt0ns

LINEDRIVEROUTPUTTIMING

Delay-ENTXHIGHtoTXAOUTorTXBOUT:HighSpeedt25

Delay-ENTXHIGHtoTXAOUTorTXBOUT:LowSpeedt200

Linedrivertransitiondifferentialtimes:

(HighSpeed,controlregisterCR13=Logic0)µs

CWSTR

CWSTR

LowSpeedt128µs

EN

EN

EN1EN2

PL1PL2

PL

PL1PL2

hightolowt1.01.52.0

lowtohight1.01.52.0

CWSTR

CWSET

CWHLD

D/R

D/R

D/REN

END/R

SELEN

ENSEL

ENDATA

DATAEN

EN

ENEN

READEN

PL

DWSET

DWHLD

PL12

LABEL

TX/R

PL2EN

DTX/R

ENTX/R

ENDAT

ENDAT

fx

rx

µs

µs

µs

REPEATEROPERATIONTIMING

Delay-LOWtoLOWtENPL0nsENPL

Hold-HIGHtoHIGHtPLEN0ns

PLEN

Delay-TX/RLOWtoENTXHIGHtTX/REN0ns

MasterResetPulseWidthtMR50ns

ARINCDataRateandBitTiming±1%

HOLTINTEGRATEDCIRCUITS

13

HI-8582,HI-8583

ADDITIONALHI-8582PINCONFIGURATION

FF1

-8

HF1

-9

D/R2

-10

FF2

-11

HF2

-12

SEL-13

EN1

-14

EN2

-15

BD15-16

BD14-17

BD13-18

BD12-19

BD11-20

HI-8582CJI

&

HI-8582CJT

52-PinCerquadJ-lead

(Seepage1foradditionalpinconfiguration)

46-N/C

45-

CWSTR

44-ENTX

43-V+

42-TXBOUT

41-TXAOUT

40-V39-

FFT

38-

HET

37-TX/R

36-

PL2

35-

PL1

34-BD00

ORDERINGINFORMATION

HI-8582xxx-xx

Nodashnumber

-10

I

T

CJ

PQ

35Kohm0

25Kohm10Kohm

-40°CTO+85°C NOI

-55°CTO+125°C NOT

52PINCERQUADJLEAD

SOLDER

SOLDER52PINPLASTICQUADFLATPACK(PQFP)

8582

8583

37.5Ohms0

10Ohms27.5Ohms

HOLTINTEGRATEDCIRCUITS

14

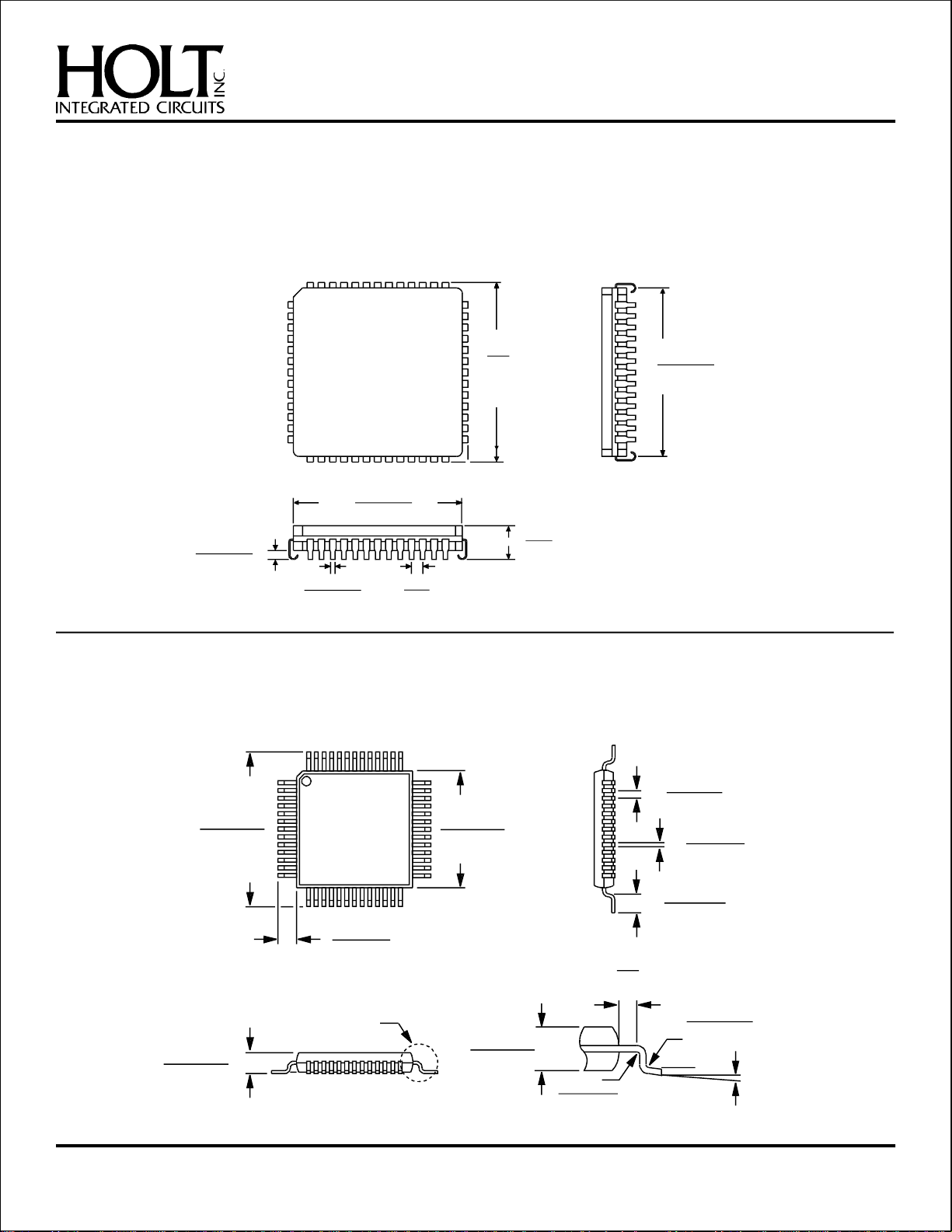

52-PINJ-LEADCERQUAD

715247

8

HI-8582PACKAGEDIMENSIONS

inches(millimeters)

PackageType:

52U

.788

(20.0)

MAX.

SQ.

.750 ± .007

(19.05 ± .18)

.040 ±.005

(1.02 ±.013)

.019 ±.002

(.483 ± .051)

.050

(1.27)

TYP.

(4.826)

52-PINPLASTICQUADFLATPACK(PQFP)

.520 ± .010

(13.2 ± .25)

SQ.

.394 ± .004

(10.00 ± .10)

SQ.

.190

MAX.

.720 ± .010

(18.29± .25)

PackageType:

.0256BSC

(0.65BSC)

.012 ± .003

(.30 ± .08)

52PQS

.092 ± .004

(2.32 ± .12)

.063 ± .032

(1.6 ± .175)

Typ.

SeeDetailA

HOLTINTEGRATEDCIRCUITS

.079 ± .002

(2.00 ± .05)

15

.009Rtyp

(0.23Rtyp)

.035 ± .006

(.88 ± .15)

.008

(0.20)

Min.

.009 ± .003R

(.225 ± .075R)

0°≤Θ≤7°

ETAILDA

Loading...

Loading...