Page 1

AAnnyybbuuss®®CCoommppaaccttCCoomm BB4400--11

DESIGN GUIDE

HMSI-27-230 3.4 en-US ENGLISH

Page 2

Important User Information

Liability

Every care has been taken in the preparation of this document. Please inform HMS Industrial Networks of any

inaccuracies or omissions. The data and illustrations found in this document are not binding. We, HMS Industrial

Networks, reserve the right to modify our products in line with our policy of continuous product development. The

information in this document is subject to change without notice and should not be considered as a commitment by

HMS Industrial Networks. HMS Industrial Networks assumes no responsibility for any errors that may appear in this

document.

There are many applications of this product. Those responsible for the use of this device must ensure that all the

necessary steps have been taken to verify that the applications meet all performance and safety requirements

including any applicable laws, regulations, codes, and standards.

HMS Industrial Networks will under no circumstances assume liability or responsibility for any problems that may

arise as a result from the use of undocumented features, timing, or functional side effects found outside the

documented scope of this product. The effects caused by any direct or indirect use of such aspects of the product

are undefined, and may include e.g. compatibility issues and stability issues.

The examples and illustrations in this document are included solely for illustrative purposes. Because of the many

variables and requirements associated with any particular implementation, HMS Industrial Networks cannot assume

responsibility for actual use based on these examples and illustrations.

Intellectual Property Rights

HMS Industrial Networks has intellectual property rights relating to technology embodied in the product described in

this document. These intellectual property rights may include patents and pending patent applications in the USA

and other countries.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 3

Table of Contents

Page

1 Preface ................................................................................................................................. 3

1.1 About this Document........................................................................................................3

1.2 Related Documents .......................................................................................................... 3

1.3 Document history ...................................................... ....... ....... ....... ....... .......................... 3

1.4 Document Conventions ..................................................................................................... 4

1.5 Document Specific Conventions..........................................................................................4

1.6 Trademark Information .............................................................. ....... ....... ....... ....... ....... ....5

2 About the Anybus CompactCom B40-1.............................................................................. 6

2.1 General Information .... ............................................................... ....... ....... ....... ....... ....... ... 6

2.2 Features .........................................................................................................................7

3 Host Interface ...................................................................................................................... 8

3.1 Overview ....... ....... ....... ....... ....... ....... ....... ....... ....... ......................................................... 8

3.2 Host Application Connector ............ ....... .......................................................................... 10

3.3 Parallel Interface Operation ............................................................... ....... ....... ....... ....... .. 20

3.4 SPI Operation ................................................................................. ....... ........................ 26

3.5 Stand-alone Shift Register................................................................................................ 30

3.6 UART Operation... ....... ........................................................ ....... ....... ....... ....... ....... ....... . 37

4 Network Connector........................................................................................................... 40

4.1 Overview ....... ....... ....... ....... ....... ....... ....... ....... ....... ....................................................... 41

4.2 Power Supply Pins ........................................................................................... ....... ....... . 43

4.3 How to Connect Unused Network Connector Pins................................................................ 43

4.4 Ethernet Based Networks (Copper) ........................... ....... ................................................. 44

4.5 Ethernet Fiber Optic Networks ................................................. ....... ....... ....... ....... ....... ..... 45

4.6 DeviceNet...... ....... ....... ....... .......................................................................................... 47

4.7 PROFIBUS ............................................................................................. ........................ 47

4.8 CC-Link. ....... ....... ....... ........................................................ ....... ....... ....... ....... ....... ....... . 47

4.9 LED Indicators ..... ....... ........................................................ ....... ....... ....... ....... ....... ....... . 48

5 EMC .................................................................................................................................... 50

5.1 General ........................... ....... ....... ....... ....... ....... ....... ....... ............................................ 50

5.2 Bulk and Decoupling ....................................................................................................... 50

5.3 Reset Signal ................... ....... ....... ....... ........................................................ ....... ....... .... 50

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 4

6 Black Channel/Safety Interface ........................................................................................ 51

A Mechanical Specification .................................................................................................. 53

A.1 Anybus CompactCom B40-1 ............................................................................................. 53

A.2 Connector Board for PROFIBUS ..... ....... ....... ....... ....... ....... ....... ....... .................................. 54

A.3 Connector Board for Copper Based Ethernet....................................................................... 55

A.4 Connector Board for Fiber Optic Ethernet . ....... ....... ....... ....... ....... ...................................... 56

A.5 Connector Board for CC-Link and DeviceNet ............................ ....... ....... ....... ....... ....... ........ 57

A.6 Footprints. ....... ....... ....... ....... ....... ....... ........................................................ ....... ....... .... 58

A.7 Height Restrictions ......................................................................................................... 59

A.8 Front Plate Restrictions .... ....... ....... ....... ........................................................ ....... ....... .... 60

A.9 Assembly.. ....... ....... ....... ....... ....... ....... ........................................................ ....... ....... .... 60

B Technical Specification...................................................................................................... 63

B.1 Environmental ................................................................................ ....... ........................ 63

B.2 Shock and Vibration .......... ....... ....... ....... ....... ....... .......................................................... 63

B.3 Electrical Characteristics .................................................................................................. 63

B.4 Regulatory Compliance ................................................................................................... 64

C How to Disable Ethernet Port 2 (EtherNet/IP) ................................................................ 65

D Implementation Examples ................................................................................................ 66

D.1 General ..... ....... ....... ....... .............................................................................................. 66

D.2 SPI.... ....... ....... ....... ...................................................................................................... 67

D.3 16-bit Parallel . ....... ....... ....... ....... ....... ....... ..................................................................... 68

D.4 8-bit Parallel............................... ....... ....... ....... ....... ....... ....... ....... ....... ........................... 69

D.5 Serial .................................................................................................... ....... ....... ....... .. 70

D.6 Network Status LED Outputs (LED[1A...4B]) .................................................... ....... ....... ...... 70

D.7 Power Supply Considerations ....................... ....... ............................................................. 72

E Design Examples, Network Interface ............................................................................... 74

E.1 Recommendations ....... ....... ....... ....... ....... ....... ....... ....... ................................................. 74

E.2 PCB Layout .. ....... ....... ........................................................ ....... ....... ....... ....... ....... ....... . 76

E.3 Network Interface Examples ........................................................... ....... ....... ....... ....... ..... 77

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 5

Preface 3 (78)

1 Preface

1.1 About this Document

This document is intended to provide a good understanding of how to use the Anybus

CompactCom B40-1.

The reader of this document is expected to be familiar with hardware design and communication

systems in general. For additional information, documentation, support etc., please visit the

support website at www.anybus.com/support.

1.2 Related Documents

Document

Anybus CompactCom 40 Software Design Guide

Anybus CompactCom 40 Network Guides

Anybus CompactCom Host Application Implementation Guide

1.3 Document history

Author

HMS HMSI-216-125

HMS

HMS HMSI-27-334

Document ID

Version

1.23 2015-09-03 Last FM version.

2.0 2016-03-10

2.1 2016-12-07

3.0 2017-09-12

3.1 2018-03-09

3.2 2018-05-25

3.3 2018-10-23 Minor corrections

3.4 2019-02-27

Date

Description

Moved from FM to XML

Misc. updates

Added information for Anybus CompactCom B40 CC-Link IE Field

Minor corrections and updates

Added content to make the design guide independent of the M40 HWDG

Added new example schematics

Added BACnet/IP

Updated section on DIP1 and DIP2 usage

Added section on EMC

Misc corrections

Corrected pinnings for 8-bit parallel

Misc corrections

Updated for CANopen release

Rebranded

®

Anybus

CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 6

Preface 4 (78)

1.4 Document Conventions

Ordered lists are used for instructions that must be carried out in sequence:

1. First do this

2. Then do this

Unordered (bulleted) lists are used for:

• Itemized information

• Instructions that can be carried out in any order

...and for action-result type instructions:

► This action...

→ leads to this result

Bold typeface indicates interactive parts such as connectors and switches on the hardware, or

menus and buttons in a graphical user interface.

Monospaced text is used to indicate program code and other

kinds of data input/output such as configuration scripts.

This is a cross-reference within this document: Document Conventions, p. 4

This is an external link (URL): www.hms-networks.com

This is additional information which may facilitate installation and/or operation.

This instruction must be followed to avoid a risk of reduced functionality and/or damage

to the equipment, or to avoid a network security risk.

Caution

This instruction must be followed to avoid a risk of personal injury.

WARNING

This instruction must be followed to avoid a risk of death or serious injury.

1.5 Document Specific Conventions

• The terms “Anybus” or “module” refers to the Anybus CompactCom module.

• The terms “host” or “host application” refer to the device that hosts the Anybus.

• Hexadecimal values are written in the format NNNNh or 0xNNNN, where NNNN is the

hexadecimal value.

• A byte always consists of 8 bits.

• All dimensions in this document have a tolerance of ±0.10 mm unless otherwise stated.

• Outputs are TTL compliant unless otherwise stated.

• Signals which are “pulled to GND” are connected to GND via a resistor.

• Signals which are “pulled to 3V3” are connected to 3V3 via a resistor.

• Signals which are “tied to GND” are directly connected to GND,

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 7

Preface 5 (78)

• Signals which are “tied to 3V3” are directly connected to 3V3.

1.5.1 PIN Types

The pin types of the connectors are defined in the table below. The pin type may be different

depending on which mode is used.

Pin type

I Input

O Output

I/O Input/Output (bidirectional)

OD Open Drain

Power

Definition

Pin connected directly to module power supply, GND or 3V3

1.6 Trademark Information

Anybus®is a registered trademark of HMS Industrial Networks.

EtherCAT®is a registered trademark and patented technology, licensed by Beckhoff Automation

GmbH, Germany.

All other trademarks are the property of their respective holders.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 8

About the Anybus CompactCom B40-1 6 (78)

2 About the Anybus CompactCom B40-1

2.1 General Information

The Anybus CompactCom B40-1 concept is developed for applications where the standard

Anybus CompactCom M40 cannot be used. The brick consists of a board with network

connectivity functionality, where the customer provides the physical network interface, including

network connectors. There are also available interface boards for several networks, providing

network connectors and physical interface.

All Anybus CompactCom B40-1 share footprint and electrical interface. The brick has two

connectors that provides communication with the host application board. The host application

connector provides an interface between the host application and the brick, while the network

connector provides network access. This enables full Anybus CompactCom functionality for all

applications without loss of network compatibility or environmental characteristics.

All dimensions expressed in this document are stated in millimeters and have a tolerance of

±0.10 mm unless stated otherwise.

For general information about the Anybus CompactCom 40 platform, consult the Anybus

CompactCom 40 Software Design Guide.

This a class A product. In a domestic environment, this product may cause radio

interference in which case the user may be required to take adequate measures.

This product contains ESD (Electrostatic Discharge) sensitive parts that may be damaged if

ESD control procedures are not followed. Static control precautions are required when

handling the product. Failure to observe this may cause damage to the product.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 9

About the Anybus CompactCom B40-1 7 (78)

2.2 Features

• Hardware support for triple buffered process data, which increases performance

• Supports synchronization for selected industrial networks

• Black channel interface, offering a transparent channel for safety communication for

selected networks

• Low latency

• Integrated protocol stack handling (where applicable)

• Control pins for status indications according to each network standard (where applicable)

• Separate network connector boards available

• Firmware upgradable (FLASH technology)

• 3.3 V design

• 8-bit and 16-bit parallel modes

• SPI mode

• Shift register mode

• UART/Serial mode

• Transparent Ethernet functionality

• Precompliance tested for network conformance (where applicable).

• Precompliance tested for CE & UL. Contact HMS Industrial Networks for further information.

All Anybus CompactCom B40-1 will be precertified for network conformance. This is done

to ensure that the final product can be certified, but it does not necessarily mean that the

final product does not require recertification. Contact HMS Industrial Networks for

further information.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 10

Host Interface 8 (78)

Host

CPU

Flash

Parallel Interface,

8-bit or 16-bit

Serial Interface

LED I/F

or RMII

RAM

A0 ... A13

Tx

Rx

LED[1A, 1B, 2A, 2B]

LED[3A, 3B, 4A, 4B]

RESET

OM[0...3]

MI[0...1]

MD

D0 ... D7

CS

OE

WE

IRQ

Physical Interface

Anybus

CPU

Network

Communications Controller

SPI

Shift Registers

SS

SCLK

MISO

MOSI

LD

SCLK

DO

DI

CT

PA

DIP1[0...7]

DIP2[0...7]

IRQ

D8 ... D15

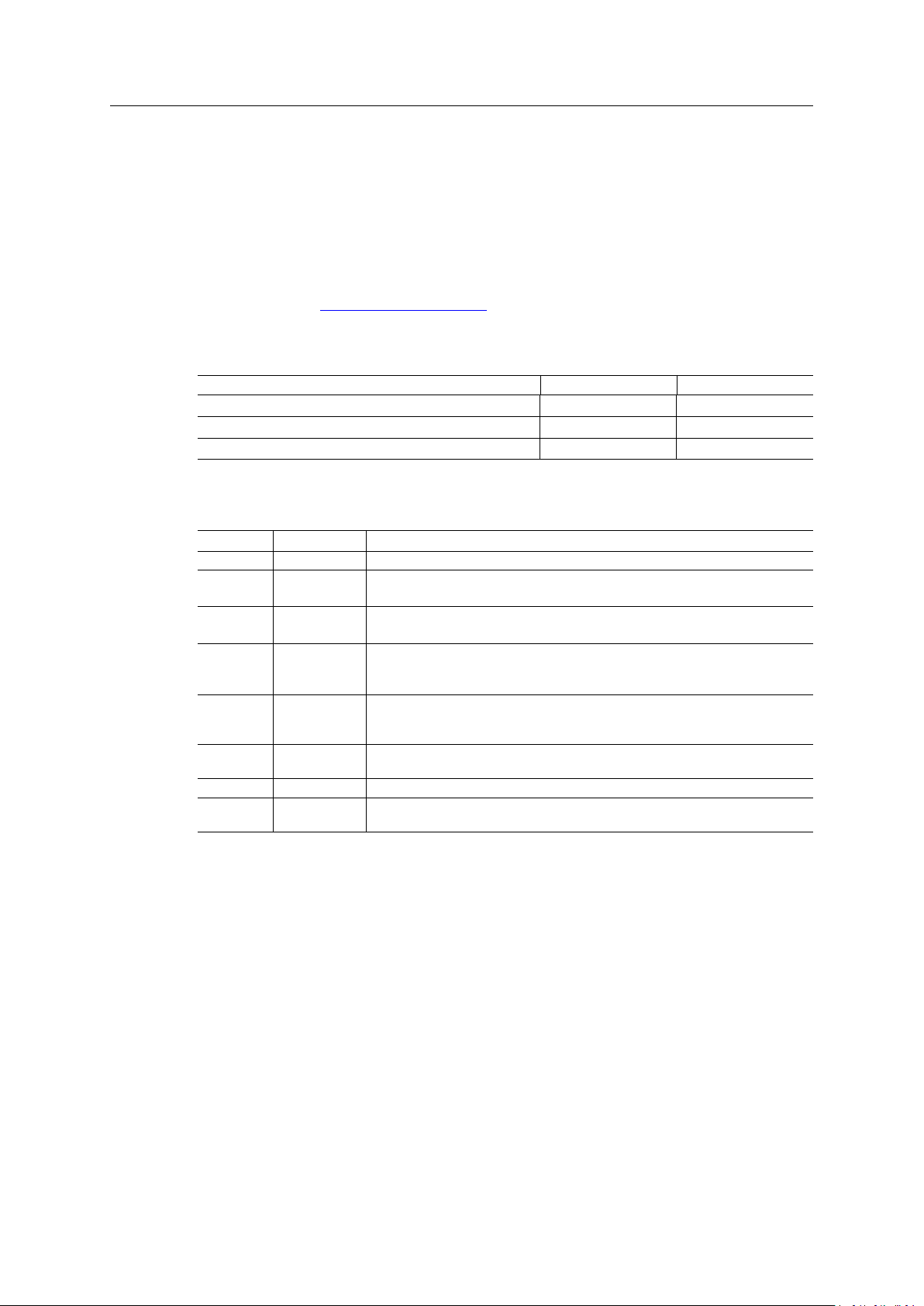

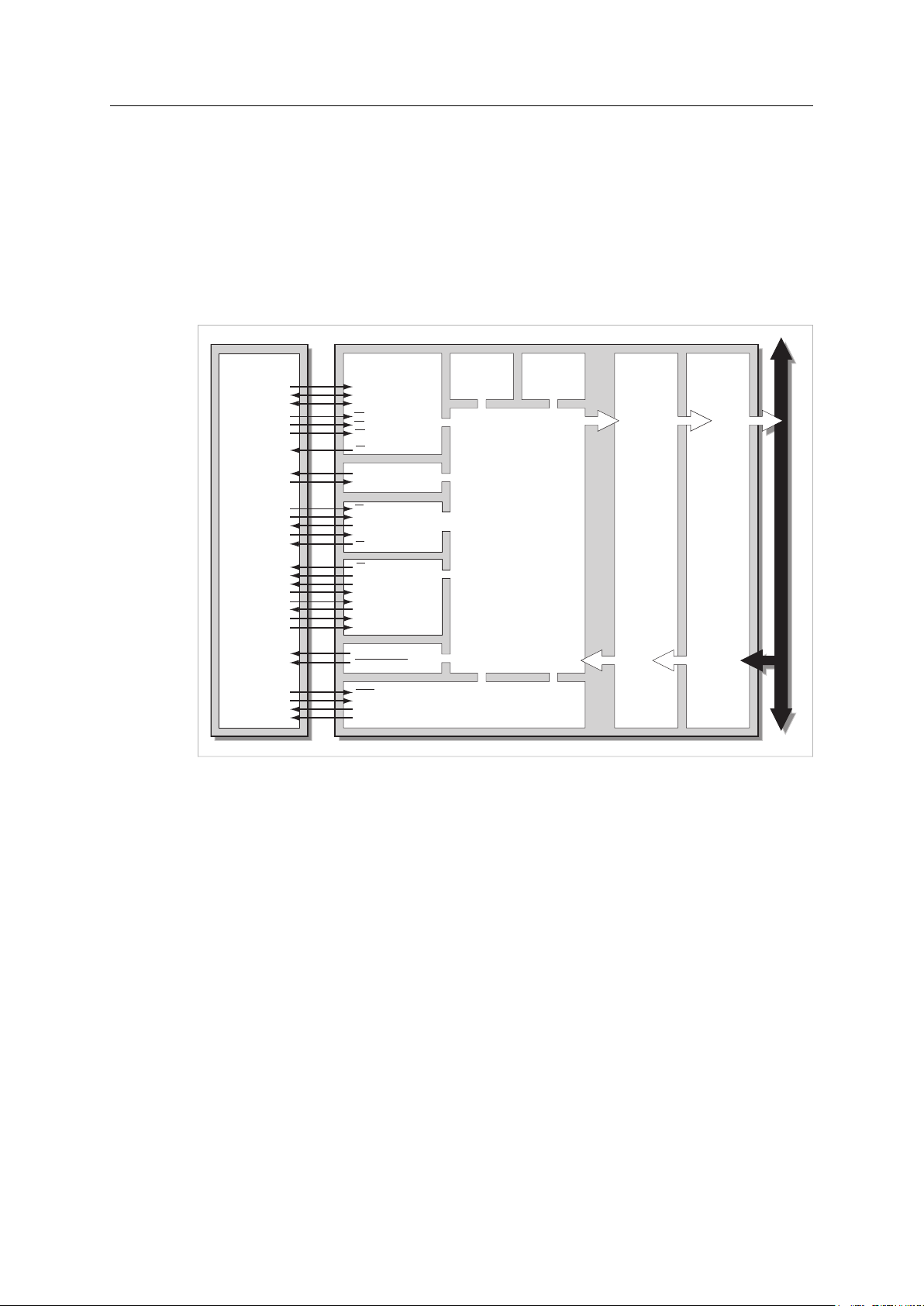

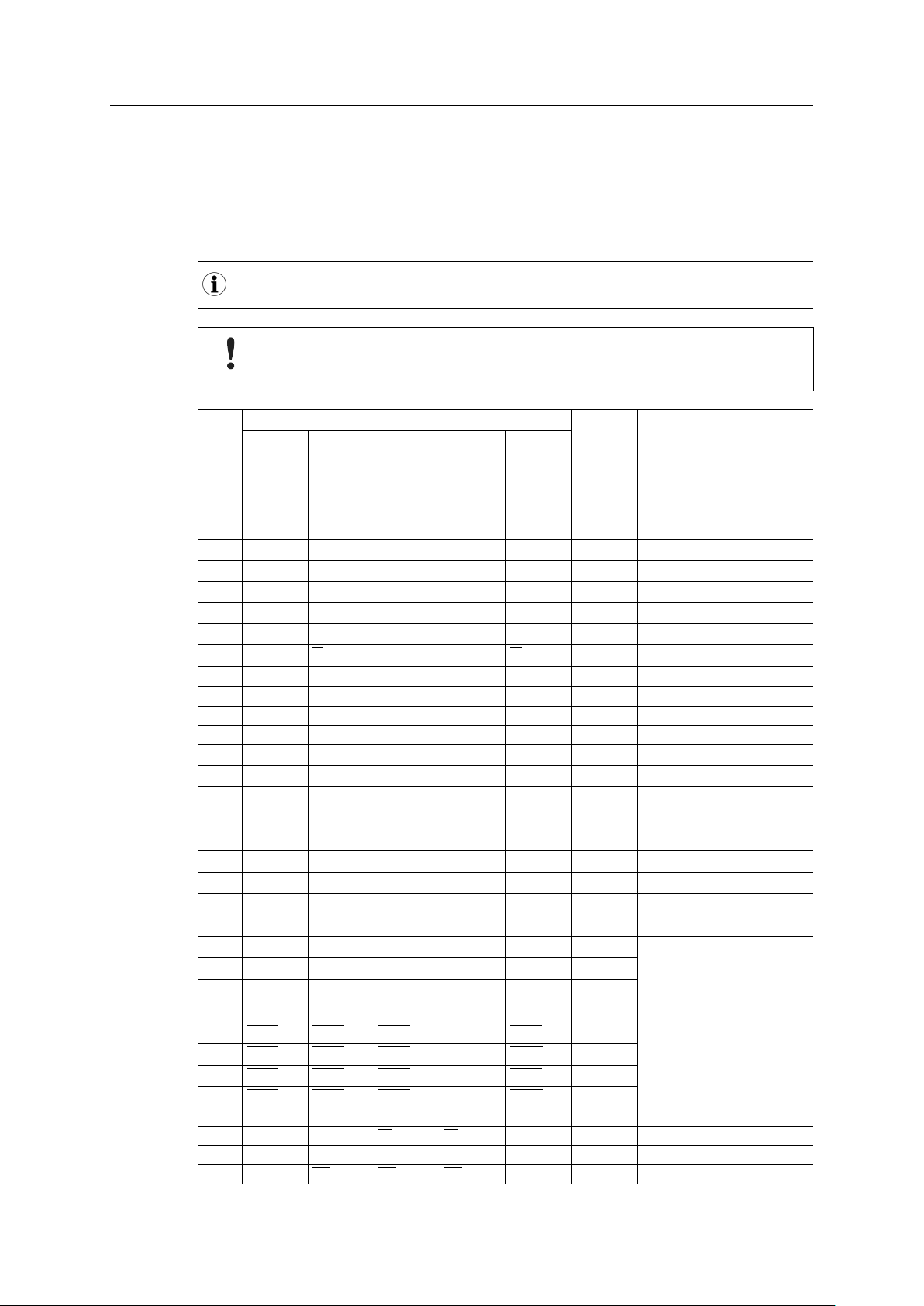

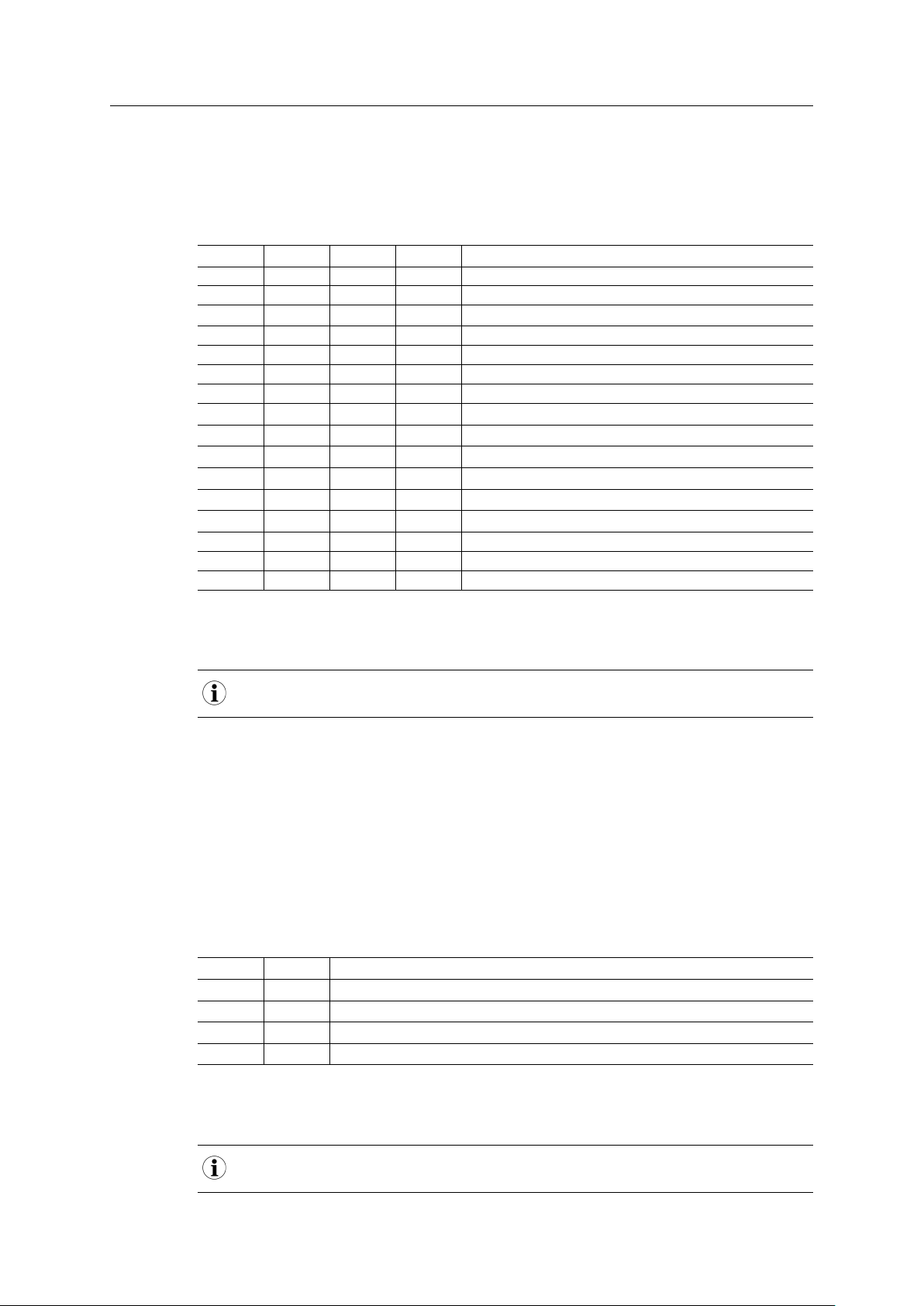

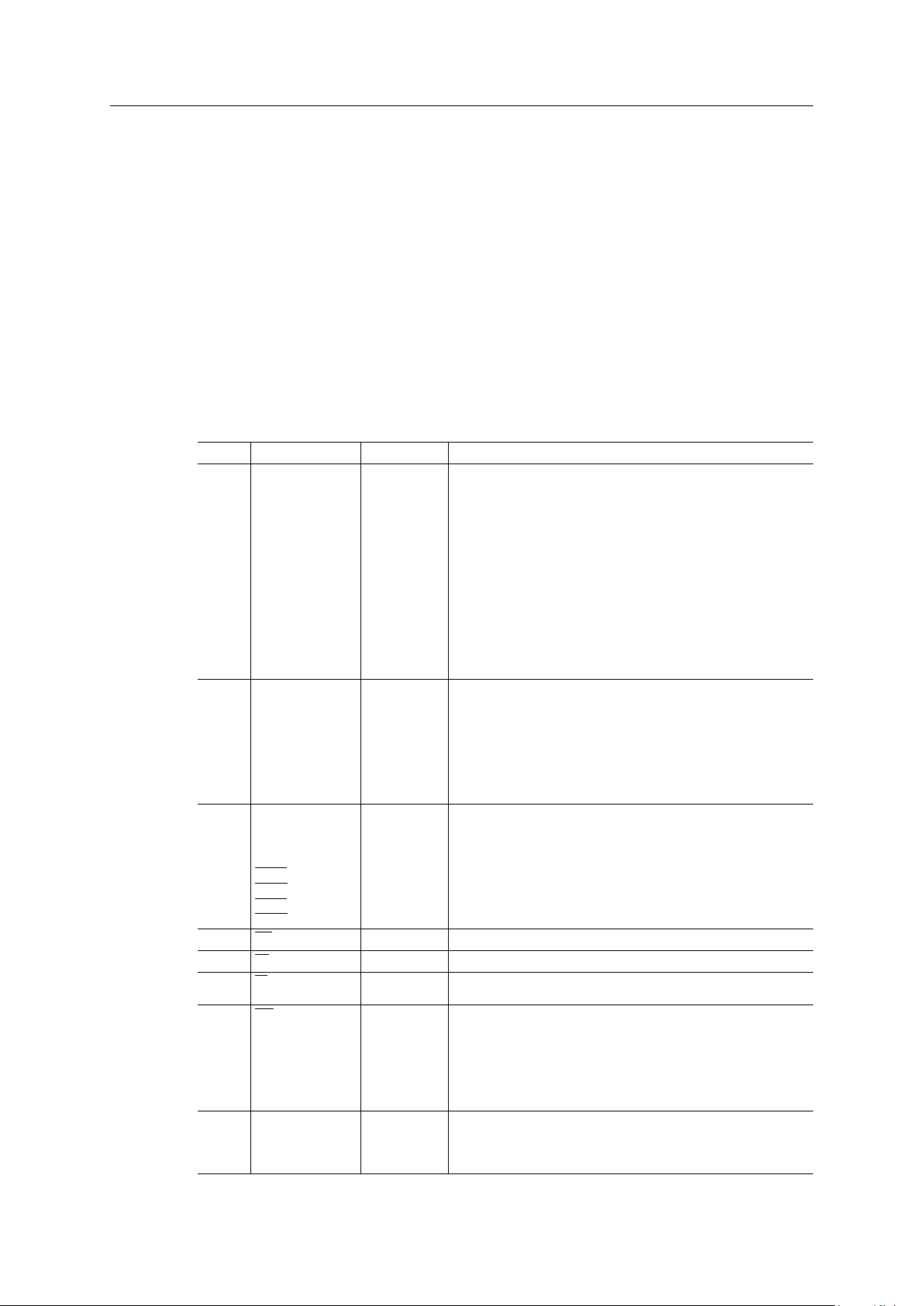

3 Host Interface

This chapter describes the low level properties of the Anybus CompactCom interface.

3.1 Overview

The Anybus CompactCom has five different host communication interfaces, corresponding to

different operating modes. The figure below illustrates the basic properties of these interfaces as

well as various I/O and control signals, and how they relate to the host application.

Fig. 1

Please note that only one communication interface at a time is available. Which one is decided

at startup.

3.1.1 Parallel Interface, 8-bit or 16-bit

From an external point of view, the parallel interface is a common 8-bit or 16-bit parallel slave

port interface, which can easily be incorporated into any microprocessor based system that has

3.1.2 SPI

Anybus®CompactCom B40-1 Design Guide

implementing an 8-bit or 16-bit wide SRAM. Additionally, the parallel interface features an

interrupt request line, allowing the host application to service the module only when actually

needed.

The Serial Peripheral Interface (SPI) is a synchronous serial link. It operates in full duplex mode

and devices communicate in master/slave mode where the Anybus CompactCom modules

always act as slaves. The interface can provide much higher performance than the serial

interface, but not as high as the parallel interface.

an external address/data bus. Generally, implementing this type of interface is comparable to

HMSI-27-230 3.4 en-US

Page 11

Host Interface 9 (78)

3.1.3 Stand-Alone Shift Register Interface

In this mode the Anybus CompactCom B40-1 operates stand-alone, with no host processor.

Process data is communicated to the shift registers on the host.

3.1.4 Serial Interface (UART)

The serial interface is provided for backward compatibility with the Anybus CompactCom 30. The

interface is event based, and has lower performance than the SPI and parallel modes. For more

information about the serial interface, see the Anybus CompactCom Hardware Design Guide for

the 30 series.

Please note that the Anybus CompactCom B40-1 is not backward compatible to the Anybus

CompactCom B30 hardware wise.

3.1.5 LED Interface

The status of the network LEDs is available as follows:

• As LED output signals on the network interface connector. These signals are able to drive a

LED directly and are available for all networks and operating modes. (Recommended)

• As LED output signals on the host interface connector for all operating modes except 16-bit

parallel mode. These signals are not able to drive a LED directly.

• In the LED status register for all modes, see Anybus CompactCom 40 Software Design guide

for more information.

3.1.6 Reduced Media-Independent Interface (RMII)

This interface is used for Transparent Ethernet, where Industrial Ethernet communication is

handled by the Anybus CompactCom and other Ethernet communication is routed to the host

application. 16–bit parallel mode and the LED Interface signals are not available in the host

application connector when Transparent Ethernet is enabled. The LED signals are still available

on the network connector of the Anybus CompactCom B40-1.

See RMII — Reduced Media-Independent Interface, p. 17 for mor information.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 12

Host Interface 10 (78)

Pin 1

Application

interface

Pin 1

Network

interface

Outline of brick

Top view

1

2

56

55

Top view

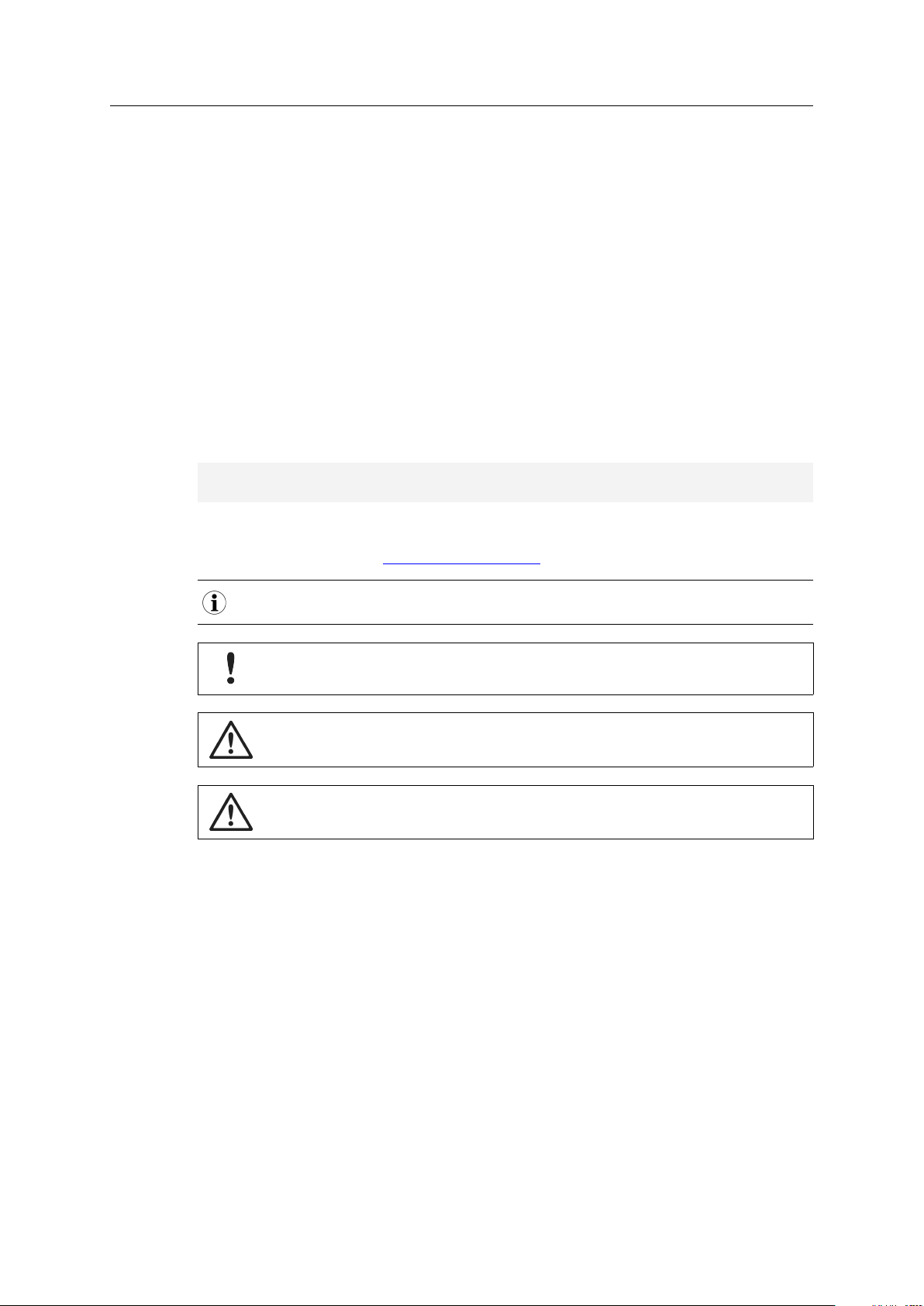

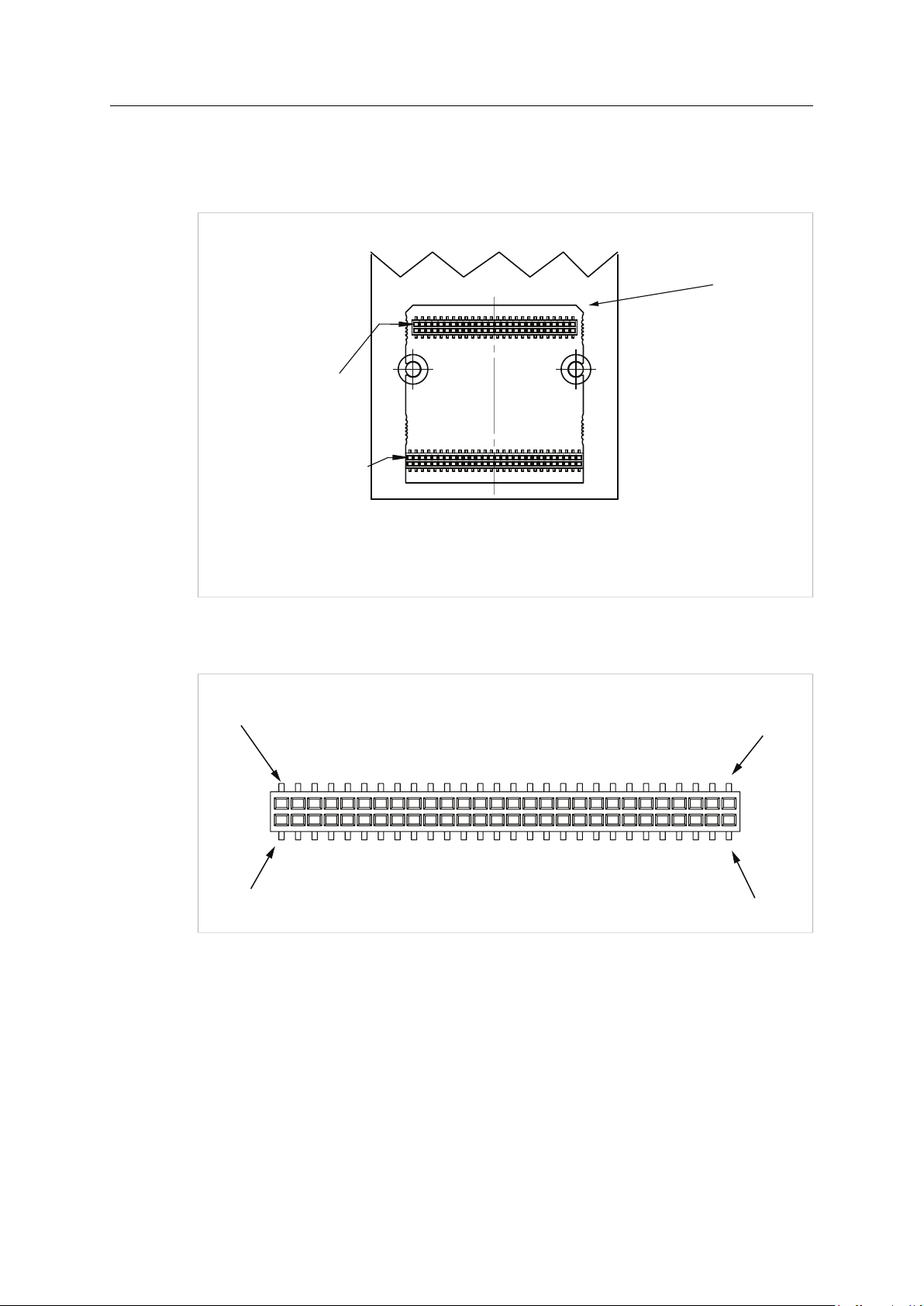

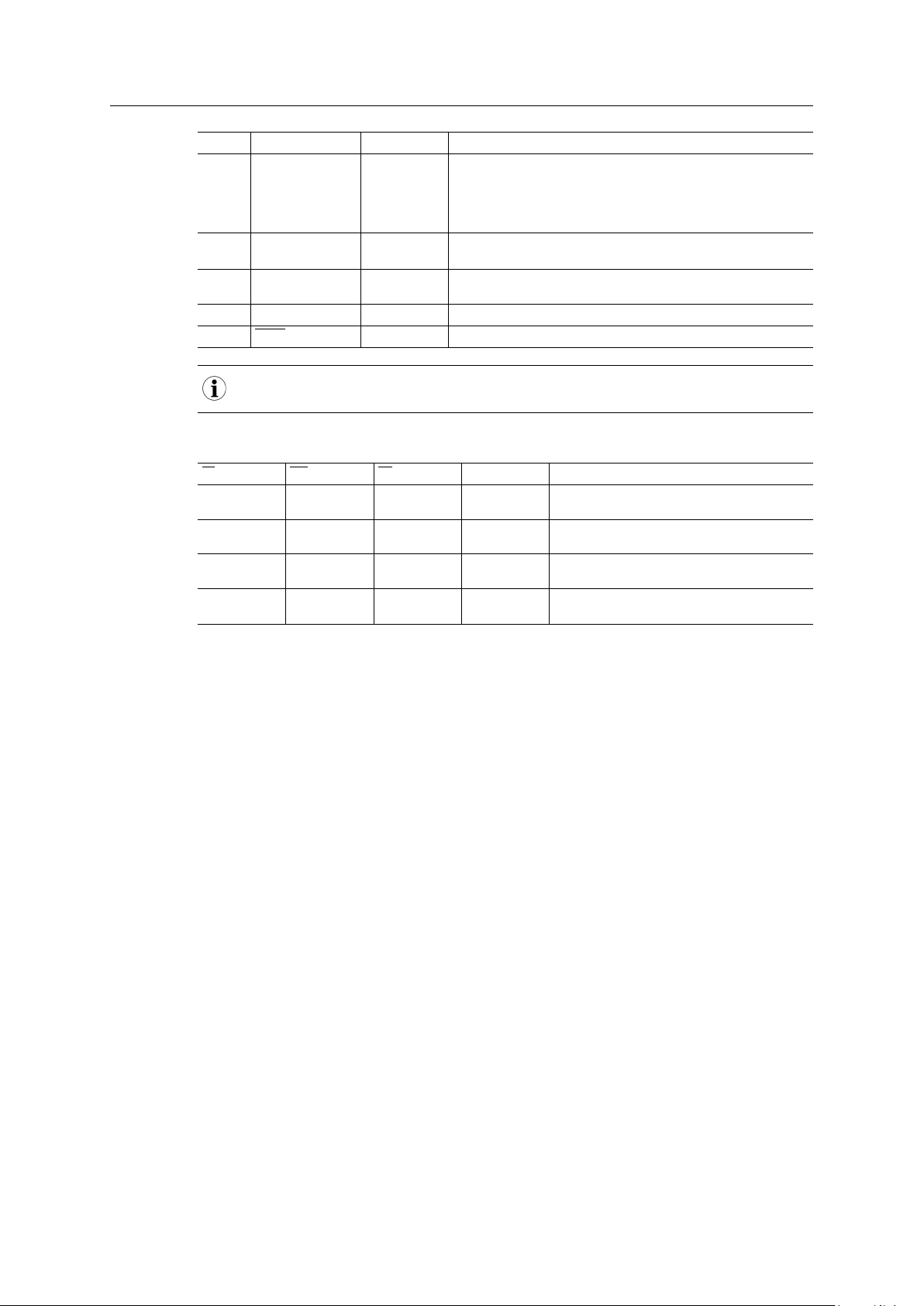

3.2 Host Application Connector

The host application connector provides an interface between the host application and the

Anybus CompactCom B40-1.

Fig. 2

The connector is implemented by a standard 1.27 mm 56 pin header surface mounted to the

bottom side of the PCB.

Fig. 3

The pictures shows the pinning of the mating connector on the host application seen from the

top.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 13

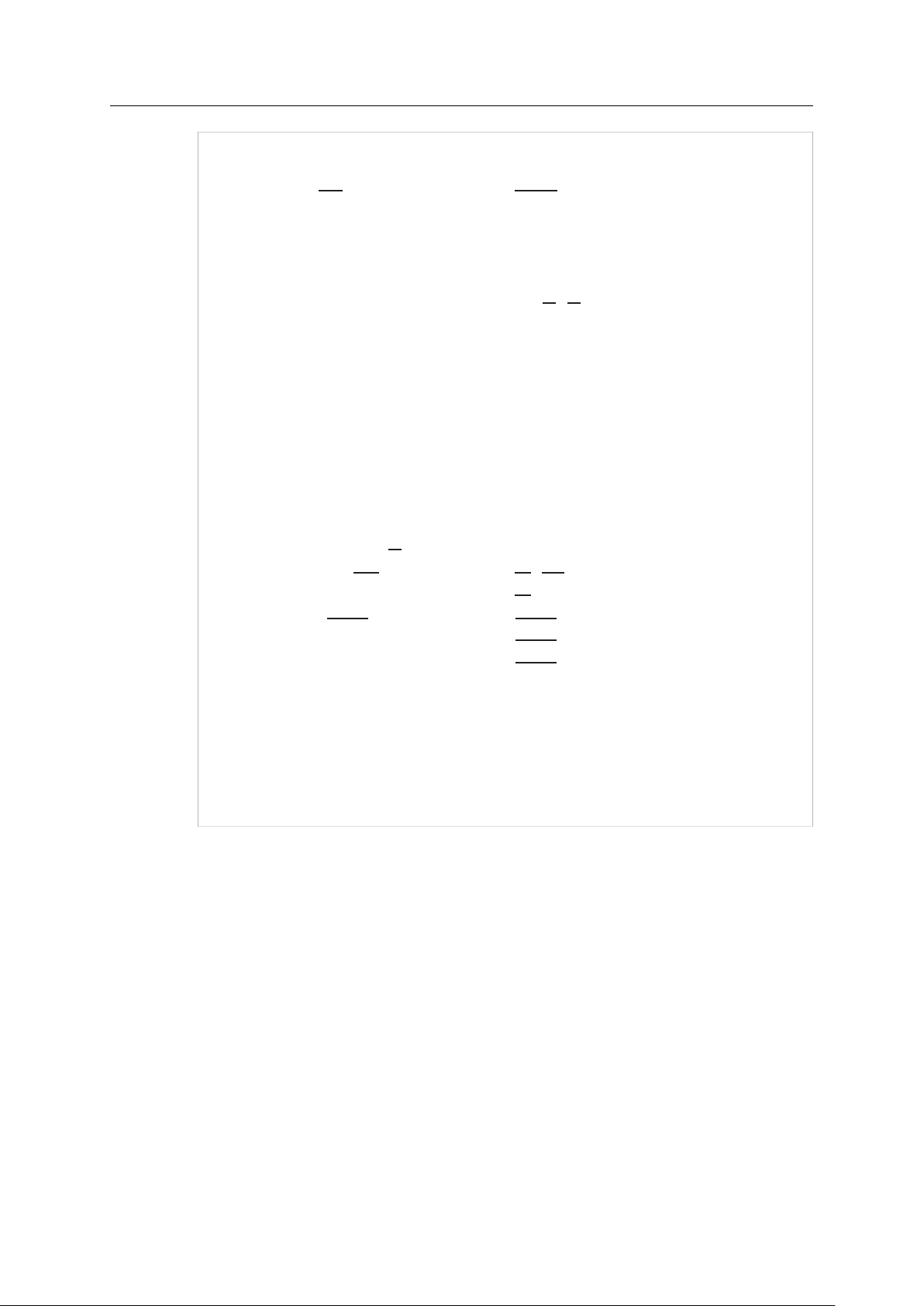

Host Interface 11 (78)

GND 2 1 3V3

A0/WEH/DIP1_0 4

3 RESET

A2/DIP1_2 6

5 A1/DIP1_1

GND 8

7 A3/DIP1_3

A5/DIP1_5 10

9 A4/DIP1_4

A7/DIP1_7 12

11 A6/DIP1_6

GND 14

13 A8/LD/SS

A10/DO/MISO 16

15 A9/SCLK

GND 18

17 A11/DI/MOSI

A13/ASI_TX 20

19 A12/ASI_RX

D6/DIP2_6 22

21 D7/DIP2_7

GND 24

23 D5/DIP2_5

D3/DIP2_3 26

25 D4/DIP2_4

GND 28

27 D2/DIP2_2

MD0 30

29 D1/DIP2_1

OM0 32

31 D0/DIP2_0

GND 34

33 OM1

CS 36

35 OM2

IRQ/PA 38

37 WE/WEL/CT

GND 40

39 OE

LED4B/D14 42

41 LED4A/D15

GND 44

43 LED3A/D13

LED2A/D11 46

45 LED3B/D12

LED1A/D9 48

47 LED2B/D10

GND 50

49 LED1B/D8

TX/ASI_TX/OM3 52

51 RX/ASI_RX

MI0/SYNC 54

53 MI1

GND 56

55 3V3

Anybus®CompactCom B40-1 Design Guide

Fig. 4

See Pin Overview, p. 12 for information on how each pin is used in the different modes.

HMSI-27-230 3.4 en-US

Page 14

Host Interface 12 (78)

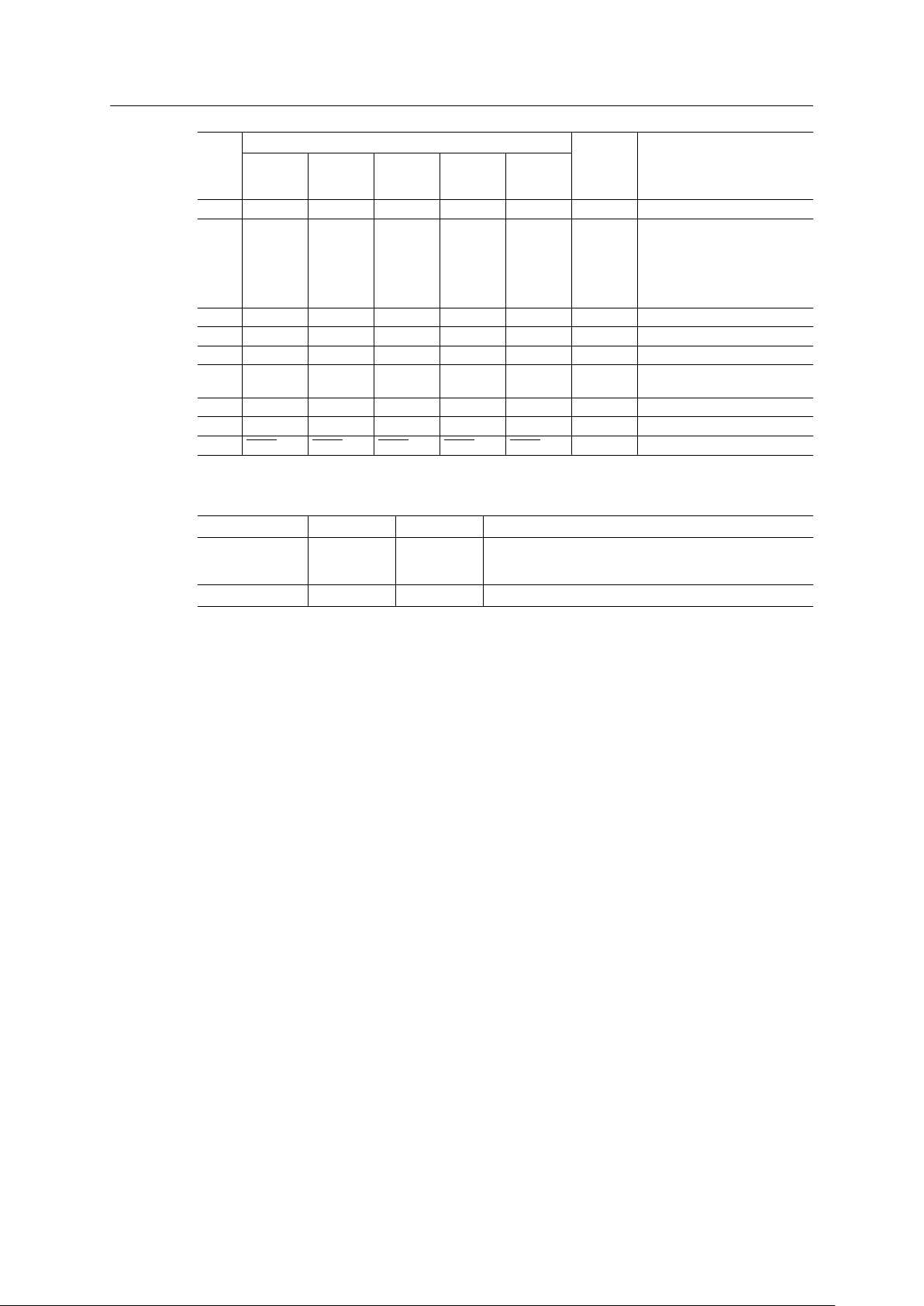

3.2.1 Pin Overview

Depending on operating mode, the pins have different names and different functionality.

Presented below is an overview of all pins except GND and 3V3.

The pin types of the connector are defined in PIN Types, p. 5. The pin type may be different

depending on which mode is used.

The ASI (Anybus Safety Interface) signals are used to connect a safety module to the safety interface of

an Anybus CompactCom 40-series module.

Note: The pin numbers of the Anybus CompactCom B40 (brick) host application

connector are different from those of the Anybus CompactCom M40 (module) host

application connector.

Pin Signal Name

Serial

Mode

4 DIP1_0 DIP1_0 A0 WEH DIP1_0 I

5 DIP1_1 DIP1_1 A1 A1 DIP1_1 I

6 DIP1_2 DIP1_2 A2 A2 DIP1_2 I

7 DIP1_3 DIP1_3 A3 A3 DIP1_3 I

9 DIP1_4 DIP1_4 A4 A4 DIP1_4 I

10 DIP1_5 DIP1_5 A5 A5 DIP1_5 I

11 DIP1_6 DIP1_6 A6 A6 DIP1_6 I

12 DIP1_7 DIP1_7 A7 A7 DIP1_7 I

13 SS A8 A8 LD

15 SCLK A9 A9 SCLK O, I

16 MISO A10 A10 DO O, I

17 MOSI A11 A11 DI I

19 ASI RX A12 A12 I

20 ASI TX A13 A13 O, I

31 DIP2_0 DIP2_0 D0 D0 DIP2_0

29 DIP2_1 DIP2_1 D1 D1 DIP2_1

27 DIP2_2 DIP2_2 D2 D2 DIP2_2

26 DIP2_3 DIP2_3 D3 D3 DIP2_3

25 DIP2_4 DIP2_4 D4 D4 DIP2_4

23 DIP2_5 DIP2_5 D5 D5 DIP2_5

22 DIP2_6 DIP2_6 D6 D6 DIP2_6

21 DIP2_7 DIP2_7 D7 D7 DIP2_7

49 LED1B LED1B LED1B D8 LED1B

48 LED1A LED1A LED1A D9 LED1A

47 LED2B LED2B LED2B D10 LED2B

46 LED2A LED2A LED2A D11 LED2A

45 LED3B LED3B LED3B D12 LED3B

43 LED3A LED3A LED3A D13 LED3A

42 LED4B LED4B LED4B D14 LED4B

41 LED4A LED4A LED4A D15 LED4A

37 WE WEL CT I

39 OE OE I

36 CS CS I

38 IRQ IRQ IRQ PA O

SPI Mode 8-bit

Mode

16-bit

Mode

Shift

Register

Mode

Type Notes

I/O

I, I/O

I, I/O

I, I/O

I, I/O

I, I/O

I, I/O

I, I/O

I, I/O

O, I/O

O, I/O

O, I/O

O, I/O

OD, I/O

OD, I/O

O, I/O

O, I/O

In modules supporting RMII,

these pins are used for the RMII

interface when this has been

activated, see RMII — Reduced

Media-Independent Interface, p.

17.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 15

Host Interface 13 (78)

Pin Signal Name

Serial

Mode

51 RX ASI RX ASI RX ASI RX ASI RX I

52

TX / OM3 ASI TX /

32 OM0 OM0 OM0 OM0 OM0 I

33 OM1 OM1 OM1 OM1 OM1 I

35 OM2 OM2 OM2 OM2 OM2 I

54 MI0

53 MI1 MI1 MI1 MI1 MI1 O

30 MD0 MD0 MD0 MD0 MD0 O

3 RESET RESET RESET RESET RESET I

SPI Mode 8-bit

OM3

MI0/SYNC MI0/SYNC MI0/SYNC MI0/SYNC

3.2.2 Power Supply Pins

Signal

GND Power 2, 8, 14, 18, 24,

3V3 Power 1, 55

Type

Mode

ASI TX /

OM3

16-bit

Mode

ASI TX /

OM3

Pin Description

28, 34, 40, 44,

50, 56

Ground

Power and signal ground reference.

3.3 V power supply.

Shift

Register

Mode

ASI TX /

OM3

Type Notes

I/O

O

Strapping input with internal

weak pull-up during powerup.

To configure OM3, use an

external pull-up/pull-down of

1.0 to 2.2 kΩ. The pin changes to

output after powerup

Low at power-up and before

reset release.

Tied to 3V

Tied to GND

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 16

Host Interface 14 (78)

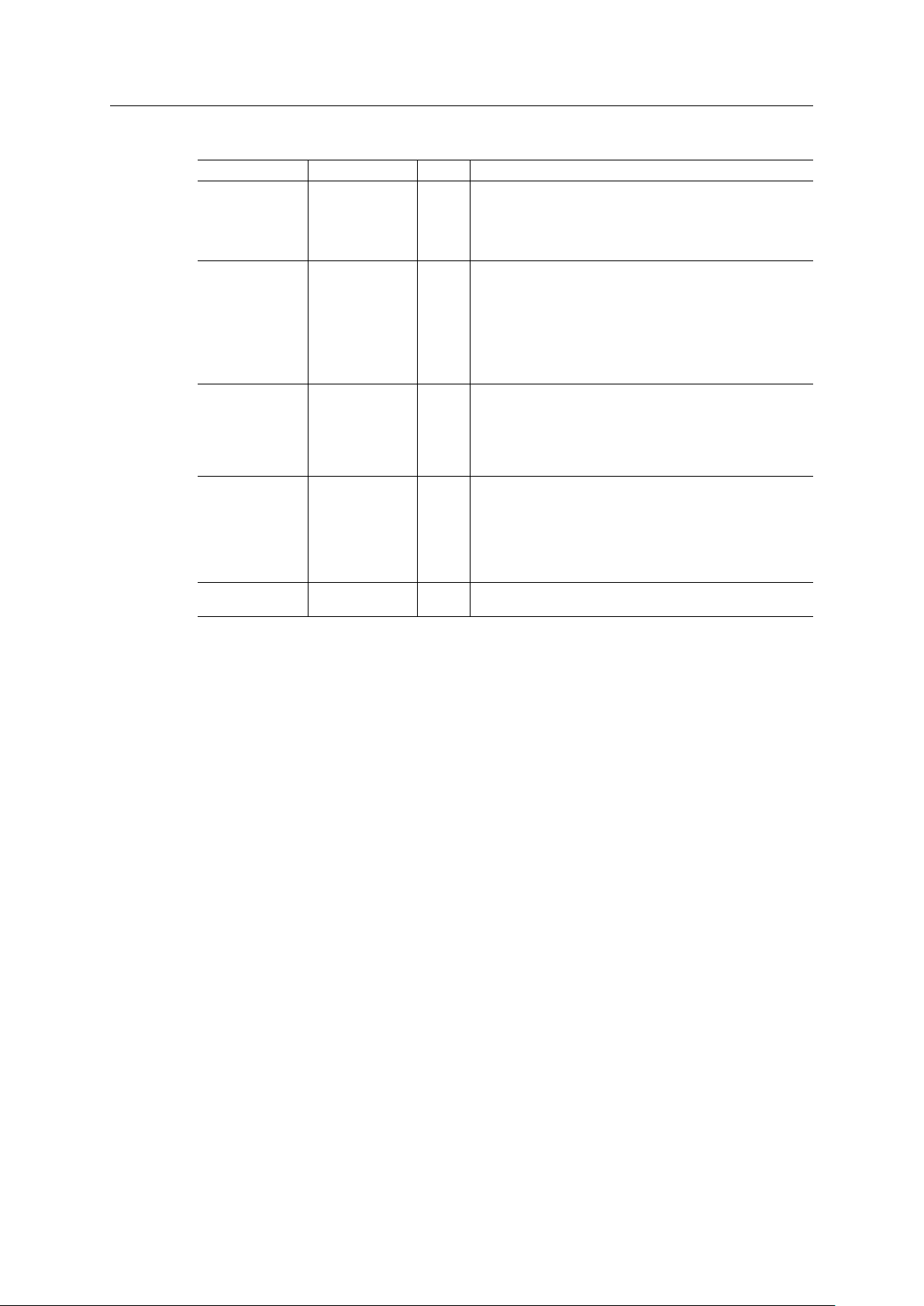

3.2.3 LED Interface / D8–D15 (Data Bus)

Signal Name

LED1A / D9 O / I/O

LED1B / D8 O / I/O

LED2A / D11 O / I/O

LED2B / D10 O / I/O

LED3A / D13 OD / I/O

LED3B / D12 OD / I/O

LED4A / D15 O / I/O

LED4B / D14 O / I/O

Pin Type Pin

48

49

46

47

43

45

41

42

Description, LED Interface

LED 1 Indication A

• Green

LED 1 Indication B

• Red

LED 2 Indication A

• Green

LED 2 Indication B

• Red

LED 3 Indication A

• Green

• Mainly used for link/

activity on network port 1

on the Ethernet modules.

Pin is open-drain to maintain

backward compatibility with

existing applications, where this

pin may be tied to GND.

LED 3 Indication B

• Yellow or red, depending

on network

• Mainly used for link/

activity on network port 1

on the Ethernet modules

(yellow).

Pin is open-drain to maintain

backward compatibility with

existing applications, where this

pin may be tied to GND.

LED 4 Indication A

• Green

• Mainly used for link/

activity on network port 2

on the Ethernet modules.

LED 4 Indication B

• Yellow or red, depending

on network

• Mainly used for link/

activity on network port 2

on the Ethernet modules

(yellow)

Description, Data Bus

D9 Data Bus

• "D9" in 16-bit parallel

mode.

D8 Data Bus

• "D8" in 16-bit parallel

mode.

D11 Data Bus

• "D11" in 16-bit parallel

mode.

D10 Data Bus

• "D10" in 16-bit parallel

mode.

D13 Data Bus

• "D13" in 16-bit parallel

mode.

D12 Data Bus

• "D12" in 16-bit parallel

mode.

D15 Data Bus

• "D15" in 16-bit parallel

mode.

D14 Data Bus

• "D14" in 16-bit parallel

mode.

The LED signals are also available on the network connector as active high push/pull signals. Those

signals are easier to use for LEDs.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 17

Host Interface 15 (78)

3.2.4 Settings / Sync

Signal Name

OM0

OM1

OM2

OM3 (ASI TX) (TX)

MI0 / SYNC

MI1

MD0 O 30

ASI RX

ASI TX

RX

TX

Type

I

I

I

I (Used as OM3

during power up)

O

O

I

O

I

O

Pin Description

32

33

35

52

54

53

51

52

UART

operation:

19

20

51

52

Operating Mode

Used to select interface and baud rate, see below.

Module Identification

MI0 and MI1 can be used by the host application to determine

what type of Anybus CompactCom that is connected.

SYNC

On networks that support synchronous communication, a

periodic synchronization pulse is provided on the SYNC output.

The SYNC pulse is also available as a maskable interrupt using the

IRQ signal.

Module Detection

This signal can be used by the host application to determine that

an Anybus CompactCom is inserted into the slot, see Module

Detection, p. 16.

The signal is connected directly to GND on the Anybus

CompactCom.

Black Channel Communication

These signals can be connected to a safety module, e.g. to IXXAT

Safe T100 to provide a safe channel for black channel

communication

If not used, pin 51 (for UART operation pin 19) should be pulled

to 3V3.

Serial Communications Signals

®

Anybus

CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 18

Host Interface 16 (78)

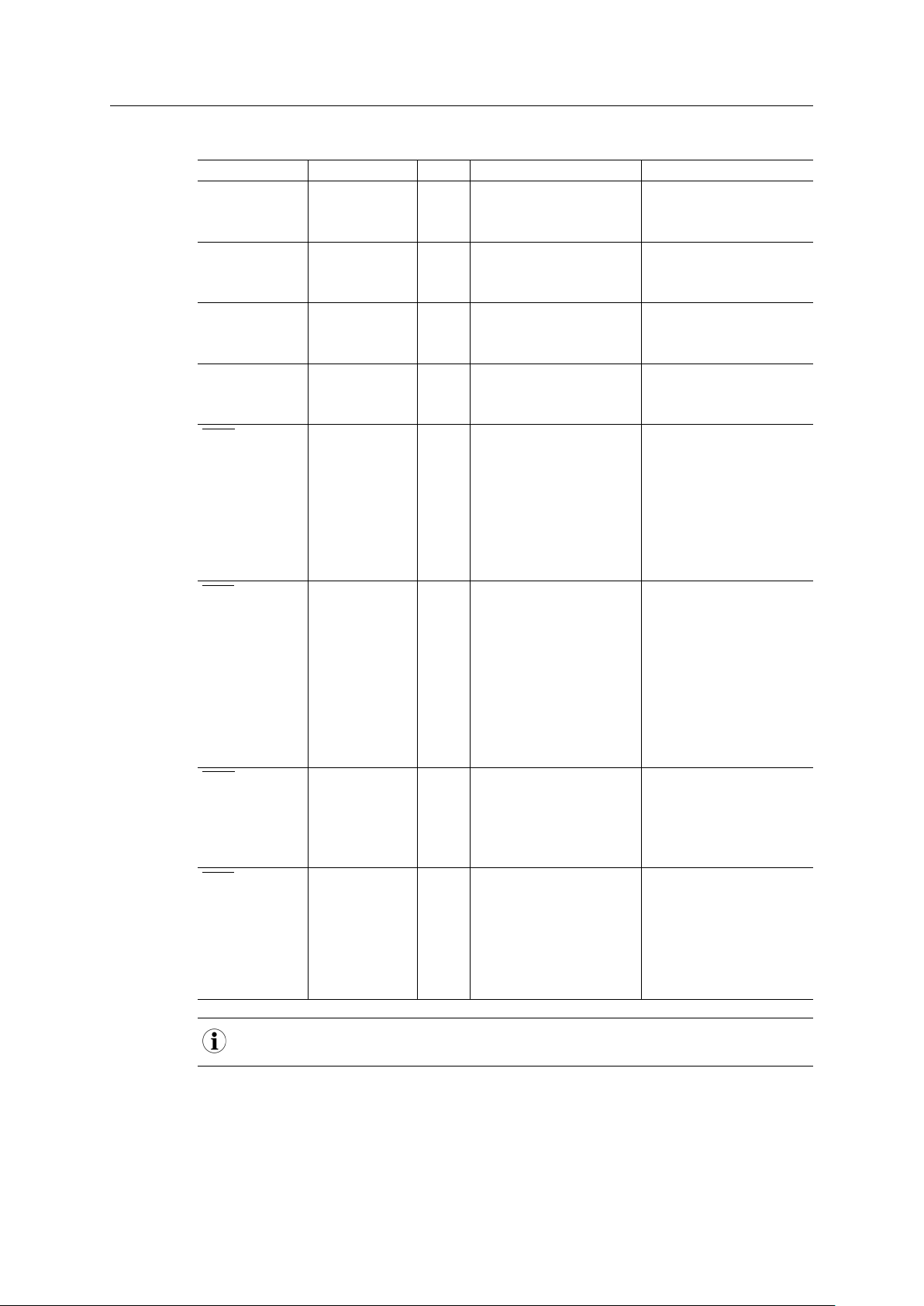

Operating Modes

These inputs select the interface that should be used to exchange data (SPI, stand-alone shift

register, parallel or serial) and, if the serial interface option is used, the operating baud rate. The

state of these signals is sampled once during startup, i.e. any changes require a reset in order to

have effect.

OM3 OM2 OM1 OM0

LOW LOW LOW LOW

LOW LOW LOW HIGH SPI

LOW LOW HIGH LOW

LOW LOW HIGH HIGH

LOW HIGH LOW LOW

LOW HIGH LOW HIGH

LOW HIGH HIGH LOW

LOW HIGH HIGH HIGH

HIGH LOW LOW LOW

HIGH LOW LOW HIGH

HIGH LOW HIGH LOW

HIGH LOW HIGH HIGH

HIGH HIGH LOW LOW

HIGH HIGH LOW HIGH

HIGH HIGH HIGH LOW

HIGH HIGH HIGH HIGH

LOW = V

HIGH = V

IL

IH

These signals must be stable prior to releasing the RESET signal. Failure to observe this may result in

faulty behavior.

Operating Mode

Reserved

Stand-alone shift register

Reserved

Reserved

Reserved

Reserved

16-bit parallel

8-bit parallel

Serial 19.2 kbps

Serial 57.6 kbps

Serial 115.2 kbps

Serial 625 kbps

Reserved

Reserved

Service Mode

Module Detection

This signal is internally connected to GND, and can be used by the host application to detect

whether a module is present or not. When connecting an external pull-up resistor, a low signal

indicates that a module is present.

If not used, leave this signal unconnected.

Module Identification

These signals indicate which type of module that is connected. It is recommended to check the

state of these signals before accessing the module.

MI1 MI0

LOW LOW

LOW HIGH

HIGH LOW

HIGH HIGH

LOW = V

HIGH = V

OL

OH

On modules supporting “SYNC”, MI0 is used as a SYNC signal during operation. MI0 should only be

sampled by the application during the time period from power up to the end of SETUP state.

Module Type

Active Anybus CompactCom 30

Passive Anybus CompactCom

Active Anybus CompactCom 40

Customer specific

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 19

Host Interface 17 (78)

3.2.5 RMII — Reduced Media-Independent Interface

In RMII enabled modules, the pins described in the table below are used for the RMII

communication. They are set to tristate during startup, making it impossilbe to indicate e.g.

exception during setup. When setup is complete, they are set to inputs/outputs according to the

selected mode. See Anybus CompactCom 40 Software Design Guide for more information on

mode selection.

The 16-bit parallel mode can not be used when RMII is enabled

LED status will not be available when RMII is enabled.

Pin Signal Name

49 RXD0 O

48 RXD1 O

47 RXDV O

46 I

45 TXD0 I

43 TXD1 I

42 TXEN I

41 CLK I

Type Notes

3.2.6 IRQ (Interrupt Request)

Signal Name Pin Type Pin Description

IRQ O 38 Interrupt Request

The use of this signal is optional but highly recommended. Even if the host application lacks

interrupt capabilities, it is recommended to connect this signal to an input port to simplify

software design.

This signal must be pulled to 3V3 on the host application side to prevent spurious interrupts

during startup.

-

-

-

Not used (connect to external pull-down)

-

-

-

-

Active low interrupt signal.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 20

Host Interface 18 (78)

Power

/RESET

0V

3.3V

Power

On

Power

Stable

t

B

t

A

V

IL

V

IH

t

t

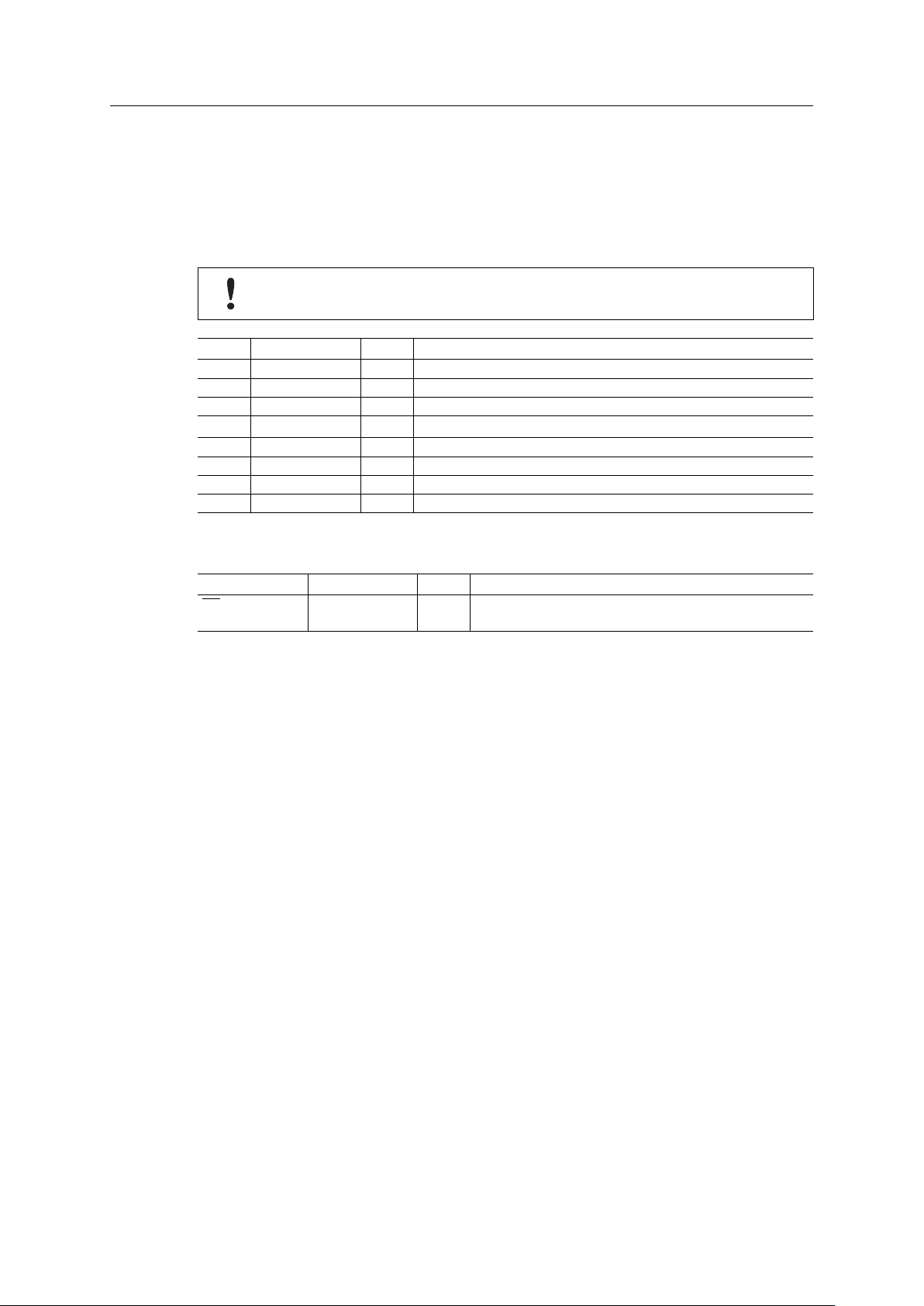

3.2.7 RESET (Reset Input)

Signal Name

Pin Type Pin Description

RESET I 3 Reset

Used to reset the module.

The master reset input is active low. It must be connected to a host application controllable

output pin in order to handle the power up sequence, voltage deviations and to be able to

support network reset requests. If the brick is used in stand-alone mode, with no host processor,

a separate reset circuit can be used, see Reset Circuit Example, p. 36.

The brick does not feature any internal reset regulation. To establish a reliable interface, the host

application is solely responsible for resetting the module when the supply voltage is outside the

specified range.

Power Up

Fig. 5

Powerup time limits are given in the table below:

Symbol Min.

t

A

t

B

- -

1 ms

Max.

-

Definition

Time until the power supply is stable after power-on; the duration depends

on the power supply design of the host application and is thus beyond the

scope of this document.

Safety margin.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 21

Host Interface 19 (78)

RESET

t

C

V

IL

V

IH

t

Restart

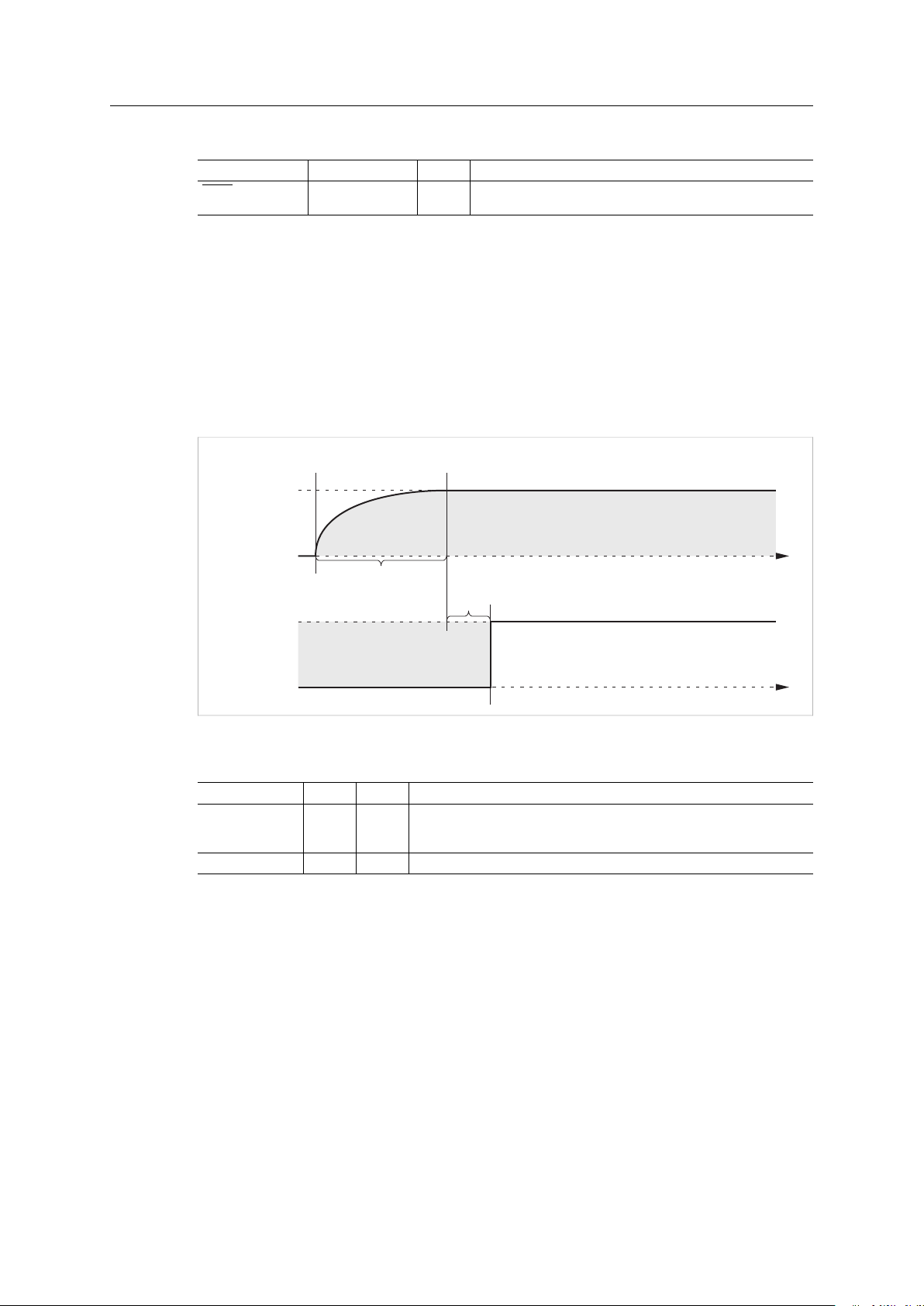

The reset pulse duration must be at least 10 µs in order for the NP40 to properly recognize a

reset.

Fig. 6

Symbol Min.

t

C

10 µs

Max.

-

Definition

Reset pulse width.

®

Anybus

CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 22

Host Interface 20 (78)

3.3 Parallel Interface Operation

3.3.1 General Description

The parallel interface is based on an internal memory architecture, that allows the Anybus

CompactCom module to be interfaced directly as a memory mapped peripheral. The M40

modules can be configured for 8-bit or 16-bit parallel operation. The access time is 30 ns.

Polled operation is possible, but at the cost of an overhead. For increased efficiency, an optional

interrupt request signal (IRQ) can relieve the host application from polling for new information,

thus increasing the performance.

The parallel interface must be enabled using OM[0...3].

3.3.2 Pin Usage in 8-bit Parallel Mode

The parallel 8-bit interface uses the following signals:

Pin Signal Name Pin Type

4

5

6

7

9

10

11

12

13

15

16

17

19

20

31

29

27

26

25

23

22

21

49

48

47

46

45

43

42

41

37 WE I

39 OE I

36 CS I

38 IRQ O

32

33

35

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

D0

D1

D2

D3

D4

D5

D6

D7

LED1B

LED1A

LED2B

LED2A

LED3B

LED3A

LED4B

LED4A

OM0

OM1

OM2

I

I/O

O

O

O

O

OD

OD

O

O

I

Description/Comments

A[0...3]: Mandatory address input signals.

Standard bidirectional data bus.

8-bit mode: LED functionality, see LED Interface, p. 9.

Active low write signal or combined read/write signal.

Bus output enable; enables output on the data bus when low.

Bus chip select enable; enables parallel access to the module when

low.

Active low Interrupt Request signal. Asserted by the Anybus

CompactCom module.

The use of this signal is optional but highly recommended. Even if the

host application lacks interrupt capabilities, it is recommended to

connect this signal to an input port to simplify software design.

This signal must be pulled to 3V3 on the host application side to

prevent spurious interrupts during startup.

Operating mode. Connect all three to GND for 8-bit parallel operating

mode.

For more information see Operating Modes, p. 16.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 23

Host Interface 21 (78)

Pin Signal Name Pin Type

52

51 ASI RX I

54

53

30 MD0 O

3 RESET I

OM3 / ASI TX

MI0/SYNC

MI1

O, I

O

Description/Comments

Black channel output.

See Black Channel/Safety Interface, p. 51.

During startup the pin (with OM[0..2]) is used to define the operating

mode of the module. Connect to external pull-up for 8-bit parallel

operating mode, see Pin Overview, p. 12.

Black channel input. Tie to 3V3 if not used.

See Black Channel/Safety Interface, p. 51

See Module Identification, p. 16

See Module Detection, p. 16

See RESET (Reset Input), p. 18.

There are no internal pull-up resistors on any of the signals above, except for OM3, which has an internal

weak pull-up.

Function Table (CS, WE, OE, D[0...7])

CS WE OE

HIGH X X

LOW LOW X Data Input

LOW HIGH LOW Data Output

LOW HIGH HIGH

D[0...7] State

High

impedance

(Write)

(Read)

High

impedance

Comment

Module not selected.

Data on D[0...7] is written to location selected by

address bus.

Data from location selected by address bus is

available on D[0...7].

Module is selected, but D[0...7] is in a high

impedance state.

X = don’t care

LOW = V

HIGH = V

IL

IH

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 24

Host Interface 22 (78)

3.3.3 Pin Usage in 16-bit Parallel Mode

The parallel 16-bit interface uses the following signals:

Pin Signal Name Pin Type

5

6

7

9

10

11

12

13

15

16

17

19

20

31

29

27

26

25

23

22

21

49

48

47

46

45

43

42

41

4 WEH I

37 WEL I

39 OE I

36 CS I

38 IRQ O

32

33

35

54

53

52

51 ASI RX I

30 MD0 O

3 RESET I

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

OM0

OM1

OM2

MI0/SYNC

MI1

OM3 / ASI TX

I

I/O

I

O

O, Strap

Description/Comments

A[1...13]: Mandatory address input signals.

Selects source/target location.

Standard bidirectional data bus.

Write enable high byte.

Write enable low byte.

Bus output enable; enables output on the data bus when low.

Bus chip select enable; enables parallel access to the module when

low.

Active low Interrupt Request signal. Asserted by the Anybus

CompactCom module.

The use of this signal is optional but highly recommended. Even if the

host application lacks interrupt capabilities, it is recommended to

connect this signal to an input port to simplify software design.

This signal must be pulled to 3V3 on the host application side to

prevent spurious interrupts during startup.

Operating mode. Connect all three to 3V3 for 16-bit parallel operating

mode.

For more information see Operating Modes, p. 16

See Module Identification, p. 16

Black channel output.

See Black Channel/Safety Interface, p. 51

During startup the pin (with OM[0..2]) is used to define the operating

mode of the module. Connect to pull-down for 16-bit parallel

operating mode, see Pin Overview, p. 12.

Black channel input. Connect to 3V3 if not used.

See Black Channel/Safety Interface, p. 51

See Module Detection, p. 16.

See RESET (Reset Input), p. 18

The A0 signal is not needed in 16-bit parallel operating mode, as 16 bits are addressed instead of

8 bits. If there is need for writing one byte at the time signals WEH and WEL can be used to

enable writing to the high or low byte respectively. If both are enabled both bytes are written.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 25

Host Interface 23 (78)

Function Table (CS, WEL, WEH, OE, D[0...15])

CS WEL WEH OE

HIGH X X X

LOW LOW HIGH X

LOW HIGH LOW X

LOW LOW LOW X

LOW HIGH HIGH LOW

LOW HIGH HIGH HIGH

D[0...15] State

High impedance Module not selected.

Data Input (Write) Data on D[0...7] is written to low byte of

Data Input (Write) Data on D[8...15] is written to high byte

Data Input (Write) Data on D[0 ...15] is written to location

Data Output (Read) Data from location selected by address

High impedance Module is selected, but D[0...15] is in a

Comment

location selected by address bus.

of location selected by address bus.

selected by address bus.

bus is available on D[0...15].

high impedance state.

X = don’t care

LOW = V

HIGH = V

IL

IH

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 26

Host Interface 24 (78)

Address

CS

OE

Data

Data valid

Data valid

tAA tAA

tACS

tAR

tHZ

tHZ

Address valid

Address valid

tDH

tRC

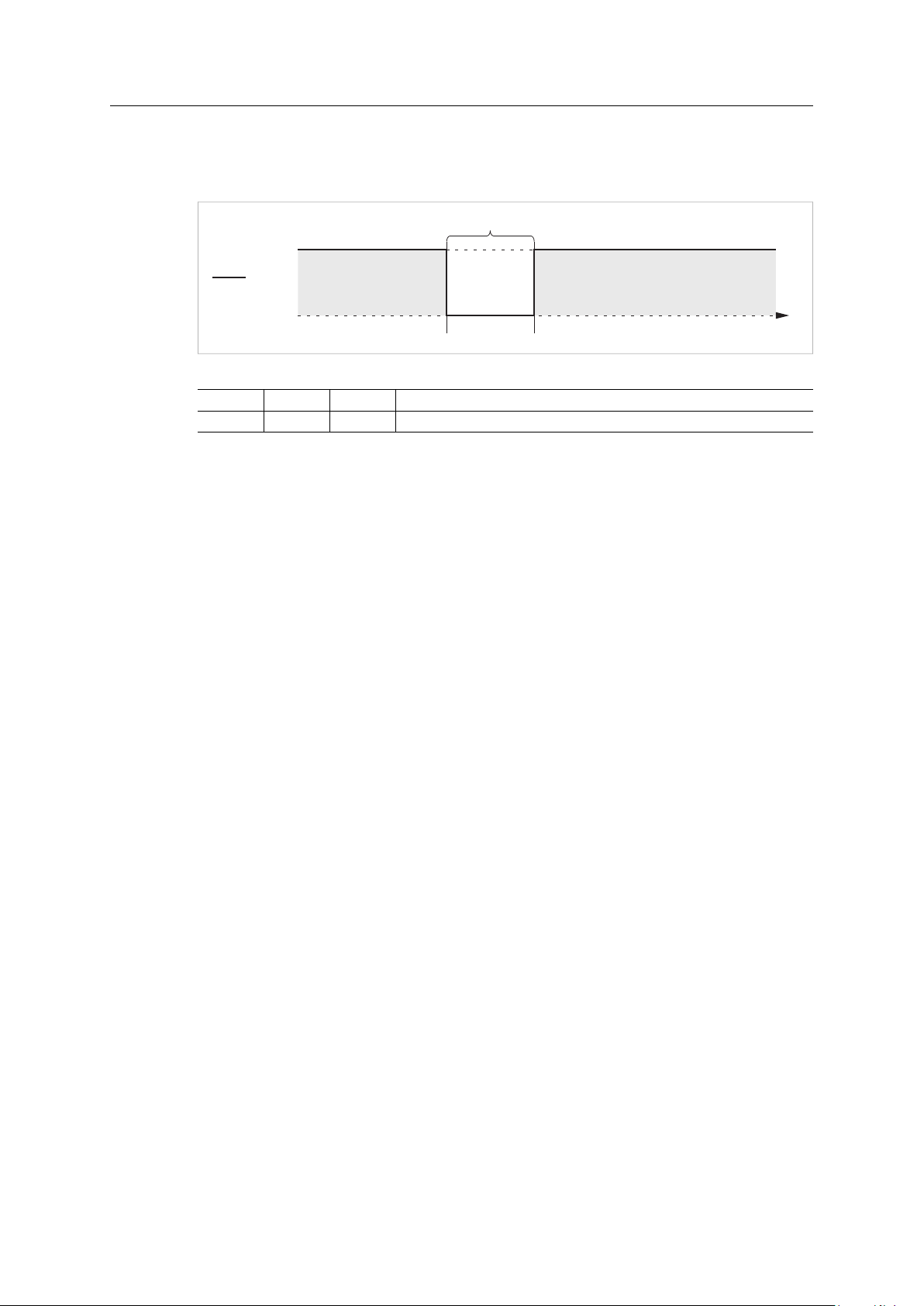

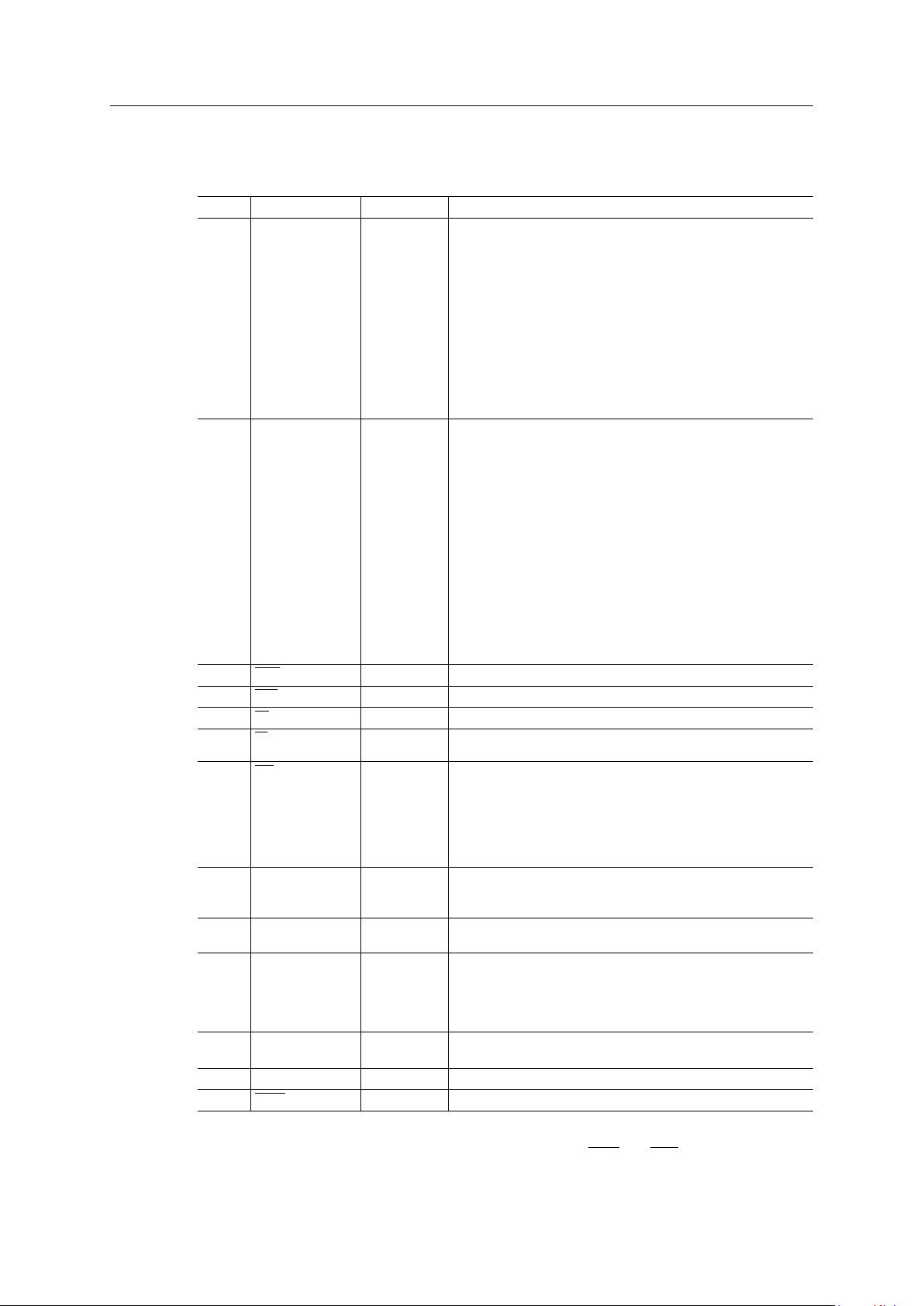

3.3.4 Memory Access Read Timing

The WE input signal must remain high during a read access. The timing diagram shows a burst

read, but the timing applies for a single read as well. The Anybus CompactCom B40-1 has no

setup or hold timing requirements on the address bus relative to CS during read operations. The

only limitation on read setup and hold times is that the pingpong and powerup interrupt will be

acknowledged if all address lines are high for 10-15 ns or more while CS is low.

Fig. 7

Symbol

tRC

tAA

tACS

tAR

tHZ

tDH

Parameter

Read cycle time

Address valid to Data valid

CS low to Data valid

OE low to Data valid

CS or OE high to output reached tristate

Data hold time

Min (ns) Max (ns)

30

-

-

-

-

0

-

30

30

15

15

-

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 27

Host Interface 25 (78)

Address

CS

WE

Data

Data valid

Data valid

tAS tAH

tWP

Address valid

Address valid

tDHtDS

tWR

tAS tAH

tWP

tDHtDS

tWC

tWR

Address valid

Address

CS

WE

Data

Data valid

Data valid

tAS tAH

tWP

Address valid

Address valid

tDHtDS

tWR

tAS tAH

tWP

tDHtDS

tWC

tWR

Address valid

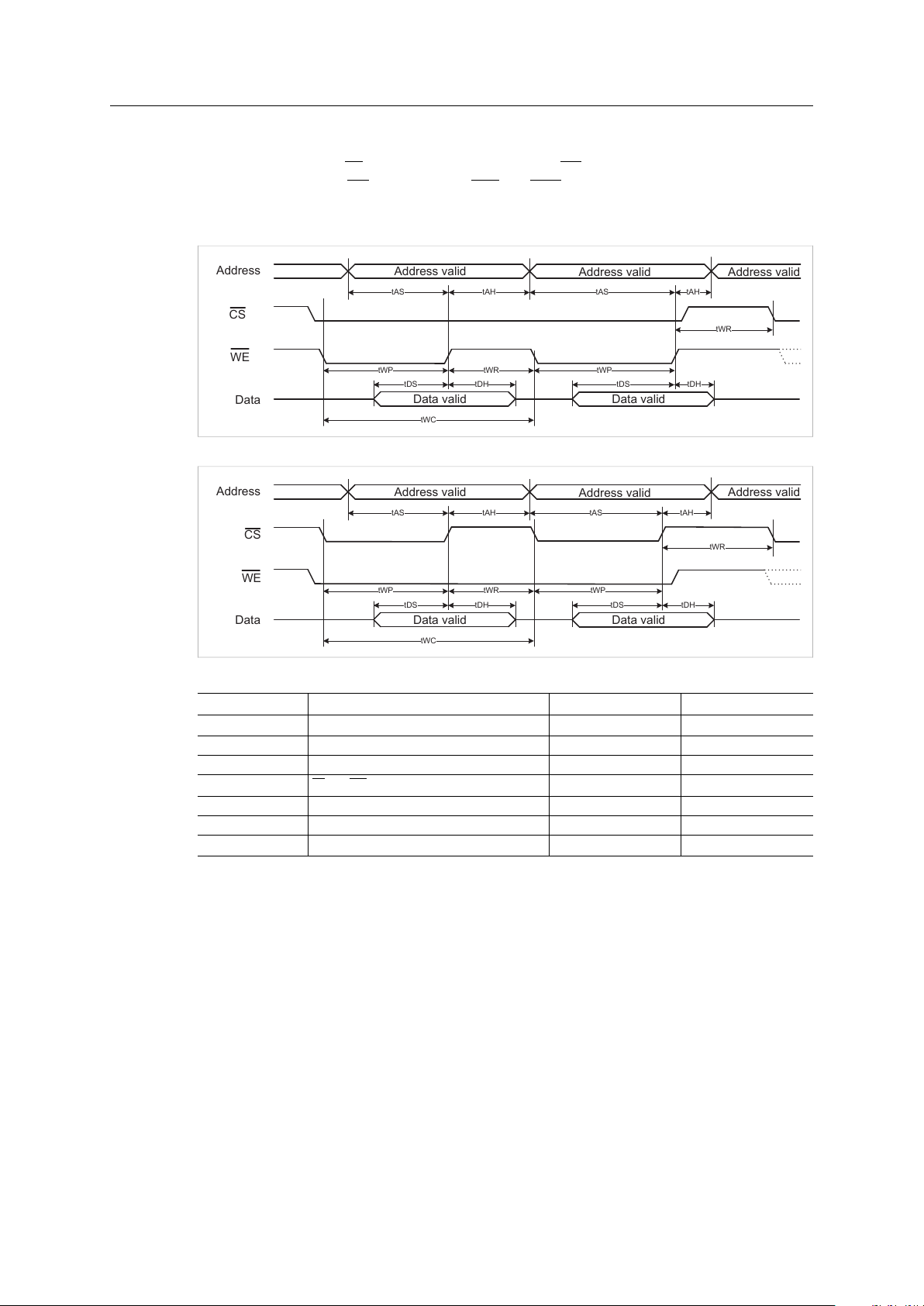

3.3.5 Memory Access Write Timing

It doesn’t matter if the OE signal is low or high as long as WE is active (low). In 16 bit mode, the

timing requirements of WE applies to both WEL and WEH. The timing diagrams show a burst

write but the timing applies for a single write as well. The first diagram shows write enable

controlled write timing and the second shows chip select controlled write timing.

Fig. 8

Fig. 9

Symbol

tWC

tAS

tAH

tWP

tDS

tDH

Parameter

Write cycle time

Address valid before End-of-Write

Address valid after End-of-Write

CS and WE low pulse width

Data valid before End-of-Write

Data valid after End-of-Write

tWR Write recovery time 10

Min (ns) Max (ns)

30

15

0

15

15

0

-

-

-

-

-

-

-

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 28

Host Interface 26 (78)

3.4 SPI Operation

3.4.1 General Description

The SPI (Serial Peripheral Interface) bus is a synchronous serial data link standard which operates

in full duplex mode.

The SPI interface is activated using the OM[0...3] inputs. See Operating Modes, p. 16.

3.4.2 Pin Usage in SPI Mode

Presented below is an overview of all pins except GND and 3V3.

Pin Signal Name

4

5

6

7

9

10

11

12

13 SS I

15 SCLK I

16 MISO O

17 MOSI I

19

20

31

29

27

26

25

23

22

21

49

48

47

46

45

43

42

41

37

39

36

38 IRQ O

32

33

35

52

DIP1_0

DIP1_1

DIP1_2

DIP1_3

DIP1_4

DIP1_5

DIP1_6

DIP1_7

(not used)

DIP2_0

DIP2_1

DIP2_2

DIP2_3

DIP2_4

DIP2_5

DIP2_6

DIP2_7

LED1B

LED1A

LED2B

LED2A

LED3B

LED3A

LED4B

LED4A

(not used)

OM0

OM1

OM2

OM3 / ASI TX

Type

I

I

I

I

I

I

I

I

I

O, I

I

I

I

I

I

I

I

I

O

O

O

O

OD

OD

O

O

I Tie to 3V3.

I

O, Strap

Description/Comments

DIP switch. Usage defined by application.

Readable through attribute #14 (Switch status) in Anybus Object,

instance #1.

Tie to GND if not used.

Slave select. Active low.

Serial Clock Input

Master input, slave output. Input to the master’s shift register, and

output from the slave’s shift register.

Master output, slave input. Output from the master’s shift register,

and input to the slave’s shift register.

Tie to 3V3.

DIP switch. Usage defined by application.

Readable through attribute #14 (Switch status) in Anybus Object,

instance #1.

Tie to GND if not used.

LED interface. Gives access to LED indications. For more information,

see LED Interface / D8–D15 (Data Bus), p. 14".

Active low Interrupt Request signal. Asserted by the Anybus

CompactCom module.

The use of this signal is optional but highly recommended. Even if the

host application lacks interrupt capabilities, it is recommended to

connect this signal to an input port to improve the startup time.

This signal must be pulled to 3V3 on the host application side to

prevent spurious interrupts during startup.

Operating mode [OM2, OM1, OM0]: 0,0,1 for SPI operating mode.

For more information see Operating Modes, p. 16

Black channel output. See Black Channel/Safety Interface, p. 51

During startup the pin (with OM[0..2]) is used to define the operating

mode of the module. Connect to external pull-down for SPI operating

mode,see Pin Overview, p. 12.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 29

Host Interface 27 (78)

Pin Signal Name

51 ASI RX I

54

53

30 MD O

3 RESET I

MI0/SYNC

MI1

3.4.3 SPI Interface Signals

The SPI interface option uses three (optionally four) signals:

Signal

SCLK

MOSI

MISO

SS

For increased efficiency, the interrupt request signal (IRQ) is also available, allowing the host

application to service the Anybus CompactCom module only when necessary.

Description

Serial Clock Input

Master output, slave input. Output from the master’s shift register, and input to the slave’s shift

register.

Master input, slave output. Input to the master’s shift register, and output from the slave’s shift

register.

Slave Select (optional)

Type

O

Description/Comments

Black channel input. Connect to 3V3 if not used.

See Black Channel/Safety Interface, p. 51

See Module Identification, p. 16

See Module Detection, p. 16

See RESET (Reset Input), p. 18

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 30

Host Interface 28 (78)

D0D1D2

D0D1D2

D0D1D2D3D4D5D7 D6

D0D1D2D3D4D5D7 D6

D0D1D2D3D4 D5D7 D6D5D7 D6

D0D1D2D3D4 D5D7 D6D5

SS

SCLK

MOSI

MISO

Byte 0 Byte NByte 1 Byte N-1

D7 D6

SCLK

MISO

MOSI

D7 D6 D5

D7 D6 D5

t

SU

t

HD

t

DO

t

CL

t

CH

SS

D0

D0

t

CSLZ

t

CSHZ

t

CSS

t

CSH

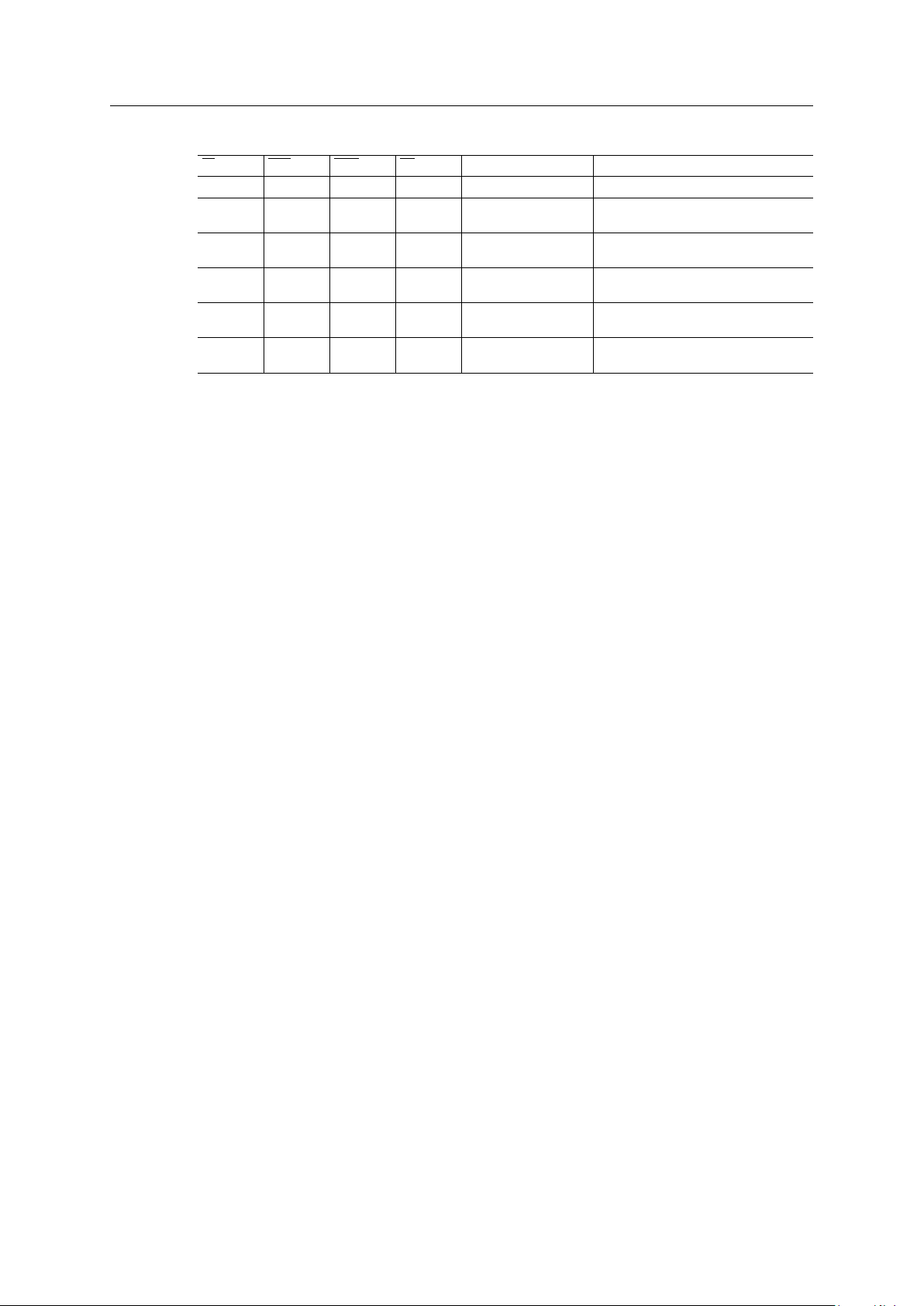

4–Wire Mode

In 4-wire mode the SS signal is used to indicate the start and stop of an SPI transfer. In this mode

the SCLK signal is allowed to be either idle high or idle low. This mode also allows multiple SPI

slaves on the same SPI bus, since Anybus CompactCom MISO is tri-stated when SS is high.

A 4-wire diagram example:

Fig. 10

Fig. 11

Item

tSU

tHD

tDO

tCL

tCH

tCL+tCH

Description

MOSI setup before SCK rising edge

MOSI hold after SCK rising edge

MISO change after SCK falling edge

SCK low period

SCK high period

SCLK period.

Min Value Max Value

10 ns

10 ns

-

-

0 ns 20 ns

20 ns

20 ns

50 ns

-

-

-

Max. frequency supported is 20 MHz.

tCSS

tCSH

tCSLZ

tCSHZ

SS setup before first SCLK rising edge.

SS hold after last SCLK rising edge.

MISO valid after falling edge of SS.

MISO high-Z after rising edge of SS.

20ns

20ns

-

-

-

-

20ns

20ns

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 31

Host Interface 29 (78)

D0D1D2

D0D1D2

D0D1D2D3D4D5D7 D6

D0D1D2D3D4D5D7 D6

D0D1D2D3D4 D5D7 D6D5D7 D6

D0D1D2D3D4 D5D7 D6D5

SCLK

MOSI

MISO

Byte 0 Byte NByte 1 Byte N-1

D7 D6

MISO

SPI

CTRL

5 Words

Reserv

ed

MSGLEN

APP

STAT

INT

MASK

LEDSTAT

ANB

STAT

SPI

STAT

RdMsgField RdPdField

CRC

MOSI

MSG LEN Words

PD LEN Words

4 Words

2 Words

WrPdField CRC

1 WordMSG LEN Words

PD LEN Words 2 Words

PDLEN

Reserv

ed

Reserv

ed

NETTIME

WrMsgField PADDING

3–Wire Mode

In 3-wire mode the SS signal must be tied low permanently, and the SCLK signal must be idle high.

Multiple SPI slaves on the same bus are not possible in this mode. The module detects start and

stop of a transfer by monitoring SCLK activity.

There must be an idle period of at least 10 µs between two transfers in this mode, and the SCLK

signal must never remain high for more than 5 µs during a transfer.

A 3-wire diagram example.

Fig. 12

SPI diagram and bit timing for 3-wire mode.

Fig. 13

Item

tSU

tHD

tDO

tCL

tCH

tCL+tCH

Description Min Value Max Value

MOSI setup before SCK rising edge

MOSI hold after SCK rising edge

MISO change after SCK falling edge

SCK low period

SCK high period

SCK period

10 ns

10 ns

0 ns 20 ns

20 ns

20 ns

50 ns

-

-

-

-

-

Max. frequency supported is 20 MHz.

SPI Frame Format

Fig. 14

The bytes are transmitted with the most significant bit first. The byte order for non-byte frame

elements is typically little endian. This means that the least significant byte is transmitted first.

The CRC32 checksum is an exception as it is transmitted in big endian byte order (most

significant byte first).

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 32

Host Interface 30 (78)

INPUT SHIFT

REGISTER 32

Input Byte 31Input Byte n-1

Output Byte 31Output Byte n-1

OUTPUT SHIFT

REGISTER 32

INPUT SHIFT

REGISTER 1

INPUT SHIFT

REGISTER 2

INPUT SHIFT

REGISTER 3

OUTPUT SHIFT

REGISTER 1

OUTPUT SHIFT

REGISTER 2

OUTPUT SHIFT

REGISTER 3

INPUT SHIFT

REGISTER n

Input Byte 0

Input Byte 1 Input Byte 2

Output Byte 0 Output Byte 1 Output Byte 2

OUTPUT SHIFT

REGISTER n

ADI #1 ADI #2

ADI #3

ADI #32

ADI #64 ADI #63

ADI #62

ADI #33

LD

SCLK

Input byte 0

DO

DI

Output byte 31 Output byte 30

Input byte 1

Output byte 0

Input byte 31

3.5 Stand-alone Shift Register

3.5.1 General Information

In this mode the Anybus CompactCom B40-1 operates stand-alone, with no host processor.

Process data is communicated to shift registers on the host. The Anybus CompactCom B40-1

supports up to 32 registers in each direction, for a total of 256 bits of data.

Fig. 15

Even though the Anybus CompactCom B40-1 operates stand-alone, it is still possible to set host

application attributes, via the use of the virtual attributes list. Some attributes are mandatory to

implement in order to pass conformance test. See the Virtual Attributes section in the Anybus

CompactCom 40 Software Design Guide for more information.

The Anybus CompactCom B40-1 will automatically detect the number of connected input and

output shift registers. Every shift register will be represented by one UINT8 ADI. The input ADIs

will be named “Input 0”, “Input 1”, etc. The output ADIs will be named “Output 0”, “Output 1”,

etc.

The ADI access descriptor values cannot be changed:

Input ADIs: 09h (Get access + Write process data mapping possible).

Output ADIs: 11h (Get access + Read process data mapping possible)

Bits are clocked out/in MSB first, on the positive side of CLK. An active low load signal (LD) loads

all shift registers before and after a transfer.

Fig. 16

A fifth signal, PA, is high when the module is in active state, and low when the module is not.

This signal can be used by the application to clear/set the output shift registers to default values

when the module is not in active state.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 33

Host Interface 31 (78)

3.5.2 Pin Usage in Stand-Alone Shift Register Mode

Presented below is an overview of all pins except GND and VDD.

Pin Signal Name

4

5

6

7

9

10

11

12

13 LD O

15 SCLK O

16 DO O

17 DI I

19

20

31

29

27

26

25

23

22

21

49

48

47

46

45

43

42

41

37 CT I

38 PA O

39

36

51 ASI RX I

52

32

33

35

54

53

30 MD O

3 RESET I

DIP1_0

DIP1_1

DIP1_2

DIP1_3

DIP1_4

DIP1_5

DIP1_6

DIP1_7

(not used)

(not used)

DIP2_0

DIP2_1

DIP2_2

DIP2_3

DIP2_4

DIP2_5

DIP2_6

DIP2_7

LED1B

LED1A

LED2B

LED2A

LED3B

LED3A

LED4B

LED4A

(not used)

(not used)

ASI TX / OM3

OM0

OM1

OM2

MI0/SYNC

MI1

Type

I

I

I

I

I

I

I

I

-

-

I

I

I

I

I

I

I

I

O

O

O

O

OD

OD

O

O

-

-

O, Strap

I

O

Description/Comments

DIP switch node address / IP address.

See DIP1 and DIP2 Pins Usage, p. 32.

Shift register load.

Clock output.

Serial data output to shift registers.

Serial data input from shift registers.

Leave unconnected

Leave unconnected

DIP switch baud rate / Device ID / station name.

See DIP1 and DIP2 Pins Usage, p. 32.

LED interface. Gives access to LED indications. For more information,

see LED Interface / D8–D15 (Data Bus), p. 14.

Center tap signal for shift register mode.

The number of connected input and output shift registers will be

detected using this signal.

Process active signal for shift register mode.

In a PROFINET shift register stand-alone application, the PA signal

must be used to clear outputs, when the Anybus CompactCom B40-1

is not in state PROCESS ACTIVE. Otherwise it will not be possible to

certify the final product. See the Anybus CompactCom 40 PROFINET

IRT Network Guide for more information.

Leave unconnected.

Leave unconnected.

Black channel input. Connect to 3V3 if not used.

See Black Channel/Safety Interface, p. 51

Black channel output.

See Black Channel/Safety Interface, p. 51

During startup the pin (with OM[0..2]) is used to define the operating

mode of the module. Connect to external pull-down for shift register

operating mode, see Pin Overview, p. 12.

Operating mode [OM2, OM1, OM0]: 0,1,0 for shift register operating

mode.

For more information seeOperating Modes, p. 16.

See Module Identification, p. 16.

See Module Detection, p. 16.

SeeRESET (Reset Input), p. 18

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 34

Host Interface 32 (78)

DIP1 and DIP2 Pins Usage

The use of the DIP1 and DIP2 pins is network specific. If used, they will be read during SETUP

state. Thereafter, DIP switch changes will be sampled and written to the Network Configuration

Object every 0.5 seconds.

DIP1 is linked to the Network Configuration Object, instance 1 (node address) or instance 3 (IP

address). DIP2 is linked to the Network Configuration Object, instance 2 (baud rate) or instance 1

(Device ID, EtherCAT), or, in the case of PROFINET, linked to the PROFINET IO Object , instance 1,

attribute 24.

See Network Configuration Object (04h) in the Anybus CompactCom 40 Software Design Guide

for more information.

Network DIP1 (linked to Network

DeviceNet

EtherCAT 1 - 254 (Instance 3: IP

EtherNet/IP

Modbus-TCP 1 - 254 (Instance 3: IP

Common Ethernet 1 - 254 (Instance 3: IP

Ethernet

POWERLINK

PROFIBUS

Configuration Object)

0 - 63 (Instance 1: Node

address)

address)

1 - 254 (Instance 3: IP

address)

address)

address)

NMT_CS_BASIC_ETHERNET:

1 - 254 (Instance 3: IP

address)

NMT_CS_EPL_MODE:

1 - 239 (Instance 1: Node

address)

0 - 126 (Instance 1: Node

address)

DIP2 Notes

Value: 0 - 3 (Network

Configuration Object,

Instance 2: Baud Rate)

0 - 255 (Network

Configuration Object,

Instance 1: Device ID)

Not used

Not used

Not used

Not used If no POWERLINK traffic is seen at

Not used

DIP2: Network Configuration Object,

Instance 2: Baud Rate (125 kbps, 250

kbps, 500 kbps, Auto)

If DIP1 is set to 0, saved values from

instances 3 - 6 are used. If DIP1 is set

to 255, DHCP is used for all settings.

The DIP switches set the last byte of

the IP address. Virtual attributes are

used to configure the remaining part

the IP address, as well as the

subnetmask (Network Configuration

Object, instance 4) and the gateway

(instance 5).

startup the module will enter the

NMT_CS_BASIC_ETHERNET state

after 5 seconds. In this state DIP1 is

used for the IP address.

As soon as the module detects

POWERLINK traffic it will enter the

NMT_CS_EPL_MODE super state. In

this state DIP1 is used as the

POWERLINK node address. In the

NMT_CS_EPL_MODE state the IP

address of the module is fixed to

192.168.100.yyy where yyy is the

node address.

Note that IT functionality can be

disabled in the POWERLINK host

application object. If that is done

DIP1 is never used for the IP address.

-

®

Anybus

CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 35

Host Interface 33 (78)

Network DIP1 (linked to Network

PROFINET

CC-Link 1 - 64 (Instance 1: Node

CC-Link IE Field 1 - 120 (Instance 1: Station

BACnet/IP

CANopen

Configuration Object)

1 - 254 (Instance 3: IP

address)

address).

Number).

1 - 254 (Instance 3: IP

address)

0 - 127 (Instance 1: Node

address)

DIP2 Notes

Value: 1 — 255 (PROFINET

IO object, Instance 1,

attribute 24)

Value: 0 - 4 (Network

Configuration Object,

Instance 2: Baud Rate)

1 - 239 (Instance 3: Network

Number).

Not used

Value: 0 - 9 (Network

Configuration Object,

Instance 2: Data Rate)

If DIP1 is set to 0, saved values from

instances 3 - 6 are used. If DIP1 is set

to 255, DHCP is used for all settings.

The DIP1 to switches set the last

byte of the IP address. Virtual

attributes are used to configure the

remaining part the IP address, as

well as the subnetmask (Network

Configuration Object, instance 4) and

the gateway (instance 5).

If DIP2 is set to 0, the value saved in

the non volatile memory will be used.

The DIP2 switches set the last three

digits of the station name. see the

Anybus CompactCom 40 PROFINET

IRT Network Guide.

DIP1: Depending on number of

stations used. An invalid value will

generate a NACK on Setup Complete.

DIP2: Network Configuration Object,

Instance 2: Baud Rate (156 kbps, 625

kbps, 2.5 Mbps, 5 Mbps, 10 Mbps)

-

-

DIP2: Network Configuration Object,

Instance 2: Data Rate

Unused DIP pins should be connected to ground (GND).

External pull-down resistors are needed if DIP switches are connected to the DIP1 and DIP2 pins,

see DIP Switches Example, p. 36.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 36

Host Interface 34 (78)

SCK

DI

DO

D7 D6 D5

D7 D6 D5

t

SUOtHDO

t

HDI

t

SUI

t

CH

LD

t

CL

D1 D0

D1 D0

CT

t

HDI

t

SUI

t

CH

t

CL

3.5.3 Timing

The Anybus CompactCom B40-1 operates in 12.5 MHz in shift register mode.

Timing Diagram

Fig. 17

Abbreviations from the diagram above, explained, and timing details:

Item

tSUO

tHDO

tSUI

tHDI

tCH

tCL

tCH + tCL

Description Min Value

DO setup before SCK rising edge

DO hold after SCK rising edge

DI/CT setup before SCK rising edge

DI/CT hold after SCK rising edge

SCK high period

SCK low period

SCK period

20 ns

20 ns

10 ns

0 ns

35 ns

35 ns

78 ns

The idle time between two transfers, i.e. when the LD signal is low, is at least 1 µs.

The cycle time range is typically 160 µs to 200 µs. However it is highly module and network

dependent, and may differ from the defined range.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 37

Host Interface 35 (78)

RCLR

RCLR

RCLR

RCLR

SRCLR

SRCLR

SRCLR

PL

Q7

Q7

Q7

Q7

Q7

CKE

CKE

I2 D4

O0 D5

I1 D0

I3 D0

I3 D2

I1 D6

O2 D7

O1 D7

O3 D2

I2 D7

I0 D1

O0 D7

O1 D1

O0 D3

O3 D5

O3 D6

O1 D5

OUTPUTS

I0 D6

I3 D7

O1 D3

I2 D2

O3 D3I3 D3

I1 D2

O3 D0

INPUTS

O0 D6

O2 D5

I2 D1

I0 D3

O3 D4

I2 D3

O1 D2

I0 D7

I1 D1

I3 D4

O0 D4

O0 D1

O2 D0

O1 D4

I2 D5

I0 D0

I3 D6

I0 D5

I0 D4

O2 D4

O2 D6

I1 D3

I2 D6

I1 D4

O2 D1

O2 D2

I1 D5

O0 D0

I3 D5

I3 D1

O2 D3

I1 D7

O1 D6

O0 D2

O3 D7

I2 D0

O3 D1

I0 D2

O1 D0

OUT_REG_3

74LVC594A

9

13

10

14

11

12 15

1

2

3

4

5

6

7

SDOSDI

SRCLK

RCLK A

B

C

D

E

F

G

H

OUT_REG_0

74LVC594A

9

13

10

+3.3V

14

11

12 15

1

2

3

4

5

6

7

SDO

SRCLR

SDI

SRCLK

RCLK A

B

C

D

E

F

G

H

OUT_REG_2

74LVC594A

9

13

10

14

11

12 15

1

2

3

4

5

6

7

SDOSDI

SRCLK

RCLK A

B

C

D

E

F

G

H

IN_REG_1

74LV165/SO

7

910

2

15

1

11

12

13

14

3

4

5

6

Q7

SDI

CLK

PL

A

B

C

D

E

F

G

H

IN_REG_0

74LV165/SO

7

910

2

15

1

11

12

13

14

3

4

5

6

Q7

SDI

CLK

CKE

PL

A

B

C

D

E

F

G

H

IN_REG_2

74LV165/SO

7

910

2

15

1

11

12

13

14

3

4

5

6

SDI

CLK

PL

A

B

C

D

E

F

G

H

OUT_REG_1

74LVC594A

9

13

10

14

11

12 15

1

2

3

4

5

6

7

SDOSDI

SRCLK

RCLK A

B

C

D

E

F

G

H

IN_REG_3

74LV165/SO

7

910

2

15

1

11

12

13

14

3

4

5

6

Q7

SDI

CLK

CKE

A

B

C

D

E

F

G

H

PA

Input byte 3

SR DO

Input byte 0

SR CLK

Output byte 2

Output byte 3

Output byte 0

SR LD_N

SR CT

Input byte 1

SR DI

(Pin 38, Optional)

(Pin 16)

(Pin 15)

(Pin 13)

(Pin 37)

(Pin 17)

Input byte 2

Output byte 1

+3.3V

+3.3V

+3.3V

3.5.4 Basic Shift Register Circuit

The schematic below illustrates a basic shift register circuit.

®

Anybus

CompactCom B40-1 Design Guide

Fig. 18

HMSI-27-230 3.4 en-US

Page 38

Host Interface 36 (78)

H_RESET_N

3V3

3V3

C2

1nF/50V

U?

TPS3828-33

RESET

1

GND

2

MR

3

WDI

4

VCC

5

R1

2k2

C1

100nF/16V

C3

1nF/50V

B1

SW PUSHBUTTON RIGHT ANGLE

1 2

3 4

DIP[1_0 .. 1_7]

DIP1_0

DIP1_1

DIP1_2

DIP1_3

DIP1_4

DIP1_5

DIP1_6

DIP1_7

DIP1_1

DIP1_2

DIP1_3

DIP1_4

DIP1_5

DIP1_6

DIP1_7

DIP1_0

3V3

10k10k10k 10k10k 10k10k10k

DIP switches

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

3.5.5 Reset Circuit Example

The reset circuit example in the figure, is a common 3.3 V supervisor. The main usage is to obtain

a defined reset release delay after the voltage is switched on. The power supply has to provide a

stable voltage within the interval 3.15–3.45 V

Fig. 19

3.5.6 DIP Switches Example

Pull-down resistors are necessary if DIP switches are connected to the DIP inputs.

Fig. 20

®

Anybus

CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 39

Host Interface 37 (78)

3.6 UART Operation

3.6.1 General Description

The serial interface is a common asynchronous serial interface, which can easily be interfaced

directly to a microcontroller or UART. It is provided for backward compatibility with the Anybus

CompactCom 30 series.

The serial interface is activated using the OM[0...3] inputs, which also are used to select the

operating baud rate, see Operating Modes, p. 16.

Other communication settings are fixed to the following values:

Data bits: 8

Parity: None

Stop bits: 1

Communication settings are fixed to asynchronous, 8-N-1, with bit order LSB first and without

hardware flow control signals.

It is not possible to build a synchronous application in this mode.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 40

Host Interface 38 (78)

3.6.2 Pin Usage in Serial Mode

Presented below is an overview of all pins except GND and 3V3

Pin Signal Name Pin Type

4

5

6

7

9

10

11

12

13

15

16

17

19 ASI RX I

20 ASI TX O

31

29

27

26

25

23

22

21

49

48

47

46

45

43

42

41

37

39

36

38

51 RX I Receive Input

DIP1_0

DIP1_1

DIP1_2

DIP1_3

DIP1_4

DIP1_5

DIP1_6

DIP1_7

(not used)

(not used)

DIP2_0

DIP2_1

DIP2_2

DIP2_3

DIP2_4

DIP2_5

DIP2_6

DIP2_7

LED1B

LED1A

LED2B

LED2A

LED3B

LED3A

LED4B

LED4A

(not used)

(not used)

I

I

I

I

I

I

I

I

I

I

O,I

I

I

I

I

I

I

I

I

I

O

O

O

O

OD

OD

O

O

I

I

I

O

Description/Comments

DIP switch. Usage defined by application.

Readable through attribute #14 (Switch status) in Anybus Object,

instance #1.

Connect directly to GND if not used.

Connect directly to GND

Connect directly to 3V3.

See Black Channel/Safety Interface, p. 51

If not used, connect directly to 3V3.

See Black Channel/Safety Interface, p. 51

If not used, leave unconnected.

DIP switch. Usage defined by application.

Readable through attribute #14 (Switch status) in Anybus Object,

instance #1.

Connect directly to GND if not used.

LED interface. Gives access to LED indications. For more information,

LED Interface / D8–D15 (Data Bus), p. 14.

When not used, LED1A, LED1B, LED2A, LED2B, LED4A and LED4B can

be left unconnected.

LED3A and LED3B are open-drain outputs and should, if not used, be

pulled either to GND or to 3V3, depending on application.

Connect directly to 3V3.

Leave unconnected

• Direction: Host application -> CompactCom

• Idle state = High

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 41

Host Interface 39 (78)

Pin Signal Name Pin Type

52

32

33

35

54

53

30 MD0 O

3 RESET I

TX / OM3

OM0

OM1

OM2

MI0/SYNC

MI1

It is important to connect all signals correctly for proper functioning of the serial interface.

3.6.3 Baud Rate Accuracy

Description/Comments

O, I Transmit Output

• Direction: CompactCom -> Host application

• Idle state = High

This pin doubles as OM3 strapping input on Anybus CompactCom

M40 modules. Connect a pull-up resistor on the application for this

pin in serial mode.

I

O

Operating mode [OM2, OM1, OM0]:

001

010

011

100

For more information see Operating Modes, p. 16.

See Module Identification, p. 16

See Module Detection, p. 16

See RESET (Reset Input), p. 18

Serial 19.2 kbps

Serial 57.6 kbps

Serial 115.2 kbps

Serial 625 kbps

As with most asynchronous communication devices, the actual baud rate used on the Anybus

CompactCom may differ slightly from the ideal baud rate.

The baud rate error of the module is less than ±1.5%. For proper operation, it is recommended

that the baud rate accuracy in the host application lies within ±1.5% from the ideal value.

Anybus®CompactCom B40-1 Design Guide

HMSI-27-230 3.4 en-US

Page 42

Network Connector 40 (78)

Pin 1

Application

interface

Pin 1

Network

interface

Outline of brick

Top view