Page 1

V

5

1

+

3

6

/

n

0

0

1

d

r

a

o

B

P

S

D

o

8

2

3

6

/

n

2

0

1

3

1

L

C

5

r

a

t

i

u

G

t

u

p

n

I

1

P

J

s

a

F

J

F

J

F

J

F

P

J

a

F

1

~

V

0

3

8

,

4

L

.

t

2

P

N

G

A

,

6

L

.

t

s

a

3

P

a

P

a

5

s

~

V

0

3

,

4

L

.

t

s

4

A

V

0

1

,

4

L

.

t

s

A

V

0

1

8

,

4

L

.

t

2

3

4

1

1

J

0

4

/

µ

2

2

A

m

0

0

0

2

B

S

1

C

A

0

5

2

/

n

0

2

2

D

3

2

C

A

A

m

0

0

0

2

B

S

2

8

A

m

0

3

6

B

S

1

C

1

F

8

D

N

G

D

2

C

1

1

R

4

C

P

8

7

0

3

3

C

M

5

6

2

U

3

F

5

5

C

4

F

k

n

0

1

9

4

C

k

n

0

1

8

4

C

2

0

k

1

C

V

5

1

+

0

M

k

0

4

1

R

k

0

6

1

R

7

0

4

5

N

1

5

D

6

0

4

5

N

1

6

D

0

4

5

N

1

7

D

6

0

4

5

N

1

8

D

B

k

n

0

1

0

5

C

k

n

0

1

7

4

C

1

6

6

V

3

3

-

0

0

5

1

C

0

8

1

U

3

2

5

R

5

3

k

R

1

0

4

/

7

µ

5

2

C

2

V

3

3

+

0

5

4

/

2

µ

C

0

0

7

4

0

2

4

3

/

C

µ

0

0

7

4

y

l

o

P

6

3

C

C

8

U

+

U

4

2

U

7

k

4

2

R

p

0

0

1

5

2

C

s

W

5

/

0

0

1

9

4

R

W

5

/

0

0

1

w

S

7

8

4

R

E

X

R

h

c

t

i

2

F

3

6

5

/

2

n

/

0

µ

0

0

1

0

2

2

P

8

7

0

3

3

C

M

1

n

r

u

t

e

R

/

d

n

e

S

o

t

E

R

E

R

5

2

/

µ

0

2

2

5

2

/

µ

0

2

2

5

0

5

1

5

3

C

3

C

0

4

/

µ

2

2

k

0

1

2

W

D

N

G

A

D

N

G

A

D

N

G

A

D

N

G

A

_

D

N

E

S

_

D

N

E

S

V

5

1

+

V

5

1

-

R

_

N

R

U

T

L

_

N

R

U

T

3

6

/

6

n

2

0

C

0

1

3

6

/

1

n

3

0

C

0

1

A

m

0

0

S

8

7

L

N

I

D

N

G

2

N

G

D

1

2

3

4

L

5

R

6

7

8

9

0

1

0

1

C

C

F

1

N

I

3

U

7

2

C

0

3

C

2

5

3

T

U

O

3

5

U

6

/

n

0

0

1

D

0

2

2

8

R

7

R

µ

7

,

4

5

1

8

7

L

D

N

G

2

G

N

D

1

I

N

5

1

9

7

L

1

5

C

1

D

7

,

2

D

P

Z

.

i

b

0

4

/

7

,

4

0

6

C

+

1

5

V

V

5

1

-

1

5

R

k

0

0

1

3

T

U

O

4

U

O

U

T

3

T

S

_

C

C

V

V

5

+

T

S

_

D

N

G

0

4

/

µ

2

2

9

5

C

7

,

2

D

P

Z

9

2

D

.

i

b

0

4

/

µ

8

5

C

n

a

T

9

2

µ

C

2

,

2

n

a

T

3

3

µ

C

2

,

2

V

5

1

-

E

G

A

E

G

A

t

1

.

1

W

1

2

3

4

5

C

C

F

9

D

7

0

0

4

N

1

+

1

5

V

V

5

1

-

L

N

I

R

N

I

d

e

l

b

m

e

s

s

a

t

o

n

8

C

/

7

C

D

N

G

A

L

T

U

O

R

T

U

O

5

T

H

G

I

R

_

P

M

A

R

E

W

O

P

2

R

0

s

1

k

P

g

o

l

2

L

k

0

1

7

M

1

4

1

R

3

6

/

6

µ

5

7

C

,

4

k

7

0

M

0

2

0

4

5

1

1

1

5

V

R

R

W

1

/

0

3

3

0

3

R

7

k

4

0

1

R

B

5

4

2

F

B

7

Q

_

P

M

A

R

E

W

O

P

R

s

k

g

0

o

1

l

P

k

L

0

1

B

5

4

2

F

B

4

1

Q

9

P

J

1

2

3

3

T

S

J

3

6

/

n

7

4

6

C

3

6

/

n

5

,

!

2

1

p

8

6

3

6

/

n

0

2

5

C

k

7

4

4

C

T

F

E

L

3

6

/

n

7

4

6

1

C

3

6

/

n

5

,

1

p

8

1

3

R

2

6

7

k

B

4

3

6

/

n

0

2

5

1

C

k

7

4

4

C

D

E

L

r

e

w

o

P

5

k

7

1

C

8

C

B

6

4

5

C

B

1

Q

9

R

7

k

4

9

k

3

3

6

/

n

7

3

1

8

1

C

/

7

1

C

5

7

k

1

1

C

8

1

C

B

6

4

5

C

8

Q

3

1

R

7

k

4

9

k

3

3

6

/

n

7

3

2

n

o

i

t

p

O

0

0

4

1

R

7

2

R

8

2

R

t

o

n

2

3

R

5

4

R

6

4

R

5

1

1

R

0

0

1

6

1

R

B

6

4

5

C

B

6

1

/

2

Q

µ

7

4

0

6

5

8

,

6

3

D

D

P

Z

!

d

e

l

b

m

e

s

s

a

0

0

3

1

3

R

0

0

1

4

3

R

B

6

4

5

C

B

6

1

/

9

Q

µ

7

4

0

6

5

8

,

6

4

D

D

P

Z

1

k

2

2

2

1

C

6

2

R

1

k

2

2

2

2

C

4

4

R

V

3

3

+

3

Q

8

3

2

D

B

p

0

5

9

C

7

k

2

8

5

1

2

R

R

5

k

1

5

k

1

3

3

-

3

3

+

p

0

5

9

1

C

7

k

2

6

3

3

4

R

R

5

k

1

5

k

1

3

3

-

p

0

7

1

R

9

k

3

T

R

9

1

R

4

2

R

0

2

1

2

C

7

1

k

0

1

h

0

1

T

P

1

R

0

4

/

µ

7

4

L

1

1

C

V

V

0

1

Q

8

3

2

D

B

p

0

5

3

R

9

k

3

7

3

R

2

4

R

0

2

2

2

C

2

R

T

k

0

1

v

0

1

T

P

R

0

4

/

µ

7

4

L

1

2

C

V

:

e

l

t

i

T

p

m

A

n

e

Z

R

E

W

O

P

,

P

M

A

R

E

W

O

P

:

e

m

a

n

e

l

i

F

C

1

-

1

0

R

-

P

S

-

0

0

1

0

U

H

9

3

0

2

R

9

7

6

D

B

4

Q

6

0

1

3

2

R

9

3

8

3

R

7

6

D

B

1

1

Q

0

1

1

4

R

I

,

Y

L

P

P

U

S

b

.

1

0

2

1

4

0

-

Q

7

3

1

P

I

T

1

4

9

3

1

Q

7

3

1

P

I

T

R

O

T

C

E

S

T

U

P

N

g

i

T

Q

8

1

W

5

/

2

7

5

4

R

1

2

,

0

W

5

/

1

7

2

4

R

,

0

T

Q

W

5

/

2

7

2

4

R

,

0

W

5

/

9

7

3

4

R

,

0

y

b

d

e

k

c

e

h

C

M

0

o

B

l

e

a

h

c

i

0

0

2

-

c

e

D

-

4

V

3

3

+

2

3

1

P

I

5

)

+

R

t

u

p

t

u

O

(

6

P

J

8

,

4

L

.

t

s

a

F

W

1

9

/

2

7

R

4

3

6

/

4

n

1

2

C

2

)

M

O

C

t

u

p

t

u

O

(

V

3

3

-

3

+

2

3

1

P

I

2

1

W

1

/

7

4

3

6

/

n

2

2

:

r

e

d

n

e

l

h

1

7

P

J

3

,

6

L

.

t

s

a

F

V

3

)

+

L

t

u

p

t

u

O

(

8

P

J

8

,

4

L

.

t

s

a

F

7

4

R

4

2

C

V

3

3

-

:

y

b

n

w

a

r

D

.

M

t

a

D

-

4

0

a

r

D

0

U

H

g

a

P

r

e

d

n

e

l

h

o

B

:

e

1

0

0

2

-

c

e

D

:

.

r

N

-

g

n

i

w

-

0

0

1

:

e

C

1

-

1

0

R

-

P

S

3

/

1

Page 2

V

3

,

3

+

1

R

k

n

i

l

k

0

1

P

2

R

N

I

A

G

L

k

n

0

0

1

k

n

i

l

k

0

1

5

4

C

P

3

R

S

S

A

B

L

k

n

0

0

1

k

n

i

l

k

0

1

4

4

C

P

4

R

D

I

M

L

k

n

0

0

1

k

n

i

l

k

0

1

3

4

C

P

5

R

E

L

B

E

R

L

T

k

n

0

0

1

k

n

i

l

k

0

1

2

4

C

P

6

R

E

C

N

E

L

S

E

R

P

k

n

0

0

1

k

n

i

l

k

0

1

1

4

C

P

7

R

E

M

U

L

L

O

V

k

n

i

l

k

0

1

k

n

9

0

3

0

C

1

P

8

R

B

R

E

V

L

E

R

k

n

i

l

k

0

1

k

n

8

0

3

0

C

1

P

9

R

P

k

n

R

E

L

T

E

M

A

R

A

P

X

k

F

n

0

0

1

i

l

k

0

1

7

3

C

Y

A

L

E

D

L

k

n

0

0

1

-

1

5

V

0

4

C

V

5

1

+

V

5

1

+

V

5

1

N

I

A

G

S

S

A

B

D

I

M

E

L

B

E

R

T

E

C

N

E

S

E

R

P

E

M

U

L

O

V

B

R

E

V

E

R

R

E

T

E

M

A

R

A

P

X

F

Y

A

L

E

D

D

N

G

D

V

5

+

E

G

A

T

S

_

D

N

G

E

G

A

T

S

_

C

C

V

2

.

1

W

1

2

3

4

5

6

7

8

9

0

1

1

1

2

1

3

1

4

1

5

1

5

1

C

C

F

+

5

V

T

k

n

0

0

1

4

5

4

3

C

k

n

0

0

1

4

1

2

5

C

k

n

0

0

1

2

3

3

5

C

k

n

0

0

1

h

C

6

4

C

k

n

0

0

1

4

5

C

k

n

0

0

1

1

6

C

k

n

0

0

1

2

6

C

o

C

h

a

s

s

i

s

G

r

o

u

n

d

s

i

s

s

a

3

,

6

L

.

t

s

a

F

0

1

P

J

o

t

)

y

r

a

t

o

R

(

s

e

h

c

t

i

w

S

3

W

6

1

5

1

P

A

T

4

1

P

A

T

3

1

A

D

H

2

1

A

D

H

1

1

A

D

H

0

1

A

D

H

9

A

D

H

8

A

D

H

7

6

5

4

3

2

1

6

1

C

C

F

V

5

+

D

E

L

Y

E

K

0

A

T

1

A

T

2

A

T

3

A

T

4

A

T

5

A

T

6

A

T

A

D

H

7

A

T

A

D

H

0

S

C

1

S

C

2

S

C

D

N

G

D

V

3

,

3

+

3

.

1

W

1

2

3

4

5

6

7

8

9

e

l

u

d

o

M

-

P

S

D

o

0

1

1

1

2

1

3

1

4

1

5

1

C

F

t

5

1

C

T

Z

P

F

H

:

y

b

n

w

a

r

D

.

M

:

e

l

t

i

p

m

A

n

e

R

O

T

C

E

S

T

U

P

N

I

,

Y

L

P

P

U

S

R

E

W

O

P

,

P

M

A

R

E

W

O

:

e

m

a

n

e

l

i

g

i

b

.

1

0

2

1

4

0

-

C

1

-

1

0

R

-

P

S

-

0

0

1

0

U

h

C

i

M

4

0

:

y

b

d

e

k

c

e

l

e

a

h

c

-

c

e

D

-

e

d

n

e

l

h

o

B

1

0

0

2

t

a

D

-

4

0

a

r

D

0

U

H

g

a

P

r

r

e

d

n

e

l

h

o

B

:

e

1

0

0

2

-

c

e

D

:

.

r

N

-

g

n

i

w

-

0

0

1

:

e

C

1

-

1

0

R

-

P

S

3

/

2

Page 3

p

p

m

u

J

E

G

A

T

S

_

C

C

V

V

5

+

3

4

D

N

G

D

1

2

V

5

1

+

D

N

G

A

D

N

G

A

V

5

1

+

D

N

G

D

V

5

1

-

D

N

G

D

B

L

E

F

U

T

S

D

N

E

R

E

F

U

T

S

D

N

E

V

5

1

-

V

9

R

B

p

m

u

J

+

0

1

R

B

p

m

u

J

4

8

R

B

p

m

u

J

D

1

1

R

B

p

m

u

J

2

3

R

B

p

m

u

J

+

3

1

R

B

p

m

u

J

A

5

R

B

p

m

u

J

A

4

R

B

p

m

u

J

+

6

R

B

p

m

u

J

D

2

R

B

p

m

u

J

-

7

R

B

p

m

u

J

D

4

1

R

p

m

u

J

E

6

1

R

B

p

m

u

J

E

5

1

R

B

p

m

u

J

-

1

R

B

E

G

A

T

S

_

C

C

V

5

3

D

N

G

1

V

5

1

D

N

G

D

N

G

V

5

1

D

N

G

V

5

1

D

N

G

L

E

F

U

T

S

D

N

R

E

F

U

T

S

D

N

V

5

1

h

C

G

D

G

A

m

u

J

s

i

s

s

a

2

1

R

B

p

m

u

J

D

N

7

1

R

B

p

m

u

J

D

N

8

1

R

B

s

i

s

s

a

h

C

D

N

G

D

s

i

s

s

a

h

C

2

.

3

e

2

.

3

e

l

o

H

D

N

G

A

5

O

H

2

.

3

e

l

o

H

D

N

G

A

3

O

H

l

o

H

s

i

s

s

a

h

C

2

2

.

3

e

l

o

H

s

i

s

s

a

h

C

3

:

y

b

n

w

a

r

T

Z

P

F

H

D

.

M

:

e

l

t

i

p

m

A

n

e

R

O

T

C

E

S

T

U

P

N

I

,

Y

L

P

P

U

S

R

E

W

O

P

,

P

M

A

R

E

W

O

:

e

m

a

n

e

l

i

g

i

b

.

1

0

2

1

4

0

-

C

1

-

1

0

R

-

P

S

-

0

0

1

0

U

h

C

i

M

4

0

:

y

b

d

e

k

c

e

l

e

a

h

c

-

c

e

D

-

e

d

n

e

l

h

o

B

1

0

0

2

t

a

D

-

4

0

a

r

D

0

U

H

g

a

P

r

r

e

d

n

e

l

h

o

B

:

e

1

0

0

2

-

c

e

D

:

.

r

N

-

g

n

i

w

-

0

0

1

:

e

C

1

-

1

0

R

-

P

S

3

/

3

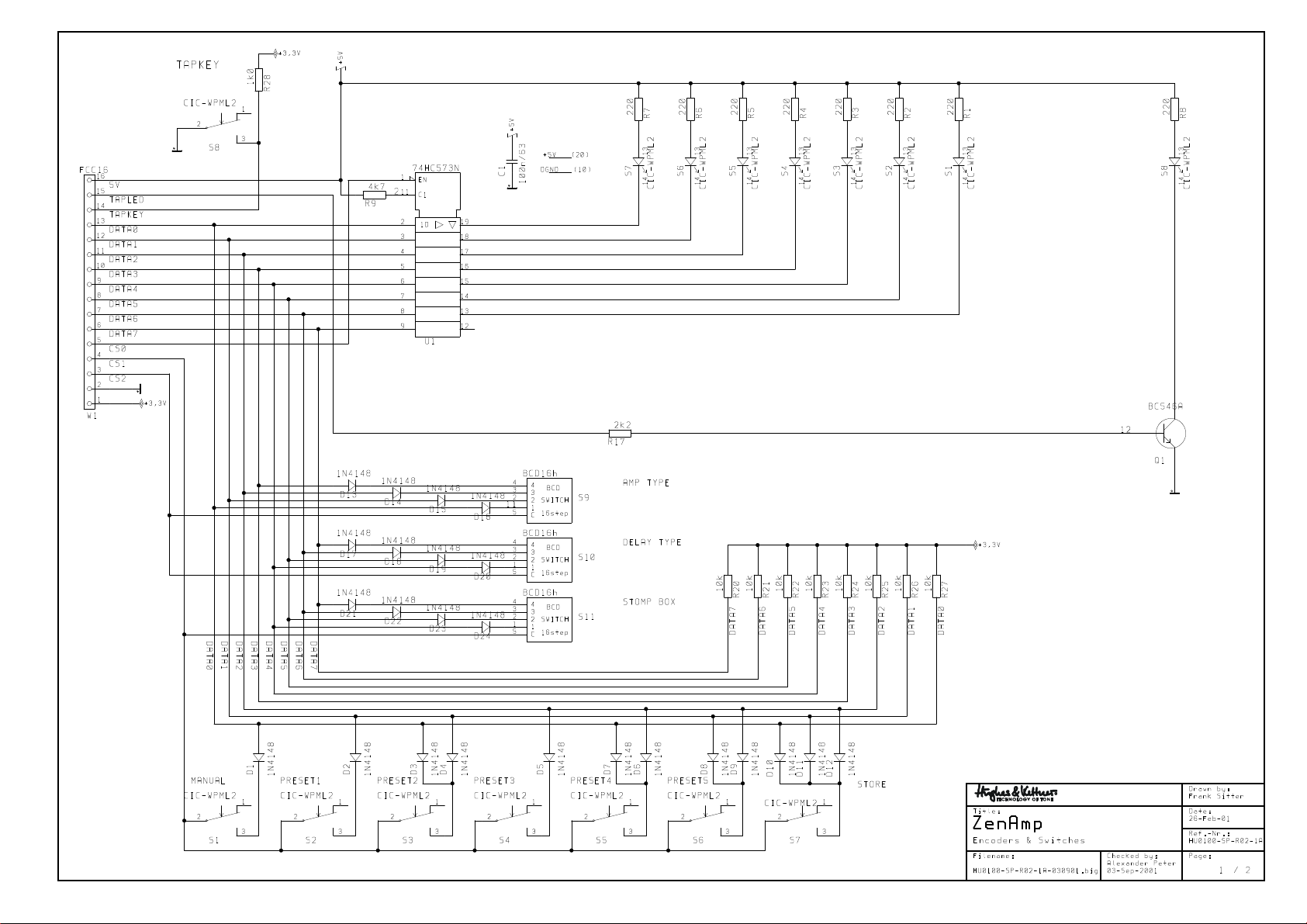

Page 4

Page 5

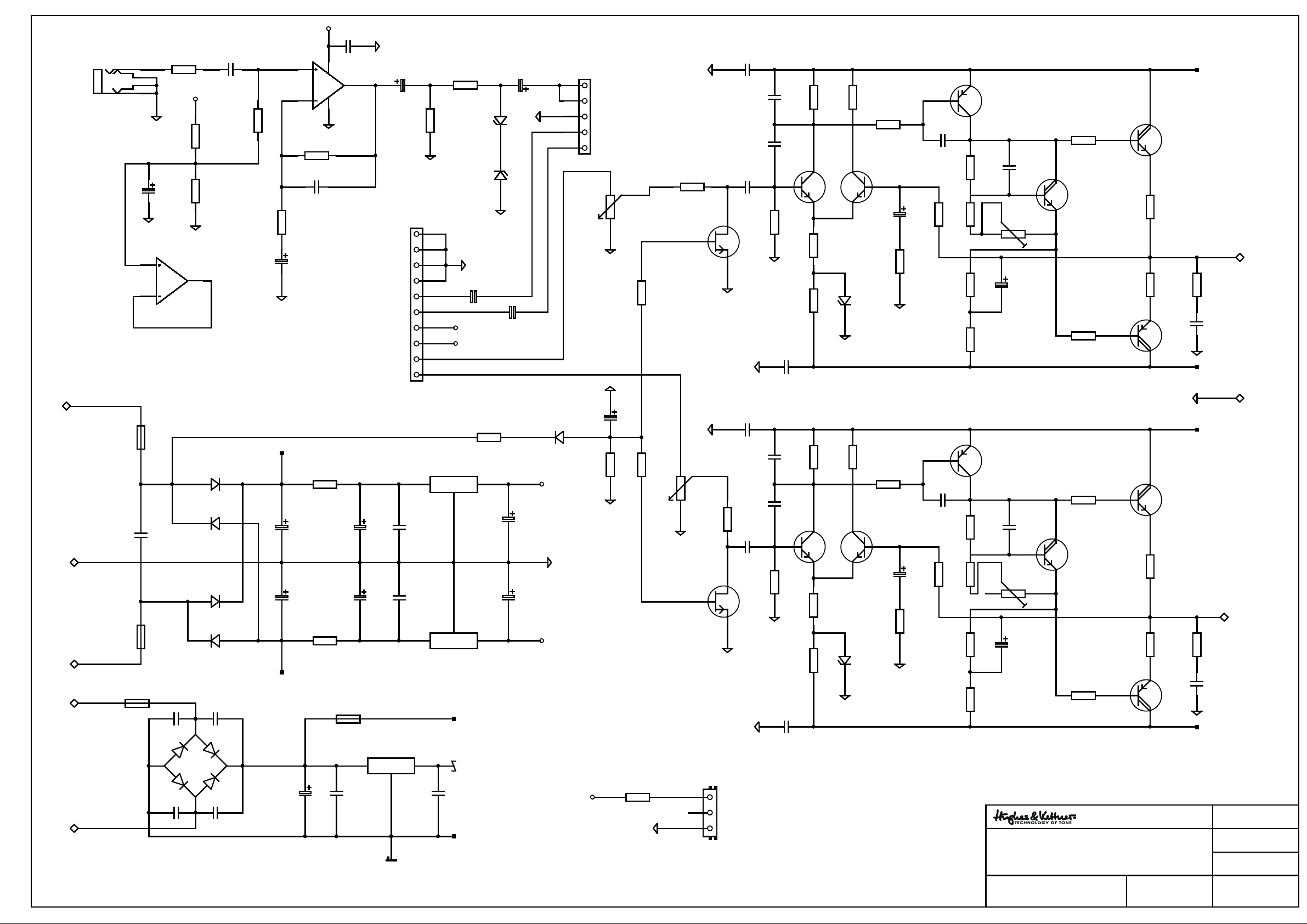

Page 6

7654321

8

T

J1

R12

18K

+

-

TS

SS

S

RM122-02

T

J2

TS

SS

S

RM122-02

U2D

14

MC33079P(MOT)

Send-L

Send-R

C10

220n/63V_RM5

R15

8K2

W1

1

2

3

4

5

Send-L

Send-R

6

7

from poweramp pcb

AWG24-10-2.54

8

9

10

Return-R

Return-L

22n/63V_RM5

D

+

2u2/35V-T

C7

C1

C2

+

2u2/35V-T

C8

22n/63V_RM5

R1

47R

+15V

-15V

R11

220K

R2

47R

12

13

C

R14

12K

R35

1

9K1

R31

2K2

C18

10n/63V_RM5

R32

2K2

R13

4K7

2

-

3

+

C9

10n/63V_RM5

-15V

VCCVEE

4 11

U4A

MC33079P(MOT)

+15V

Return-L

Return-R

3

2

C20

1n/63V_RM5

R37

3K9

J3

RM122-02

J4

RM122-02

+15V

+

-

-15V

R38

220R

411

U2A

VCCVEE

MC33079P(MOT)

1

6

5

T

TS

SS

S

T

TS

SS

S

C11

1n/63V_RM5

R16

18K

+

R17

10K

7

U4B

MC33079P(MOT)

C3

1u/63V_RM5

R18

11K

12

13

R3

1K0

U3D

+

-

MC33079P(MOT)

R19

22K

C12

22pF/100V-K

R20

9K1

R41

39K

14

R21

36K

R4

47KR522K

R22

1K2

R23

39K

C21

3n3/63V_RM5

R42

3K9

3

+

2

-

C13

33n/63V_RM5

C14

3n3/63V_RM5

R24

82K

9

-

10

+

3

2

+15V

-15V

+

-

411

VCCVEE

+15V

84

VCCVEE

U1A

1

OP275

-15V

R6

22K

C4

47pF/100V-K

U3A

MC33079P(MOT)

1

8

U4C

MC33079P(MOT)

R25

1K5

C5

1u/63V_RM5

5

6

C15

3n3/63V_RM5

+

-

U4D

12

+

13

-

MC33079P(MOT)

R7

1K0

U3B

7

MC33079P(MOT)

14

R8

47KR922K

R26

10K

R27

10K

9

10

5

6

U3C

+

MC33079P(MOT)

+

-

R10

22K

C6

47pF/100V-K

8

U1B

OP275

R28

4K7

R29

4K7

7

D

JP1

R30

220R

2

3

1

XLR/M-RX90602

R49

47R/1W

JP3

FASTON-4.8-LG

C23

100n/63V-K

Rec Out L

C

Chassis

C33

100n/63V-K

C34

100n/63V-K

B

C16

22n/63V_RM5

A

C17

22n/63V_RM5

R50

2K2

R33

220K

C24

10n/63V_RM5

R51

2K2

R34

18K

+

-

R52

4K7

2

-

3

+

U2C

MC33079P(MOT)

C25

10n/63V_RM5

-15V

VCCVEE

4 11

8

U6A

MC33079P(MOT)

10

9

+15V

1

C19

220n/63V_RM5

R53

12K

R54

9K1

R36

8K2

5

+

6

-

C26

1n/63V_RM5

R55

3K9

R56

220R

U2B

7

MC33079P(MOT)

BR2

0R0

R57

18K

6

-

5

+

R39

10K

C27

1n/63V_RM5

R58

11K

7

U6B

MC33079P(MOT)

12

13

U5D

+

-

MC33079P(MOT)

R40

22K

C28

22pF/100V-K

R59

9K1

R60

39K

R43

1K2

14

C22

33n/63V_RM5

R61

36K

R62

39K

C29

3n3/63V_RM5

R65

3K9

10

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by a ny means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 78

3

2

C30

3n3/63V_RM5

R63

82K

9

+

+15V

+

-

-15V

U5A

411

VCCVEE

MC33079P(MOT)

1

8

U6C

MC33079P(MOT)

R44

1K5

5

6

C31

3n3/63V_RM5

12

13

U5B

+

-

MC33079P(MOT)

U6D

+

-

MC33079P(MOT)

B

8

M. Bohlender

M. Bohlender

R47

4K7

R64

4K7

R48

220R

JP2

2

3

1

XLR/M-RX90602

Title:

R66

47R/1W

C32

100n/63V-K

HU0100 - zenAmp Combo

FX-Loop / Redbox

2HU0100-SP-R03-2A A

12.03.2002

13.03.2002

Date:

Rec Out R

Page:

1

A

1

Pages

7

R45

10K

R46

10K

U5C

9

-

10

+

MC33079P(MOT)

66606 St. Wendel / Germany

14

Number: Version: Revision:

Drawn by: Date:

Checked by:

Material: Surface:

Filename: HU0100-SP-R03-2A.sch

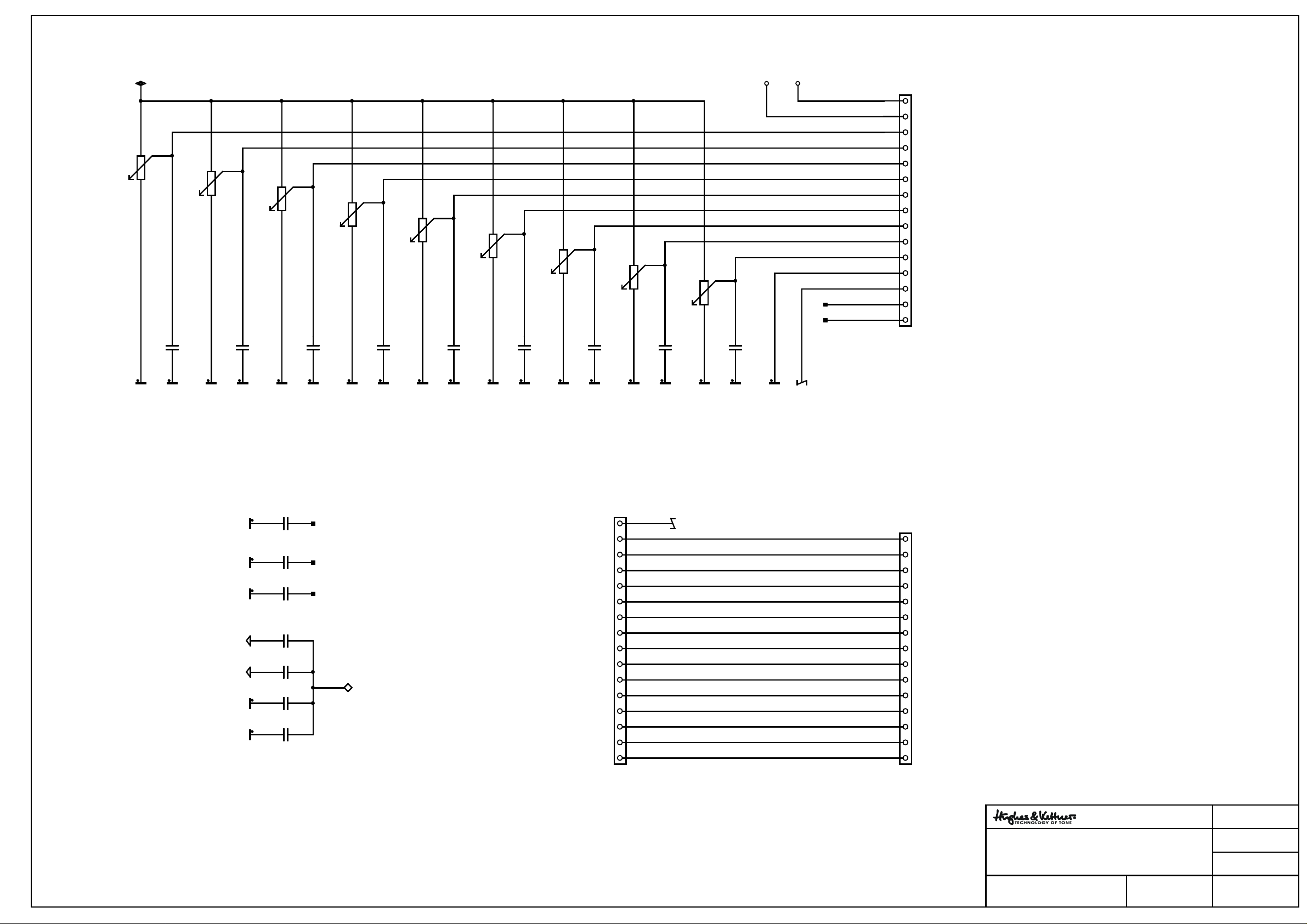

Page 7

Page 8

Page 9

87654321

Codec

Codec.sch

AINL

AINR

AOUTL

AOUTR CODECBUS

D

Hostcontrollerunit

Analog-Input

Analog-Input.sch

STAGEV1

STAGEV2

AVDD

ASEL0

Main-Connector

Main-Connector.sch

AINL

AINR

AOUTL

GNDSTAGE

VSTAGE

TAPLED

C

TAPKEY

AOUTR

ANALOG_IN

HOSTCTRLBUS

PER_BUS

SBUS

ASEL1

AVALOG_IN

VREFHI

APORT

Hostcontrollerunit.sch

CODECBUS

VREFHI

APORT

PER_BUS

HOSTADRBUS

HOSTDATABUS

HOSTCTRLBUS

INTSBUS

LLSBUS

ADDRESSBUS

DATABUS

PeripheralsPowerAndJTAG

PeripheralsPowerAndJTAG.sch

CODECBUS

SPORTBUS1

INTSBUS

DSPandSDRAM

DSPandSDRAM.sch

MEMCTRLBUS

ADRESSBUS

DATABUS

SHCS

Testpoints

Testpoints.sch

DATABUS

HOSTCTRLBUS

MEMCTRLBUS

SHARCRST

/HBR

/HBG

FPBUS

D

C

FlashMemAndResetCircuit

FlashMemAndResetCircuit.sch

HOSTCTRLBUS

HOSTDATABUS

HOSTADRBUS

HOSTRST

RS232-Transceiver

RS232-Transceiver.sch

LLSBUS

SBUS

B

B

A

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

Title:

zenAmp

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

Material: Surface:

Filename:HU0100-SP-R05-1A.sch

M. Bohlender

A. Peter

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Date:

Page:

10

A

1

Pages

Page 10

8765432

1

C46

Analog Filters and Voltage Converters

0..5V Stageboard outputs

0..3V DSP Module

STAGEV1

SVOLT1

D

100n

L2

100uH

R40

10k

R41

6k2

2

3

MC33078D

IC15

1

Voltage Conversion

R42

10k

6

5

C45

DGND

DGND DGND

C48

R45

6k2

STAGEV2

SVOLT2

100n

C47

L3

100uH

R44

10k

2

3

MC33078D

IC16

1

+5V +5V

R46

10k

6

5

R43

10k

MC33078D

IC15B

Filter

R47

10k

MC33078D

IC16B

330n

330n

R82

7

+5V

1k

Emergency Shutdown

APORT0

D

D1

BAR43

DGNDDGND

+5V

3.0V

D7D8

ZMM003ZMM003,3

D2

R83

1k

100n

C49

7

VRH

BAR43

D3

BAR43

Imax = 15mAImax = 12mA

BAR43

D4

DGND

APORT1

VREFHI

C

DGND

ASEL0

ASEL1

DGND DGND

ASEL0

ASEL1

R111

1k

R112

1k

T1

BC847

R98

1k

T2

BC847

R110

R48R49 R50R51

1k

100n

180R330R 220R330R

3.2V

AVDD

AVDD

C39

C

DGNDDGND

AVALOG_IN

+15V

100n100n

B

IC15P

MC33078D

4 8

-15V

+5VA

IC16P

MC33078D

4 8

C62C63

100n 100n

C64 C65

ANALOG[0..8]

+

C99

10u/30V

+

C101

10u/30V

C100

C102

+

10u/30V

+

DGND

10u/30V

ANALOG0

ANALOG1

ANALOG2

ANALOG3

ANALOG4

ANALOG5

ANALOG6

ANALOG7

ANALOG8

100n

100n

100n

C50

C51

C52

DGND DGND DGND

100n

C53

DGND

DGNDDGND

DGND

IC19

12

14

15

11

1

5

2

4

6

10

9

74HCT4052

X0

X1

X2

X3

Y0

Y1

Y2

Y3

INH

A

B

13

X

3

Y

Analog Multiplexer

L4

100uH

L5

100uH

L7

100uH

L8

100uH

L9

100uH

L10

100uH

APORT2

B

APORT3

APORT4

APORT5

APORT6

APORT7

APORT

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Page:

10

A

2

Pages

Title:

APORT[0..7]

zenAmp

Date:

VDD

16

100n

100n

IC19P

A

7

8

VEEVSS

C67

C68

100n

C56

C57

DGND DGND

C55

DGND DGND DGND

DGND

C54

100n

C58

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

M. Bohlender

A. Peter

100n

100n

100n

Material: Surface:

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

Filename:Analog-Input.sch

Page 11

8765432

1

LINE INPUT BUFFERS

Left Channel Input

D

AINL

+5VA

Right Channel Input

AINR

C

AINLAINR

R7

12k

R8

10k

R14

12k

C13

AGND AGND AGND

N$4

+

10u/16V

6

5

N$16

6

5

100n

C14

C8

C10

R5

4k7

MC33078D

IC2B

R12

4k7

MC33078D

IC3B

R15

100p

100p

10k

N$2N$3

7

7

CODECBUS

N$6

R2 R3

22R 4k7

N$5

R9 R10

22R 4k7

SCLK,LRCLK,SDIN,SDOUT,SCL,SDA,AD0,/RST

Serial Interface Bus

Connects Codec with DSP

N$7

N$9

2

3

N$11

2

3

N$11

C7

C11

R6

4k7

MC33078D

IC2

R13

4k7

MC33078D

IC3

100p

100p

OUTPUT BUFFERS

R17

R26

15k

15k

R19

3k3

R16

3k3

R28

3k3

R25

3k3

100p

C15

N$44

N$41

100p

C20

IC4

MC33078D

3

2

1

R18

100R

AOUTL

AOUTLAOUTR

D

N$25

IC4B

MC33078D

5

6

7

N$42

R27

100R

AOUTR

C

R22R23

N$50

N$39

R24

N$1

R4

1

22R

820p

N$8

AUDIO CODEC

IC1

CS4224

20

AINL+

AOUTL+

25

3k3

470p

C19

470p

C18

C9

N$6

19

N$15

N$5

AINL-

17

AINR+

16

AINR-

AOUTL-

AOUTR+

AOUTR-

N$13

R35

SCLK

LRCLK

SDIN

SDOUT

SCL

SDA

AD0

/RST

1k

R11

1

22R

820p

C12

Mastermode

5

SCLK

4

LRCLK

9

SDIN

8

SDOUT

10

SCL/CCLK

11

SDA/CDIN

12

AD0/CS

27

/RST

18

I2C/SPI

XTI

XTO

NC@4

NC@3

NC@2

NC@1

N$49

26

R33

3k3

N$45

N$46

470p

C24

470p

C23

N$47

24

N$48

23

N$10

N$17

Q1

1 2

3

2

11.28MHz

28

15

14

1

40p

C25

40p

C26

DGNDDGNDDGND

N$30 N$33N$38

12k3k3

R21

N$23 N$24

12k

470p

470p

R20

15k

C16

C17

AGNDAGNDAGNDAGNDAGND

R31R32

N$43

12k3k3

R30

N$40

12k

470p

470p

R29

15k

C21

C22

AGNDAGNDAGNDAGNDAGND

DGNDDGND

B

Isolated analog and digital power

supply for codec.

+15V

A

IC18

7805

VI1VO

GND

3

2

100n

C5

+

10u/16V

C30

+5VA

21

VA VD VL

100n

ANALOG DIGITAL

AGND

C6

22

+5V

R34

0R

C1

+

10u/16V

+3,3V

100n

C2

C3

+

10u/16V

100n

C4

3.3V digital I/O

6

DGND

13

7

IC1P

CS4224

DGND

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

AGND

AGND

AGND

+15V

IC2P

MC33078D

4 8

-15V

IC3P

MC33078D

4 8

IC4P

MC33078D

4 8

Power supply for Op.Amps.

100n

100n

C31

C32

100n

100n

C27

C28

100n

C91

+

10u/30V

C92

+

10u/30V

C93C96

++

10u/30V10u/30V

C33

100n

C98

+

10u/30V

C97

+

10u/30V

AGND

C29

Title:

zenAmp

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

M. Bohlender

A. Peter

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Date:

Material: Surface:

Filename:Codec.sch

Page:

10

B

A

3

Pages

Page 12

8765432

1

D

+15V

+5V +3,3V

D

X1

AINL

1

MAINBAORD CONNECTOR

C

AINR

2

AGND

3

AOUTL

4

AOUTR

5

+15V

6

-15V

7

ANALOG0

8

ANALOG1

9

ANALOG2

10

ANALOG3

11

ANALOG4

12

ANALOG5

13

ANALOG6

14

ANALOG7

15

ANALOG8

16

DGND

17

+5V

18

GNDSTAGE

19

VSTAGE

20

TAPLED

21

TAPKEY

22

PBUS0

23

PBUS1

24

PBUS2

25

PBUS3

26

PBUS4

27

PBUS5

28

PBUS6

29

PBUS7

30

CS0

31

CS1

32

CS2

33

DGND

34

+3,3V

35

AINL

AINR

AOUTL

AOUTR

GNDSTAGE

VSTAGE

TAPLED

TAPKEY

ANALOG[0..8]

SBUS

CS[0..2],CSD,CSP[0..1],R/W,LSTRB,/R/W

MISO,MOSI,SSCLK,/SS,CONNECT

PBUS[0..7]

ANALOG_IN

PER_BUS

HOSTCTRLBUS

VSTAGE

MOSI

SVOLT1

MISO

SVOLT2

SSCLK

HSENSE

/SS

GNDSTAGE

X2

STW10

1

2

STAGEBOARD

3

CONNECTOR

4

5

6

7

8

n/c

9

10

TEST SERIAL RS232

INTERFACE

C

PINHD-1X35

DGND

-15V

AGND

B

LINEAR -LOW DROP- 3.3V REGULATOR

+3,3V+5V

470n

IC12

LM3940IT-3.3

VI1VO

GND

2

3

+

C82

33u/16V

C59

DGNDDGNDDGND

A

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

Title:

zenAmp

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

m. Bohlender

A. Peter

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Date:

Page:

10

Material: Surface:

Filename:Main-Connector.sch

B

A

4

Pages

Page 13

8765432

1

/RAS,/CAS,/SDWE,DQM,SDCLK0,SDCLK1,SDCKE,SDA10,/RD,/WR,/SW,/MS[0..3],/BMS

R127

R126

10k

R125

10k

R124

10k

R123

DGND

10k

R122

10k

R121

10k

R120

10k

R119

10k

R118

10k

R117

10k

R116

10k

R115

10k

R114

10k

R113

10k

R99

10k

10k

+3,3V +3,3V +3,3V +3,3V

D

C

R73

4k7

SHCS

B

R72

4k7

ADDR8

ADDR9

ADDR10

ADDR11

ADDR12

ADDR13

ADDR14

ADDR15

ADDR16

ADDR17

ADDR18

ADDR19

ADDR20

ADDR21

ADDR22

ADDR23

R71

R70

4k7

4k7

Single Processor ID

SHARC data and address pins

IC6

ADSP21065L MT48LC4M16

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

ADDR9

ADDR10

ADDR11

ADDR12

ADDR13

ADDR14

ADDR15

ADDR16

ADDR17

ADDR18

ADDR19

ADDR20

ADDR21

ADDR22

ADDR23

195

194

193

190

189

188

185

184

183

180

179

178

175

174

173

171

170

169

166

165

164

162

161

160

143

144

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

ADDR9

ADDR10

ADDR11

ADDR12

ADDR13

ADDR14

ADDR15

ADDR16

ADDR17

ADDR18

ADDR19

ADDR20

ADDR21

ADDR22

ADDR23

28

/BR2

27

/BR1

ID0

ID1

DGND

69

n/c

/SHCS

ACK

56

/SBTS

55

/CS

152

BSEL

Host booting enabled

DGND

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

DATA16

DATA17

DATA18

DATA19

DATA20

DATA21

DATA22

DATA23

DATA24

DATA25

DATA26

DATA27

DATA28

DATA29

DATA30

DATA31

/RAS

/CAS

/SDWE

DQM

SDCLK0

SDCLK1

SDCKE

SDA10

/RD

/WR

/SW

/MS0

/MS1

/MS2

/MS3

/BMS

82

83

84

86

87

88

90

91

92

96

97

98

100

101

104

107

108

109

111

112

113

116

117

118

121

122

123

126

127

128

132

133

42

43

44

46

37

34

47

48

59

58

64

70

71

74

75

153

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

DATA16

DATA17

DATA18

DATA19

DATA20

DATA21

DATA22

DATA23

DATA24

DATA25

DATA26

DATA27

DATA28

DATA29

DATA30

DATA31

/RAS

/CAS

/SDWE

DQM

SDCLK0

SDCLK1

SDCKE

SDA10

/RD

/WR

/SW

/MS0

/MS1

/MS2

/MS3

/BMS

+3,3V +3,3V +3,3V +3,3V +3,3V +3,3V +3,3V +3,3V

R62

R63

R64

R65

R66

R67

R68

4k7

4k7

4k7

4k7

4k7

4k7

4k7

R69

4k7

SDCLK0

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

ADDR9

SDA10

ADDR11

ADDR12

ADDR13

SDCKE

/MS0

/SDWE

/CAS

/RAS

DQM

SDCLK1

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

ADDR9

SDA10

ADDR11

ADDR12

ADDR13

SDCKE

/MS0

/SDWE

/CAS

/RAS

DQM

SDRAM

Low Word

IC7

38

CLK

23

A0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10

35

A11

20

BA0

21

BA1

37

CKE

19

/CS

16

/WE

17

/CAS

18

/RAS

15

DQML

39

DQMH

SDRAM

optional high word

IC8

MT48LC4M16

38

CLK

23

A0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10

35

A11

20

BA0

21

BA1

37

CKE

19

/CS

16

/WE

17

/CAS

18

/RAS

15

DQML

39

DQMH

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

DATA16

DATA17

DATA18

DATA19

DATA20

DATA21

DATA22

DATA23

DATA24

DATA25

DATA26

DATA27

DATA28

DATA29

DATA30

DATA31

ADDR[0..23]

DATA[0..31]

MEMCTRLBUS

ADRESSBUS

DATABUS

D

C

B

+3,3V

1

14

3

9

43

49

VDD VDD

ISOLATED

A

VSS VSS

6

12

46

52

DGND

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

27

100n

IC7P

100n

MT48LC4M16

C35

C36

41

28

54

3

9

VDD VDD

ISOLATED

VSS VSS

6

12

1

14

43

49

46

52

27

100n

IC8P

100n

MT48LC4M16

C37

C38

41

28

54

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

M. Bohlender

A. Peter

Title:

zenAmp

Date:

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Page:

10

A

5

Pages

Material: Surface:

Filename:DSPandSDRAM.sch

Page 14

8765432

1

D

HOSTDATABUS

HOSTADRBUS

HOSTCTRLBUS

C

B

HDATA[0..15]

HADDR[0..19]

CS[0..2],CSD,CSP[0..1],R/W,LSTRB,/R/W

+3,3V +3,3V

R84

10k

CSP0

JP1

1 2

3 4

CSD

PINHD-2X2

R81

10k

HADDR1

HADDR2

HADDR3

HADDR4

HADDR5

HADDR6

HADDR7

HADDR8

HADDR9

HADDR10

HADDR11

HADDR12

HADDR13

HADDR14

HADDR15

HADDR16

HADDR17

HADDR18

HADDR19

/R/W

R/W

CS_FLSH

HADDR1

HADDR2

HADDR3

HADDR4

HADDR5

HADDR6

HADDR7

HADDR8

HADDR9

HADDR10

HADDR11

HADDR12

HADDR13

HADDR14

HADDR15

HADDR16

LSTRB

HADDR0

/R/W

R/W

CS_SR

IC22

AM29LV800BB-12

25

24

23

22

21

20

19

18

8

7

6

5

4

3

2

1

48

17

16

26

28

11

12

47

IC21

CY62126VLL-70Z

5

4

3

2

1

44

43

42

27

26

25

24

21

20

19

18

39

40

41

17

6

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

/CE

/OE

/WE

/RESET

/BYTE

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

/BLE

/BHE

/OE

/WE

/CE

D15/A-1

RY/BY

D10

D11

D12

D13

D14

D10

D11

D12

D13

D14

D15

29

D0

31

D1

33

D2

35

D3

38

D4

40

D5

42

D6

44

D7

30

D8

32

D9

34

36

39

41

43

45

15

7

D0

8

D1

9

D2

10

D3

13

D4

14

D5

15

D6

16

D7

29

D8

30

D9

31

32

35

36

37

38

In der Serie nicht bestückt!

FLASH

HDATA0

HDATA1

HDATA2

HDATA3

HDATA4

HDATA5

HDATA6

HDATA7

HDATA8

HDATA9

HDATA10

HDATA11

HDATA12

HDATA13

HDATA14

HDATA15

n/c

DEBUG

SRAM

HDATA0

HDATA1

HDATA2

HDATA3

HDATA4

HDATA5

HDATA6

HDATA7

HDATA8

HDATA9

HDATA10

HDATA11

HDATA12

HDATA13

HDATA14

HDATA15

+3,3V

100n

C44

DGND

DGND

+3,3V

37

IC22P

AM29LV800BB-12

27

46

IC11

3

VCC

RESET

2

GND

MAX809S

100n

C81

Reset Controller

-- might be replaced during layout

1

IC21P

CY62126VLL-70Z CY62126VLL-70Z

12 11

/HOSTRST

HOSTRST

TP124

IC21T

34 33

100n

C90

IC13P

SN74AHC1G125DB

3 5

100n

C69

D

C

B

IC13

SN74AHC1G125DB

/SHCS

R/W

A

1

/OE

2

A

4

Y

/WR

Title:

zenAmp

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

M. Bohlender

A. Peter

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Date:

Page:

10

A

6

Pages

Material: Surface:

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

Filename:FlashMemAndResetCircuit.sch

Page 15

8765432

1

LLSBUS

D

INTSBUS

C

PER_BUS

CODECBUS

APORT

B

VREFHI

LMOSI,LSCLK,L/SS,LMISO

+5V

+3,3V

PINHD-1X5

5

4

3

2

1

JP6

DGND

SHSIN,SHSOUT,SHSCLK,SHFS

12

5MHz

22p

C86

PBUS[0..7]

SCLK,LRCLK,SDIN,SDOUT,SCL,SDA,AD0,/RST

APORT[0..7]

22p

C87

DGNDDGND

100n

C88

+3,3V

Q2

DGNDDGND

C89

R100

+

1M

10u

PINHD-1X3

SHSOUT

SHSIN

ORXD

OTXD

LMISO

LMOSI

LSCLK

L/SS

SHSIN

SHSOUT

+3,3V

BKGD

/RESET

BKGD

PBUS0

PBUS1

PBUS2

PBUS3

PBUS4

PBUS5

PBUS6

PBUS7

SCL

SDA

AD0

/RST

ASEL0

ASEL1

SHARCRST

TAPLED

/HBG

REDY

TAPKEY

SHSIN

SHSOUT

SHFS

SHSCLK

SENSE

APORT0

APORT1

APORT2

APORT3

APORT4

APORT5

APORT6

APORT7

VRH

X4

3

2

1

R103 R106

1k 100R

JP5

DGND DGND

DEBUG INTERFACE

n/c

n/c

1 2

3 4

5 6

PINHD-2X3

n/c

DGND

100

101

102

103

104

105

106

107

108

109

110

111

112

+3,3V

97

98

99

44

40

47

46

19

75

76

77

78

81

82

83

84

3

4

5

6

7

8

9

10

87

88

89

90

91

92

93

94

85

86

IC9

MC68HC812

PS0

PS1

PS2

PS3

PS4

PS5

PS6

PS7

XFC

/RESET

XTAL

EXTAL

BKGD

PH0

PH1

PH2

PH3

PH4

PH5

PH6

PH7

PT0

PT1

PT2

PT3

PT4

PT5

PT6

PT7

PJ0

PJ1

PJ2

PJ3

PJ4

PJ5

PJ6

PJ7

PAD0

PAD1

PAD2

PAD3

PAD4

PAD5

PAD6

PAD7

VRH

VRL

BAR43

D5

RxD0

TxD0

RxD1

TxD1

SDI/MISO

SDO/MOSI

SCK

/SS

/TAGHI

IOC0

IOC1

IOC2

IOC3

IOC4

IOC5

IOC6

IOC7

KWJ0

KWJ1

KWJ2

KWJ3

KWJ4

KWJ5

KWJ6

KWJ7

AVDD

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PG0

PG1

PG2

PG3

PG4

PG5

PD0/KWD0

PD1/KWD1

PD2/KWD2

PD3/KWD3

PD4/KWD4

PD5/KWD5

PD6/KWD6

PD7/KWD7

PC0

PC1

PC2

PC3

PC4

PC5

PC6

PC7

CS0

CS1

CS2

CS3

CSD

CSP0

CSP1

XIRQ

IRQ

R/W

LSTRB

ECLK

MODA

MODB

ARST

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

ADDR9

ADDR10

ADDR11

ADDR12

ADDR13

ADDR14

ADDR15

ADDR16

ADDR17

ADDR18

ADDR19

ADDR20

ADDR21

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

PF0

PF1

PF2

PF3

PF4

PF5

PF6

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

/HOSTRST

/RESET

AVDD

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

11

12

13

16

17

18

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

68

69

70

71

72

73

74

36

37

38

39

48

49

50

51

PINHD-1X2

2

1

PINHD-1X2

2

1

HADDR0

HADDR5

HADDR6

HADDR7

HADDR8

HADDR9

HADDR10

HADDR11

HADDR12

HADDR13

HADDR14

HADDR15

HADDR16

HADDR17

HADDR18

HADDR19

FPC7

FPC8

HDATA0 HDATA0

HDATA1 HDATA1

HDATA2 HDATA2

HDATA3 HDATA3

HDATA4 HDATA4

HDATA5 HDATA5

HDATA6 HDATA6

HDATA7 HDATA7

HDATA8

HDATA9

HDATA10

HDATA11

HDATA12

HDATA13

HDATA14

HDATA15

CS0

CS1

CS2

/SHCS

CSD

CSP0

CSP1

REDY

R/W

LSTRB

/HBR

TEST

R107

4k7

R101

4k7

+3,3V

R/W

HADDR0HADDR1

HADDR1HADDR2

HADDR2HADDR3

HADDR3HADDR4

HADDR4

HADDR5

HADDR6

HADDR7

HDATA8

HDATA9

HDATA10

HDATA11

HDATA12

HDATA13

HDATA14

HDATA15

/SHCS

IC5

NC7S04

JP3

2 4

JP4

R102

4k7

DGND

HADDR[0..19]

HOSTADRBUS

IC17B

11

A1

13

15

17

19

Y1

A2

Y2

A3

Y3

A4

Y4

G

ADDR0

9

ADDR1

7

ADDR2

5

ADDR3

3

ADDRESS

BUS

BRIDGE

D

74LCX244

IC17A

ADDR4

18

ADDR5

16

ADDR6

14

ADDR7

12

ADDR[0..23]

ADDRESSBUS

+3,3V

2

4

6

8

1

74LCX244

A1

Y1

A2

Y2

A3

Y3

A4

Y4

G

IC10

2

A1

A2

A3

A4

A5

A6

A7

A8

DIR

G

B1

B2

B3

B4

B5

B6

B7

B8

3

4

5

6

7

8

9

1

19

DATA0

18

DATA1

17

DATA2

16

DATA3

15

DATA4

14

DATA5

13

DATA6

12

DATA7

11

DATA

BUS

BRIDGE

C

74LVX245

IC14

2

A1

A2

A3

A4

A5

A6

A7

A8

DIR

G

B1

B2

B3

B4

B5

B6

B7

B8

3

4

5

6

7

8

9

1

19

DATA8

18

DATA9

17

DATA10

16

DATA11

15

DATA12

14

DATA13

13

DATA14

12

DATA15

11

DATA[0..31]

DATABUS

74LVX245

B

CS[0..2],CSD,CSP[0..1],R/W,LSTRB,/R/W

/R/W

+3,3V

TEST

HDATA[0..15]

HOSTDATABUS

HOSTCTRLBUS

TP132

1

IC5P

NC7S04

3 5

100n

C66

R108

D6

1k

LTL907

VCC

+

C103

C104

C105

C106

A

1u

1u

1u

IC14P

1u

GND

+

+

+

100n

10 20

C85

VCC

IC10P

10 20

GND

100n

C84

VCC

IC17P

10 20

GND

100n

C61

100n

C60

100n

C43

100n

C42

100n

C41

2

42

79

VDD

DIGITAL ANLG.

VSS

1

41

80

14

9596

43

AVDD

IC9P

100n

MC68HC812

AVSS

15

45

C40

DGNDDGND

DGND DGND

Title:

zenAmp

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

M. Bohlender

A. Peter

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Date:

Page:

10

A

7

Pages

Material: Surface:

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

Filename:Hostcontrollerunit.sch

Page 16

8765432

1

+3,3V

R97

10k

R96

10k

R95

10k

R94

10k

n/c

n/c

151

149

148

147

5

6

16

17

SPORTS

IC6S

ADSP21065L

DR00

DR01

DR10

DR11

IC6J

ADSP21065L

TCK

TMS

TDI

/TRST

DT00

DT01

TCLK0

RCLK0

TFS0

RFS0

DT10

DT11

TCLK1

RCLK1

TFS1

RFS1

TDO

/EMU

11

12

8

4

7

2

22

23

19

15

18

13

146

145

n/c

R37

R38

R39

TDO

/EMU

SHSCLK

SHFS

100R

100R

100R

SDINSDOUT

SCLKSDA

LRCLK

n/c

n/c

D

CODECBUS

SHARCRST

SHARC Masterclock

33MHz for KS264

30MHz for KS240

HO-25B 30MHz

100n

C80

C

SCLK,LRCLK,SDIN,SDOUT,SCL,SDA,AD0,/RST SHSIN,SHSOUT,SHSCLK,SHFS

+3,3V +3,3V +3,3V +3,3V +3,3V+3,3V

R74

R75

R76

R77

R78

+3,3V

8

VCC

5

OUT

Y1

GND

4

R80

+3,3V

4k7

4k7

4k7

4k7

SHARCRST

DGND

R128

10k

/HBR

+3,3V

R86

R87

10k

10k

4k7

R88

n/c

4k7

10k

205

206

207

157

30

31

38

39

40

65

R89

IC6I

ADSP21065L

/IRQ0

/IRQ1

/IRQ2

/RESET

CLKIN

/XTAL

/DMAR1

/DMAR2

/HBR

/CPA

10k

/PWMEVENT0

/PWMEVENT1

R90

10k

SCL

FLAG0

FLAG1

FLAG2

FLAG3

FLAG4

FLAG5

FLAG6

FLAG7

FLAG8

FLAG9

FLAG10

FLAG11

/DMAG1

/DMAG2

/HBG

REDY

BMSTR

R91

10k

SDA

R92

197

198

199

201

138

137

136

134

80

79

78

76

26

24

50

51

52

63

53

10k

n/c

n/c

n/c

n/c

AD0

R93

SCL

AD0

/RST

FPC4

FPC5

FPC6

FPC7

FPC8

FPC9

FPC10

FPC11

/HBG/HBR

REDY

10k

+3,3V

R85

/RST

CODEC control

optional by SHARC or Host

Connections between SHARC and Host

for future purposes.

330R

/HBG

INTSBUS

SPORTBUS1

SCLK,LRCLK,SDIN,SDOUT,SCL,SDA,AD0,/RST

SHSIN SHSOUT

Host SPORT

R36

100R

CODEC SPORT

TCK,TMS,TDI,/TRST,TDO,/EMU

TCK

TMS

TDI

/TRST

D

C

FPC4

FPC5

FPC6

FPC7

FPC8

FPC9

FPBUS

FPC10

FPC[4..11]

FPC11

B

+3,3V

IC6P

ADSP21065L

3

A

10

SHARC Power Supply

192021293236455461666777859395105

VDD

GND

14

253335414957606268727381899499

106

110

114

120

119

124

125

130

129

131

135

140

139

141

150

156

154

158

155

163

159

172

167

176

168

182

177

191

181

192

186

200

187

196

204

100n

C76

100n

C77

100n

C78

100n

C79

DGND

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

+3,3V

R61

4k7

DGND

JTAG Interface

JP2

nc

nc

nc

PINHD-2X7

1 2

3 4

5 6

7 8

9 10

11 12

13 14

/EMU

nc

TMS

TCK

/TRST

TDI

TDO

Title:

zenAmp

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

M. Bohlender

A. Peter

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Date:

Page:

10

8

Pages

B

A

Material: Surface:

Filename:PeripheralsPowerAndJTAG.sch

Page 17

87654321

D

RS232 Transceiver

Stage- or Switchboard

Nullmodem Port

IC20

n/c

n/c

MAX3243CAI

28

24

1

2

23

22

21

20

19

18

17

16

15

C1+

C1-

C2+

C2-

FON

/FOFF

/INVALID

R2BOUT

R1OUT

R2OUT

R3OUT

R4OUT

R5OUT

T1IN14T1OUT

T2IN13T2OUT

T3IN12T3OUT

R1IN

R2IN

R3IN

R4IN

R5IN

C73

27

V+

C74

3

V-

100n

100n

DGND

R109

4k7

R52

R53

R54

R56

47R

47R

47R

47R

4

5

6

7

8

9

10

11

n/c

MOSI

SSCLK

/SSHSENSE

MISO

MISO,MOSI,SSCLK,/SS,CONNECT

SBUS

+3,3V +3,3V

C71

C72

R58

R59

LLSBUS

LMOSI,LSCLK,L/SS,LMISO

C

LMOSI

LSCLK

L/SS

LMISO

4k7

4k7

100n

100n

SENSE

D

C

DGND

+3,3V

B

100n

IC20P

MAX3243CAI

25 26

C75

DGND

A

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

Title:

zenAmp

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

M. Bohlender

A. Peter

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Date:

Page:

10

Material: Surface:

Filename:RS232-Transceiver.sch

B

A

9

Pages

Page 18

TESTPIN

+5V +5VA +3,3V

87654321

+15V

/RAS

/CAS

/SDWE

DQM

D

SDCLK0

SDCLK1

SDCKE

SDA10

/RD

/WR

/SW

/MS0

/MS1

/MS2

/MS3

/BMS

/HBR

/HBG

C

/SHCS

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

TP16

TP17

TP18

TP19

B

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

DATA16

DATA17

DATA18

DATA19

DATA20

DATA21

DATA22

DATA23

DATA24

DATA25

DATA26

DATA27

DATA28

DATA29

DATA30

DATA31

TP21

TP22

TP23

TP24

TP25

TP26

TP27

TP28

TP29

TP30

TP31

TP32

TP33

TP34

TP35

TP36

TP37

TP38

TP39

TP40

TP41

TP42

TP43

TP44

TP45

TP46

TP47

TP48

TP49

TP50

TP51

TP52

CS0

CS1

CS2

/SHCS

CSD

CSP0

CSP1

R/W

/R/W

LSTRB

TP121

TP122

TP123

TP125

TP126

TP127

TP128

TP129

TP130

TP131

-15V

TP77

TP78

TP80

TP81

TP83

D

C

B

HOSTCTRLBUS

DATABUS

MEMCTRLBUS

DGND

Kondensator nicht bestückt

A

C?

100n

CS[0..2],CSD,CSP[0..1],R/W,LSTRB,/R/W

DATA[0..31]

/RAS,/CAS,/SDWE,DQM,SDCLK0,SDCLK1,SDCKE,SDA10,/RD,/WR,/SW,/MS[0..3],/BMS

Z1

HALTEBOLZEN-LG

All rights reserved. No part of this schematic may be reproduced, stored in a retrieval system, transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

1 2 3 4 5 6 7 8

Title:

zenAmp

66606 St. Wendel / Germany

Number: Version: Revision:

Drawn by: Date:

Checked by:

M. Bohlender

A. Peter

1HU0100-SP-R05-1A A

03.09.2001

04.09.2001

Date:

Page:

10

Material: Surface:

Filename:Testpoints.sch

A

10

Pages

Page 19

Schurter CE30.6100.151

Power Switch

Power TransformerVoltage Selector

115V

Length for Power Switch

Cables = 200mm

red

L

N

A

B

3

black

white

4

blue

black

230V

6

10

100V

115V

5

7

8

9

white

brown

red

blue

100V

0V

115V

23V/2,0A

0V

23V/2,0A

10V/1,5A

0V

0V

Faston 4,8mm insulated

Faston 4,8mm insulated,

with 2nd 4,8mm pin

Magdeburger Straße 8

66606 St. Wendel

Germany

Title:

Drawn:

Alexander Peter

ZenTrix Power Transformer 100/115/230V wiring

Revision: Checked: Date :

1

Drawing Number. :

ZT_SO01_01

11-May-01

Page 20

Pin 1

Farbader

D-SUB 9pol Buchse (DIN 41 652)

(z.B. Repro 09 66 118 7500)

Zugentlastungsbügel

(z.B. Repro 09 66 108 0000)

Flachbandleitung AWG28/7, grau,

RM 1.27mm, 9 oder 10polig (wählbar),

rote Farbmarkierung für Pin 1

150mm

z.B.

Repro

09 18 009 700

bzw.

09 18 010 700

Pin 1

Magdeburger Straße 8

66606 St. Wendel

Germany

Bezeichnung:

Zentrix Stagboardschnittstellenkabel, 9pol DSUB auf 10pol Pfostenfeld

Gezeichnet von:

Alexander Peter

Harting SEK18 (DIN 41 651) 10pol

(z.B. Repro 09 18 510 7 803)

Zeichnungsnummer :

ZT_SO02_01

Revision: Geprüft: Datum :

1

11. Mai 2001

Loading...

Loading...