Page 1

To all our customers

Information regarding change of names mentioned

within this document, to Renesas Technology Corp.

On April 1st 2003 the following semiconductor operations were transferred to

Renesas Technology Corporation: operations covering microcomputer, logic,

analog and discrete devices, and memory chips other than DRAMs (flash

memory, SRAMs etc.).

Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other

Hitachi brand names are mentioned in the document, these names have all

been changed to Renesas Technology Corporation.

Except for our corporate trademark, logo and corporate statement, no

changes whatsoever have been made to the contents of the document, and

these changes do not constitute any alteration to the contents of the

document itself.

Thank you for your understanding.

Renesas Technology Home Page: www.renesas.com

Renesas Technology Corp.

April 1, 2003

Renesas Technology Corp.

Page 2

SuperH™ RISC Engine

SH7032 and SH7034

HD6417032, HD6477034,

HD6437034, HD6417034

HD6437034B, HD6417034B

Hardware Manual

ADE-602-062E

Rev. 6.0

9/18/02

Hitachi, Ltd.

Page 3

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party’s

rights, including intellectual property rights, in connection with use of the information

contained in this document.

2. Products and product specifications may be subject to change without notice. Confirm that you

have received the latest product standards or specifications before final design, purchase or

use.

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability.

However, contact Hitachi’s sales office before using the product in an application that

demands especially high quality and reliability or where its failure or malfunction may directly

threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear

power, combustion control, transportation, traffic, safety equipment or medical equipment for

life support.

4. Design your application so that the product is used within the ranges guaranteed by Hitachi

particularly for maximum rating, operating supply voltage range, heat radiation characteristics,

installation conditions and other characteristics. Hitachi bears no responsibility for failure or

damage when used beyond the guaranteed ranges. Even within the guaranteed ranges,

consider normally foreseeable failure rates or failure modes in semiconductor devices and

employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi

product does not cause bodily injury, fire or other consequential damage due to operation of

the Hitachi product.

5. This product is not designed to be radiation resistant.

6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document

without written approval from Hitachi.

7. Contact Hitachi’s sales office for any questions regarding this document or Hitachi

semiconductor products.

Page 4

Preface

The SH7032 and SH7034 are microprocessors that integrate peripheral functions necessary for

system configuration with a 32-bit internal architecture SH1-DSP CPU as its core.

The SH7032 and SH7034's on-chip peripheral functions include an interrupt controller, timers,

serial communication interfaces, a user break controller (UBC), a bus state controller (BSC), a

direct memory access controller (DMAC), and I/O ports, making it ideal for use as a

microcomputer in electronic devices that require high speed together with low power

consumption.

Intended Readership: This manual is intended for users undertaking the design of an application

system using the SH7032 and SH7034. Readers using this manual require a

basic knowledge of electrical circuits, logic circuits, and microcomputers.

Purpose: The purpose of this manual is to give users an understanding of the hardware

functions and electrical characteristics of the SH7032 and SH7034. Details

of execution instructions can be found in the SH-1, SH-2, SH-DSP

Programming Manual, which should be read in conjunction with the present

manual.

Using this Manual:

• For an overall understanding of the SH7032 and SH7034's functions

Follow the Table of Contents. This manual is broadly divided into sections on the CPU, system

control functions, peripheral functions, and electrical characteristics.

• For a detailed understanding of CPU functions

Refer to the separate publication SH-1, SH-2, SH-DSP Programming Manual.

Note on bit notation: Bits are shown in high-to-low order from left to right.

Related Material: The latest information is available at our Web Site. Please make sure that you

have the most up-to-date information available.

http://www.hitachisemiconductor.com/

Page 5

User's Manuals on the SH7032 and SH7034:

Manual Title ADE No.

SH7032 and SH7034 Hardware Manual This manual

SH-1, SH-2, SH-DSP Programming Manual ADE-602-085

Users manuals for development tools:

Manual Title ADE No.

C/C++ Complier, Assembler, Optimized Linkage Editor User's Manual ADE-702-304

Simulator Debugger Users Manual ADE-702-266

Hitachi Embedded Workshop Users Manual ADE-702-275

Application Note:

Manual Title ADE No.

C/C++ Complier ADE-502-046

Page 6

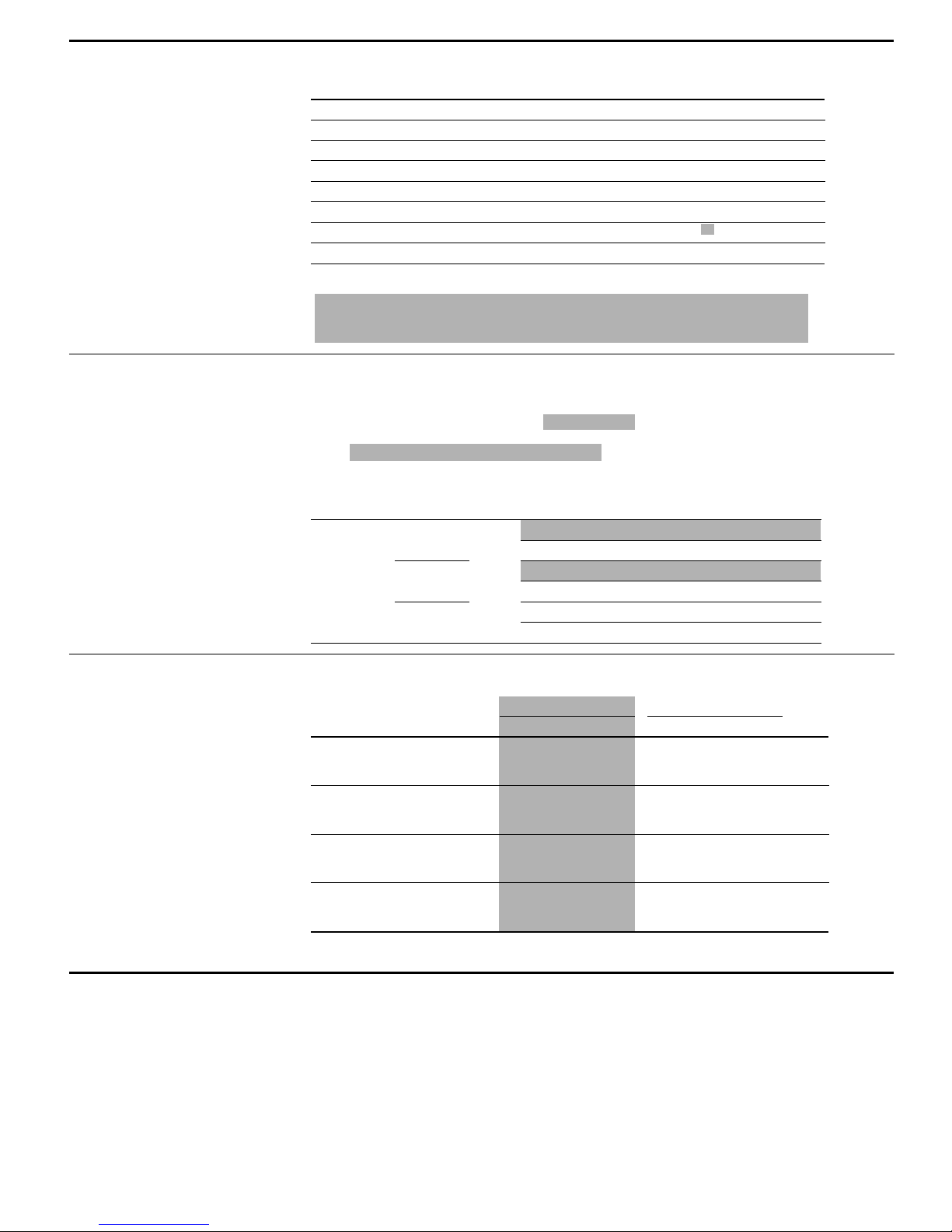

Organization of This Manual

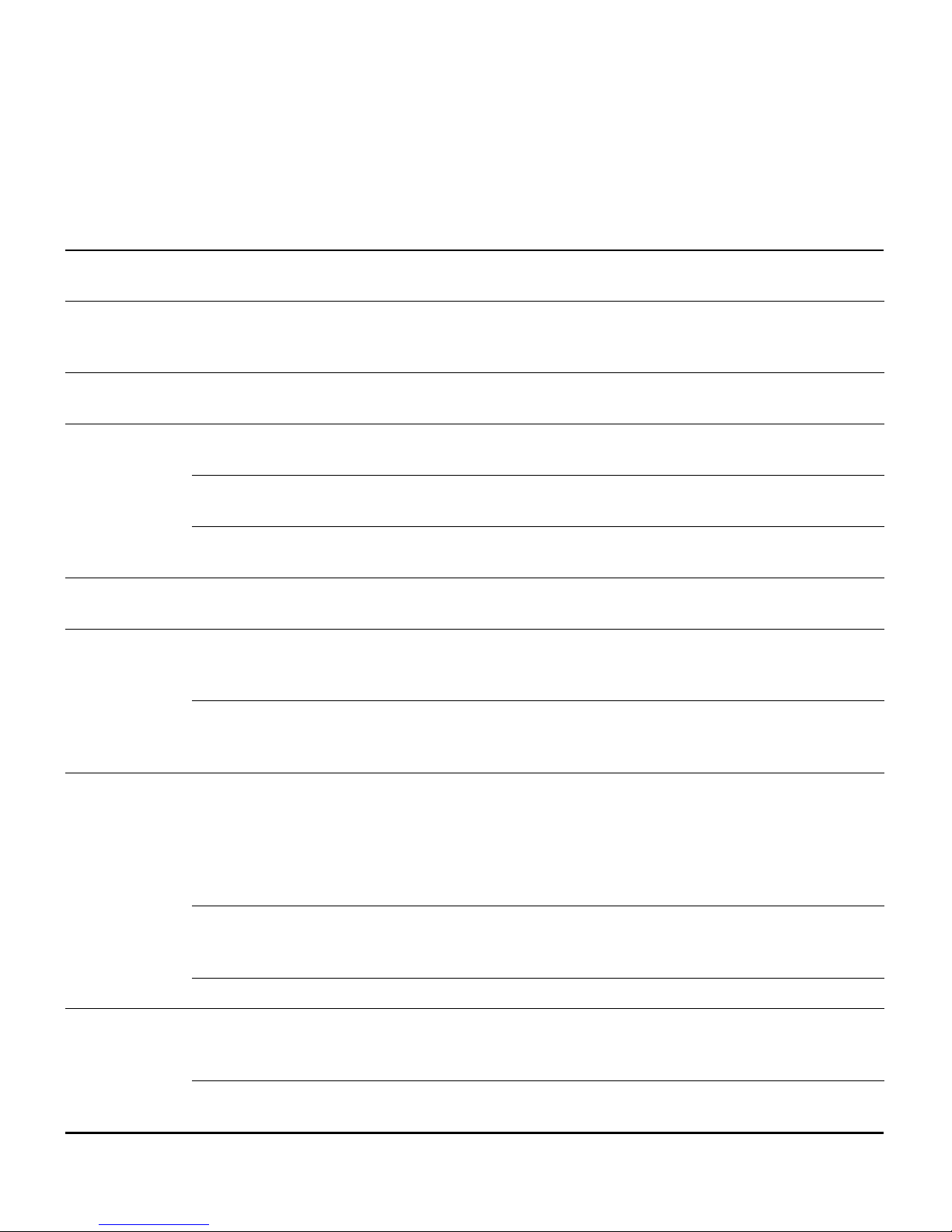

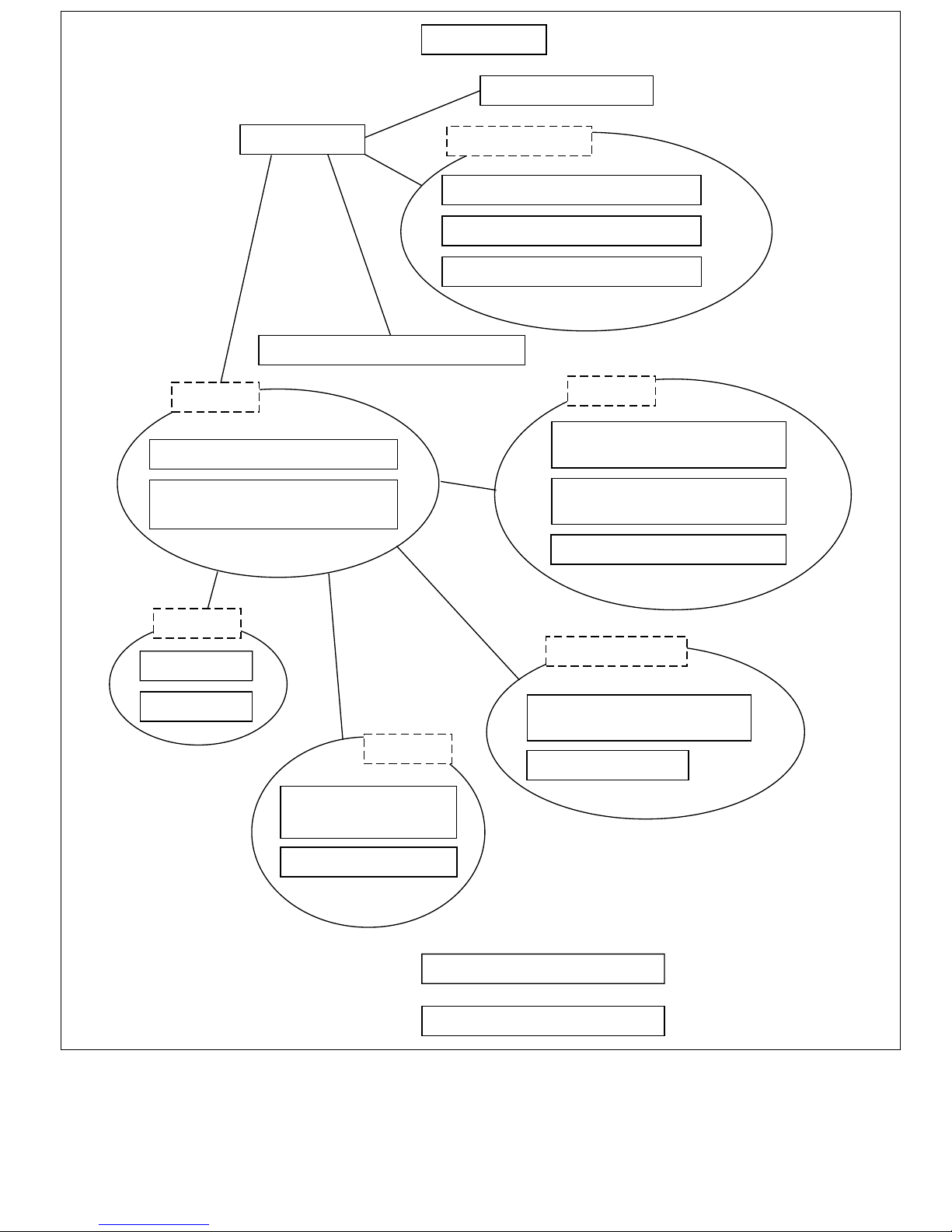

Table 1 describes how this manual is organized. Figure 1 shows the relationships between the

sections within this manual.

Table 1 Manual Organization

Abbrevi-

Category Section Title

Overview 1. Overview — Features, internal block diagram, pin

CPU 2. CPU CPU Register configuration, data structure.

ation Contents

layout, pin functions

instruction features, instruction types,

instruction lists

Operating

Modes

Internal

Modules

Clock 7. Clock Pulse

Buses 8. Bus State

Timers 10. 16-Bit Integrated

3. Operating Modes — MCU mode, PROM mode

4. Exception

Handling

5. Interrupt

Controller

6. User Break

Controller

Generator

Controller

9. Direct Memory

Access

Controller

Timer Pulse Unit

— Resets, address errors, interrupts, trap

instructions, illegal instructions

INTC NMI interrupts, user break interrupts, IRQ

interrupts, on-chip module interrupts

UBC Break address and break bus cycle

selection

CPG Crystal pulse generator, duty correction

circuit

BSC Division of memory space, DRAM

interface, refresh, wait state control, parity

control

DMAC Auto request, external request, on-chip

peripheral module request, cycle steal

mode, burst mode

ITU Waveform output mode, input capture

function, counter clear function, buffer

operation, PWM mode, complementary

PWM mode, reset synchronized mode,

synchronized operation, phase counting

mode, compare match output mode

11. Programmable

Timing Pattern

Controller

12. Watchdog Timer WDT Watchdog timer mode, interval timer mode

Data

Processing

13. Serial

Communication

Interface

14. A/D Converter A/D Single mode, scan mode, activation by

TPC Compare match output triggers, non-

overlap operation

SCI Asynchronous mode, synchronous mode,

multiprocessor communication function

external trigger

Page 7

Table 1 Manual Organization (cont)

Category Section Title

Abbreviation Contents

Pins 15. Pin Function

PFC Pin function selection

Controller

16. Parallel I/O

I/O I/O ports

Ports

Memory 17. ROM ROM PROM mode, high-speed programming

system

18. RAM RAM On-chip RAM

Power-Down

State

Electrical

Char act er i s t i c s

19. Power-Down

State

20. Electrical

Characteristics

— Sleep mode, standby mode

— Absolute maximum ratings, AC

characteristics, DC characteristics,

operation timing

Page 8

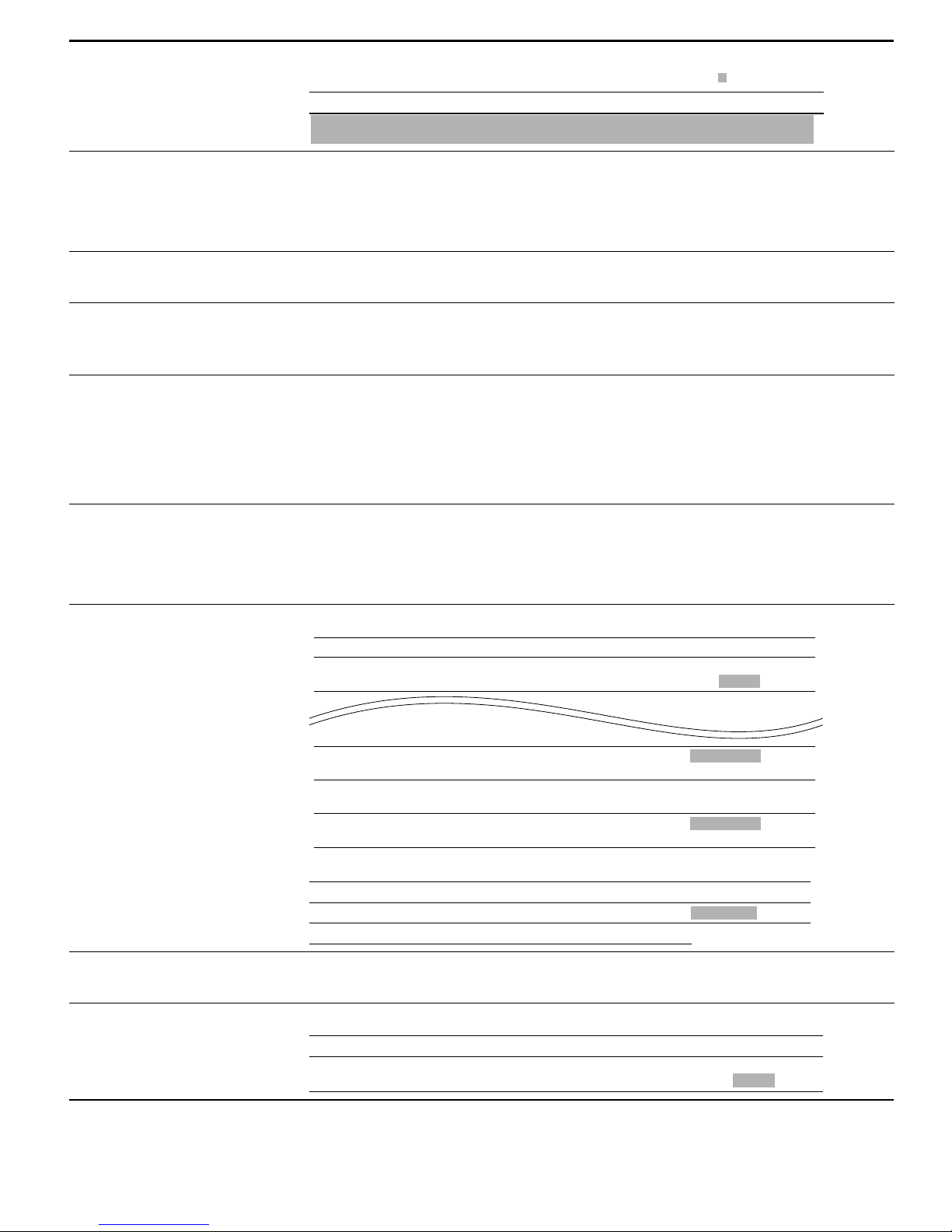

1. Overview

3. Operating modes

2. CPU

7. Clock pulse generator (CPG)

Buses

8. Bus state controller (BSC)

9. Direct memory access

controller (DMAC)

On-chip modules

4. Exception handling

5. Interrupt controller (INTC)

6. User break controller (UBC)

Timers

10. 16-bit integrated timer

pulse unit (ITU)

11. Programmable timing

pattern controller (TPC)

12. Watchdog timer (WDT)

Memory

17. ROM

18. RAM

Data processing

13. Serial communication

interface (SCI)

Pins

14. A/D converter

15. Pin function

controller (PFC)

16. Parallel I/O ports

19. Power-down state

20. Electrical characteristics

Figure 1 Manual Organization

Page 9

Addresses of On-Chip Peripheral Module Registers

The on-chip peripheral module registers are located in the on-chip peripheral module space (area

5: H'5000000–H'5FFFFFF), but since the actual register space is only 512 bytes, address bits

A23–A9 are ignored. 32k shadow areas in 512 byte units that contain exactly the same contents as

the actual registers are thus provided in the on-chip peripheral module space.

In this manual, register addresses are specified as though the on-chip peripheral module registers

were in the 512 bytes H'5FFFE00–H'5FFFFFF. Only the values of the A27–A24 and A8–A0 bits

are valid; the A23–A9 bits are ignored. When area H'5000000–H'50001FF is accessed, for

example, the result will be the same as when area H'5FFFE00–H'5FFFFFF is accessed. For more

details, see Section 8.3.5, Area Descriptions: Area 5.

Page 10

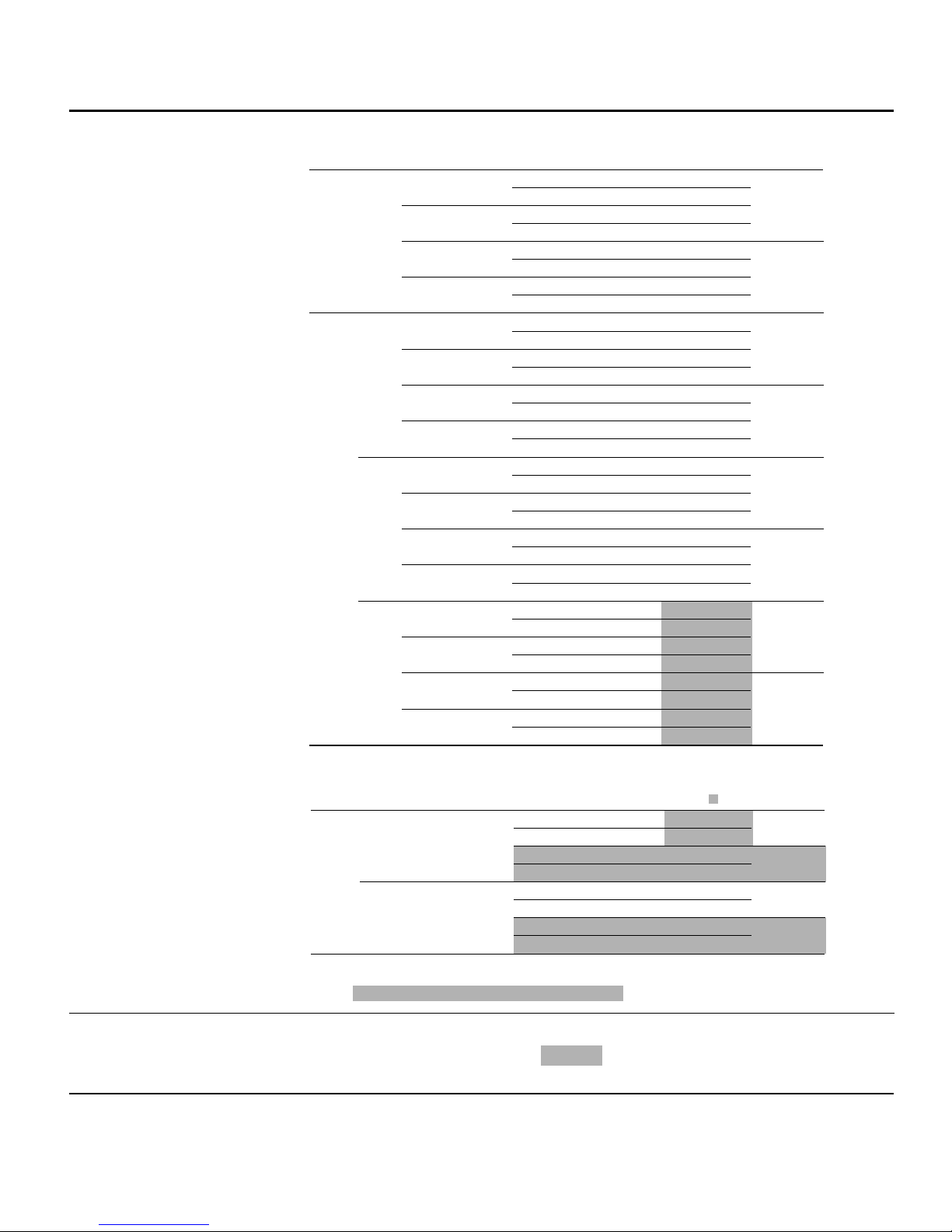

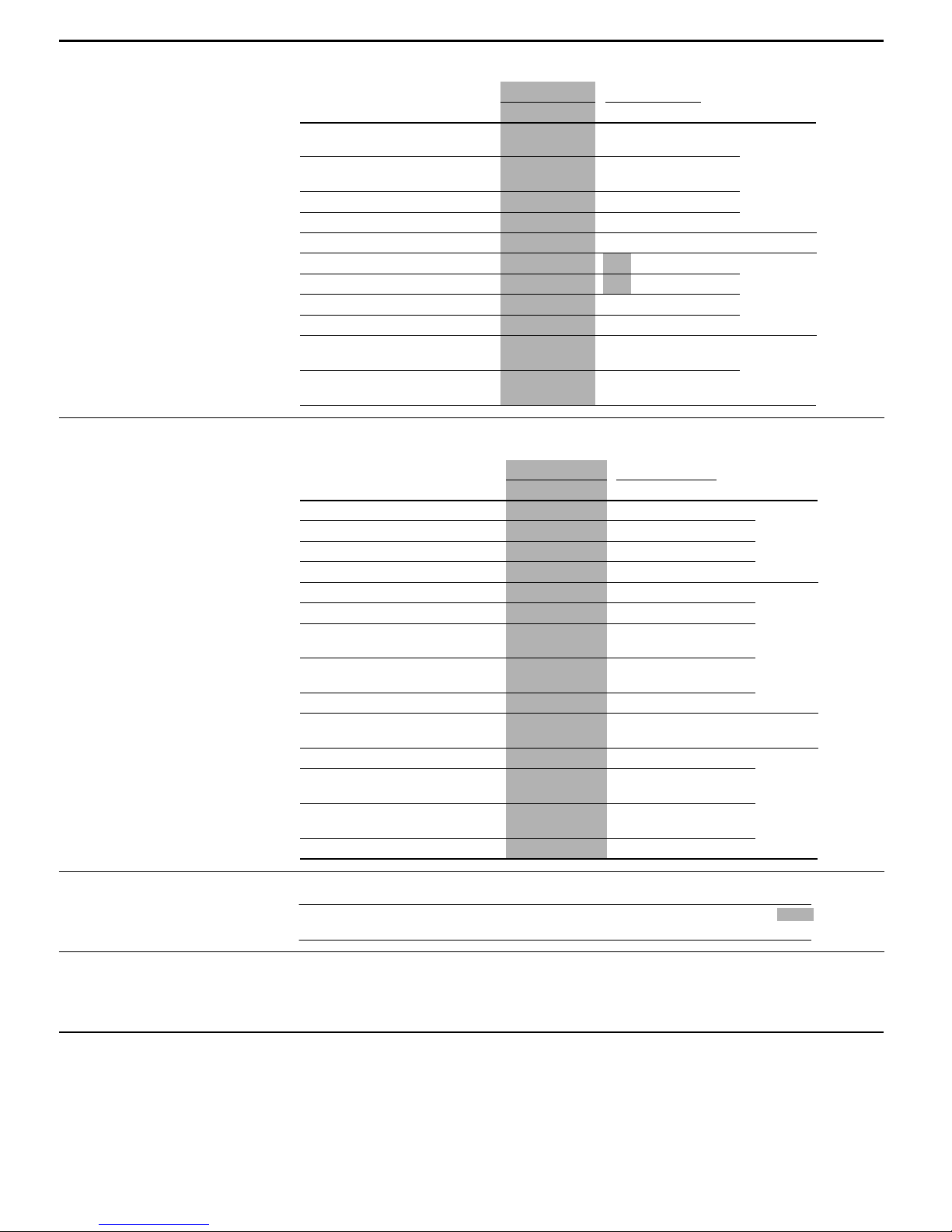

List of Items Revised or Added for This Version

Section Page Description Edition

1.1 SuperH

Microcomputer

Features

Table 1.2 Product

Lineup

6, 7 SH7034, SH7032: 2 to 16.6 MHz device deleted.

Product

Number

SH7032 ROMless 5.0 V 2 to 20 MHz -20 to +75°C HD6417032F20 HD6417032F20 112-pin plastic

SH7034 PROM 5.0 V 2 to 20 MHz -20 to +75°C HD6477034F20 HD6477034F20 112-pin plastic

On-Chip

Operating

ROM

Mask 5.0 V 2 to 20 MHz -20 to +75°C HD6437034AF20 HD6437034AF20 112-pin plastic

ROM

ROMless 5.0 V 2 to 20 MHz -20 to +75°C HD6417034F20 HD6417034F20 112-pin plastic

Operating

Voltage

Frequency

3.3 V 2 to 12.5 MHz -20 to +75°C HD6417032VF12 HD6417032VF12

5.0 V 2 to 20 MHz -20 to +75°C HD6417032X20 HD6417032TE20 120-pin plastic

3.3 V 2 to 12.5 MHz -20 to +75°C HD6417032VX12 HD6417032VTE12

3.3 V 2 to12.5 MHz -20 to +75°C HD6 4 7 70 3 4 V F1 2 HD6 4 7 70 3 4 V F1 2

5.0 V 2 to 20 MHz -20 to +75°C HD6477034X20 HD6 4 7 70 3 4 TE 2 0 120-pin plastic

3.3 V 2 to 12.5 MHz -20 to +75°C HD6 4 7 70 3 4 V X 1 2 HD6 4 7 70 3 4 V TE 1 2

3.3 V 2 to 12.5 MHz -20 to +75°C HD6437034AVF12 HD6437034AF12

5.0 V 2 to 20 MHz -20 to +75°C HD6437034AX20 HD6437034ATE20 120-pin plastic

3.3 V 2 to 12.5 MHz -20 to +75°C HD6437 0 3 4 A VX 1 2 HD6437034ATE12

3.3 V 2 to 12.5 MHz -20 to +75°C HD6417034VF12 HD6417034VF12

5.0 V 2 to 20 MHz -20 to +75°C HD6417034X20 HD6417034TE20 120-pin plastic

3.3 V 2 to 12.5 MHz -20 to +75°C HD6417034VX12 HD6417034VTE12

Temperature

Range Model

-40 to +85°C HD6417032FI20 HD6417032FI20

-40 to +85°C HD6417032VFI12 HD6417032VFI12

-40 to +85°C HD6417032XI20 HD6417032TEI20

-40 to +85°C HD6417032VXI12 HD6417032VTEI12

-40 to +85°C HD6477034FI20 HD6477034FI20

-40 to +85°C HD6 4 7 70 3 4 V FI 1 2 HD6 4 7 70 3 4 V FI 1 2

-40 to +85°C HD6477034XI20 HD6 4 7 70 3 4 TE I 2 0

-40 to +85°C HD6 4 7 70 3 4 V X I 1 2 HD6 4 7 70 3 4 V TE I 1 2

-40 to +85°C HD6437034AFI20 HD6437034AFI20

-40 to +85°C HD6437034AVFI12 HD6437034AFI12

-40 to +85°C HD6437034AXI20 HD6437034ATEI20

-40 to +85°C HD6437034AVXI12 HD6437034ATEI12

-40 to +85°C HD6417034FI20 HD6417034FI20

-40 to +85°C HD6417034VFI12 HD6417034VFI12

-40 to +85°C HD6417034XI20 HD6417034TEI20

-40 to +85°C HD6417034VXI12 HD6417034VTEI12

Marking

Model No.

6

2

*

Package

QFP (FP-112)

TQFP (TFP-120)

QFP (FP-112)

TQFP (TFP-120)

QFP (FP-112)

TQFP (TFP-120)

QFP (FP-112)

TQFP (TFP-120)

Product

Number

SH7034B

Notes: *1 The electrical characteristics of the SH7034B mask ROM version and SH7034 PROM

1.3.2 Pin Functions

Table 1.3 Pin

12 Note amended

*2 Can be used in the SH7034 PROM version.

Functions

On-Chip

Operating

Voltage

Operating

Frequency

ROM

1

*

Mask 3.3 V 4 to 12.5 MHz -20 to +75°C HD6437034BVF12 6437034B(***)F 112-pin plastic

ROM

ROMless 3.3 V 4 to 20 MHz -20 to +75°C HD6417034BVF20 HD6417034BVF20 112-pin plastic

Temperature

Range Model

-40 to +85°C HD6437034BVFW12 6437034B(***)FW

-20 to +75°C HD6437034BVX12 6437034B(***)X 120-pin plastic

-40 to +85°C HD6437034BVXW12 6437034B(***)XW

-40 to +85°C HD6417034BVFW20 HD6417034BVFW20

-20 to +75°C HD6417034BVX20 6417034BVTE20 120-pin plastic

-40 to +85°C HD6417034BVXW20 6417034BVTEW20

Marking

Model No.

2

*

Package

QFP (FP-112)

TQFP (TFP-120)

QFP (FP-112)

TQFP (TFP-120)

version are different.

*2 For mask ROM versions, (***) is the ROM code.

6

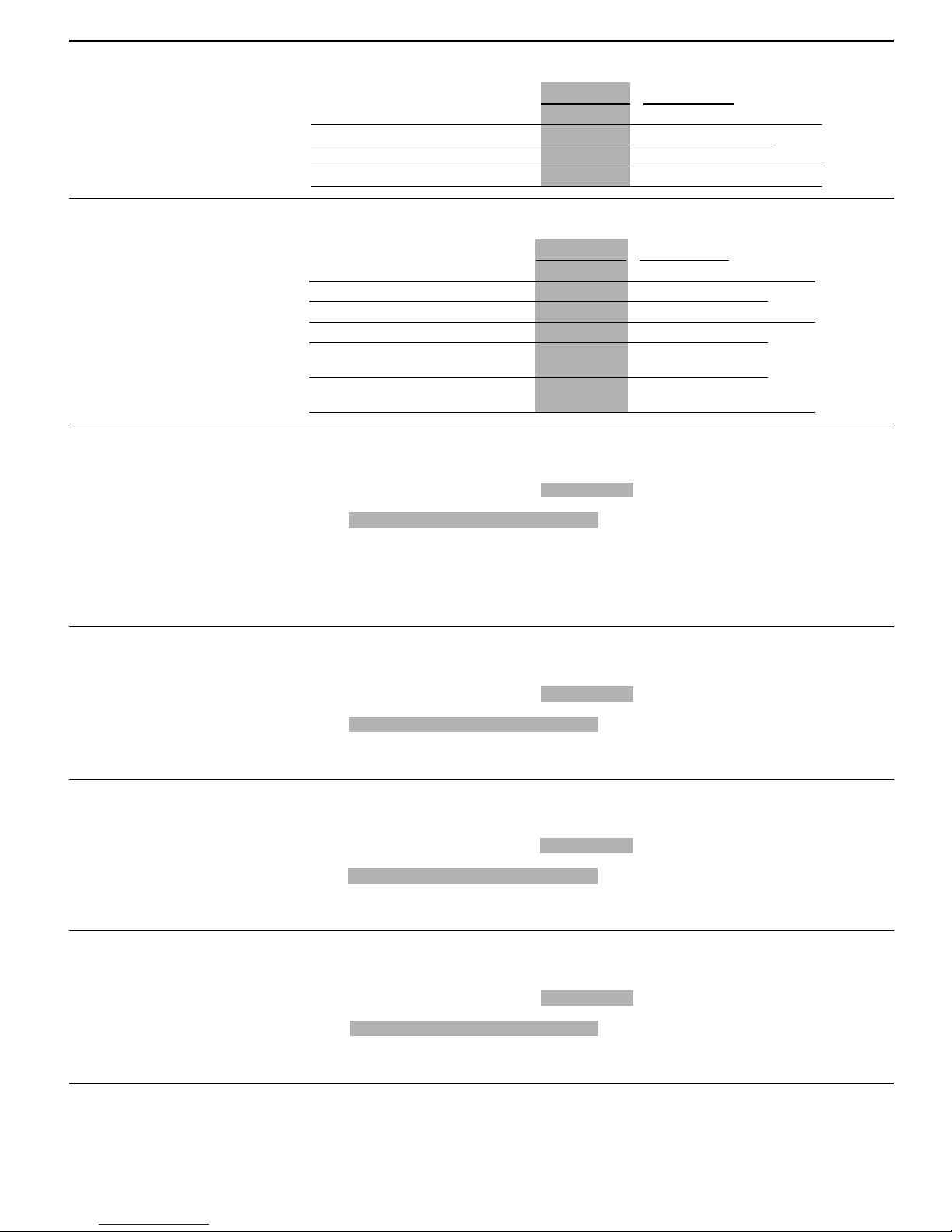

Page 11

Section Page Description Edition

2.1.2 Control

Registers

Figure 2.2 Control

Registers

2.1.4 Initial Values

of Registers

Table 2.1 Initial

Values of Registers

3.1 Types of

Operating Modes and

Their Selection

Table 3.1 Operating

Mode Selection

8.11.3 Maximum

Number of States

from BREQ Input to

Bus Release

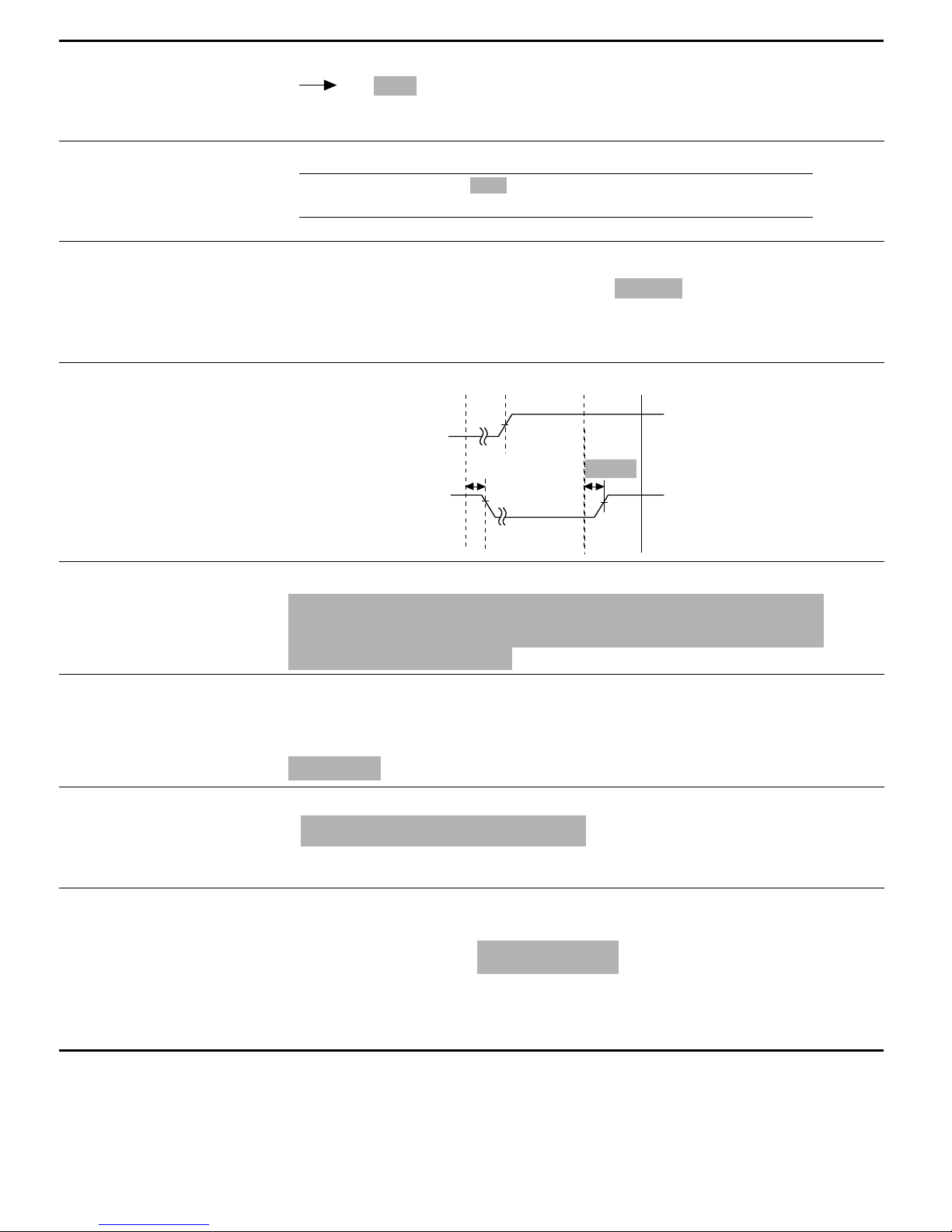

Figure 8.47 Bus

Release Procedure

18 Description amended

Bits I3–I0: Interrupt mask bits.

19 Description amended

SR Bits I3–I0 are 1111(H'F), reserved bits are 0, and other

49 Note amended

*2 Only modes 0 and 1 are available in the SH7032 and SH7034

ROMless version.

174 Description amended

bits are undefined

t

BRQS

t

BACD1

t

BACD2

6

6

6

6

9.1.4 Register

Configuration

Table 9.2 DMAC

Registers

9.3.4 DMA Transfer

Types

10.1.4 Register

Configuration

Table 10.3 Register

Configuration

10.4.5 ResetSynchronized PWM

Mode

Procedure for

Selecting ResetSynchronized PWM

Mode (figure 10.31):

179 *4 added

*4 Only the values of bits A27–A24 and A8–A0 are valid; bits A23–A9

are ignored. For details on the register addresses, see section

8.3.5, Area Descriptions.

200 Description amended

Line 3

⋅⋅⋅ destination or source must be the SCI or A/D converter

(table 9.4). ⋅⋅⋅

230 *2 description amended

*2 Only 0 can be written to clear flags.

268 Description amended

4. Set bits CMD1 and CMD0 in TFCR to select reset-synchronized

PWM mode. TIOCA3, TIOCB3, TIOCA4, TIOCB4, TOCXA4, and

TOCXB4 become PWM output pins.

6

6

6

6

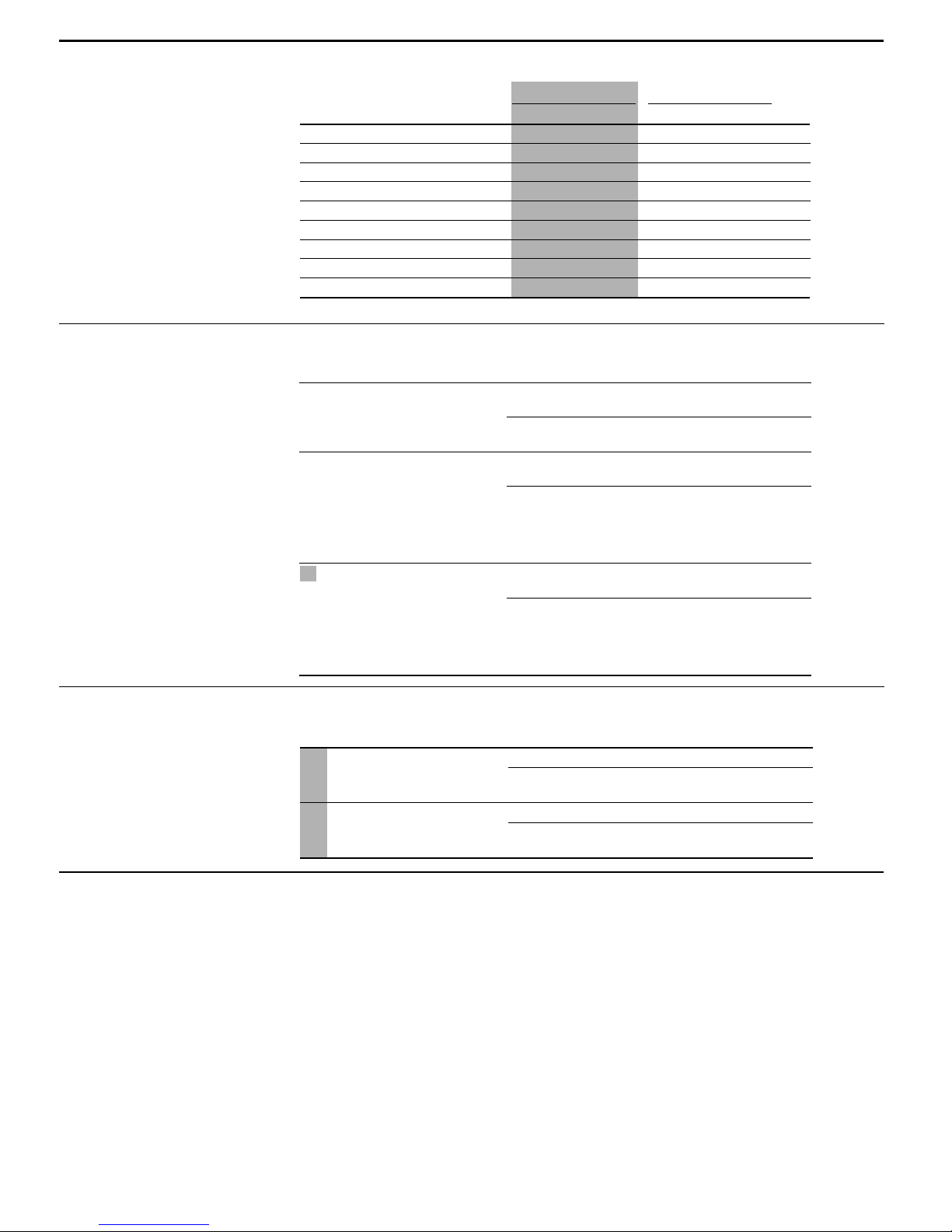

Page 12

Section Page Description Edition

10.4.6

Complementary

PWM Mode

Procedure for

Selecting

Complementary

PWM Mode (Figure

10.33):

10.6.15 ITU

Operating Modes

Table 10.18 ITU

Operating Modes

(Channel 0)

Table 10.19 ITU

Operating Modes

(Channel 1)

271 Description amended

3. Set bits CMD1 and CMD0 in TMDB to select complementary PWM

mode. TIOCA3, TIOCB3, TIOCA4, TIOCB4, TOCXA4, and

TOCXB4 become PWM pins.

301 Table amended

TSNC TMDR TFCR TOCR TIOR0 TCR0

Operating

Mode Sync MDF FDIR PWM

Synch-

ronized

preset

PWM √ — — PWM0

Output

compare A

function

SYNC0

——√ ——— — √√ √√

= 1

√ — — PWM0

302 Table amended

TSNC TMDR TFCR TOCR TIOR1 TCR1

Operating

Mode Sync MDF FDIR PWM

Synch-

ronized

preset

PWM √ — — PWM1

Output

compare A

function

SYNC1

——√ ——— — √√ √√

= 1

√ — — PWM1

Register Setting

Reset

Comp

Sync

PWM

PWM Buffer

——— — — √ * √√

= 1

— — — — IOA2 = 0,

= 0

Register Setting

Reset

Comp

Sync

PWM

PWM Buffer

——— — — √

= 1

— — — — IOA2 = 0,

= 0

Output

Level

Select IOA IOB

√√√

others:

don’t care

Output

Level

Select IOA IOB

√√√

others:

don’t care

*

Clear

Clock

Select

Select

Clear

Clock

Select

Select

√√

6

6

6

Table 10.20 ITU

Operating Modes

(Channel 2)

12.1.4 Register

Configuration

Table 12.2 WDT

Registers

303 Table amended

TSNC TMDR TFCR TOCR TIOR2 TCR2

Operating

Mode Sync MDF FDIR PWM

Synch-

ronized

preset

PWM √ — — PWM2

Output

compare A

function

SYNC2

——√ ——— — √√ √√

= 1

√ — — PWM2

337 *4 added

Name Abbreviation R/W Value Write

Timer control/status register TCSR R/(W)

Timer counter TCNT R/W H'00 H'5FFFFB9

Reset control/status register RSTCSR R/(W)

Notes: *1 Write by word transfer. A byte or longword write cannot be used.

*2 Read by byte transfer. The correct value cannot be obtained by a word or longword

read.

*3 Only 0 can be written in bit 7, to clear the flag.

*4 Only the values of bits A27–A24 and A8–A0 are valid; bits A23–A9 are ignored. For

details on the register addresses, see section 8.3.5, Area Descriptions

Register Setting

Reset

Comp

Sync

PWM

PWM Buffer

——— — — √

= 1

— — — — IOA2 = 0,

= 0

Output

Level

Select IOA IOB

3

*

3

*

Clear

Clock

Select

Select

*

√√

√√√

others:

don’t care

4

*

Initial

1

*

Address

Read

2

*

H'18 H'5FFFFB8 H'5FFFFB8

H'1F H'5FFFFBA H'5FFFFBB

6

6

Page 13

Section Page Description Edition

12.2.2 Timer

Control/Status

Register (TCSR)

13.2.6 Serial Control

Register

13.2.8 Bit Rate

Register (BRR)

Table 13.3 Bit Rates

and BRR Settings in

Asynchronous Mode

Table 13.4 Bit

Rates and BRR

Settings in

Synchronous Mode

338 Note added

Note: * Only 0 can be written, to clear the flag.

359 Initial value added

Internal clock, SCK pin used for input pin (input signal

2

is ignored) or output pin (output level is undefined)

*

(Initial value)

2

Internal clock, SCK pin used for serial clock output

*

(Initial value)

367 Note added

Note: Settings with an error of 1% or less are recommended.

368 Note deleted 6

6

6

6

15.2 Register

Configuration

Table 15.2 Pin

Function Controller

Registers

16.2.1 Register

Configuration

Table 16.1 Port A

Register

16.3.1 Register

Configuration

Table 16.3 Port B

Register

427 Note added

Name Abbreviation R/W Initial Value Address* Access Size

Port A I/O register PAIOR R/W H'0000 H'5FFFFC4 8, 16, 32

Port A control register 1 PACR1 R/W H'3302 H'5FFFFC8 8, 16, 32

Port A control register 2 PACR2 R/W H'FF95 H'5FFFFCA 8, 16, 32

Port B I/O register PBIOR R/W H'0000 H'5FFFFC6 8, 16, 32

Port B control register 1 PBCR1 R/W H'0000 H'5FFFFCC 8, 16, 32

Port B control register 2 PBCR2 R/W H'0000 H'5FFFFCE 8, 16, 32

Column address strobe

pin control register

Note: * Only the values of bits A27–A24 and A8–A0 are valid; bits A23–A9 are ignored. For

details on the register addresses, see section 8.3.5, Area Descriptions.

442 Note added

Name Abbreviation R/W Initial Value Address* Access Size

Port A data register PADR R/W H'0000 H'5FFFFC0 8, 16, 32

Note: * Only the values of bits A27–A24 and A8–A0 are valid; bits A23–A9 are ignored. For

details on the register addresses, see section 8.3.5, Area Descriptions.

443 Note added

Name Abbreviation R/W Initial Value Address* Access Size

Port B data register PBDR R/W H'0000 H'5FFFFC2 8, 16, 32

Note: * Only the values of bits A27–A24 and A8–A0 are valid; bits A23–A9 are ignored. For

details on the register addresses, see section 8.3.5, Area Descriptions.

6

CASCR R/W H'5FFF H'5FFFFEE 8, 16, 32

6

6

16.4.1 Register

Configuration

Table 16.5 Port C

Register

445 Note added

Name Abbreviation R/W Initial Value Address* Access Size

Port C data register PCDR R/W H'5FFFFD0 8, 16, 32

Note: * Only the values of bits A27–A24 and A8–A0 are valid; bits A23–A9 are ignored. For

6

—

details on the register addresses, see section 8.3.5, Area Descriptions.

Page 14

Section Page Description Edition

19.1.2 Register

Table 19.2 Standby

Control Register

(SBYCR)

20.1.2 DC

Characteristics

Table 20.2 DC

Characteristics

Table 20. 2 DC

Characteristics

Table 20.3

Permitted Output

Current Values

20.1.3 AC

Characteristics

(1) Clock Timing

Table 20.4 Clock

Timing

460 Note added

Name Abbreviation R/W Initial Value Address* Access size

Standby control register SBYCR R/W H'1F H'5FFFFBC 8, 16, 32

Note: * Only the values of bits A27–A24 and A8–A0 are valid; bits A23–A9 are ignored. For

details on the register addresses, see section 8.3.5, Area Descriptions.

467 16.6 MHz deleted 6

Table of 16.6 MHz deleted 6

471 16.6 MHz deleted 6

472 16.6 MHz deleted 6

6

(2) Control Signal

Timing

Table 20.5 Control

Signal Timing

(3) Bus Timing

Table 20.6 Bus

Timing (1)

Table 20.7 Bus

Timing (2)

474 16.6 MHz deleted 6

478,

479

Description amended

6

Read data access time 1

Read data access time 2

Read data access time from

6

*

CAS 2

Read data access time from

6

*

RAS 1

Read data access time from

6

*

RAS 2

Data setup time for CAS t

CAS setup time for RAS t

Row address hold time t

*

6

*

Table deleted

t

ACC1

t

ACC2

t

CAC2

t

RAC1

t

RAC2

DS

CSR

RAH

4

*

t

– 30

cyc

t

× (n+2) –

cyc

3

*

30

t

× (n+1) –

cyc

3

*

25

t

× 1.5 – 20 — ns 20.11, 20.12

cyc

t

× (n+2.5)

cyc

3

*

– 20

5

*

0

10 — ns 20.16–20.18

10 — ns 20.11, 20.13

— ns 20.8, 20.11, 20.12

— ns 20.9, 20.10,

—ns

—ns

— ns 20.11, 20.13

20.13–20.15

20.13–20.15

20.13–20.15

6

6

Table 20.7 Bus

Timing (2)

494 Description amended

Read data access time 1

Read data access time 2

4

*

4

*

t

ACC1tcyc

t

ACC2tcyc

– 44 — ns 20.21, 20.24, 20.25

2

× (n+2) – 44

*

— ns 20.22, 20.23,

20.26–20.28

6

Page 15

Section Page Description Edition

(4) DMAC Timing

Table 20.8 DMAC

Timing

(5) 16-bit Integrated

Timer Pulse Unit

Timing

Table 20.9 16-bit

Integrated Timer

Pulse Unit Timing

(6) Programmable

Timing Pattern

Controller and I/O

Port Timing

Table 20.10

Programmable

Timing Pattern

Controller and I/O

Port Timing

507 16.6 MHz deleted 6

509 16.6 MHz deleted 6

510 16.6 MHz deleted 6

(7) Watchdog Timer

Timing

Table 20.11

Watchdog Timer

Timing

(8) Serial

Communication

Interface Timing

Table 20.12 Serial

Communication

Interface Timing

(9) A/D Converter

Timing

Table 20.13 A/D

Converter Timing

20.1.4 A/D

Converter

Characteristics

511 16.6 MHz deleted

512 16.6 MHz deleted

513 16.6 MHz deleted

516 16.6 MHz deleted

6

6

6

6

Table 20.14 A/D

Converter

Characteristics

20.2 SH7034B 3.3 V

517 12.5 MHz added 6

12.5 MHz Version

and 20 MHz

1

Version

*

Electrical

Characteristics

Page 16

Section Page Description Edition

20.2.1 Absolute

Maximum Ratings

Table 20.15

Absolute Maximum

Ratings

Table 20.16 DC

Characteristics

517 Notes amended

Item Symbol Rating Unit

Power supply voltage V

Input voltage (except port C) V

Input voltage (port C) V

Analog power supply voltage AV

Analog reference voltage AV

Analog input voltage V

Operating temperature T

Storage temperature T

518,

Caution: Operating the chip in excess of the absolute maximum rating may result in permanent

Notes: *1 ROMless products only for 20 MHz version

12.5 MHz added

damage.

*2 Regular-specification products; for wide-temperature-range products, Topr = –40 to

+85°C

519

Conditions: VCC = 3.3 V ±0.3V, AVCC = 3.3 V ±0.3V, AVCC = VCC ±0.3V, AV

AV

CC

Notes: *1 ROMless products only for 20 MHz version

*2 Regular-specification products; for wide-temperature-range products, Ta = –40 to

+85°C

CC

in

in

CC

ref

AN

opr

stg

, VSS = AVSS = 0 V, φ = 12.5 to 20 MHz

–0.3 to +4.6 V

–0.3 to VCC + 0.3 V

–0.3 to AVCC + 0.3 V

–0.3 to +4.6 V

–0.3 to AVCC + 0.3 V

–0.3 to AVCC + 0.3 V

–20 to +75

–55 to +125 ˚C

1

*

, Ta = –20 to +75°C

2

*

= 3.0 V to

ref

2

*

6

˚C

6

Table 20.17

Permitted Output

Current Values

Current Ordinary I

consumption operation

Sleep — 20 — mA f = 12.5 MHz

Standby — 0.1 5 µA Ta ≤ 50°C

521 12.5 MHz added

Item Symbol Min Typ Max Min Typ Max Unit

Output low-level

permissible current

(per pin)

Output low-level

permissible current

(total)

Output high-level

permissible current

(per pin)

Output high-level

permissible current

(total)

Caution: To ensure reliability of the chip, do not exceed the output current values given in table

20.18.

I

OL

∑ I

–I

–∑ I

OH

CC

— 25 — mA f = 12.5 MHz

— 35 60 mA f = 20 MHz

— 30 40 mA f = 20 MHz

——10 µA50°C < Ta

6

12.5 MHz 20 MHz

——10 ——10mA

OL

——80 ——80mA

——2.0 ——2.0mA

——25 ——25mA

OH

Page 17

Section Page Description Edition

20.2.3 AC

Characteristics

(1) Clock Timing

Table 20.18 Clock

Timing

(2) Control Signal

Timing

Table 20.19 Control

Signal Timing

522 12.5 MHz added and description amended

12.5 MHz 20 MHz

Item Symbol Min Max Min Max Unit Figures

EXTAL input high level

pulse width

EXTAL input low level

pulse width

EXTAL input rise time t

EXTAL input fall time t

Clock cycle time t

Clock high pulse width t

Clock low pulse width t

Clock rise time t

Clock fall time t

Reset oscillation settling

time

Software standby

oscillation settling time

t

EXH

t

EXL

EXr

EXf

cyc

CH

CL

Cr

Cf

t

OSC1

t

OSC2

22 — 15 — ns 20.45

22 — 15 — ns

—10 —5 ns

—10 —5 ns

80 500 50 250 ns 20.45, 20.46

30 — 20 — ns 20.46

30 — 20 — ns

—10 —5 ns

—10 —5 ns

10 — 10 — ms 20.47

10 — 10 — ms

524 12.5 MHz added and description amended

12.5 MHz 20 MHz

Item Symbol Min Max Min Max Unit Figure

RES setup time t

RES pulse width t

NMI reset setup time t

NMI reset hold time t

NMI setup time t

NMI hold time t

IRQ0–IRQ7 setup time

(edge detection)

IRQ0–IRQ7 setup time

(level detection)

IRQ0–IRQ7 hold time t

IRQOUT output delay

time

Bus request setup time t

Bus acknowledge delay

time 1

Bus acknowledge delay

time 2

Bus 3-state delay time t

RESS

RESW

NMIRS

NMIRH

NMIS

NMIH

t

IRQES

t

IRQLS

IRQEH

t

IRQOD

BRQS

t

BACD1

t

BACD2

BZD

320 — 200 — ns 20.48

20 — 20 — t

320 — 200 — ns

320 — 200 — ns

160 — 100 — ns 20.49

80 — 50 — ns

160 — 100 — ns

160 — 100 — ns

80 — 50 — ns

— 80 — 50 ns 20.50

80 — 50 — ns 20.51

— 80 — 50 ns

— 80 — 50 ns

— 80 — 50 ns

6

6

cyc

(3) Bus Timing

Table 20.20 Bus

528 Description amended

Read data access time 2

Timing (1)

(3) Bus Timing

Table 20.20 Bus

530 to

532

Newly added 6

Timing (2)

6

6

*

t

ACC2

t

× (n+2) –

cyc

3

*

30

— ns 20.53, 20.54, 20.57–20.59

Page 18

Section Page Description Edition

(4) DMAC Timing

Table 20.21 DMAC

Timing

(5) 16-bit Integrated

Timer Pulse Unit

Timing

Table 20.22 16-bit

Integrated Timer

Pulse Unit Timing

(6) Programmable

Timing Pattern

Controller and I/O

Port Timing

Table 20.23

Programmable

Timing Pattern

Controller and I/O

Port Timing

546 12.5 MHz added

Item Symbol Min Max Min Max Unit Figure

DREQ0, DREQ1 setup time t

DREQ0, DREQ1 hold time t

DREQ0, DREQ1 Pulse width t

547 12.5 MHz added

Item Symbol Min Max Min Max Unit Figure

Output compare delay time t

Input capture setup time t

Timer clock input setup time t

Timer clock pulse width

(single edge)

Timer clock pulse width

(both edges)

548 Description amended

Conditions: VCC = 3.3 V ±0.3V, AVCC = 3.3 V ±0.3V, AVCC = VCC ±0.3V, AV

, VSS = AVSS = 0 V, φ = 12.5 to 20 MHz

AV

CC

Notes: *1 ROMless products only for 20 MHz version

*2 Regular-specification products; for wide-temperature-range products, Ta = –40 to

+85°C

DRQS

DRQH

DRQW

TOCD

TICS

TCKS

t

TCKWH/L

t

TCKWL/L

12.5 MHz 20 MHz

80 — 27 — ns 20.65

30 — 30 — ns

1.5 — 1.5 — t

12.5 MHz 20 MHz

— 100 — 100 ns 20.67

50 — 35 — ns

50 — 50 — ns 20.68

1.5 — 1.5 — t

2.5 — 2.5 — t

1

*

, Ta = –20 to +75°C

cyc

cyc

cyc

= 3.0 V to

ref

2

*

20.66

6

6

6

(7) Watchdog Timer

Timing

Table 20.24

Watchdog Timer

Timing

(8) Serial

Communication

Interface Timing

Table 20.25 Serial

Communication

Interface Timing

(9) A/D Converter

Timing

Table 20.26 A/D

Converter Timing

549 Description amended

Conditions: VCC = 3.3 V ±0.3V, AVCC = 3.3 V ±0.3V, AVCC = VCC ±0.3V, AV

AV

, VSS = AVSS = 0 V, φ = 12.5 to 20 MHz

CC

Notes: *1 ROMless products only for 20 MHz version

*2 Regular-specification products; for wide-temperature-range products, Ta = –40 to

+85°C

550 Description amended

Conditions: VCC = 3.3 V ±0.3V, AVCC = 3.3 V ±0.3V, AVCC = VCC ±0.3V, AV

, VSS = AVSS = 0 V, φ = 12.5 to 20 MHz

AV

CC

Notes: *1 ROMless products only for 20 MHz version

*2 Regular-specification products; for wide-temperature-range products, Ta = –40 to

+85°C

551 Description amended

Conditions: VCC = 3.3 V ±0.3V, AVCC = 3.3 V ±0.3V, AVCC = VCC ±0.3V, AV

, VSS = AVSS = 0 V, φ = 12.5 to 20 MHz

AV

CC

Notes: *1 ROMless products only for 20 MHz version

*2 Regular-specification products; for wide-temperature-range products, Ta = –40 to

+85°C

1

*

, Ta = –20 to +75°C

1

*

, Ta = –20 to +75°C

1

*

, Ta = –20 to +75°C

= 3.0 V to

ref

2

*

= 3.0 V to

ref

2

*

= 3.0 V to

ref

2

*

6

6

6

Page 19

Section Page Description Edition

20.2.4 A/D

Converter

Characteristics

Table 20.27 A/D

Converter

Characteristics

A.2.17 Timer Status

Registers 0–4

(TSR0–TSR4)

Table A.18 TSR0–

TSR4 Bit Functions

554 12.5 MHz added

Item Min Typ Max Min Typ Max Unit

Resolution 101010 101010bit

Conversion time — — 11.2 — — 6.7 µS

Analog input capacitance — — 20 — — 20 pF

Permissible signal-source impedance — — 1 — — 1 kΩ

Nonlinearity error* ——±4.0 — — ±4.0 LSB

Offset error* ——±4.0 — — ±4.0 LSB

Full-scale error* ——±4.0 — — ±4.0 LSB

Quantization error* ——±0.5 — — ±0.5 LSB

Absolute accuracy — — ±6.0 — — ±6.0 LSB

Note: *Reference value

581 Bit amended

Bit Bit name Value Description

2 Overflow flag (OVF) 0 Clear conditions: 0 is written in OVF after

1 Input capture/compare match

flag B (IMFB)

0 Input capture/compare match

flag A (IMFA)

6

12.5 MHz 20 MHz

6

reading OVF = 1 (Initial value)

1 Set conditions: TCNT value overflows (H'FFFF

? H'0000) or underflows (H'FFFF ? H'0000)

0 Clear conditions: 0 is written in IMFB after

reading IMFB = 1 (Initial value)

1 Set conditions: (1) When GRB is functioning as

the output compare register, and TCNT = GRB;

(2) When GRB is functioning as the input

capture register, and the TCNT value is

transferred to GRB by the input capture signal

0 Clear conditions: 0 is written in IMFA after

reading IMFA = 1 (Initial value)

1 Set conditions: (1) When GRA is functioning as

the output compare register, and TCNT = GRA;

(2) When GRA is functioning as the input

capture register, and the TCNT value is

transferred to GRA by the input capture signal

A.2.23 Timer Output

Control Register

(TOCR)

Table A.24 TOCR

Bit Functions

587 Table amended

Bit Bit name Value Description

1 Output level select 4 (OLS4) 0 Reverse output of TIOCA3, TIOCA4, TIOCB4

0 Output level select 3 (OLS3) 0 Reverse output of TIOCB3, TOCXA4, TOCXB4

6

1 Direct output of TIOCA3, TIOCA4, TIOCB4

(Initial value)

1 Direct output of TIOCB3, TOCXA4, TOCXB4

(Initial value)

Page 20

Section Page Description Edition

A.3 Register Status

in Reset and PowerDown States

Table A.77 Register

Status in Reset and

Power-Down States

644 *2 added

Watchdog timer (WDT) TCNT Initialized Initialized Held Held

Serial communication SMR Initialized Initialized Initialized Held

interface (SCI)

Notes: *1 Bits 7–5 (OVF, WT/IT, TME) are initialized, bits 2–0 (CKS2–CKS0) are held.

*2 Not initialized in the case of a reset by the WDT.

1

TCSR

2

*

RSTCR

BRR

SCR

TDR

TSR Held

SSR Initialized

RDR

RSR Held

*

Initialized

6

Page 21

Page 22

Contents

Section 1 Overview............................................................................................................ 1

1.1 SuperH Microcomputer Features ....................................................................................... 1

1.2 Block Diagram.................................................................................................................... 8

1.3 Pin Descriptions.................................................................................................................. 9

1.3.1 Pin Arrangement ................................................................................................... 9

1.3.2 Pin Functions......................................................................................................... 11

1.3.3 Pin Layout by Mode.............................................................................................. 15

Section 2 CPU...................................................................................................................... 17

2.1 Register Configuration ....................................................................................................... 17

2.1.1 General Registers (Rn).......................................................................................... 17

2.1.2 Control Registers................................................................................................... 18

2.1.3 System Registers................................................................................................... 19

2.1.4 Initial Values of Registers..................................................................................... 19

2.2 Data Formats ...................................................................................................................... 20

2.2.1 Data Format in Registers....................................................................................... 20

2.2.2 Data Format in Memory........................................................................................ 20

2.2.3 Immediate Data Format ........................................................................................ 21

2.3 Instruction Features............................................................................................................ 21

2.3.1 RISC-Type Instruction Set.................................................................................... 21

2.3.2 Addressing Modes................................................................................................. 24

2.3.3 Instruction Formats ............................................................................................... 27

2.4 Instruction Set .................................................................................................................... 31

2.4.1 Instruction Set by Classification ........................................................................... 31

2.4.2 Operation Code Map............................................................................................. 42

2.5 CPU State ........................................................................................................................... 45

2.5.1 State Transitions.................................................................................................... 45

2.5.2 Power-Down State ................................................................................................ 48

Section 3 Operating Modes ............................................................................................. 49

3.1 Types of Operating Modes and Their Selection................................................................. 49

3.2 Operating Mode Descriptions ............................................................................................ 49

3.2.1 Mode 0 (MCU Mode 0) ........................................................................................ 49

3.2.2 Mode 1 (MCU Mode 1) ........................................................................................ 49

3.2.3 Mode 2 (MCU Mode 2) ........................................................................................ 49

3.2.4 Mode 7 (PROM Mode)......................................................................................... 49

Section 4 Exception Handling........................................................................................ 51

4.1 Overview............................................................................................................................ 51

i

Page 23

4.1.1 Exception Handling Types and Priorities.............................................................. 51

4.1.2 Exception Handling Operation.............................................................................. 53

4.1.3 Exception Vector Table ........................................................................................ 54

4.2 Resets.................................................................................................................................. 56

4.2.1 Reset Types ........................................................................................................... 56

4.2.2 Power-On Reset .................................................................................................... 57

4.2.3 Manual Reset......................................................................................................... 57

4.3 Address Errors.................................................................................................................... 58

4.3.1 Address Error Sources .......................................................................................... 58

4.3.2 Address Error Exception Handling ....................................................................... 58

4.4 Interrupts ............................................................................................................................ 59

4.4.1 Interrupt Sources ................................................................................................... 59

4.4.2 Interrupt Priority Rankings.................................................................................... 59

4.4.3 Interrupt Exception Handling................................................................................ 60

4.5 Instruction Exceptions........................................................................................................ 61

4.5.1 Types of Instruction Exceptions............................................................................ 61

4.5.2 Trap Instruction..................................................................................................... 61

4.5.3 Illegal Slot Instruction........................................................................................... 62

4.5.4 General Illegal Instructions................................................................................... 62

4.6 Cases in which Exceptions are Not Accepted.................................................................... 63

4.6.1 Immediately after Delayed Branch Instruction..................................................... 63

4.6.2 Immediately after Interrupt-Disabling Instruction................................................ 63

4.7 Stack Status after Exception Handling............................................................................... 64

4.8 Notes................................................................................................................................... 65

4.8.1 Value of the Stack Pointer (SP) ............................................................................ 65

4.8.2 Value of the Vector Base Register (VBR)............................................................ 65

4.8.3 Address Errors Caused by Stacking During Address Error

Exception Handling............................................................................................... 65

Section 5 Interrupt Controller (INTC).......................................................................... 67

5.1 Overview............................................................................................................................ 67

5.1.1 Features ................................................................................................................. 67

5.1.2 Block Diagram...................................................................................................... 67

5.1.3 Pin Configuration.................................................................................................. 69

5.1.4 Registers................................................................................................................ 69

5.2 Interrupt Sources ................................................................................................................ 70

5.2.1 NMI Interrupts ...................................................................................................... 70

5.2.2 User Break Interrupt.............................................................................................. 70

5.2.3 IRQ Interrupts ....................................................................................................... 70

5.2.4 On-Chip Interrupts................................................................................................ 71

5.2.5 Interrupt Exception Vectors and Priority Rankings.............................................. 71

5.3 Register Descriptions.......................................................................................................... 74

5.3.1 Interrupt Priority Registers A–E (IPRA–IPRE).................................................... 74

ii

Page 24

5.3.2 Interrupt Control Register (ICR)........................................................................... 75

5.4 Interrupt Operation............................................................................................................. 76

5.4.1 Interrupt Sequence ................................................................................................ 76

5.4.2 Stack after Interrupt Exception Handling.............................................................. 78

5.5 Interrupt Response Time.................................................................................................... 79

5.6 Usage Notes........................................................................................................................ 80

Section 6 User Break Controller (UBC)...................................................................... 81

6.1 Overview............................................................................................................................ 81

6.1.1 Features ................................................................................................................. 81

6.1.2 Block Diagram...................................................................................................... 82

6.1.3 Register Configuration.......................................................................................... 83

6.2 Register Descriptions.......................................................................................................... 84

6.2.1 Break Address Registers (BAR) ........................................................................... 84

6.2.2 Break Address Mask Register (BAMR)................................................................ 85

6.2.3 Break Bus Cycle Register (BBR).......................................................................... 86

6.3 Operation............................................................................................................................ 88

6.3.1 Flow of User Break Operation.............................................................................. 88

6.3.2 Break on Instruction Fetch Cycles to On-Chip Memory...................................... 90

6.3.3 Program Counter (PC) Value Saved in User Break Interrupt Exception

Processing.............................................................................................................. 90

6.4 Setting User Break Conditions........................................................................................... 91

6.5 Notes................................................................................................................................... 92

6.5.1 On-Chip Memory Instruction Fetch...................................................................... 92

6.5.2 Instruction Fetch at Branches................................................................................ 92

6.5.3 Instruction Fetch Break......................................................................................... 93

Section 7 Clock Pulse Generator (CPG)...................................................................... 95

7.1 Overview............................................................................................................................ 95

7.2 Clock Source ...................................................................................................................... 95

7.2.1 Connecting a Crystal Resonator............................................................................ 95

7.2.2 External Clock Input ............................................................................................. 97

7.3 Usage Notes........................................................................................................................ 98

Section 8 Bus State Controller (BSC).......................................................................... 101

8.1 Overview............................................................................................................................ 101

8.1.1 Features ................................................................................................................. 101

8.1.2 Block Diagram...................................................................................................... 102

8.1.3 Pin Configuration.................................................................................................. 103

8.1.4 Register Configuration.......................................................................................... 104

8.1.5 Overview of Areas ................................................................................................ 105

8.2 Register Descriptions.......................................................................................................... 107

8.2.1 Bus Control Register (BCR) ................................................................................. 107

iii

Page 25

8.2.2 Wait State Control Register 1 (WCR1)................................................................. 109

8.2.3 Wait State Control Register 2 (WCR2)................................................................. 111

8.2.4 Wait State Control Register 3 (WCR3)................................................................. 113

8.2.5 DRAM Area Control Register (DCR) .................................................................. 114

8.2.6 Refresh Control Register (RCR) ........................................................................... 117

8.2.7 Refresh Timer Control/Status Register (RTCSR)................................................. 118

8.2.8 Refresh Timer Counter (RTCNT)......................................................................... 120

8.2.9 Refresh Time Constant Register (RTCOR) .......................................................... 120

8.2.10 Parity Control Register (PCR) .............................................................................. 121

8.2.11 Notes on Register Access...................................................................................... 123

8.3 Address Space Subdivision................................................................................................ 124

8.3.1 Address Spaces and Areas .................................................................................... 124

8.3.2 Bus Width.............................................................................................................. 126

8.3.3 Chip Select Signals (CS0–CS7)............................................................................ 126

8.3.4 Shadows ................................................................................................................ 127

8.3.5 Area Descriptions.................................................................................................. 129

8.4 Accessing External Memory Space.................................................................................... 136

8.4.1 Basic Timing ......................................................................................................... 136

8.4.2 Wait State Control................................................................................................. 138

8.4.3 Byte Access Control.............................................................................................. 141

8.5 DRAM Interface Operation................................................................................................ 142

8.5.1 DRAM Address Multiplexing............................................................................... 142

8.5.2 Basic Timing ......................................................................................................... 144

8.5.3 Wait State Control................................................................................................. 146

8.5.4 Byte Access Control.............................................................................................. 148

8.5.5 DRAM Burst Mode............................................................................................... 150

8.5.6 Refresh Control ..................................................................................................... 155

8.6 Address/Data Multiplexed I/O Space Access .................................................................... 159

8.6.1 Basic Timing ......................................................................................................... 159

8.6.2 Wait State Control................................................................................................. 160

8.6.3 Byte Access Control.............................................................................................. 160

8.7 Parity Check and Generation.............................................................................................. 161

8.8 Warp Mode......................................................................................................................... 162

8.9 Wait State Control.............................................................................................................. 163

8.10 Bus Arbitration ................................................................................................................... 166

8.10.1 Operation of Bus Arbitration ................................................................................ 167

8.10.2 BACK Operation................................................................................................... 168

8.11 Usage Notes........................................................................................................................ 169

8.11.1 Usage Notes on Manual Reset.............................................................................. 169

8.11.2 Usage Notes on Parity Data Pins DPH and DPL.................................................. 172

8.11.3 Maximum Number of States from BREQ Input to Bus Release.......................... 172

iv

Page 26

Section 9 Direct Memory Access Controller (DMAC) .......................................... 175

9.1 Overview............................................................................................................................ 175

9.1.1 Features ................................................................................................................. 175

9.1.2 Block Diagram...................................................................................................... 176

9.1.3 Pin Configuration.................................................................................................. 178

9.1.4 Register Configuration.......................................................................................... 179

9.2 Register Descriptions.......................................................................................................... 180

9.2.1 DMA Source Address Registers 0–3 (SAR0–SAR3)........................................... 180

9.2.2 DMA Destination Address Registers 0–3 (DAR0–DAR3) .................................. 180

9.2.3 DMA Transfer Count Registers 0–3 (TCR0–TCR3)............................................ 181

9.2.4 DMA Channel Control Registers 0–3 (CHCR0–CHCR3).................................... 181

9.2.5 DMA Operation Register (DMAOR).................................................................... 186

9.3 Operation............................................................................................................................ 188

9.3.1 DMA Transfer Flow.............................................................................................. 188

9.3.2 DMA Transfer Requests........................................................................................ 190

9.3.3 Channel Priority.................................................................................................... 192

9.3.4 DMA Transfer Types............................................................................................ 197

9.3.5 Number of Bus Cycle States and DREQ Pin Sample Timing............................... 204

9.3.6 DMA Transfer Ending Conditions........................................................................ 212

9.4 Examples of Use................................................................................................................. 213

9.4.1 DMA Transfer between On-Chip RAM and Memory-Mapped

External Device..................................................................................................... 213

9.4.2 Example of DMA Transfer between On-Chip SCI and External Memory........... 214

9.4.3 Example of DMA Transfer Between On-Chip A/D Converter and

External Memory .................................................................................................. 215

9.5 Usage Notes........................................................................................................................ 216

Section 10 16-Bit Integrated Timer Pulse Unit (ITU) ............................................... 219

10.1 Overview ............................................................................................................................ 219

10.1.1 Features .................................................................................................................219

10.1.2 Block Diagram...................................................................................................... 222

10.1.3 Input/Output Pins.................................................................................................. 227

10.1.4 Register Configuration.......................................................................................... 228

10.2 ITU Register Descriptions.................................................................................................. 230

10.2.1 Timer Start Register (TSTR)................................................................................. 230

10.2.2 Timer Synchro Register (TSNC) .......................................................................... 232

10.2.3 Timer Mode Register (TMDR)............................................................................. 233

10.2.4 Timer Function Control Register (TFCR) ............................................................ 236

10.2.5 Timer Output Control Register (TOCR)............................................................... 238

10.2.6 Timer Counters (TCNT)........................................................................................ 239

10.2.7 General Registers A and B (GRA and GRB)........................................................ 240

10.2.8 Buffer Registers A and B (BRA, BRB)................................................................ 241

v

Page 27

10.2.9 Timer Control Register (TCR).............................................................................. 242

10.2.10 Timer I/O Control Register (TIOR) ...................................................................... 244

10.2.11 Timer Status Register (TSR)................................................................................. 246

10.2.12 Timer Interrupt Enable Register (TIER)............................................................... 247

10.3 CPU Interface ..................................................................................................................... 249

10.3.1 16-Bit Accessible Registers.................................................................................. 249

10.3.2 8-Bit Accessible Registers.................................................................................... 251

10.4 Operation............................................................................................................................ 252

10.4.1 Overview............................................................................................................... 252

10.4.2 Basic Functions..................................................................................................... 253

10.4.3 Synchronizing Mode............................................................................................. 262

10.4.4 PWM Mode........................................................................................................... 264

10.4.5 Reset-Synchronized PWM Mode.......................................................................... 268

10.4.6 Complementary PWM Mode................................................................................ 271

10.4.7 Phase Counting Mode ........................................................................................... 278

10.4.8 Buffer Mode.......................................................................................................... 280

10.4.9 ITU Output Timing............................................................................................... 285

10.5 Interrupts ............................................................................................................................ 286

10.5.1 Timing of Setting Status Flags.............................................................................. 286

10.5.2 Status Flag Clear Timing ...................................................................................... 288

10.5.3 Interrupt Sources and DMAC Activation.............................................................. 289

10.6 Notes and Precautions ........................................................................................................ 290

10.6.1 Contention between TCNT Write and Clear......................................................... 290

10.6.2 Contention between TCNT Word Write and Increment....................................... 291

10.6.3 Contention between TCNT Byte Write and Increment......................................... 292

10.6.4 Contention between GR Write and Compare Match............................................ 293

10.6.5 Contention between TCNT Write and Overflow/Underflow................................ 294

10.6.6 Contention between General Register Read and Input Capture............................ 295

10.6.7 Contention Between Counter Clearing by Input Capture and

Counter Increment................................................................................................. 296

10.6.8 Contention between General Register Write and Input Capture........................... 297

10.6.9 Note on Waveform Cycle Setting ......................................................................... 297

10.6.10 Contention between BR Write and Input Capture ................................................ 298

10.6.11 Note on Writing in Synchronizing Mode.............................................................. 299

10.6.12 Note on Setting Reset-Synchronized PWM Mode/Complementary

PWM Mode........................................................................................................... 299

10.6.13 Clearing Complementary PWM Mode ................................................................. 300

10.6.14 Note on Counter Clearing by Input Capture ......................................................... 300

10.6.15 ITU Operating Modes ........................................................................................... 301

Section 11 Programmable Timing Pattern Controller (TPC).................................. 309

11.1 Overview ............................................................................................................................ 309

11.1.1 Features ................................................................................................................. 309

vi

Page 28

11.1.2 Block Diagram...................................................................................................... 310

11.1.3 Input/Output Pins.................................................................................................. 311

11.1.4 Registers................................................................................................................312

11.2 Register Descriptions.......................................................................................................... 313

11.2.1 Port B Control Registers 1 and 2 (PBCR1, PCBR2) ............................................ 313

11.2.2 Port B Data Register (PBDR)................................................................................ 314

11.2.3 Next Data Register A (NDRA) ............................................................................. 314

11.2.4 Next Data Register B (NDRB).............................................................................. 316

11.2.5 Next Data Enable Register A (NDERA)............................................................... 318

11.2.6 Next Data Enable Register B (NDERB)............................................................... 318

11.2.7 TPC Output Control Register (TPCR).................................................................. 319

11.2.8 TPC Output Mode Register (TPMR).................................................................... 321

11.3 Operation............................................................................................................................ 322

11.3.1 Overview............................................................................................................... 322

11.3.2 Output Timing....................................................................................................... 323

11.3.3 Examples of Use of Ordinary TPC Output ........................................................... 324

11.3.4 TPC Output Non-Overlap Operation.................................................................... 327

11.3.5 TPC Output by Input Capture............................................................................... 331

11.4 Usage Notes........................................................................................................................ 332

11.4.1 Non-Overlap Operation......................................................................................... 332

Section 12 Watchdog Timer (WDT)............................................................................... 335

12.1 Overview ............................................................................................................................ 335

12.1.1 Features ................................................................................................................. 335

12.1.2 Block Diagram...................................................................................................... 336

12.1.3 Pin Configuration.................................................................................................. 336

12.1.4 Register Configuration.......................................................................................... 337

12.2 Register Descriptions.......................................................................................................... 337

12.2.1 Timer Counter (TCNT)......................................................................................... 337

12.2.2 Timer Control/Status Register (TCSR)................................................................. 338

12.2.3 Reset Control/Status Register (RSTCSR)............................................................. 339

12.2.4 Notes on Register Access...................................................................................... 340

12.3 Operation............................................................................................................................ 342

12.3.1 Operation in Watchdog Timer Mode.................................................................... 342

12.3.2 Operation in Interval Timer Mode........................................................................ 344

12.3.3 Operation in Standby Mode.................................................................................. 344

12.3.4 Timing of Overflow Flag (OVF) Setting.............................................................. 345

12.3.5 Timing of Watchdog Timer Overflow Flag (WOVF) Setting.............................. 345

12.4 Usage Notes........................................................................................................................ 346

12.4.1 TCNT Write and Increment Contention................................................................ 346

12.4.2 Changing CKS2–CKS0 Bit Values....................................................................... 346

12.4.3 Changing Watchdog Timer/Interval Timer Modes............................................... 346

12.4.4 System Reset With WDTOVF.............................................................................. 347

vii

Page 29

12.4.5 Internal Reset With Watchdog Timer ................................................................... 347

Section 13 Serial Communication Interface (SCI) ..................................................... 349

13.1 Overview ............................................................................................................................ 349

13.1.1 Features ................................................................................................................. 349

13.1.2 Block Diagram...................................................................................................... 350

13.1.3 Input/Output Pins.................................................................................................. 351

13.1.4 Register Configuration.......................................................................................... 351

13.2 Register Descriptions.......................................................................................................... 352

13.2.1 Receive Shift Register........................................................................................... 352

13.2.2 Receive Data Register........................................................................................... 352

13.2.3 Transmit Shift Register ......................................................................................... 353

13.2.4 Transmit Data Register.......................................................................................... 353

13.2.5 Serial Mode Register............................................................................................. 354

13.2.6 Serial Control Register.......................................................................................... 356

13.2.7 Serial Status Register............................................................................................ 359

13.2.8 Bit Rate Register (BRR)........................................................................................ 363

13.3 Operation............................................................................................................................ 372

13.3.1 Overview............................................................................................................... 372

13.3.2 Operation in Asynchronous Mode........................................................................ 374

13.3.3 Multiprocessor Communication............................................................................ 385

13.3.4 Synchronous Operation......................................................................................... 393

13.4 SCI Interrupt Sources and the DMAC................................................................................ 403

13.5 Usage Notes........................................................................................................................ 403

Section 14 A/D Converter.................................................................................................. 407

14.1 Overview ............................................................................................................................ 407

14.1.1 Features ................................................................................................................. 407

14.1.2 Block Diagram...................................................................................................... 408

14.1.3 Configuration of Input Pins................................................................................... 409

14.1.4 Configuration of A/D Registers............................................................................ 410

14.2 Register Descriptions.......................................................................................................... 410

14.2.1 A/D Data Registers A–D (ADDRA–ADDRD)..................................................... 410

14.2.2 A/D Control/Status Register (ADCSR) ................................................................ 411

14.2.3 A/D Control Register (ADCR).............................................................................. 413

14.3 CPU Interface ..................................................................................................................... 414

14.4 Operation............................................................................................................................ 416

14.4.1 Single Mode (SCAN = 0)...................................................................................... 416

14.4.2 Scan Mode (SCAN = 1)........................................................................................ 418

14.4.3 Input Sampling Time and A/D Conversion Time................................................. 420

14.4.4 A/D Conversion Start by External Trigger Input.................................................. 421

14.5 Interrupts and DMA Transfer Requests ............................................................................. 421

14.6 Definitions of A/D Conversion Accuracy.......................................................................... 422

viii

Page 30

14.7 A/D Converter Usage Notes............................................................................................... 423

14.7.1 Setting Analog Input Voltage................................................................................ 423