Page 1

No. 0105

CL2554AN

SERVICE MANUAL

MANUEL D’ENTRETIEN

CAUTION:

Data contained within this Service

Verbesserungen ändern.

WARTUNGSHANDBUCH

Before servicing this chassis, it is important that the service technician read

the “Safety Precautions” and “Product Safety Notices” in this service manual.

ATTENTION:

Avant d’effectuer l’entretien du châassis, le technicien doit lire les

«Précautions de sécurité» et les «Notices de sécurité du produit» présentés

dans le présent manuel.

VORSICHT:

Vor Öffnen des Gehäuses hat der Service-Ingenieur die „Sicherheitshinweise“

und „Hinweise zur Produktsicherheit“ in diesem Wartungshandbuch zu lesen.

CL2854AN

manual is subject to alteration for

improvement.

Les données fournies dans le

présent manuel d’entretien

peuvent faire l’objet de

modifications en vue de

perfectionner le produit.

Die in diesem Wartungshandbuch

enthaltenen Spezifikationen

können sich zwecks

December 1999

Page 2

1 - Main features

1-1 Specifications

1-2 Channel table

1-3 ATSS sorting method

2 - Safety instruction

3 - Alignment instructions

3-1 Microcontroller configuration : Service mode

3-2 Microcontroller configuration : Option

3-3 TV set Alignment

4 - IC description

4-1 TDA936x TV signal processor - Teletext decoder with embedded m-Controller.

4-2 MSP3415D Multistandard Sound Processor

4-3 TDA894xJ Stereo Audio Amplifier

4-4 TDA835xJ Vertical Amplifier

4-4-1 TDA8357J

4-4-1 TDA8358J

4-5 TDA6107Q

4-6 24C08 8 Kbit EEPROM

4-7 STR - F6653

Service manual CL2554AN / CL2854AN

Contents

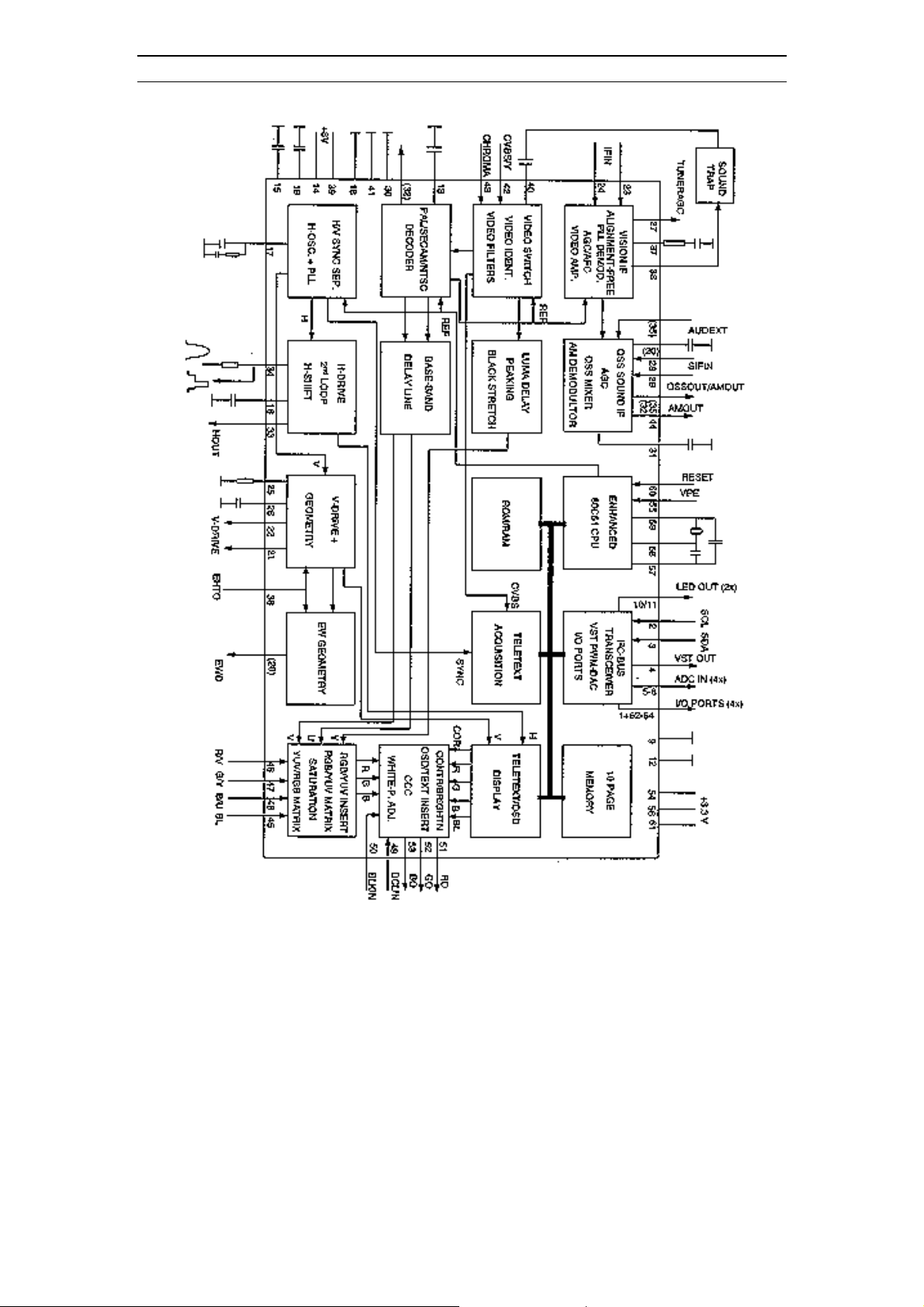

5 - Circuit description

5-1 Block diagram

5-2 IF

5-3 Source switching

5-4 m-Controller I/O pin configuration and function

5-5 Sound processing

5-6 Sound amplification

5-7 Vertical deflection

5-8 Power supply (STR F6653)

5-9 TV start-up, TV normal run and stand by mode operations

6 - Replacement parts list

- 1 -

Page 3

1-1 Specifications

Service manual CL2554AN / CL2854AN

TV standard

Sound system

Power consumption

Sound Output Power

Speaker

Teletext system

Aerial input

Channel coverage

Tuning system

Visual screen size

Channel indication

Program Selection

Aux. terminal

Remote Control Unit

PAL - SECAM B/G D/K, PAL I/I, SECAM L/L’

NICAM B/G, I, D/K, L,

FM 2Carrier B/G, D/K

21” : 49 W approx.

28” : 75 W approx.

21” : 4.5W x 2 (at 60% mod, 10%THD)

28” : 7W x 2 (at 60% mod, 10%THD)

20”, 21” : 7W 8 ohm x2

25”, 28” : 12W 8 ohm x2

10 pages memory FASTEXT (FLOF or TOP)

75 ohm unbalanced

Off-air channels, S-cable channels and hyperband

frequency synthesiser tuning system

20” : 48 cm

21” : 51 cm

25” : 59 cm

28” : 66 cm

On Screen Display

100 programmes

EURO-SCART 1 : Audio / Video In and Out, R/G/B In, Slow and

Fast switching.

EURO-SCART 2 : Audio / Video In, SVHS In.

Audio-Video Jack on front of cabinet in common connection with

EURO-SCART 2.

Headphone jack (3.5 mm) on front of cabinet

R-40A01

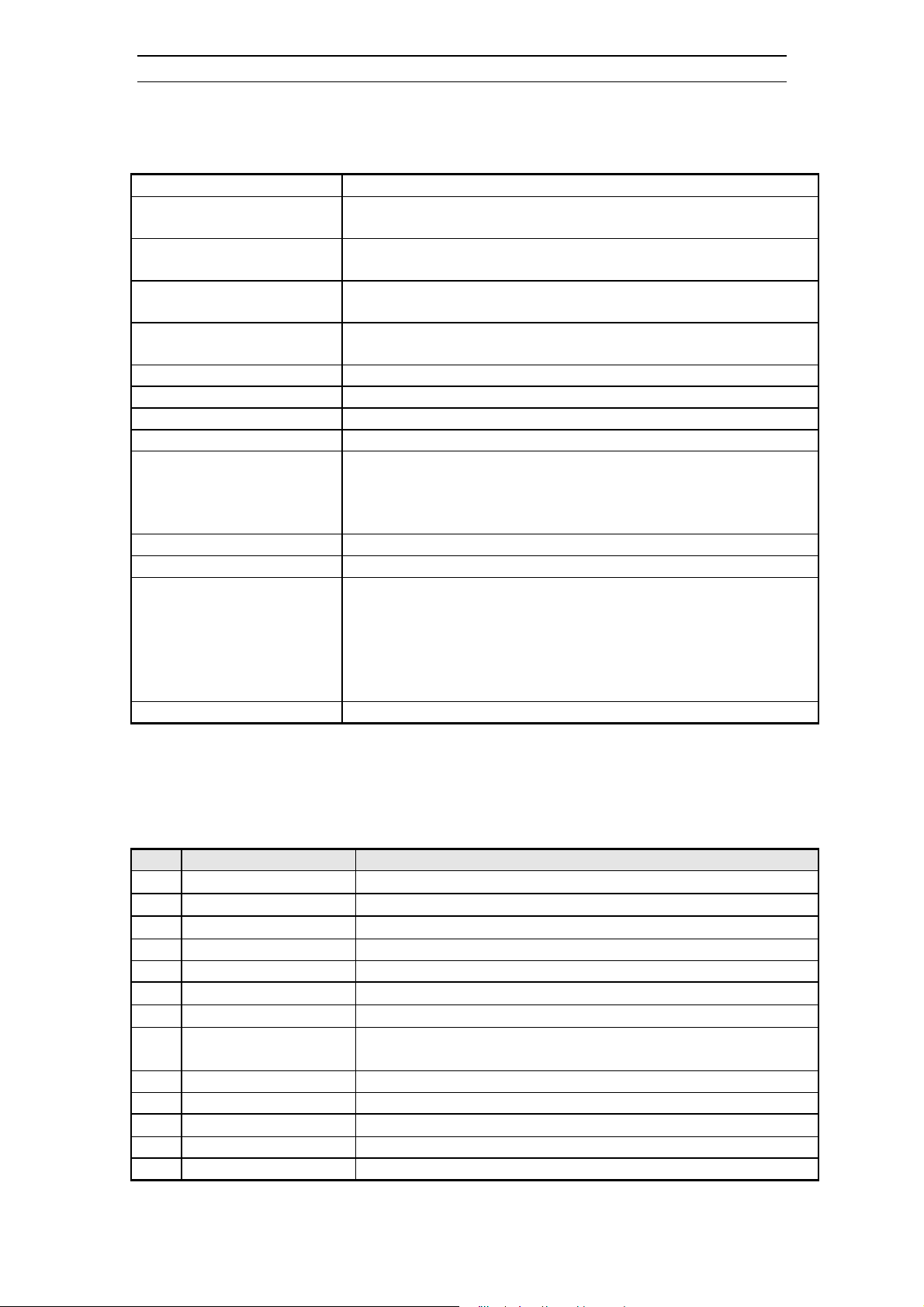

21 Pin EURO-SCART 1 :

Pin Signal Description Matching value

1 Audio Output Right

2 Audio Input Right

3 Audio Output Left

0.5 Vrms, Impedance < 1 kW, ( RF 54% Mod )

0.5 Vrms, Impedance > 10 kW

0.5 Vrms, Impedance < 1 kW, ( RF 54% Mod )

4 Audio Earth

5 Blue Earth

6 Audio Input Left

7 Blue Input

0.5 Vrms, Impedance > 10 kW

0.7 Vpp ±0.1V, Impedance 75W

8 Slow Switching TV : 0 to 2V, AV 16/9 : 4.5 to 7V, AV 4/3 : 9.5 to 12V ,

Impedance > 10 kW

9 Green Earth

10 N.C.

11 Green Input

0.7 Vpp ± 0.1V, Impedance 75W

12 N.C.

13 Red Earth

- 2 -

Page 4

14 Blanking Earth

15 Red Input

16 Fast Switching

0.7 Vpp ± 0.1V, Impedance 75W

0 to 0.4V : Logic “0”, 1 to 3V : Logic “1”, Impedance 75W

17 Video Out Earth

18 Video In Earth

19 Video Output

20 Video Input

1 Vpp ± 3dB, Impedance 75W

1 Vpp ± 3dB, Impedance 75W

21 Common Earth

21 Pin EURO-SCART 2 :

Pin Signal Description Matching value

1 N.C.

2 Audio Input Right

0.5 Vrms, Impedance > 10 kW

3 N.C.

4 Audio Earth

5 Earth

6 Audio Input Left

0.5 Vrms, Impedance > 10 kW

7 N.C.

8 N.C.

9 N.C.

10 N.C.

11 N.C.

12 N.C.

13 Earth

14 Earth

15 Chroma Input

± 3dB for a luminance signal of 1 Vpp

16 N.C.

17 Earth

18 Video In Earth

19 N.C.

20 Video Input, Y In.

1 Vpp ± 3dB, Impedance 75W

21 Common Earth

Service manual CL2554AN / CL2854AN

- 3 -

Page 5

Service manual CL2554AN / CL2854AN

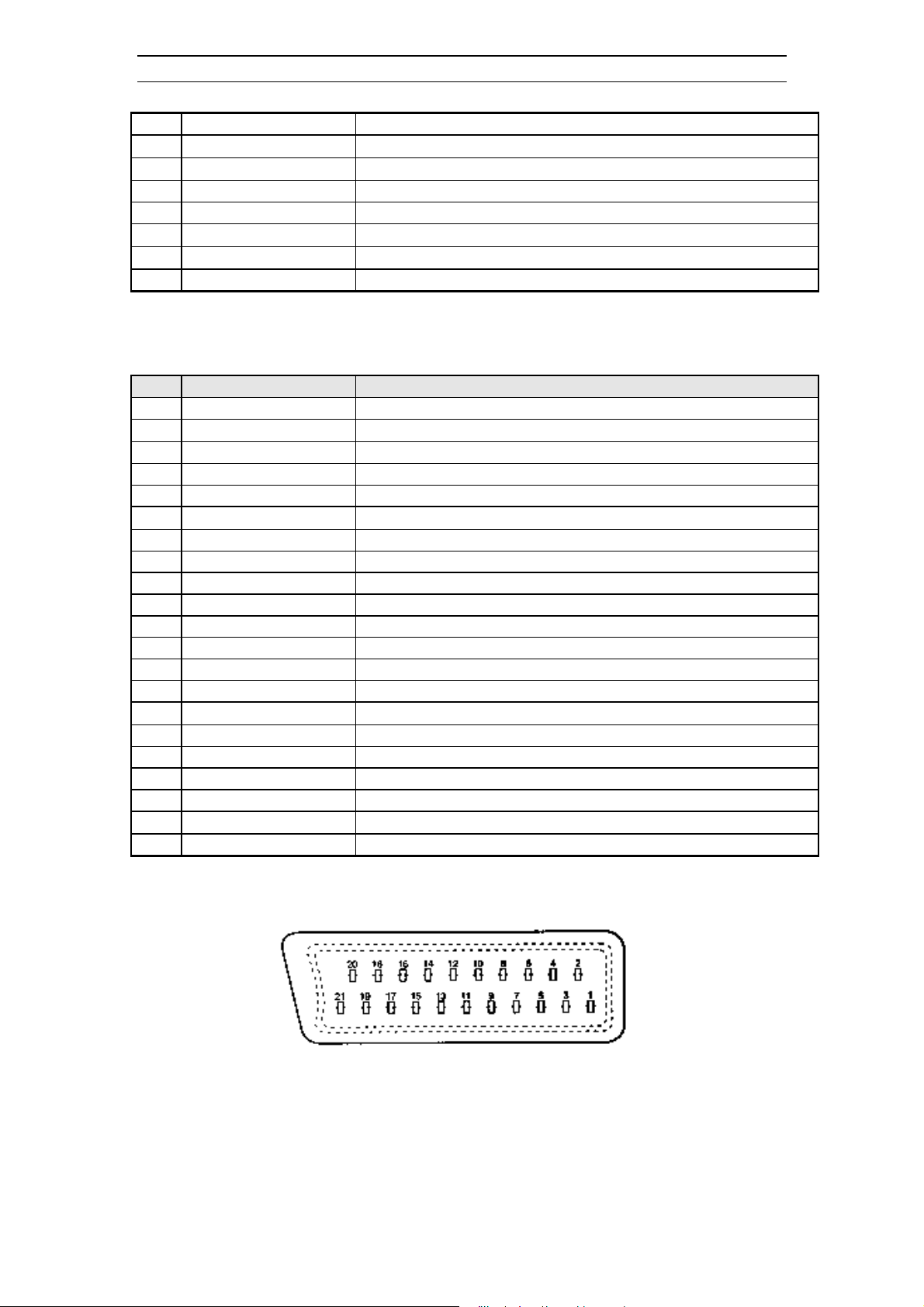

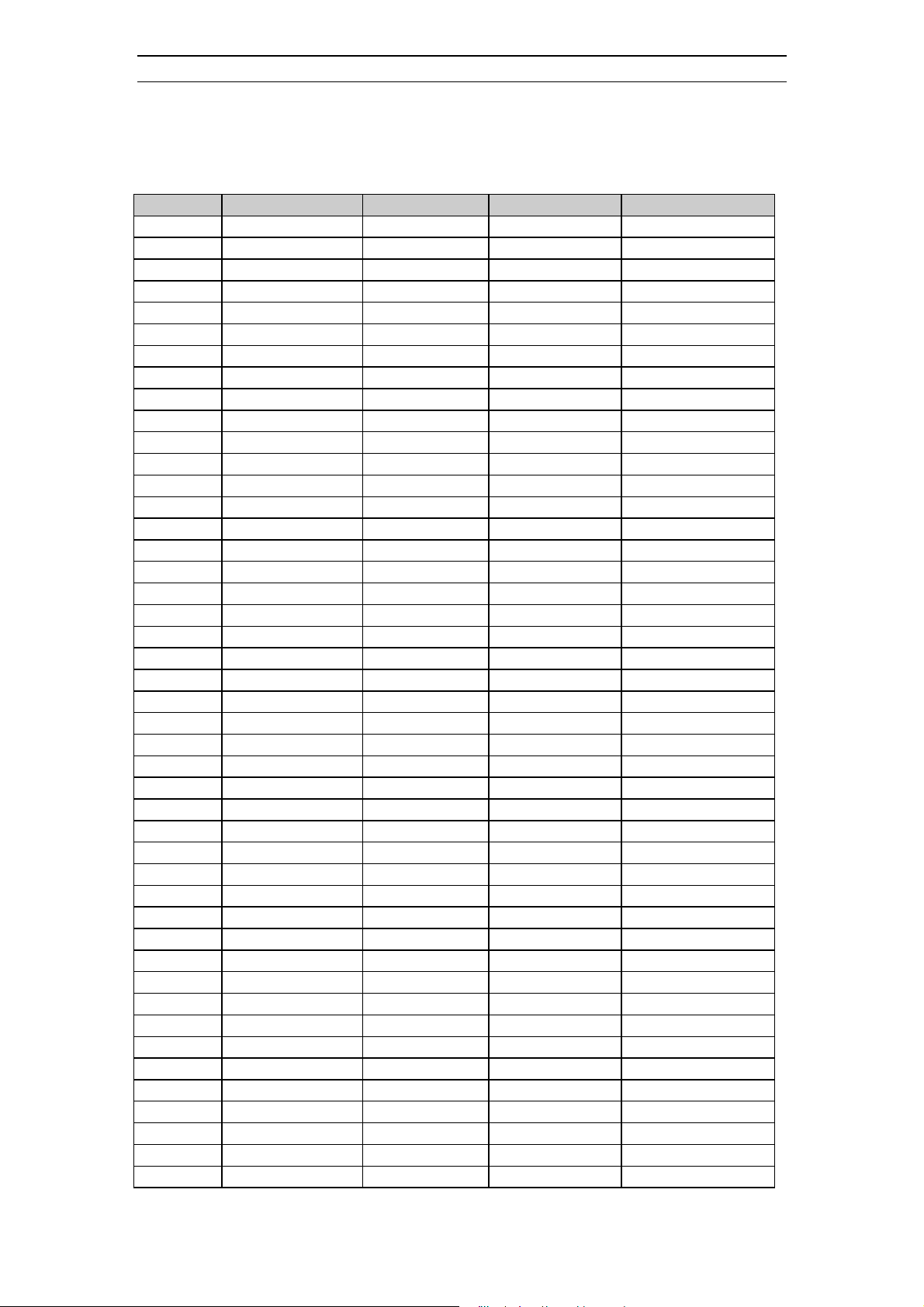

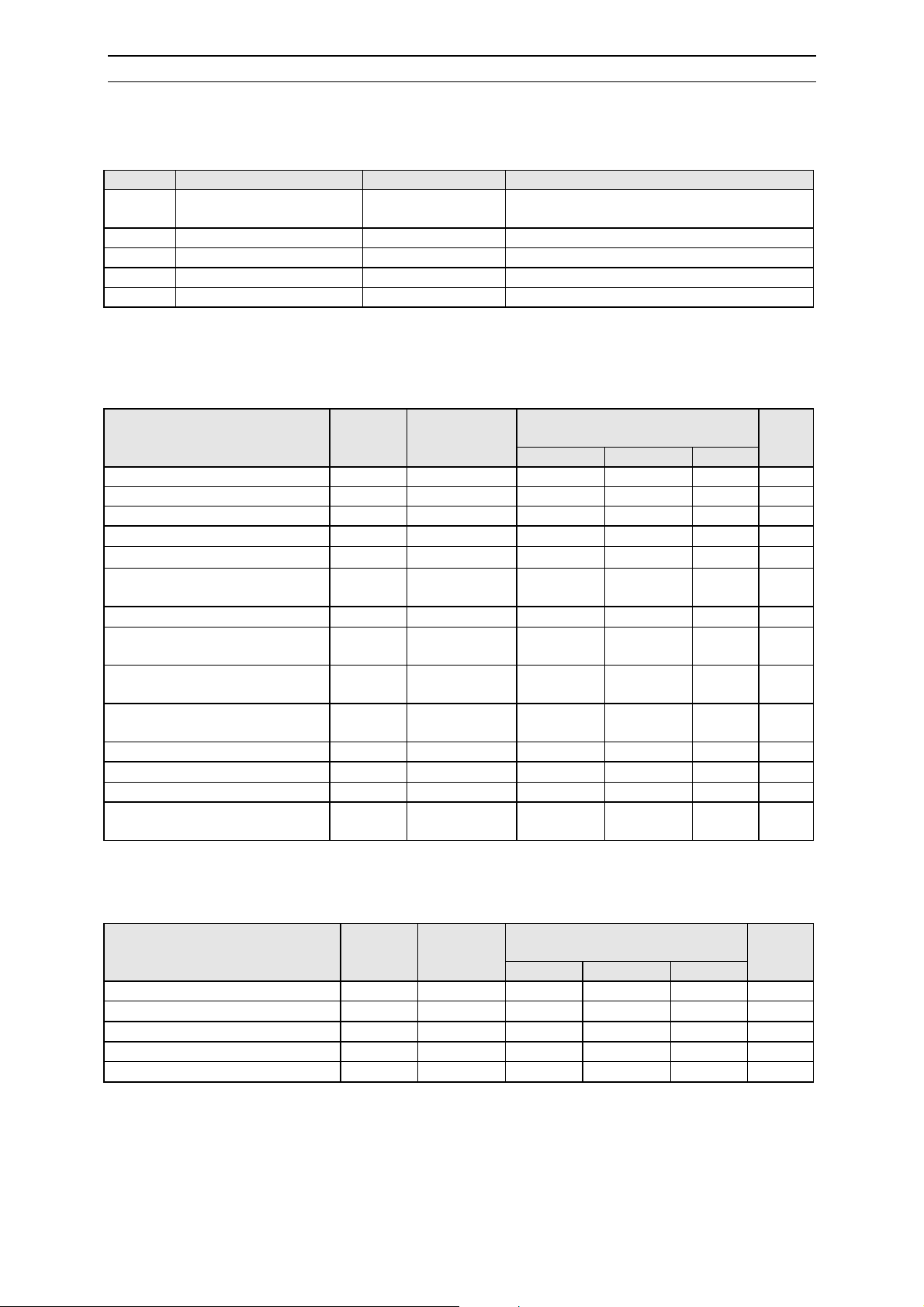

1-2 Channel table

FREQUENCY TABLE

CH EUROPE CCIR FRANCE GB(IRELAND) EAST OIRT

C01

C02

C03

C04

C05

C06

C07

C08

C09

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

C21

C22

C23

C24

C25

C26

C27

C28

C29

C30

C31

C32

C33

C34

C35

C36

C37

C38

C39

C40

C41

C42

C43

C44

C45

46.25 47.75 (L') 45.75 49.75

48.25 55.75 (L') 53.75 59.25

55.25 60.5 (L') 61.75 77.25

62.25 63.75 (L') 175.25 85.25

175.25 176.00 183.25 93.25

182.25 184.00 191.25 175.25

189.25 192.00 199.25 183.25

196.25 200.00 207.25 191.25

203.25 208.00 215.25 199.25

210.25 216.00 223.25 207.25

217.25 189.25 (LUX) 231.25 215.25

224.25 69.25 (L') 239.25 223.25

53.75 76.25 (L') 247.25 -

- 83.25 (L') 49.75 -

82.25 90.25 57.75 -

- 97.25 65.75 -

183.75 - 77.75 -

192.25 - 85.75 -

201.25 - - -

- - - -

471.25 471.25 471.25 471.25

479.25 479.25 479.25 479.25

487.25 487.25 487.25 487.25

495.25 495.25 495.25 495.25

503.25 503.25 503.25 503.25

511.25 511.25 511.25 511.25

519.25 519.25 519.25 519.25

527.25 527.25 527.25 527.25

535.25 535.25 535.25 535.25

543.25 543.25 543.25 543.25

551.25 551.25 551.25 551.25

559.25 559.25 559.25 559.25

567.25 567.25 567.25 567.25

575.25 575.25 575.25 575.25

583.25 583.25 583.25 583.25

591.25 591.25 591.25 591.25

599.25 599.25 599.25 599.25

607.25 607.25 607.25 607.25

615.25 615.25 615.25 615.25

623.25 623.25 623.25 623.25

631.25 631.25 631.25 631.25

639.25 639.25 639.25 639.25

647.25 647.25 647.25 647.25

655.25 655.25 655.25 655.25

663.25 663.25 663.25 663.25

- 4 -

Page 6

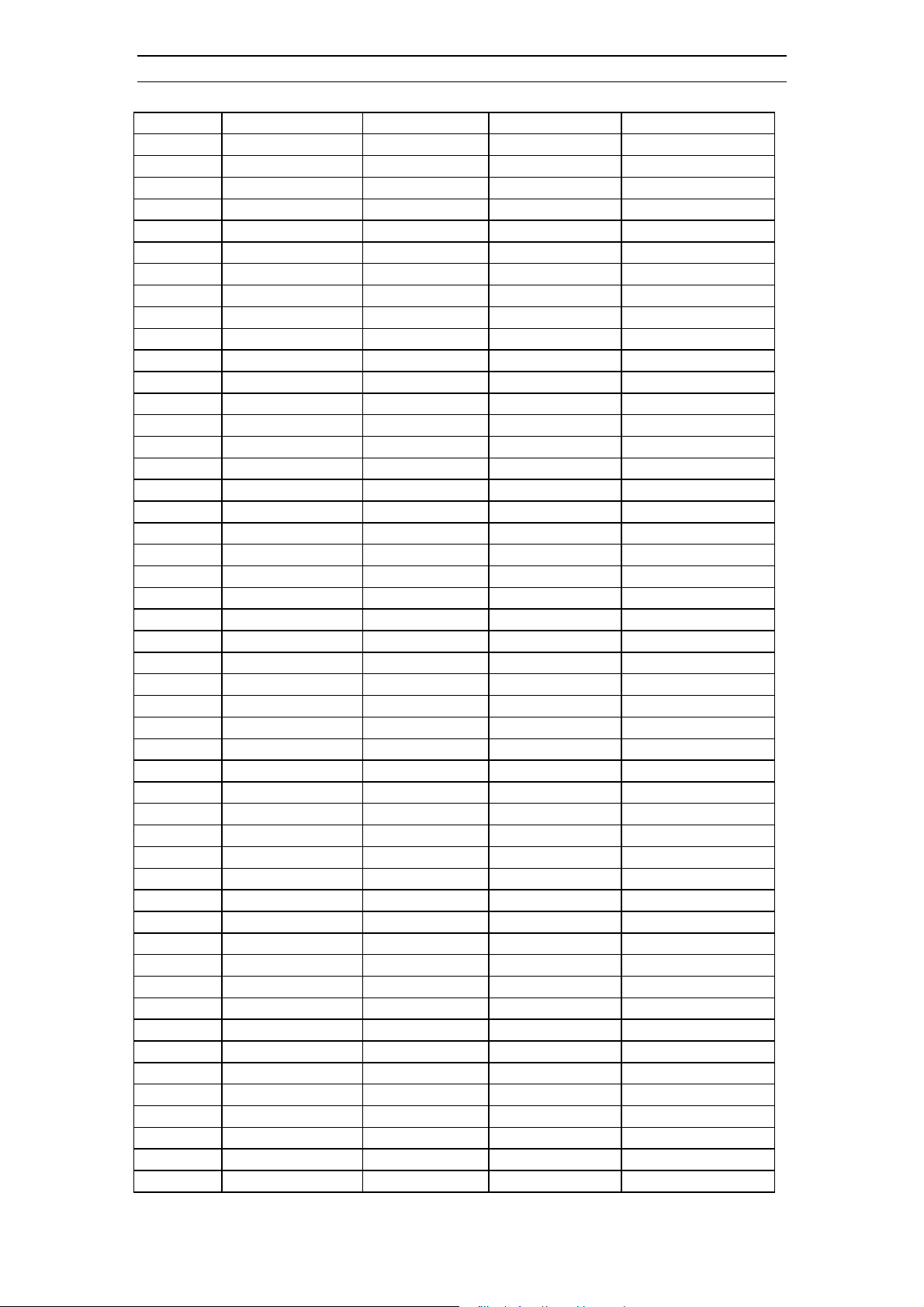

Service manual CL2554AN / CL2854AN

C46

C47

C48

C49

C50

C51

C52

C53

C54

C55

C56

C57

C58

C59

C60

C61

C62

C63

C64

C65

C66

C67

C68

C69

C70

C71

C72

C73

C74

C75

C76

C77

S01

S02

S03

S04

S05

S06

S07

S08

S09

S10

S11

S12

S13

S14

S15

S16

S17

S18

671.25 671.25 671.25 671.25

679.25 679.25 679.25 679.25

687.25 687.25 687.25 687.25

695.25 695.25 695.25 695.25

703.25 703.25 703.25 703.25

711.25 711.25 711.25 711.25

719.25 719.25 719.25 719.25

727.25 727.25 727.25 727.25

735.25 735.25 735.25 735.25

743.25 743.25 743.25 743.25

751.25 751.25 751.25 751.25

759.25 759.25 759.25 759.25

767.25 767.25 767.25 767.25

775.25 775.25 775.25 775.25

783.25 783.25 783.25 783.25

791.25 791.25 791.25 791.25

799.25 799.25 799.25 799.25

807.25 807.25 807.25 807.25

815.25 815.25 815.25 815.25

823.25 823.25 823.25 823.25

831.25 831.25 831.25 831.25

839.25 839.25 839.25 839.25

847.25 847.25 847.25 847.25

855.25 855.25 855.25 855.25

863.25 863.25 863.25 863.25

69.25 - - -

76.25 - - -

83.25 - - -

90.25 - - -

97.25 - - -

59.25 - - -

93.25 - - -

105.25 104.75 103.25 105.25

112.25 116.75 111.25 112.25

119.25 128.75 119.25 119.25

126.25 140.75 127.25 126.25

133.25 152.75 135.25 133.25

140.25 164.75 143.25 140.25

147.25 176.75 151.25 147.25

154.25 188.75 159.25 154.25

161.25 200.75 167.25 161.25

168.25 212.75 - 168.25

231.25 224.75 - 231.25

238.25 236.75 - 238.25

245.25 248.75 255.25 245.25

252.25 260.75 263.25 252.25

259.25 272.75 271.25 259.25

266.25 284.75 279.25 266.25

273.25 296.75 287.25 273.25

280.25 136.00 295.25 280.25

- 5 -

Page 7

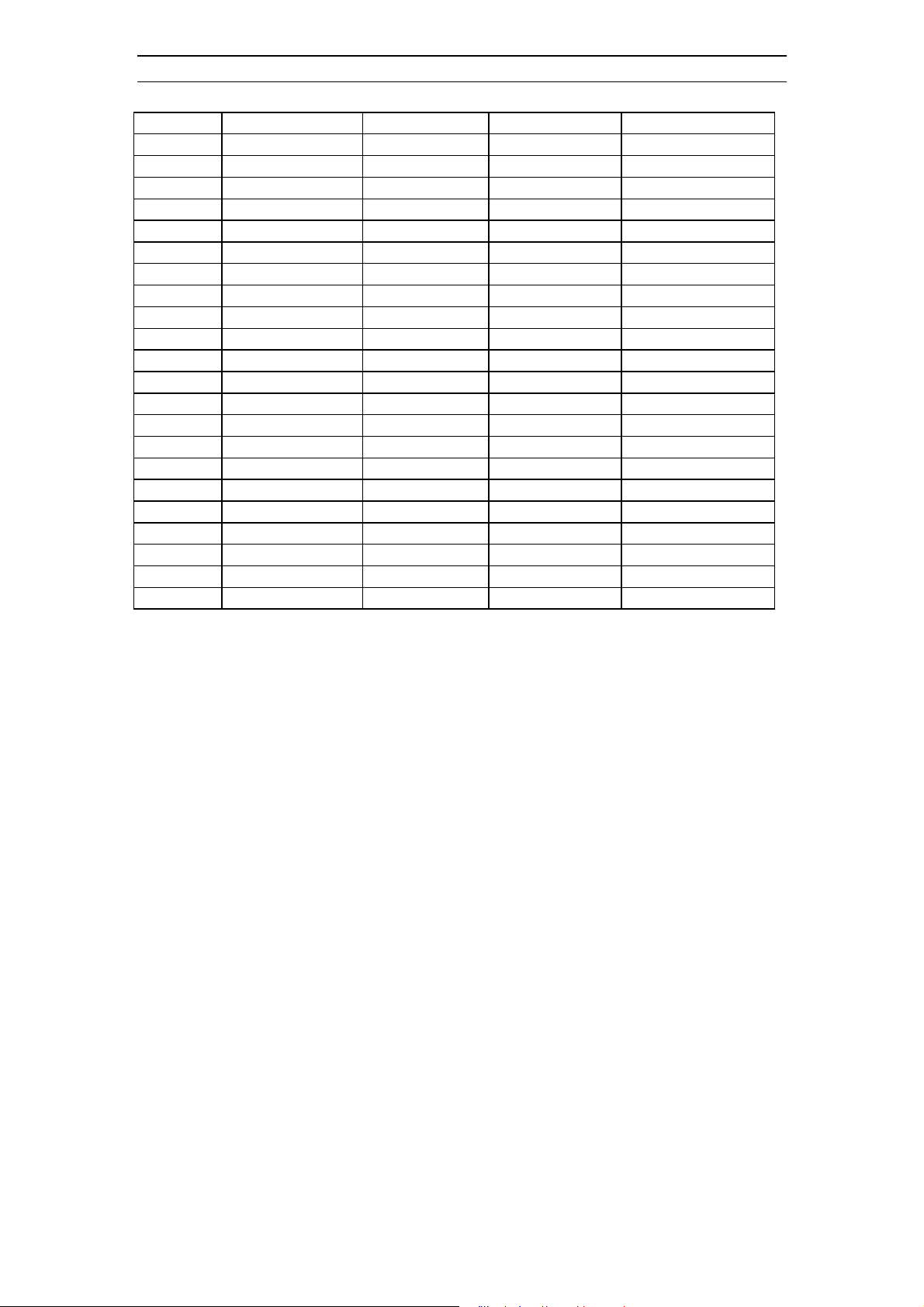

Service manual CL2554AN / CL2854AN

S19

S20

S21

S22

S23

S24

S25

S26

S27

S28

S29

S30

S31

S32

S33

S34

S35

S36

S37

S38

S39

S40

S41

287.25 160.00 303.25 287.25

294.25 - - 294.25

303.25 303.25 - 303.25

311.25 311.25 311.25 311.25

319.25 319.25 319.25 319.25

327.25 327.25 327.25 327.25

335.25 335.25 335.25 335.25

343.25 343.25 343.25 343.25

351.25 351.25 351.25 351.25

359.25 359.25 359.25 359.25

367.25 367.25 367.25 367.25

375.25 375.25 375.25 375.25

383.25 383.25 383.25 383.25

391.25 391.25 391.25 391.25

399.25 399.25 399.25 399.25

407.25 407.25 407.25 407.25

415.25 415.25 415.25 415.25

423.25 423.25 423.25 423.25

431.25 431.25 431.25 431.25

439.25 439.25 439.25 439.25

447.25 447.25 447.25 447.25

455.25 455.25 455.25 455.25

463.25 463.25 463.25 463.25

- 6 -

Page 8

Service manual CL2554AN / CL2854AN

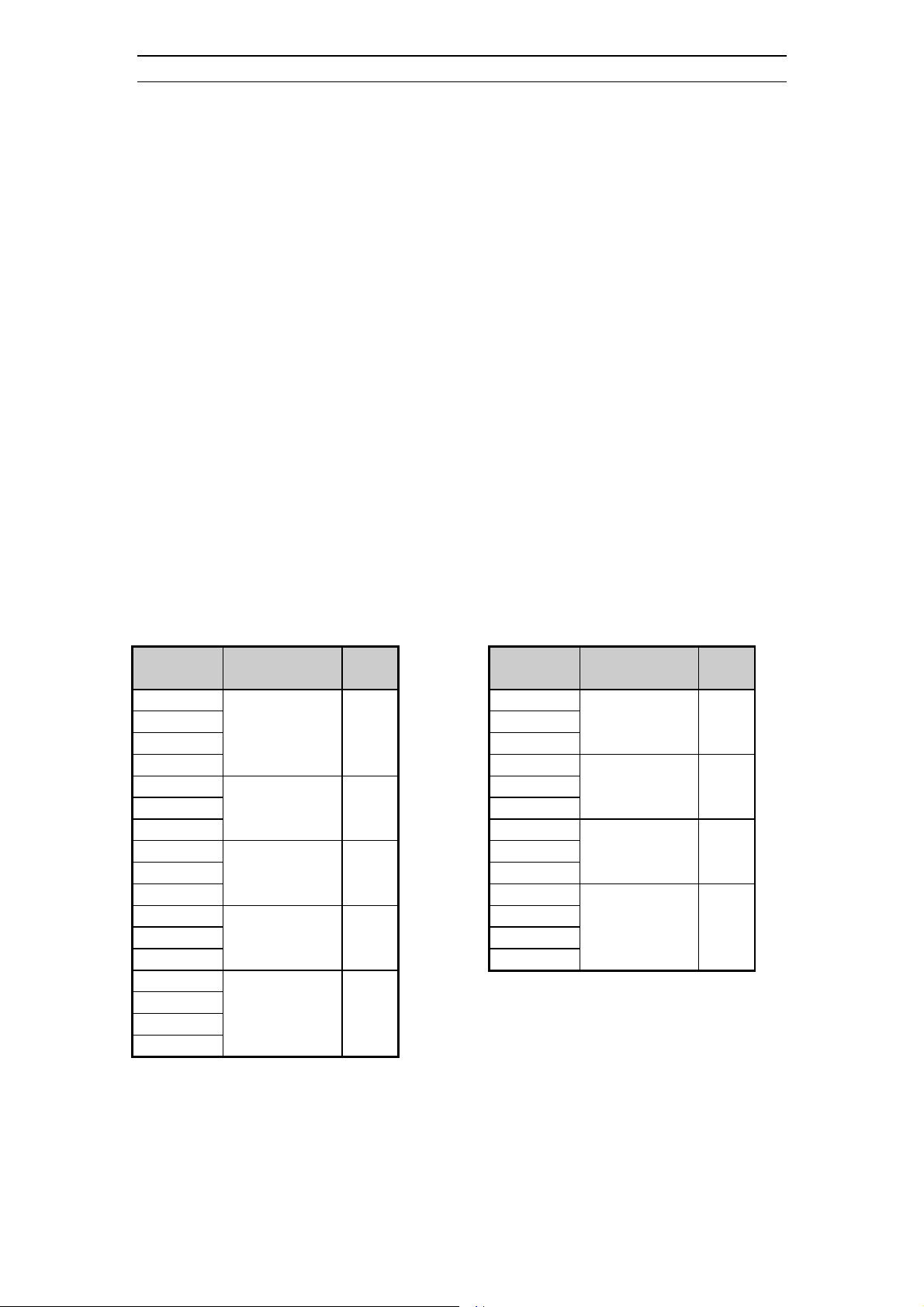

1-3 ATSS sorting method

The TV set sweeps all the TV bands from beginning of VHF to end of UHF. The TV

controlling software for each program checks if a VPS CNI code is transmitted. If no VPS CNI

code is found, the system check if a CNI code is transmitted in the teletext lines ( Packet 8/30

format 1 ). If such a code ( VPS or teletext ) is found and if this code is in the ATSS list, the

program is automatically named.

The programs found are then sorted in 4 groups :

Group I : It contains all the programs from the selected country and named by the TV

controlling software. Within this group the sorting order is fixed by the ATSS list.

Group II : It contains all the programs with a strong signal strength which are not listed in

group I.

Group III : It contains all the programs with a weak signal strength which are not listed in

group I.

Group IV : If two or more programs with the same code are found, only the strongest ( or if

they have the same level the one with the lowest frequency) is listed in group I, II or III. The

others are listed in group IV. Note : If two programs with the same name but a different code

are found these two programs are listed in group I, II or III ( e.g. Regional program SW3 in

Germany ).

The sorting order within group II, III, and IV is based on the channel frequency. The program

with the lowest frequency is allocated the first rank in its group, and so forth until the last

program of the group which has the highest frequency.

Program

number

1

2 Group I

...

n

n+1

... Group II

m

m+1

... Group III

p

p+1

... Group IV

q

Group Skip

4

Program

Group Skip

number

1

... Group II

m

m+1

... Group III

p

p+1

... Group IV

q

q+1 not used

...

99

0

4

4

q+1 not used

...

99

4

Special case : Country selection = Others

0

Special case : France

If France is selected the TV controlling software sweeps the whole TV bands firstly with France

system selected ( positive video modulation) and secondly with Europe system selected ( negative

video modulation).

- 7 -

Page 9

Service manual CL2554AN / CL2854AN

Special case : Switzerland

If Switzerland is selected the TV controlling software sweeps the whole TV bands firstly with

Europe system selected (negative video modulation) and secondly with France system selected (

positive video modulation).

Special case : GB

Note for satellite receiver users : Before starting ATSS turn On your satellite receiver and tune “

SKY NEWS “.

If GB is selected the TV controlling software seeks for programs only in UHF ( C21 to C70). The

sorting order is :

1 - BBC1

2 - BBC2

3 - ITV

4 - CH4

5 - CH5

6 - NEWS

If two or more “ identical “programs ( same name but different code e.g. BBC1 and BBC1

Scotland ) are found the following programs in the list will be shifted up. (1 - BBC1, 2 - BBC1, 3

- BBC2, 4 - ITV, 5 - CH4, 6 - CH5, 7 - NEWS, ..)

If one of the program above is not found, the associated program number remains empty

(freq.=467.25 Mhz - Skip selected - no name - system=GB).

example A : 1 - BBC1, 2 - BBC2, 3 - ITV, 4 - -----, 5 - CH5, 6 - NEWS, ...

example B ( if 2 BBC1 found ) : 1 - BBC1, 2 - BBC1, 3 - BBC2, 4 - ITV, 5 - -----, 6 - CH5, 7 NEWS, ...

- 8 -

Page 10

Service manual CL2554AN / CL2854AN

2 - Safety instruction

WARNING: Only competent service personnel may carry out work involving the testing or repair

of this equipment.

X-RAY RADIATION PRECAUTION

1. Excessive high voltage can produce potentially hazardous X-RAY RADIATION. To avoid

such hazards, the high voltage must not exceed the specified limit. The nominal value of the

high voltage of this receiver is 25-26 KV (20”-21”) or 26 KV (25” - 28”) at max beam

current. The high voltage must not, under any circumstances, exceed 27.5 KV (20”), 29KV

(21”), 29.5 KV (25") or 30 KV (28"). Each time a receiver requires servicing, the high

voltage should be checked. It is important to use an accurate and reliable high voltage meter.

2. The only source of X-RAY Radiation in this TV receiver is the picture tube. For continued

X-RAY RADIATION protection, the replacement tube must be exactly the same type tube as

specified in the parts list.

SAFETY PRECAUTION

1. Potentials of high voltage are present when this receiver is operating. Operation of the

receiver outside the cabinet or with the back board removed involves a shock hazard from the

receiver.

1) Servicing should not be attempted by anyone who is not thoroughly familiar with the

precautions necessary when working on high voltage equipment.

2) Discharge the high potential of the picture tube before handling the tube. The picture tube

is highly evacuated and if broken, glass fragments will be violently expelled.

2. If any Fuse in this TV receiver is blown, replace it with the FUSE specified in the

Replacement Parts List.

3. When replacing a high wattage resistor (oxide metal film resistor) in circuit board, keep the

resistor 10 mm away from circuit board.

4. Keep wires away from high voltage or high temperature components.

5. This receiver must operate under AC 230 volts, 5O Hz. NEVER connect to DC supply or

any other power or frequency.

PRODUCT SAFETY NOTICE

Many electrical and mechanical parts in this equipment have special safety-related characteristics.

These characteristics are often passed unnoticed by a visual inspection and the X-RAY

RADIATION protection afforded by them cannot necessarily be obtained by using replacement

components rated for higher voltage, wattage, etc. Replacement parts which have these special

safety characteristics are identified in this manual and its supplements, electrical components

having such features are identified by designated symbol on the parts list. Before replacing any of

these components, read the parts list in this manual carefully. The use of substitutes replacement

parts which do not have the same safety characteristics as specified in the parts list may create XRAY Radiation.

- 9 -

Page 11

Service manual CL2554AN / CL2854AN

3 - Alignment instructions

3-1 Microcontroller configuration : Service mode

To switch the TV set into service mode please see instruction below.

1 - Select pr. number 91

2 - Adjust sharpness to minimum and exit all menu.

3 - Quickly press the key sequence : RED - GREEN - menu

To exit SERVICE menu press menu key or Std By key.

In Service Mode press “OK” to stop the microcontroller i.e. the I2C bus is free and the set can be

controlled by external equipment. Press “OK” again to allow the microcontroller to control the set

again

3-2 Microcontroller configuration : Option

Option Tuner maker Cut off / Video Amp.

0 DAEWOO / SAMSUNG 140V / 92V

1 DAEWOO / SAMSUNG

2 SIEL 140V / 92V

3-3 TV set Alignment

3-3-1 - G2 alignment

- TV in AV mode without video signal Þ Black screen.

- TV pre-set with WP Red, WP Green and WP Blue equal to 32.

- TV pre-set with Black R, Black G equal to 8.

- Set TV in NORMAL I mode

- Adjust screen volume ( on FBT ) such that the highest cathode cut-off voltage measured on CRT

board, is V cut off ± 5V.

Screen size V cut-off

20” & 21” 125 V

25” & 28” 140 V

3-3-2 - White balance

- Select a dark picture and adjust Black G and Black R to the desired colour temperature.

- Select a bright picture and adjust WP Red, WP Green, WP Blue to the desired colour

temperature.

3-3-3 - Focus

- Adjust the Focus volume ( on FBT ) to have the best resolution on screen.

3-3-4 - Vertical geometry

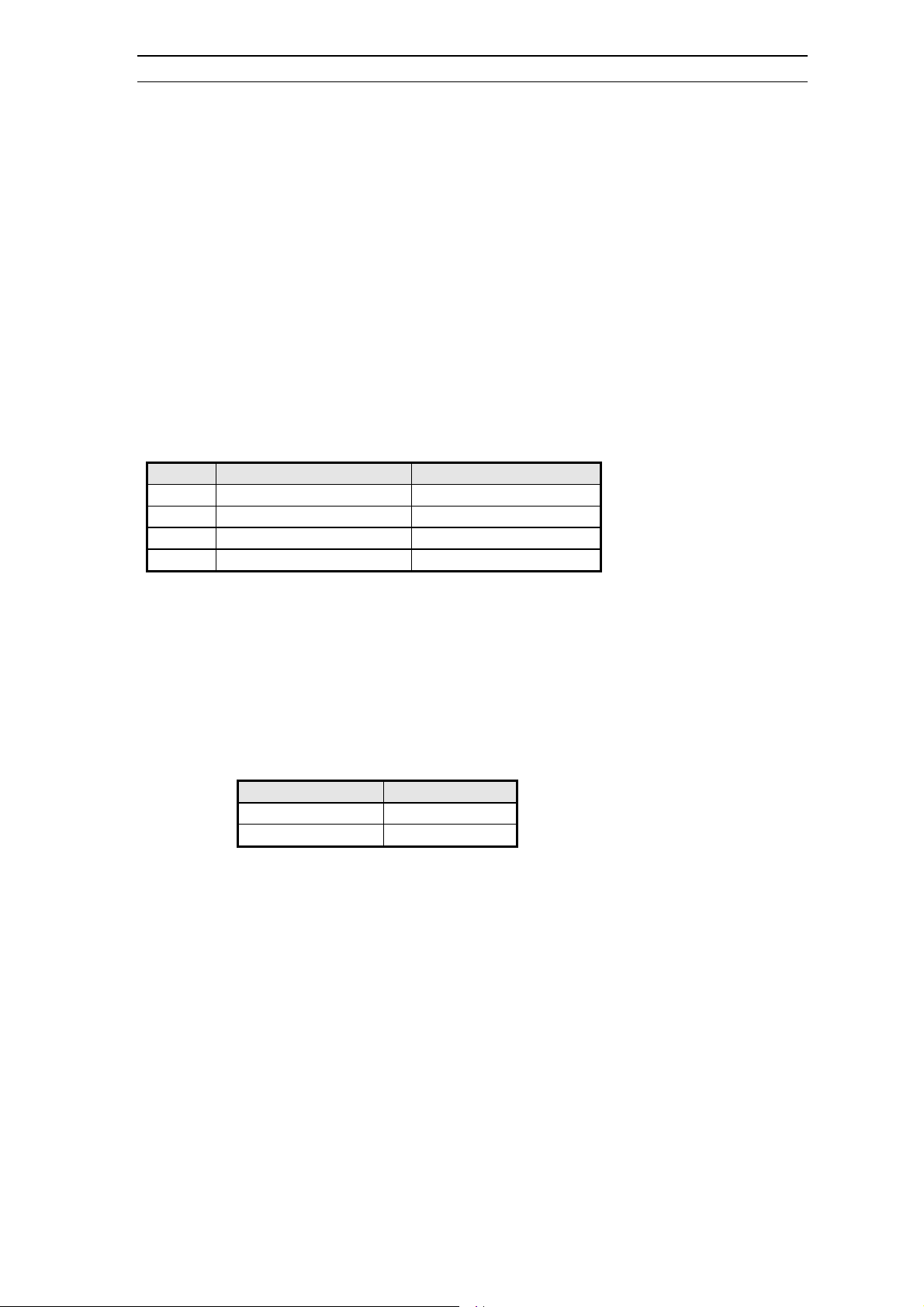

- Adjust the Vertical Amplitude, Shift, S-

Correction and Slope to compensate for

vertical distortion.

- 10 -

Page 12

Service manual CL2554AN / CL2854AN

3-3-5 - Horizontal picture centring

- Adjust H Shift to have the picture in the centre of the screen.

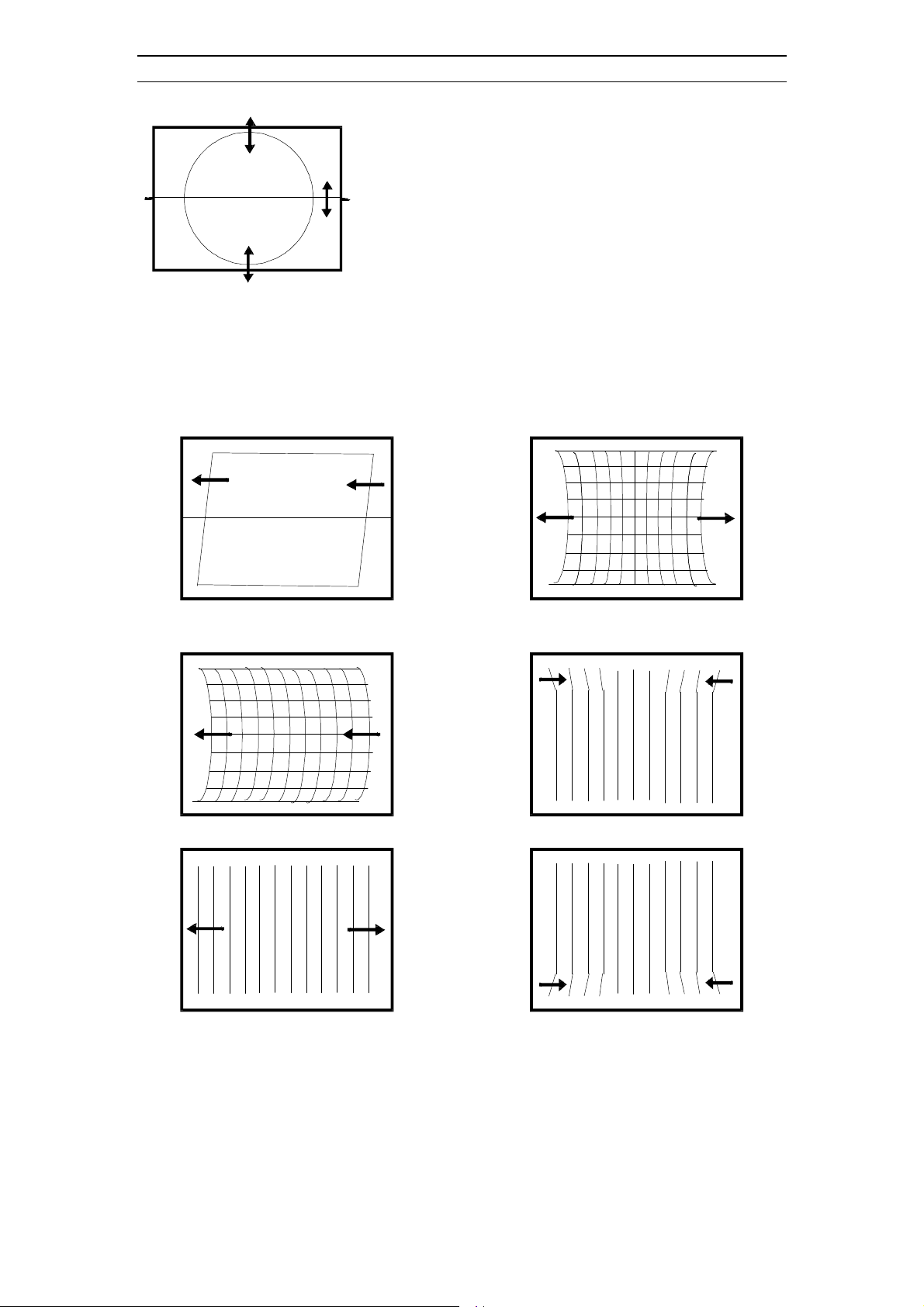

3-3-6 - East / West correction

- Adjust the H Parall, H Bow, H Width, EW Parabo, Up Corner, Dw Corner, EW trapez to

compensate for geometrical distortion.

H. Parall

H. Bow

H.Width

EW.Parabo

Up Corner

Dw Corner

- 11 -

Page 13

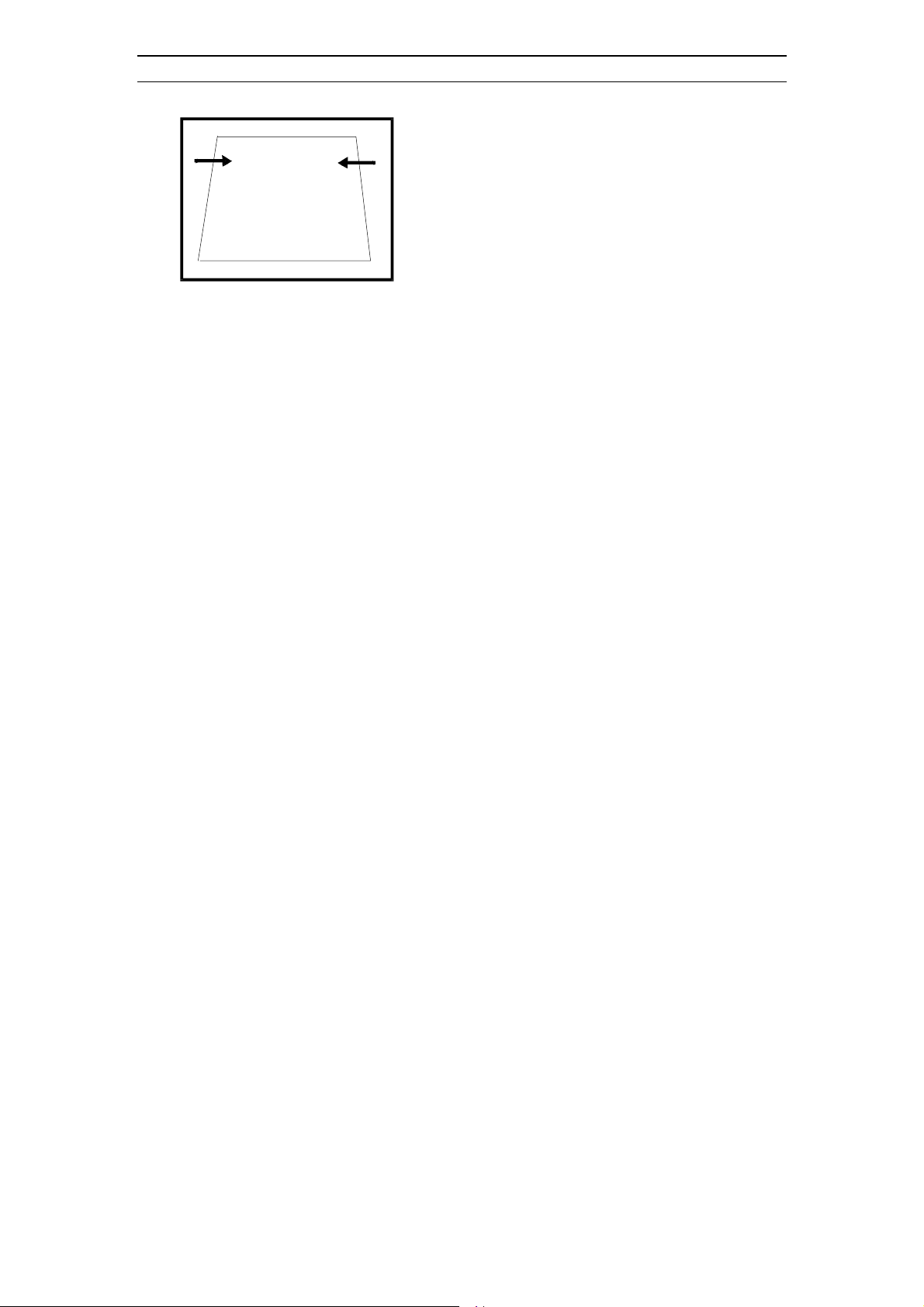

Service manual CL2554AN / CL2854AN

EW Trapez

3-3-7 - AGC

- Adjust the antenna signal level at 68 dBmV± 2 (UHF - CH25)

- Set RF AGC to 0.

- Increase RF AGC level and stop when the level on pin 6 of TDA936x goes below 2.5 Vdc

- 12 -

Page 14

Service manual CL2554AN / CL2854AN

4 - IC description

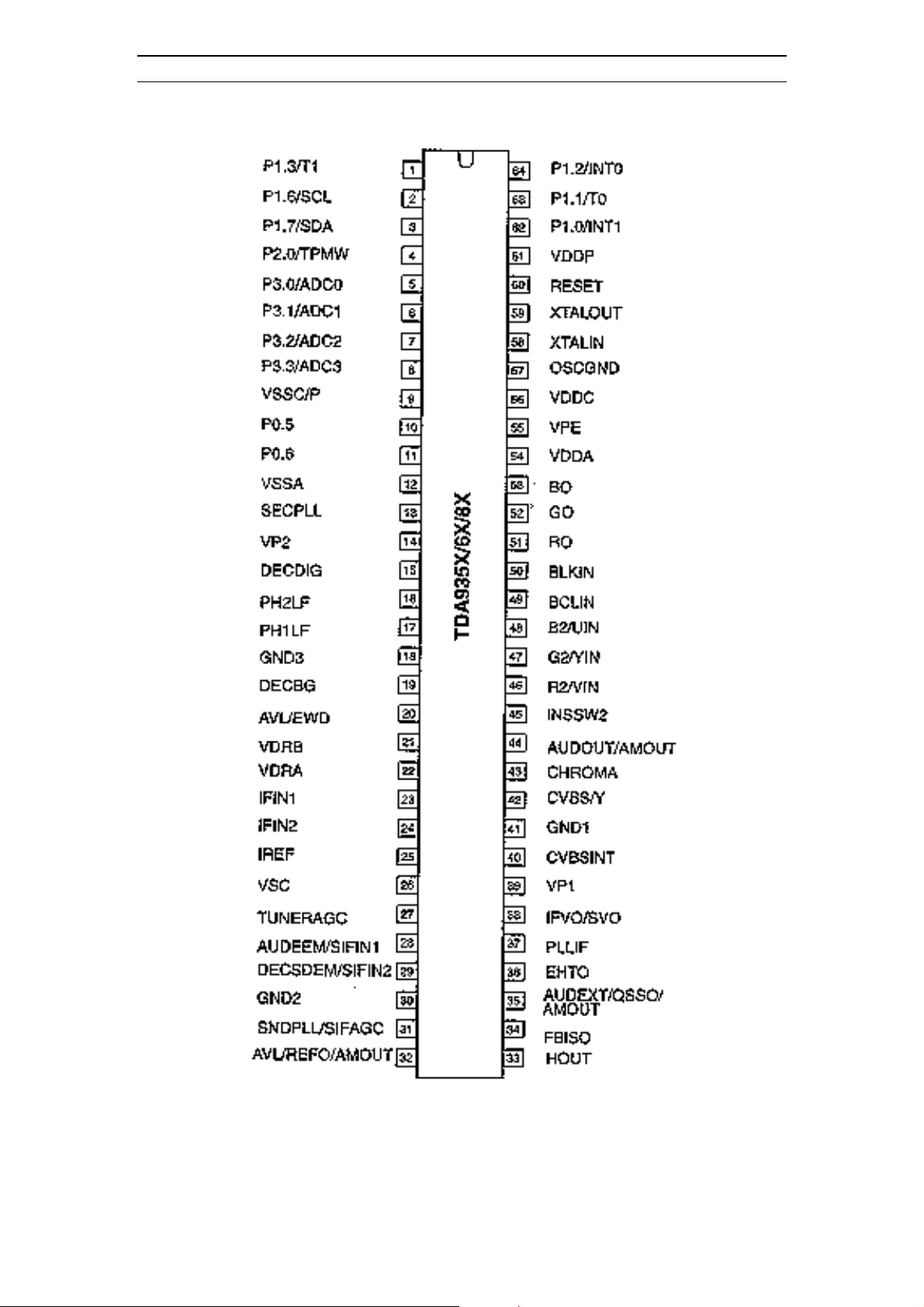

4-1 TDA936x TV signal processor - Teletext decoder with embedded m-Controller.

TV-signal Processor

l Multistandard vision IF circuit with alignment-free PLL demodulator

l Internal (switchable) time-constant for the IF-AGC circuit

l Source selection between 'Internal' CVBS and external CVBS or Y/C signals

l Integrated chrominance trap circuit

l Integrated luminance delay line with adjustable delay time

l Asymmetrical ‘delay line type’ peaking in the luminance channel

l Black stretching for non-standard luminance signals

l Integrated chroma band-pass filter with switchable centre frequency

l Only one reference (12 MHz) crystal required for the m-Controller, Teletext and the colour

decoder

l PAL / NTSC or multistandard colour decoder with automatic search system

l Internal base-band delay line

l RGB control circuit with 'Continuous Cathode Calibration', white point and black level off

set adjustment so that the colour temperature of the dark and the bright parts of the screen

can be chosen independently.

l Linear RGB or YUV input with fast blanking for external RGB/YUV sources. The

Text/OSD signals are internally supplied from the m-Controller/Teletext decoder

l Contrast reduction possibility during mixed-mode of OSD and Text signals

l Horizontal synchronisation with two control loops and alignment-free horizontal oscillator

l Vertical count-down circuit

l Vertical driver optimised for DC-coupled vertical output stages

l Horizontal and vertical geometry processing

l Horizontal and vertical zoom function for 16 : 9 applications

l Horizontal parallelogram and bow correction for large screen picture tubes

µµ-Controller

l 80C51 m-controller core standard instruction set and timing

l 1ms machine cycle

l 32 - 128Kx8-bit late programmed ROM

l 3 - 12Kx8-bit Auxiliary RAM (shared with Display and Acquisition)

l Interrupt controller for individual enable/disable with two level priority

l Two 16-bit Timer/Counter registers

l WatchDog timer

l Auxiliary RAM page pointer

l 16-bit Data pointer

l IDLE and Power Down (PD) mode

l 14 bits PWM for Voltage Synthesis Tuning

l 8-bit A/D converter

l 4 pins which can be programmed as general I/0 pin, ADC input or PWM (6-bit) output

Data Capture

l Text memory 10 pages

l Inventory of transmitted Teletext pages stored in the Transmitted Page Table (TPT) and

Subtitle Page Table (SPT)

- 13 -

Page 15

Service manual CL2554AN / CL2854AN

l Data Capture for US Closed Caption

l Data Capture for 525/625 line WST, VPS (PDC system A) and Wide Screen Signalling

(WSS) bit decoding Automatic selection between 525 WST/625 WST

l Automatic selection between 625 WST/VPS on line 16 of VBI

l Real-time capture and decoding for WST Teletext in Hardware, to enable optimised m-

processor throughput

l Automatic detection of FASTEXT transmission

l Real-time packet 26 engine in Hardware for processing accented, G2 and G3 characters

l Signal quality detector for video and WST/VPS data types

l Comprehensive teletext language coverage

l Full Field and Vertical Blanking Interval (VBI) data capture of WST data

Display

l Teletext and Enhanced OSD modes

l Features of lever 1.5 WST and US Close Caption

l Serial and Parallel Display Attributes

l Single/Double/Quadruple Width and Height for characters

l Scrolling of display region

l Variable flash rate controlled by software

l Enhanced display features including overlining, underlining and italics

l Soft colours using CLUT with 4096 colour palette

l Globally selectable scan lines per row (9/10/13/16) and character matrix [12x10, 12xl3,

12x16 (VxH)]

l Fringing (Shadow) selectable from N-S-E-W direction

l Fringe colour selectable

l Meshing of defined area

l Contrast reduction of defined area

l Cursor

l Special Graphics Characters with two planes, allowing four colours per character

l 32 software re-definable On-Screen display characters

l 4 WST Character sets (GO/G2) in single device (e.g. Latin, Cyrillic, Greek, Arabic)

l G1 Mosaic graphics, Limited G3 Line drawing characters

l WST Character sets and Closed Caption Character set in single device

Data Capture

The Data Capture section takes in the analogue Composite Vidéo and Blanking Signal

(CVBS), and from this extracts the required data, which is then decoded and stored in memory.

The extraction of the data is performed in the digital domain. The first stage is to convert the

analogue CVBS signal into a digital form. This is done using an ADC sampling at 12MHz.

The data and clock recovery is then performed by a Multi-Rate Video Input Processor

(MuIVIP). From the recovered data and clock the following data types are extracted WST

Teletext (625/525), Closed Caption, VPS, WSS. The extracted data is stored in either memory

(DRAM) via the Memory Interface or in SFR locations.

Data Capture Features

- Video Signal Quality detector

- 14 -

Page 16

Service manual CL2554AN / CL2854AN

- Data Capture for 625 line WST

- Data Capture for 525 line WST

- Data Capture for US Closed Caption

- Data Capture for VPS data (PDC system A)

- Data Capture for Wide Screen Signalling (WSS) bit decoding

- Automatic selection between 525 WST/625WST

- Automatic selection between 625WST/VPS on line 16 of VBI

- Real-time capture and decoding for WST Teletext in Hardware, to enable optimised

microprocessor throughput

- 10 pages stored On-Chip

- Inventory of transmitted Teletext pages stored in the Transmitted Page Table (TPT) and

Subtitle Page Table (SPT)

- Automatic detection of FASTEXT transmission

- Real-time packet 26 engine in Hardware for processing accented, G2 and G3 characters

- Signal quality detector for WST/VPS data types

- Comprehensive Teletext language coverage

- Full Field and Vertical Blanking Interval (VBI) data capture of WST data

- 15 -

Page 17

Service manual CL2554AN / CL2854AN

- 16 -

Page 18

Service manual CL2554AN / CL2854AN

TV processor version and µµ-Controller capacity

IC version TDA9365 Nx / 3 TDA9367 Nx / 3

TV range 110° 90°

QSS sound IF amplifier with

separated input and AGC circuit

PAL decoder

SECAM decoder

NTSC decoder

Horizontal geometry (E-W)

Horizontal and vertical zoom

ROM size 64 k 64 k

RAM size 2 k 2 k

Teletext 10 pages 10 pages

IC marking and version

üü üü

üü üü

üü üü

üü üü

üü

üü

IC marking

( line 3 )

DW9365/N1/3-BE x

( note : x is the

software version )

DW9365/N1/3-BDx

( note : x is the

software version )

PINNING

OSD languages ATSS country Text

English, French,

German, Italian,

Spanish, Dutch,

Danish, Finnish,

Norwegian, Swedish

GB, France,

Germany,

Belgium, Spain,

Italy,

Switzerland,

Pan-European

( West )

Austria,

Denmark,

Finland,

Netherlands,

Norway,

Sweden, Ireland,

Others

English, Polish,

Russian, Hungarian,

Czech, Slovakian,

Poland,

Hungary, Czech

rep., Others

Pan-European,

East, Cyrillic,

Greek.

Romanian, Greek

SYMBOL PIN DESCRIPTION

n.u. 1 Port 1.3 Not used.

SCL 2 I2C bus clock line

SDA 3 I2C Data line

SECAM L’ out 4 Port 2.0 : High when L’ selected (PushPull )

OCP 5 Port 3.0 : Over Current Protection

RF AGC in 6 ADC 1 : For factory use only ( High impedance )

Key-in 7 ADC 2 : local key input ( High impedance )

S/SW 8 ADC 3 : Scart Slow switching input ( See XXX)

VssC/P 9

digital ground for m-controller core and peripheral

LED 1 10 port 0.5 ( 8mA current sinking capability )

- 17 -

Page 19

Service manual CL2554AN / CL2854AN

LED 2 11 port 0.6 ( 8mA current sinking capability )

VSSA 12 analogue ground of teletext decoder and digital ground of TV

processor

SEC PLL 13 SECAM PLL decoupling

VP2 14 2nd supply voltage TV-processor

DECDIG 15 decoupling digital supply of TV-processor

PH2LF 16 phase-2 filter

PH1LF 17 phase-1 filter

GND3 18 ground 3 for TV-processor

DECBG 19 bandgap decoupling

AVL/EWD 20 East / West drive output

VDRB 21 vertical drive B output

VDRA 22 vertical drive A output

IFIN1 23 IF input 1

IFIN2 24 IF input 2

IREF 25 reference current input

VSC 26 vertical sawtooth capacitor

TUNERAGC 27 tuner AGC output

SIFIN1 28 SIF input 1

SIFIN2 29 SIF input 2

GND2 30 ground 2 for TV processor

SIF AGC 31 AGC sound IF

REF0 32 n.u.

HOUT 33 horizontal output

FBISO 34 flyback input / sandcastle output

QSS out 35 QSS intercarrier output

EHT0 36 EHT/Overvoltage protection

PLLIF 37 IF PLL loop filter

IFVO 38 IF video output

VP1 39 main supply voltage TV-processor

CVBSINT 40 internal CVBS input

GND1 41 ground 1 for TV-processor

CVBS/Y 42 external CVBS/Y input

CHROMA 43 chrominance input (SVHS)

AMOUT 44 n.u.

INSSW2 45 2nd RGB insertion input

R2IN 46 2nd R input

G2IN 47 2nd G input

B2IN 48 2nd B input

BCLIN 49 beam current limiter input

BLKIN 50 black current input

R0 51 RED Output

G0 52 GREEN Output

B0 53 BLUE Output

VDDA 54 analogue supply of Teletext decoder and digital supply of TV-

Processor (3.3V)

VPE 55 OTP programming supply

VDDC 56 digital supply to core (3.3V)

OSCGND 57 oscillator ground supply

XTALIN 58 crystal oscillator input

- 18 -

Page 20

Service manual CL2554AN / CL2854AN

XTALOUT 59 crystal oscillator output

RESET 60 reset

VDDP 61 digital supply to periphery (3.3V)

Audio Mute 62 Port 1.0 : Audio mute output (PushPull )

Power 63 Port 1.1 : Power output (PushPull )

IR in 64 Interrupt input 0 : R/C Infrared input

- 19 -

Page 21

Service manual CL2554AN / CL2854AN

- 20 -

Page 22

Service manual CL2554AN / CL2854AN

4-2 MSP3415D Multistandard Sound Processor

The MSP 3415D is designed as a single-chip Multistandard Sound Processor for applications

in analogue and digital TV sets, video recorders, and PC cards.

MSP 3415D features

- sound IF input

- No external filters required

- Stereo baseband input via integrated AD converters

- Two pairs of DA converters

- Two carrier FM or NICAM processing

- AVC : Automatic Volume Correction

- Bass, treble, volume processing

- Full SCART in/out matrix without restrictions

- Improved FM-identification

- Demodulator short programming

- Auto-detection for terrestrial TV - sound standards

- Precise bit-error rate indication

- Automatic switching from NICAM to FM/AM or vice versa

- Improved NICAM synchronisation algorithm

- Improved carrier mute algorithm

- Improved AM-demodulation

- Reduction of necessary controlling

- Less external components

Basic Features of the MSP 3415D

Demodulator and NICAM Decoder Section

The MSP 3415D is designed to simultaneously perform digital demodulation and decoding of

NICAM-coded TV stereo sound, as well as demodulation of FM or AM mono TV sound.

Alternatively, two carrier FM systems according to the German terrestrial specs can be

processed with the MSP 3415D.

The MSP 3415D facilitates profitable multistandard capability, offering the following

advantages:

- Automatic Gain Control (AGC) for analogue input: input range: 0.10 - 3 Vpp

- integrated A/D converter for sound-IF input

- all demodulation and filtering is performed on chip and is individually programmable

- easy realisation of all digital NICAM standards (B/G, I, L and D/K)

- FM-demodulation of all terrestrial standards (include identification decoding)

- no external filter hardware is required

- only one crystal clock (18.432 MHz) is necessary

- high deviation FM-mono mode (max. deviation: approx. ±360 kHz)

DSP-Section (Audio Baseband Processing)

- flexible selection of audio sources to be processed

- performance of terrestrial de-emphasise systems (FM, NICAM)

- digitally performed FM-identification decoding and de-matrixing

- digital baseband processing: volume, bass, treble

- 21 -

Page 23

Service manual CL2554AN / CL2854AN

- simple controlling of volume, bass, treble

Analogue Section

- two selectable analogue pairs of audio baseband input (= two SCART inputs) input level: <2

V RMS,

input impedance: >25 kW

- one selectable analogue mono input (i.e. AM sound): Not used in this chassis

- two high-quality A/D converters, S/N-Ratio: >85 dB

- 20 Hz to 20 kHz bandwidth for SCART-to-SCART copy facilities

- loudspeaker: one pair of four-fold oversampled D/A converters

output level per channel: max. 1.4 VRMS output resistance: max. 5 kW

S/N-ratio: >85 dB at maximum volume max. noise voltage in mute mode: < 10 mV (BW: 20

Hz... 16 kHz)

- one pair of four-fold oversampled D/A converters supplying a pair of SCART-outputs.

output level per channel: max. 2 V RMS, output resistance: max. 0.5 kW,

S/N-Ratio: >85 dB (20 Hz... 16 kHz)

Application Fields of the MSP 3415D

In the following sections, a brief overview about the two main TV sound standards, NICAM

728 and German FM Stereo, demonstrates the complex requirements of a multistandard audio

IC.

NICAM plus FM/AM-Mono

According to the British, Scandinavian, Spanish, and French TV-standards, high-quality stereo

sound is transmitted digitally. The systems allow two high-quality digital sound channels to be

added to the already existing FM/AM-channel. The sound coding follows the format of the socalled Near Instantaneous Companding System (NICAM 728). Transmission is performed

using Differential Quadrature Phase Shift Keying (DQPSK. Table below offers an overview of

the modulation parameters.

In the case of NICAM/FM (AM) mode, there are three different audio channels available:

NICAM A, NICAM B, and FM/AM-mono. NICAM A and B may belong either to a stereo or

to a dual language transmission. Information about operation mode and about the quality of the

NICAM signal can be read by the controlling software via the control bus. In the case of low

quality (high bit error rate), the controlling software may decide to switch to the analogue

FM/AM-mono sound. Alternatively, an automatic NICAM-FM/AM switching may be applied.

German 2-Carrier System (DUAL FM System)

Since September 1981, stereo and dual sound programs have been transmitted in Germany

using the 2-carrier system. Sound transmission consists of the already existing first sound

carrier and a second sound carrier additionally containing an identification signal. More details

of this standard are given in Tables below. For D/K very similar system is used.

TV standards

TV

system

Position of sound

carrier (MHz)

Sound modulation Colour system Country

B/G 5.5 / 5.7421875 FM Stereo PAL Germany

- 22 -

Page 24

Service manual CL2554AN / CL2854AN

B/G 5.5 / 5.85 FM-Mono / NICAM PAL Scandinavia,

Spain

L 6.5 / 5.85 AM - Mono / NICAM SECAM-L France

I 6.0 / 6.552 FM-Mono / NICAM PAL UK

D/K 6.5 / 6.2578125

D/K1

6.5 / 6.7421875

D/K2

6.5 / 5.85 D/KNICAM

FM Stereo

FM-Mono / NICAM

SECAM-East USSR

Hungary

Architecture of MSP3415D

Pin connections and short description

Pin No. Pin Name Type Short description

1 TP Out Test pin

2 NC Not Connected

3 NC Not Connected

4 TP Out Test pin

5 TP Out Test pin

6 ADR_SEL In I2C bus Address select

7 STANDBYQ In Standby ( Low-active)

8 NC Not Connected

9 I2C_CL In / Out I2C Clock

10 I2C_DA In / Out I2C data

11 TP In / Out Test pin

12 TP In / Out Test pin

13 TP Out Test pin

14 NC Not Connected

- 23 -

Page 25

Service manual CL2554AN / CL2854AN

15 TP Out Test pin

16 TP Out Test pin

17 TP Out Test pin

18 DVSUP Digital power supply +5V

19 DVSS Digital Ground

20 NC Not Connected

21 NC Not Connected

22 NC Not Connected

23 NC Not Connected

24 RESETQ In Power-On-reset

25 NC Not Connected

26 NC Not Connected

27 VREF2 Reference ground 2 high voltage part

28 DACM_R Out Loudspeaker out Right

29 DACM_L Out Loudspeaker out Left

30 NC Not Connected

31 TP Out Test pin

32 NC Not Connected

33 NC Not Connected

34 NC Not Connected

35 VREF1 Reference ground 1 high voltage part

36 SC1_OUT_R Out Scart output 1, right

37 SC1_OUT_L Out Scart output 1, left

38 NC Not Connected

39 AHVSUP Analogue power supply 8.0V

40 CAPL_M Volume capacitor MAIN

41 AHVSS Analogue ground

42 AGNDC Analogue reference voltage high voltage part

43 NC Not Connected

44 NC Not Connected

45 NC Not Connected

46 NC Not Connected

47 NC Not Connected

48 ASG2 Analogue Shield Ground 2

49 SC2_IN_L In Scart input 2 in, left

50 SC2_IN_R In Scart input 2 in, right

51 ASG1 Analogue Shield Ground 1

52 SC1_IN_L In Scart input 1 in, left

53 SC1_IN_R In Scart input 1 in, right

54 VREFTOP Reference voltage IF A/D converter

55 MONO_IN In Mono input

56 AVSS Analogue ground

57 AVSUP Analogue power supply

58 ANA_IN1+ In IF input 1

59 ANA_IN1- In IF common

60 NC Not Connected

61 TESTEN In Test pin

62 XTAL_IN In Crystal oscillator

63 XTAL_OUT Out Crystal oscillator

- 24 -

Page 26

Service manual CL2554AN / CL2854AN

64 NC Test pin

4-3 TDA894xJ Stereo Audio Amplifier

The TDA 8944J ( TDA 8946J ) is a dual-channel audio power amplifier with an output power

of 2 x 7 W ( 2 x 15 W ) at an 8 W load and a 12 V supply. The circuit contains two Bridges

Tied Load (BTL) amplifiers with an all-NPN output stage and standby/mute logic. The

TDA8944J comes in a 17-pin DIL power package.

Features

Few external components

Fixed gain

Standby and mute mode

No on/off switching plops

low standby current

High supply voltage ripple rejection

Outputs short-circuit protected to ground, supply and across the load

Thermally protected

Pin description

Pin Symbol Description

1 OUT1- negative loudspeaker terminal 1

2 GND1 ground channel 1

3 Vcc1 supply voltage channel 1

4 OUT1+ positive loudspeaker terminal

5 n.c. not connected

6 IN1+ positive input1

7 n.c. not connected

8 IN1- negative input1

9 IN2- negative input2

10 MODE mode selection input

11 SVR half supply voltage decoupling

12 IN2+ positive input2

1

(ripple rejection)

- 25 -

Page 27

Service manual CL2554AN / CL2854AN

Block diagram TDA8944J

4-4 TDA835xJ Vertical Amplifier

The TDA835xJ are power circuit for use in 90° and 110° colour deflection systems for field

frequencies of 25 to 200Hz and 16/9 picture tubes. The circuit provides a DC driven vertical

deflection output circuit, operating as a highly efficient class G system. Due to the full bridge

output circuit the deflection coils can be DC coupled.

The IC is constructed in a Low Voltage DMOS process that combines Bipolar, CMOS and

DMOS devices. MOS transistors are used in the output stage because of the absence of second

breakdown.

4-4-1 TDA8357J

Features :

- Few external components

- Highly efficient fully DC-coupled vertical output bridge circuit

- Short rise and fall time of the vertical flyback switch

- Guard circuit

- Temperature (thermal) protection

- High EMC because of common mode inputs

- 26 -

Page 28

Pinning

Pin Symbol Description

1 Vi(pos) input voltage (positive)

2 Vi(neg) input voltage (negative)

3 Vp supply voltage

4 V

OB

output voltage B

5 GND ground

6 Vflb flyback supply voltage

7 V

8 V

O(guard)

9 V

OA

output voltage A

guard output voltage

input measuring resistor

M

Service manual CL2554AN / CL2854AN

4-4-1 TDA8358J

An East-West output stage is provided that

is able to sink current from the diode

modulator circuit.

- 27 -

Page 29

Features :

- Few external components

- Highly efficient fully DC-coupled vertical

output bridge circuit

- Short rise and fall time of the vertical

flyback switch

- Guard circuit

- Temperature (thermal) protection

- High EMC because of common mode

inputs

- East-West output stage

Service manual CL2554AN / CL2854AN

4-5 TDA6107Q

The TDA6107Q includes three video output amplifiers in one plastic DIL-Bent-SIL 9-pin

medium power package, using high voltage DMOS technology, and is intended to drive the

three cathodes of a colour CRT directly. To obtain maximum performance, the amplifier

should be used with black-current control.

- 28 -

Page 30

Service manual CL2554AN / CL2854AN

Features

- Typical bandwidth of 5.5 MHz for an output signal of 60 Vpp

- High slew rate of 900V/ms

- No external components required

- Very simple application

- Single supply voltage of 200V

- Internal reference voltage of 2.5 V

- Fixed gain of 50.

- Black-current stabilisation (BCS) circuit

- Thermal protection

Pin description

Pin Symbol Description

1 V

2 V

3 V

i(1)

i(2)

i(3)

4 GND ground (fin)

5 I

6 V

7 V

8 V

9 V

om

DD

OC(3)

OC(2)

OC(1)

inverting input 1

inverting input 2

inverting input 3

black current measurement

output

supply voltage

cathode output 3

cathode output 2

cathode output 1

- 29 -

Page 31

Service manual CL2554AN / CL2854AN

Block diagram TDA6107Q

4-6 24C08 8 Kbit EEPROM

features :

- 8 Kbit serial I2C bus EEPROM

- Single supply voltage : 4.5 V to 5.5 V

- 1 Million Erase/Write cycles (minimum)

- 40 year data retention (minimum)

Pin description

Pin No. Name Description

1, 2, 3 E0, E1, E2 Device address

5 SDA Serial Data/Address Input/Output

6 SCL Serial clock

7 WC Write control

8 Vcc Supply voltage

4 Vss Ground

The memory device is compatible with the I2C memory standard. This is a two wire serial interface that

uses a bi-directional data bus and serial clock. The memory carries a built-in 4-bit unique device type

identifier code (1010) in accordance with the I2C bus definition.

Serial Clock (SCL)

The SCL input is used to strobe all data in and out of the memory.

Serial Data (SDA)

The SDA pin is bi-directional, and is used to transfer data in or out of the memory

- 30 -

Page 32

Service manual CL2554AN / CL2854AN

4-7 STR - F6653

4-7-1 General description

The STR-F6653 is an hybrid IC with a build-in MOSFET and control IC, designed for flyback

converter type switch mode power supply applications.

4-7-2 Features

- Small SIP fully isolated molded 5 pins package

- Many protection functions :

* Pulse-by-pulse overcurrent protection (OCP)

* Overvoltage protection with latch mode (OVP)

* Thermal protection with latch mode (TSD)

4-7-3 Block diagram

- 31 -

Page 33

Service manual CL2554AN / CL2854AN

4-7-4 Pins description

pin name symbol description

1 Overcurrent / feedback O.C.P./ F.B. Input of overcurrent detection signal and

feedback signal

2 Source S MOSFET source

3 Drain D MOSFET drain

4 Supply V

IN

5 Ground GND Ground

4-7-5 Control part electrical characteristics

description IC pins symbol rating unit

number min. typ. max.

Operation start voltage 4-5 VIN (on) 14.4 16 17.6 V

Operation stop voltage 4-5 VIN (off) 9 10 11 V

Circuit current in operation 4-5 IIN (on) - - 30 mA

Circuit current in non-operation 4-5 IIN (off) - - 100

Maximum OFF time -

Minimum time for input of quaxi

1-5 TTH (2) - - 1.0

resonant signals

Minimum off time - T

O.C.P./F.B. terminal threshold

1-5 VTH (1) 0.68 0.73 0.78 V

voltage 1

O.C.P./F.B. terminal threshold

1-5 VTH (2) 1.3 1.45 1.6 V

voltage 2

O.C.P./F.B. terminal extraction

1-2 I

current

O.V.P. operation voltage 4-5 VIN (OVP) 20.5 22.5 24.5 V

Latch circuit sustaining voltage 4-5 IIN (H) - - 400

Latch circuit release voltage 4-5 VIN (La.off) 6.6 - 8.4 V

Thermal shutdown operating

- TJ (TSD) 140 - -

temperature

T

(max)

OFF

(min) - - 1.5

OFF

OCP/FB

Input of power supply for control circuit

45 - 55

1.2 1.35 1.5 mA

mA

msec

msec

msec

mA

0

C

4-7-6 MOSFET electrical characteristics

description IC pins symbol rating unit

number min. typ. max.

Drain-to-source breakdown voltage 3-2 V

Drain leakage current 3-2 I

DSS

DSS

On-resistance 3-2 RDS (on) - - 1.95

Switching time 3-2 tf - - 250 nsec

Thermal resistance -

q

CH -F

- 32 -

650 - - V

- - 300

- - 1.25

mA

0

C/W

W

Page 34

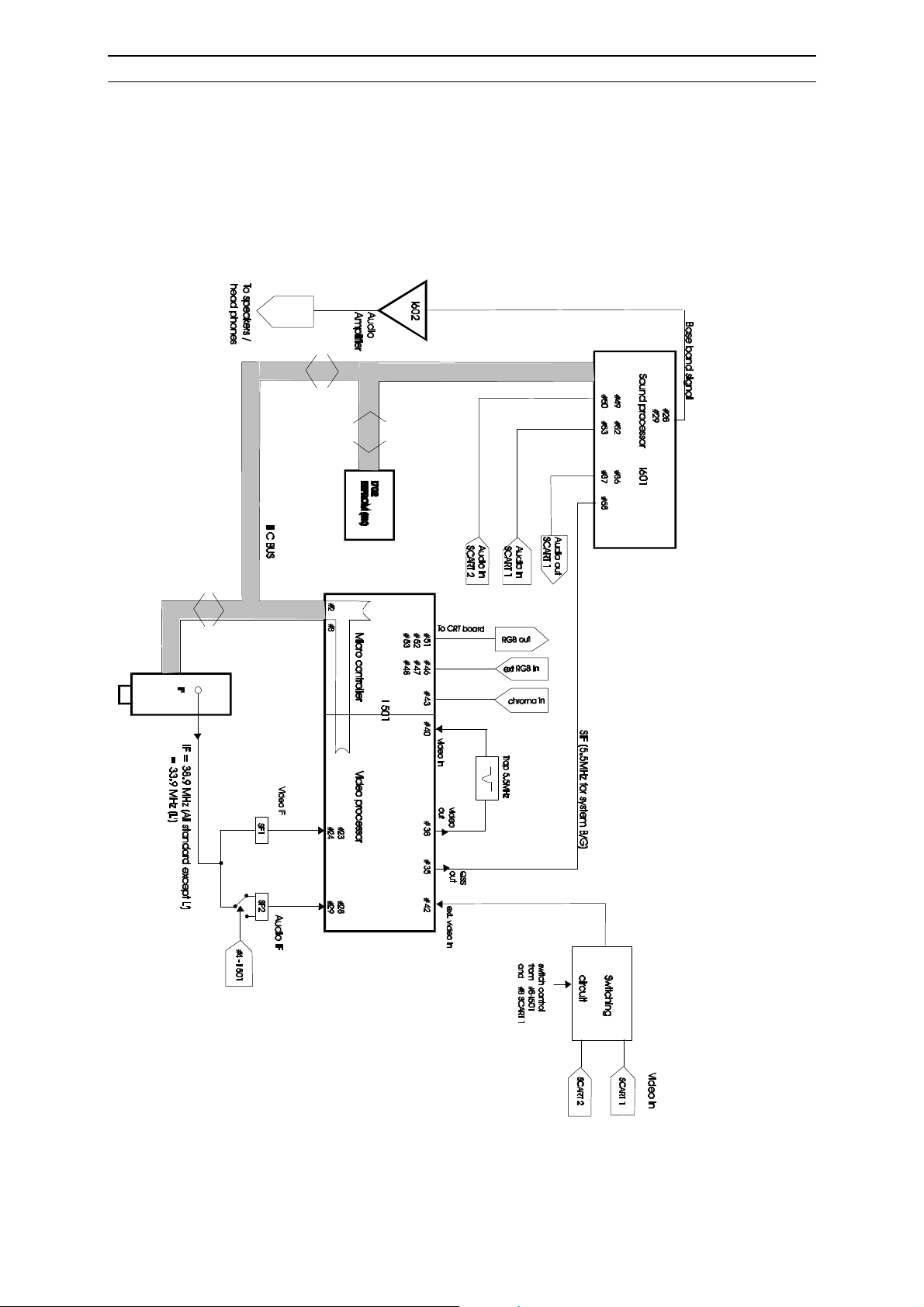

5 - Circuit description

5-1 Block diagram

Service manual CL2554AN / CL2854AN

- 33 -

Page 35

Service manual CL2554AN / CL2854AN

FUNCTIONAL DESCRIPTION OF VIDEO PROCESSOR Vision IF amplifier

The vision IF amplifier can demodulate signals with positive and negative modulation. The PLL

demodulator is completely alignment-free.

The VCO of the PLL circuit is internal and the frequency is fixed to the required value by using the

clock frequency of the m-Controller/Teletext decoder as a reference. The setting of the various

frequencies is made by the controlling software in subaddress 27H (38.9 MHz for all system except L’

or 33.9 MHz for system L’). Because of the internal VCO the IF circuit has a high immunity to EMC

interference's.

QSS Sound circuit

The sound IF amplifier is similar to the vision IF amplifier

and has an external AGC decoupling capacitor.

The single reference QSS mixer is realised by a multiplier. In this multiplier the SIF signal is converted

to the intercarrier frequency by mixing it with the regenerated picture carrier from the VCO. The mixer

output signal is supplied to the output via a high-pass filter for attenuation of the residual video signals.

With this system a high performance hi-fi stereo sound processing can be achieved.

Video switches

The video switch has one input for an external CVBS or Y/C signal. The selected CVBS signal can be

supplied to pin 38, the IF video output. The selection between both signals is realised by the controlling

software in subaddress 22H.

The video ident circuit is connected to the selected signal. This ident circuit is independent of the

synchronisation.

Synchronisation circuit

The IC contains separator circuits for the horizontal and vertical sync pulses and a data-slicing circuit

which extracts the digital teletext data from the analogue signal.

The horizontal drive signal is obtained from an internal VCO which is running at a frequency of 25

MHz. This oscillator is stabilised to this frequency by using a 12 MHz signal coming from the

reference oscillator of the m-Controller/Teletext decoder.

The horizontal drive is switched on and off via the soft start/stop procedure. This function is realised

by means of variation of the TON of the horizontal drive pulses.

The vertical synchronisation is realised by means of a divider circuit. The vertical ramp generator needs

an external resistor and capacitor. For the vertical drive a differential output current is available. The

outputs are DC coupled to the vertical output stage.

- 34 -

Page 36

Service manual CL2554AN / CL2854AN

In the type TDA9367, intended for 90° picture tubes the following geometry parameters can be

adjusted:

· Horizontal shift

· Vertical amplitude

· Vertical slope

· S-correction

· Vertical shift

The types which are intended to be used in combination with 110° picture tubes have an East-West

control circuit. The additional controls for these types are:

· EW width

· EW parabola width

· EW upper and lower corner parabola correction

· EW trapezium correction

· Vertical zoom, horizontal parallelogram and bow correction.

Chroma and luminance processing

The chroma band-pass and trap circuits (including the SECAM cloche filter) are realised by means of

gyrators and are tuned to the right frequency by comparing the tuning frequency with the reference

frequency of the colour decoder. The luminance delay line and the delay cells for the peaking circuit are

also realised with gyrators. The circuit contains a black stretcher function which corrects the black

level for incoming signals which have a difference between the black level and the blanking level.

Colour decoder

The ICs can decode PAL, NTSC and SECAM signals. The PAL/NTSC decoder does not need external

reference crystals but has an internal clock generator which is stabilised to the required frequency by

using the 12 MHz clock signal from the reference oscillator of the m-Controller/Teletext decoder.

The Automatic Colour Limiting (ACL) circuit (switchable via the ACL bit in subaddress 2OH)

prevents oversaturation occurring when signals with a high chroma-to-burst ratio are received. The

ACL circuit is designed such that it only reduces the chroma signal and not the burst signal. This has

the advantage that the colour sensitivity is not affected by this function.

SOFTWARE CONTROL

The CPU communicates with the peripheral functions using Special function Registers (SFRS) which

are addressed as RAM locations. The registers for the Teletext decoder appear as normal SFRs in the

m-Controller memory map and are written to these functions by using a serial bus. This bus is

controlled by dedicated hardware which uses a simple handshake system for software synchronisation.

For compatibility reasons and possible re-use of software blocks, the TV processor is controlled by I2C

bus. The TV processor control registers cannot be read. Only the status registers can be read ( Read

address 8A ).

The SECAM decoder contains an auto-calibrating PLL demodulator which has two references, via the

divided 12 MHz reference frequency (obtained from the m-Controller) which is used to tune the PLL to

- 35 -

Page 37

Service manual CL2554AN / CL2854AN

the desired free-running frequency and the bandgap reference to obtain the correct absolute value of the

output signal. The VCO of the PLL is calibrated during each vertical blanking period, when the IC is in

search or SECAM mode.

The base-band delay line (TDA 4665 function) is integrated. This delay line is also active during

NTSC to obtain a good suppression of cross colour effects. The demodulated colour difference signals

are internally supplied to the delay line.

RGB output circuit and black-current stabilisation

In the RGB control circuit the signal is controlled on contrast, brightness and saturation. The ICs have

a linear input for external RGB signals. The signals for OSD and text are internally supplied to the

control circuit. The output signal has an amplitude of about 2 Volts black-to-white at nominal input

signals and nominal settings of the various controls.

To obtain an accurate biasing of the picture tube the 'Continuous Cathode Calibration’ system has been

included in these ICs. A black level off set can be made with respect to the level which is generated by

the black current stabilisation system. In this way different colour temperatures can be obtained for the

bright and the dark part of the picture.

The black current stabilisation system checks the output level of the 3 channels and indicates whether

the black level of the highest output is in a certain window or below or above this window. This

indication is read from the status byte 01 and is used for automatic adjustment of the Vg2 voltage

during the production of the TV receiver.

During switch-off of the TV receiver a fixed beam current is generated by the black current control

circuit. This current ensures that the picture tube capacitance is discharged. During the switch-off

period the vertical deflection is placed in an overscan position so that the discharge is not visible on the

screen.

- 36 -

Page 38

Service manual CL2554AN / CL2854AN

5-2 IF

The TDA936x has an alignment free IF PLL demodulator. The fully integrated oscillator is

automatically calibrated, using the 12 MHz crystal as a frequency reference. The IF frequency is simply

set in TV-Processor by I2C bus.

The AFC information is available via I2C bus from the TV-Processor status bytes. The controlling

software uses this information for tuner frequency tracking ( automatic following ). The AFC windows

is typically 125Khz wide. The minimum frequency step of the tuner is 62.5 kHz.

This AFC function is disabled when a program is tuned using the direct frequency entry or after fine

tuning adjustment. Therefore it is recommended to tune channel with the TV search function ( manual

or ATSS ) or using the direct channel entry to enable the Automatic Frequency Control.

SAW filters

Ref. Standard Features

K3953M B/G - D/K - I - L/L’ - IF filter for video application

- TV IF filter with Nyquist slopes at 33.9 MHz and

38.9 MHz

- Constant group delay

K9650M B/G - D/K - I - L/L’ - IF filter for audio application

- TV IF audio filter with two channels

- Channel 1 (L’) with one pass band for sound

carrier at 40.40 MHz

- Channel 2 ( L, D/K, I, B/G) with one pass band for

sound carriers between 32.40 MHz and 33.40 MHz

For SECAM L and L’ the TDA936x is switched to positive modulation via I2C bus. SECAM L’ only

occur in VHF band I and have their picture and sound carrier interchanged, compared to SECAM L and

PAL B/G channels. For SECAM L’ the picture carrier is situated at 33.9 MHz and the AM sound

carrier at 40.40 MHz. The IF PLL reference is tuned from 38.9 to 33.9 MHz, this is done via I2C Bus

and the SIF filter is switched from channel 2 to channel 1 ; this is done by pin 4 of TDA 936x. The

tuner AGC time constant is slower than for negative modulation, because the TDA936x reduces its

AGC current. To even slower the AGC time constant an extra series resistor R103 is added. To prevent

IF overload when jumping from a very strong transmitter to a weak transmitter a diode D101 has been

added

The SAW filter ( SF1 ) has a double Nyquist slope at 38.9 MHz and 33.9 MHz needed for this

multistandard application. The disadvantage of this choice is that a 5.5 MHz trap filter ( Z501 ) is

needed to suppress the residual sound carrier in the video for B/G signals.

- 37 -

Page 39

Service manual CL2554AN / CL2854AN

Chassis block diagram : IF

- 38 -

Page 40

Service manual CL2554AN / CL2854AN

5-3 Source switching

The TDA936x has only one external video input, the external video switching circuit made with Q504,

Q505, Q507, Q508 and Q509 allows 2 external video signal inputs. The switching command can be

either the SCART1 slow switching pin 8 or the m-Controller pin 8 when the software takes control of

the video source. The m-Controller pin 8 is automatically configured by the controlling software ( See

table below ). This pin is also capable of detecting the 3 Status ( 0, 1A, 1B ) described in SCART

specifications for automatic format switching.

TV mode

µµ-Controller pin 8 Status

Level

RF auto Input - High Impedance < 1V

RF Forced Input - High Impedance not defined

AV 1 Auto 4:3 Input - High Impedance > 2.7 V

AV 1 Auto 16:9 Input - High Impedance 1 V < x < 2.7 V

AV 1 forced Output - Push Pull Max. 3.3V

AV 2 Output - Push Pull < 0.2 V

SVHS Output - Push Pull < 0.2 V

The controlling software via I2C bus selects the signal source :

- Video signal from tuner ( Pin 40 ).

- External video ( SCART 1 or 2 ) depending on Q508 base level.

- External SVHS from SCART 2.

The sound source switching is done in the MSP3415D ( I601 ), by the m-Controller via I2C bus.

Fast R, G, B insertion : The external R, G, B insertion needs a fast switching and cannot be controlled

by the software ( instruction cycle of 1m sec ). The fast switching pin 16 of SCART 1 is directly

connected to the TV processor pin 45 ( Fast blanking input ). The display is synchronised with the

selected video source, i.e. to get stable R, G, B inserted signal they must be synchronised with the

selected video source. The controlling software only enable or disable ( AV2, SVHS, or Forced RF

source selected ) fast blanking.

5-4 m-Controller I/O pin configuration and function

The I/O pins of the m-Controller can be configured in many way. All port functions can be individually

programmed by use of the SFR registers.

Each I/O port pin can be individually programmed in these configurations :

Open drain

In this mode, the port can function as in and output. It requires an external pull-up resistor. The

maximum allowable supply voltage for this pull up resistor is +5V.

So in this mode it is possible to interface a 5 Volt environment like I2C while the m-Controller has a 3.3

Volt supply.

Push-Pull

The push pull mode can be used for output only. Both sinking and sourcing is active, which leads to

sleep slopes. The levels are 0 and Vddp, the supply voltage 3.3Volts.

High impedance

- 39 -

Page 41

Service manual CL2554AN / CL2854AN

This mode can be used for input only operation of the port.

Special port for LED

Pin 10 and 11 have the same functionality as the general I/O pins but in addition, their current source

and sink capacity is 8 mA instead of 4 mA. These pins are used for driving LED’s via a series current

limiting resistor.

m-Controller I/O pin configuration and function table

pin name configuration description

Stand by TV ON

1 n.u. High impedance High impedance not used

2 SCL Open Drain Open Drain Serial clock line

3 SDA Open Drain Open Drain Serial data line

4 SECAM L’ High impedance Push Pull SIF filter switching

5 OCP High impedance High impedance Over Current Protection

( Switch the set OFF if

the voltage on this pin is

<2.7V )

6 - High impedance High impedance For factory use only

7 Key in High impedance High impedance Local keyboard input

8 S/SW High impedance See table above external video switch

10 Red LED High impedance Open Drain

11 Green LED Open Drain High impedance

62 Audio mute Push Pull Push Pull High in stand by mode

5-5 Sound processing

Analogue sound IF - input section

The input pins ANA_IN1+ and ANA_IN- offer the possibility to connect sound IF sources to the MSP

3415D. The analogue-to-digital conversion of the pre-selected sound IF signal is done by an A/D

converter, whose output is used to control an analogue automatic gain circuit (AGC), providing an

optimal level for a wide range of input levels.

Quadrature Mixers

The digital input coming from the integrated A/D converter may contain audio information at a

frequency range of theoretically 0 to 9 MHz corresponding to the selected standards. By means of two

programmable quadrature mixers, two different audio sources ; for example, NICAM and FM-mono,

may be shifted into baseband position.

Phase and AM discrimination

The filtered sound IF signals are demodulated by means of the phase and amplitude discriminator block.

On the output, the phase and amplitude is available for further processing. AM signals are derived from

the amplitude information, whereas the phase information serves for FM and NICAM demodulation.

NICAM decoder

In case of NICAM - mode, the phase samples are decoded according the DQPSK - coding scheme. The

output of this block contains the original NICAM bitstream.

- 40 -

Page 42

Service manual CL2554AN / CL2854AN

DSP section

All audio baseband functions are performed by digital signal processing (DSP). The DSP section

controls the source and output selection, and the signals processing.

Sound Mode switching

In case of NICAM transmission, the controlling software read the bit error rate and the operation mode

from the NICAM Decoder. When the set is in “Auto detection” mode ( default mode after ATSS ) the

controlling software set automatically the sound mode ( NICAM mono, NICAM Dual 1 or NICAM

Dual 2 ) depending on the transmitted mode.

In case of 2 Carrier FM transmission, the controlling software read the transmission mode and the

signal quality level from the Stereo Detection Register. When the set is in “Auto detection” mode the

controlling software set automatically the sound mode ( mono, Stereo, Dual 1, Dual 2 ) depending on

the transmitted mode.

In “Auto detection” mode the controlling software evaluate the signal quality and automatically switch

to the analogy sound carrier 1, if the transmission quality is too poor. To avoid unwanted automatic

switching the threshold levels mono to stereo and stereo to mono is different.

In “forced mono “ mode ( Red OSD in recall section ), the controlling software configure the

MSP3415D to demodulate only the analogue (FM or AM) sound carrier 1, no matter the signal quality.

The sound mode “ forced “ or “ Autodetect” is stored for each programme.

- 41 -

Page 43

Service manual CL2554AN / CL2854AN

Sound signal flow diagram

- 42 -

Page 44

Service manual CL2554AN / CL2854AN

5-6 Sound amplification

The TDA8944J (TDA8946J) is a stereo BTL audio amplifier capable of delivering 2 x 7 W (2 x 15 W)

output power to an 8 W load at THD = 10%, using a 12 V power supply and an external heatsink. The

voltage gain is fixed at 32dB.

With the three-level MODE input the device can be switched from ‘standby’ to ‘mute’ and to

‘operating’ mode.

The TDA 8944J outputs are protected by an internal thermal shutdown protection mechanism and

short-circuit protection.

Power amplifier

The power amplifier is a Bridge Tied Load (BTL) amplifier with an all-NPN output stage, capable of

delivering a peak output current of 1.5 A.

The BTL principle offers the following advantages :

- Lower peak value of the supply current.

- The ripple frequency on the supply voltage is twice the signal frequency.

- No DC-blocking capacitor

- Good low frequency performance

Mode selection

The TDA894xJ has several functional modes, which can be selected by applying the proper DC voltage

to pin MODE.

Mute : In this mode the amplifier is DC biased but not operational (no audio output). This allows the

input coupling capacitors to be charged to avoid pop-noise. The devices is in mute mode when 2.5 V <

V

< (Vcc-1.5 V).

MODE

Operating : In this mode the amplifier is operating normally. The operating mode is activated at V

MODE

< 0.5 V.

5-7 Vertical deflection

The vertical driver circuit is a bridge configuration. The deflection coil is connected between the output

amplifiers, which are driven in phase opposition. The differential input circuit is voltage driven. The

input circuit is especially intended for direct connection to driver circuits which deliver symmetrical

current signals, but is also suitable for asymmetrical currents. The output current of these devices is

converted to voltages at the input pins via resistors R350 and R351. The differential input voltage is

compared with the output current through the deflection coils measured as voltage across R302, which

provides internal feedback information. The voltage across R302 is proportional to the output current.

Flyback voltage

The flyback voltage is determined by an additional supply voltage V

. The principle of operation with

flb

two supply voltages (class G) makes it possible to fix the supply voltage Vp optimum for the scan

voltage and the second supply voltage V

high efficiency is achieved. The supply voltage V

optimum for the flyback voltage. Using this method, very

flb

is almost totally available as flyback voltage across

flb

the coil, this being possible due to the absence of a coupling capacitor.

Protection

The output circuit has protection circuits for :

- Too high die temperature

- Overvoltage of output stage A

Guard circuit

The guard signal is not used by the TDA936x to blank the screen in case of fault condition.

Damping resistor

For HF loop stability a damping resistor (R305) is connected across the deflection coil.

- 43 -

Page 45

Service manual CL2554AN / CL2854AN

EAST-WEST Amplifier (TDA8358J only)

The East-West amplifier is current driven. It can only sink currents of the diode modulator circuit. A

feedback resistor R397 is connected between the input and output of this inverting amplifier in order to

convert the East-West correction input into an output voltage.

- 44 -

Page 46

Service manual CL2554AN / CL2854AN

R819

D802

D804

R802

4

4

Ground

T801 SMPS TRANS

3

5

5-8 Power supply (STR-F6653)

5-8 -1 STR-F6653 general description

The STR-F6653 is an hybrid IC with a build-in MOSFET and control IC, designed for flyback

converter type switch mode power supply applications.

5-8 -2 Power supply primary part operations

An oscillator generates pulses signals which turn on and off a MOSFET transistor.

* Start -up circuit: V

IN

The start-up circuit is used to start and stop the operation of the control IC, by detecting a voltage

appearing at VIN pin (pin 4).

D801

C804

C803

D803

C805

2

L801

6

R805

D805

7

Main AC voltage

C806

Drain Vin

I801 STR-F6653

Power supply start-up circuit

- 45 -

Page 47

Service manual CL2554AN / CL2854AN

When the power switch is pushed on, VIN increases slowly. During this time, C806 is charged through

R802.

As soon as VIN reaches 16V, the STR-F6653 control circuit starts operating. Then, VIN is obtained by

smoothing the winding voltage which appears between pin6 and pin7 of the SMPS transformer.

As this winding voltage does not increase to the set voltage immediately after the control circuit starts

operating, VIN starts dropping. However, as this winding voltage reaches the set value before V

voltage drops to the shutdown voltage (at 11V), the control circuit continues operating (see below V

voltage at start-up). R805 resistor prevents that VIN pin voltage varies according to the secondary side

output current.

IN

IN

VIN must be set higher than the shutdown voltage (VIN (off) = 11V

(overvoltage protection) operating voltage

(V

= 20.5V

OVP

O.V.P.voltage 20.5V

Shutdown voltage 11V

)

min

Vin

16V (TYP.)

) and lower than the O.V.P.

max

Waveform of Vin pin voltage at start-up

- 46 -

t

Page 48

* STR-F6653 oscillating operation

Service manual CL2554AN / CL2854AN

STR-F6653

OSC

Comp.2

C1

R1

Comp.1

Vth(2)

Vth(1)

DRIVE

1.35mA

Rg2

Rg1

Oscillating operation

3

DRAIN

2

SOURCE

1

OCP/FB

5

GND

TO PIN4 SMPS

R808

From PIN 6

SMPS

(FEEDBACK)

C850

R804

C1

(STR-F6653

internal capacitor)

Pin 1

(OCP / FB)

I

D

(MOSFET drain current)

V

DS

(MOSFET drain - source voltage)

MOSFET switching ON/OFF

6.5V

3.7V

0.73V

0V

ON

1

3

2

ON ON

OFFOFF

4

OFF

Waveforms during oscillating operation

- 47 -

Page 49

Service manual CL2554AN / CL2854AN

¬ When the MOSFET is ON, the STR-F6653 internal capacitor C1 is charged at the constant voltage

6.5V.

At the same time, the voltage at pin 1 (OCP / FB) increases with the same waveform as the MOSFET

drain current.

- When the pin 1 voltage reaches the threshold voltage V

= 0.73V, the STR-F6653 internal

TH1

comparator 1 starts operating. The STR-F6653 internal oscillator is inverted and the MOSFET turns

OFF.

® When the MOSFET turns OFF, charging of STR-F6653 internal capacitor C1 is released and C1

starts discharging by the STR-F6653 internal resistance R1. So, C1 voltage starts falling in accordance

with the gradient regulated by the constant discharging time of C1 and R1. So, this means that the fixed

time determined by C1 and R1 is the OFF-time of the MOSFET.

¯ When C1 voltage falls to around 3.7V, the STR-F6653 internal oscillator is reversed again and the

MOSFET turns ON. C1 is quickly charged to around 6.5V

The MOSFET continues to oscillate by repeating the above procedure.

* STR-F6653 protection circuits

· overcurrent protection function (OCP)

Overcurrent protection is performed pulse by pulse detecting at STR-F6653 pin 1 (OCP) the peak of the

MOSFET drain current in every pulse.

· latch circuit

This circuit sustains an output low from the STR-F6653 internal oscillator and stops operation of the

power supply when overvoltage protection (OVP) and thermal shutdown (TSD) circuit are under

operation

· thermal shutdown circuit (TSD)

This circuit triggers the latch circuit when the frame temperature of STR-F6653 IC exceeds 140°C

· overvoltage protection circuit (OVP)

This circuit triggers the latch circuit when the V

voltage exceeds 22V (typ.)

in

- 48 -

Page 50

Service manual CL2554AN / CL2854AN

1

636054

L511

L512

Vddc

VddA

Reset N

Power

3

3

4

CONTROL IC

EEPROM

SW801

D801... D804

L801

8V

Vddp

5-9 TV start-up, TV normal run and stand-by mode operations

5-9-1 TV start-up operations

* Schematic diagram for start-up operations

I823 REG 3.3V

12

IN

GND

2 3

OUT

5661

L510

IN

RESET

PULSE

CIRCUIT

OUT

T801 SMPS TRANSFORMER

2

(GRAETZ BRIDGE)

D

I801 MOSFET AND

POWER SWITCH

MAIN AC VOLTAGE

I501

MICROCONTROLLER PART

SDA

SCL

2

56

I702

Start-up operations

* TV start-up and microcontroller initialization

- When SW801 power switch is pushed, main AC voltage is applied to T801 transformer (after

rectification by D801...D804 diodes). Then, T801 SMPS transformer starts operating and supplies

DC voltage to I823 (3.3V regulator).

- This regulator provides 3.3V DC voltage to I501 microcontroller power supply pins (pins 54, 56, 61)

and to the reset pulse circuit which provides reset pulse to I501 microcontroller reset pin (pin 60).

- Then, the microcontroller starts its initialization. Its power pin (pin 63) is set to high which allows

delivery of power supply voltages (123V, 8V, 5V...). At this step, all IC’s start working but no picture

appears on screen: I501 IC doesn’t provide horizontal drive voltage.

- Then, the microcontroller consults I702 EEPROM via I2C bus to know the last TV set mode (normal

run mode or stand-by mode ) before switching off.

- 49 -

Page 51

. If the TV set was on normal run mode before switching off, the microcontroller delivers

3.3V

3.0V

3.0V

1.2V

1.2V0VDC supply voltage

I823

pin 3

reset pulse

I501

pin 60

from I823

pin 3

R591

100WD591

DZ2.4

R593

10K

W

R592

10k

W

Q510

R594

10K

W

Q511

C501

50V

10mF

0

V

horizontal drive voltage at pin 33 and picture appears on screen.

. If the TV set was on stand-by mode before switching off, the microcontroller switches TV set

to stand-by mode, decreasing power pin voltage (pin 63). This matter will be explained on

paragraph 5-9-2-b.

* Reset pulse circuit

Service manual CL2554AN / CL2854AN

+

to I501

pin 60

Reset pulse circuit and corresponding waveforms

- 50 -

Page 52

Service manual CL2554AN / CL2854AN

I810

CONTROLLED

RECTIFIER

R820

R830

C830

R829

Q808

6V DC

11V DC

R870

D811

Q811

Q809

Q807

Q810

LOW

LOW

LOW

LOW

HIGH

HIGH

CONDUCTING

POWER

HIGH

NOT

CONDUCTING

* Reset pulse circuit operations description

- When DC supply voltage from I823 regulator starts rising (from 0V to 1.2V), no current flows

through D591 zener diode. So, Q510 is in off mode.

Also V

Then, no voltage reaches I501 pin 60.

- When this voltage reaches 1.2 V, Q510 stays in off mode

but V

- When the DC supply voltage reaches (2.4V +0.6V ) =3.0V, Q510 starts conducting but as the Q511

base-emitter voltage is the same as the collector-emitter voltage of the saturated Q510, Q511 switches

off and no voltage reaches I501 pin 60.

- If the DC supply voltage decreases below 3 V, Q510 switches off immediately. Q511 starts

conducting, pulling I501 pin 60 high.

At the same time, it discharges the reset capacitor C501. Discharging this capacitor is necessary to

garantee a defined reset pulse duration.

5-9-2 TV normal run and stand-by mode operations

=Vcc/2 -Vcc = -Vcc/2 > -0.6V. So, Q511 is in off mode.

be Q511

= -0.6V. So, Q511 is switched on and starts driving DC supply voltage to I501 pin 60.

be Q511

Depending on remote control commands, I501 microcontroller part pin 63 (power) is set to:

- high for normal run mode

- low for stand-by mode

a) TV on normal run mode

* I501 microcontroller part pin 63 (power) effect

I501 microcontroller part pin 63 (power) is connected to the following circuit:

I501 microcontroller part pin 63 (POWER) effect

On normal run mode, I501 microcontroller pin 63 (power) is set to high

- 51 -

Page 53

Service manual CL2554AN / CL2854AN

5V

3.3V

REGULATOR

14.5V (CP785)

5V

3

3

11V8V6V13

123V-113V (CP385)

D820

D860

D830

D831

C832

C823

C861

91213

1624

R810

3

IC ERROR AMPLIFIER

12.5V

123V / 113V

T801 SMPS TRANSFORMER

(GRAETZ BRIDGE)

D

I801

CONTROL IC

POWER

MAIN AC VOLTAGE

L801

I822

8

· So, I810 controlled rectifier is not conducting

- Q809 is conducting. So, Q808 is not conducting and Q807 is conducting

- So, Q807 collector is connected to the ground and I810 controlled rectifier gate pin is

set to low (no conducting)

· So, current from 11V DC voltage (from T801 SMPS transformer pin 13) does not flow through

Q811 and Q810 transistors but flows through I806 IC error amplifier

- Q809 is conducting. So, Q810 is not conducting and no current flows from Q810

collector to the ground

Therefore, the power supply circuit diagram is the one shown on the next paragraph

* power supply circuit diagram during TV set normal run

3.3V

12.5V (CP385)

D801... D804

14.5V

SW801

SWITCH

I820

REGULATOR

1 1

8.5V

8V

3

MOSFET AND

11.5V

11V

143V

C813

1

I806

2

I823

V

REGULATOR

R823

11V

143V (CP785)

Power supply operation during TV set normal run

- 52 -

Page 54

Service manual CL2554AN / CL2854AN

* power supply functioning during TV set normal run mode