SERVICE MANUAL

MANUEL D'ENTRETIEN

WARTUNGSHANDBUCH

CAUTION:

Before servicing this chassis, it is important that the service technician read the “Safety

Precautions” and “Product Safety Notices” in this service manual.

SM0065

42PMA225EZ

Data contained within this Service

manual is subject to alteration for

improvement.

ATTENTION:

Avant d’effectuer l’entretien du châassis, le technicien doit lire les «Précautions de sécurité»

et les «Notices de sécurité du produit» présentés dans le présent manuel.

VORSICHT:

Vor Öffnen des Gehäuses hat der Service-Ingenieur die „Sicherheitshinweise“ und „Hinweise

zur Produktsicherheit“ in diesem Wartungshandbuch zu lesen.

Les données fournies dans le présent

manuel d’entretien peuvent faire l’objet

de modifications en vue de perfectionner

le produit.

Die in diesem Wartungshandbuch

enthaltenen Spezifikationen können sich

zwecks Verbesserungen ändern.

SPECIFICATIONS AND PARTS ARE SUBJECT TO CHANGE FOR IMPROVEMENT

Colour Television

September 2004

TABLE OF CONTENTS

INTRODUCTION.......................................................................................................................................1

1.

2. MULTI STANDARD SOUND PROCESSOR ............................................................................................1

3. VIDEO SWITCH TEA6415........................................................................................................................1

4. AUDIO AMPLIFIER STAGE WITH TDA8928ST ......................................................................................1

5. POWER SUPPLY (SMPS)........................................................................................................................1

6. MICROCONTROLLER..............................................................................................................................2

7. SERIAL ACCESS CMOS 4K x 8 (32K bit) EEPROM 24C32A .................................................................2

8. CLASS AB STEREO HEADPHONE DRIVER TDA1308..........................................................................2

9. IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM........................................................................2

9.1. TEA6415C .............................................................................................................................................3

9.1.1. General Description .....................................................................................................................3

9.1.2. Features ........................................................................................................................................3

9.1.3. Pinning..........................................................................................................................................3

9.2. 24C32A..................................................................................................................................................3

9.2.1. Features ........................................................................................................................................3

9.2.2. Description....................................................................................................................................4

9.2.3. Pin Function table........................................................................................................................4

9.2.4. Functional Descriptions..............................................................................................................5

9.3. LM317....................................................................................................................................................5

9.3.1. General Description .....................................................................................................................5

9.3.2. Features ........................................................................................................................................5

9.4. ST24LC21 .............................................................................................................................................5

9.4.1. Description....................................................................................................................................5

9.4.2. Features ........................................................................................................................................5

9.4.3. Pin connections ...........................................................................................................................6

9.5. TLC7733................................................................................................................................................6

9.5.1. Description....................................................................................................................................6

9.6. 74LVC257A ...........................................................................................................................................7

9.6.1. Features ........................................................................................................................................7

9.6.2. Description....................................................................................................................................7

9.6.3. Pin Description.............................................................................................................................7

9.7. 74LVC14A .............................................................................................................................................7

9.7.1. Features ........................................................................................................................................7

9.7.2. Applications..................................................................................................................................7

9.7.3. Description....................................................................................................................................7

9.7.4. Pin Description.............................................................................................................................8

9.8. TEA6420................................................................................................................................................8

9.8.1. Features ........................................................................................................................................8

9.8.2. Description....................................................................................................................................8

9.9. LM1086..................................................................................................................................................8

9.9.1. Description....................................................................................................................................8

9.9.2. Features ........................................................................................................................................8

9.9.3. Applications..................................................................................................................................9

9.9.4. Connection Diagrams..................................................................................................................9

9.10. LM1117 ..............................................................................................................................................9

9.10.1. General Description .................................................................................................................9

9.10.2. Features.....................................................................................................................................9

9.10.3. Applications..............................................................................................................................9

9.10.4. Connection Diagrams ..............................................................................................................9

9.11. DS90C385 .......................................................................................................................................10

9.11.1. General Description ...............................................................................................................10

9.11.2. Features...................................................................................................................................10

9.11.3. Pin Description .......................................................................................................................10

9.12. MSP34X1G ......................................................................................................................................12

9.12.1. Introduction.............................................................................................................................12

9.12.2. Features...................................................................................................................................13

9.12.3. Pin connections......................................................................................................................13

i

Plasma TV Service Manual 11/01/2005

TDA1308..........................................................................................................................................15

9.13.

9.13.1. General Description ...............................................................................................................15

9.13.2. Features...................................................................................................................................15

9.13.3. Pinning.....................................................................................................................................16

9.14. PI5V330 ...........................................................................................................................................16

9.14.1. General Description ...............................................................................................................16

9.15. AD9883A..........................................................................................................................................16

9.15.1. General Description ...............................................................................................................16

9.15.2. Features...................................................................................................................................16

9.15.3. Pin Descriptions .....................................................................................................................17

9.16. SAA7118E .......................................................................................................................................19

9.16.1. General Description ...............................................................................................................19

9.16.2. Features...................................................................................................................................20

9.16.3. Pinning.....................................................................................................................................21

9.17. TPS72501 ........................................................................................................................................25

9.17.1. General Description ...............................................................................................................25

9.17.2. Features...................................................................................................................................25

9.18. TSOP1836 .......................................................................................................................................26

9.18.1. Description..............................................................................................................................26

9.18.2. Features...................................................................................................................................26

9.19. PCF8591..........................................................................................................................................26

9.19.1. General Description ...............................................................................................................26

9.19.2. Features...................................................................................................................................26

9.19.3. Pinning.....................................................................................................................................27

9.20. PW1231 ...........................................................................................................................................27

9.20.1. General Description ...............................................................................................................27

9.20.2. Features...................................................................................................................................27

9.20.3. Applications............................................................................................................................28

9.21. PW181 .............................................................................................................................................28

9.21.1. General Description ...............................................................................................................28

9.21.2. Features...................................................................................................................................28

9.21.3. Applications............................................................................................................................29

9.22. SIL151B ...........................................................................................................................................29

9.22.1. General Description ...............................................................................................................29

9.22.2. Features...................................................................................................................................29

9.23. SDRAM 4M x 16 (MT48LC4M16A2TG-75) .....................................................................................29

9.23.1. General Description ...............................................................................................................29

9.23.2. Features...................................................................................................................................30

9.23.3. Pin Descriptions .....................................................................................................................30

9.24. FLASH 8MBit ...................................................................................................................................32

9.24.1. Description..............................................................................................................................32

9.24.2. Features...................................................................................................................................32

10. SERVICE MENU SETTINGS..................................................................................................................33

10.1. display menu....................................................................................................................................33

10.2. calibration menu...............................................................................................................................35

deinterlacer menu...........................................................................................................................................36

10.3. Service menu factory reset values...................................................................................................38

11. BLOCK DIAGRAM ..................................................................................................................................39

12. CIRCUIT DIAGRAMS .............................................................................................................................47

ii

Plasma TV Service Manual 11/01/2005

1. INTRODUCTION

42” Plasma TV is a progressive TV control system with built-in de-interlacer and scaler. It uses a

852*480 panel with 16:9 aspect ratio. The TV is capable of operation in PAL, SECAM, NTSC (playback)

colour standards and multiple transmission standards as B/G, D/K, I/I’, and L/L´ including German and

NICAM stereo. Sound system output is supplying 2x10W (10%THD) for stereo 8! speakers. The

chassis is equipped with many inputs and outputs allowing it to be used as a center of a media system.

It supports following peripherals:

2 SCART’s with all of them supporting full SCART features including RGB input

1 AV inputs. (CVBS+ Stereo Audio)

1 SVHS input

1 Streeo Headphone output

1 D-Sub 15 PC input

1 DVI input

1 Stereo audio input for PC/DVI

Other features include, Picture-In-Picture (PIP) , Picture-And-Picture (PAP) .

2. MULTI STANDARD SOUND PROCESSOR

The MSP34x1G family of single-chip Multistandard Sound Processors covers the sound processing of

all analog TV-Standards worldwide, as well as the NICAM digital sound standards. The full TV sound

processing, starting with analog sound IF signal-in, down to processed analog AF-out, is performed on

a single chip.

These TV sound processing ICs include versions for processing the multichannel television sound

(MTS) signal conforming to the standard recommended by the Broadcast Television Systems

Committee (BTSC). The DBX noise reduction, or alternatively, Micronas Noise Reduction (MNR) is

performed alignment free. Other processed standards are the Japanese FM-FM multiplex standard

(EIA-J) and the FM Stereo Radio standard.

Current ICs have to perform adjustment procedures in order to achieve good stereo separation for

BTSC and EIA-J. The MSP34x1G has optimum stereo performance without any adjustments.

3. VIDEO SWITCH TEA6415

In case of three or more external sources are used, the video switch IC TEA6415 is used. The main

function of this device is to switch 8 video-input sources on the 6 outputs.

Each output can be switched on only one of each input. On each input an alignment of the lowest level

of the signal is made (bottom of sync. top for CVBS or black level for RGB signals).

Each nominal gain between any input and output is 6.5dB.For D2MAC or Chroma signal the alignment

is switched off by forcing, with an external resistor bridge, 5VDC on the input. Each input can be used

as a normal input or as a MAC or Chroma input (with external Resistor Bridge). All the switching

possibilities are changed through the BUS. Driving 75ohm load needs an external resistor. It is possible

to have the same input connected to several outputs.

4. AUDIO AMPLIFIER STAGE WITH TDA8928ST

The TDA8928ST is a switching power stage for high efficiency class-D audio power amplifier system.

With this power stage a compact 2x10 W Self Oscillating Digital Amplifier System (SODA) can be built,

operating with high efficiency and very low dissipation. No heat sink is required. The system operates

over a wide supply voltage range from ±7.5 V to ±30 V and consumes a very low quiescent current.

5. POWER SUPPLY (SMPS)

The DC voltages required at various parts of the chassis are provided by an SMPS transformer

controlled by the IC MC44608, which is designed for driving, controlling and protecting switching

transistor of SMPS. The transformer generates 145V for FBT input, +/-14V for audio amplifier, 5V and

3.3V stand by voltage and 33V, 12V and 5V supplies for other different parts of the chassis.

An optocoupler is used to control the regulation of line voltage and stand-by power consumption. There

is a regulation circuit in secondary side. This circuit produces a control voltage according to the

changes in 145V DC voltage, via an optocoupler (TCET1102G) to pin3 of the IC.

During the switch on period of the transistor, energy is stored in the transformer. During the switch off

period energy is fed to the load via secondary winding. By varying switch-on time of the power

1

Plasma TV Service Manual 11/01/2005

transistor, it controls each portion of energy transferred to the second side such that the output voltage

remains nearly independent of load variations.

6. MICROCONTROLLER

The microprocessor is embedded inside PW181 chip which also handles scaling, frame rate conversion

and OSD generation. The on-chip 16-bit microprocessor is a Turbo x86-compatible processor core with

on-chip peripherals (timers, interrupt controller, 2-wire serial master/slave interface, UART, I/O ports,

and more). Special peripherals such as Infrared (IR) pulse decoders and a digital pulse width modulator

(PWM) are also included. There are two independent 2-wire serial master/slave interface modules that

can be multiplexed to control up to five 2-wire serial ports. The slave 2-wire interface is designed for

HDCP use only (and requires the use of HDCP Image Processors). On-chip RAM of up to 64 Kbytes is

available. A complete microprocessor system can be implemented simply by adding external ROM. The

on-chip processor can be disabled to allow external processor control of all internal functions.

7. SERIAL ACCESS CMOS 4K x 8 (32K bit) EEPROM 24C32A

The Microchip Technology Inc. 24C32A is a 4K x 8 (32K bit) Serial Electrically Erasable PROM. It has

been developed for advanced, low power applications such as personal communications or data

acquisition. The 24C32A also has a page-write capability of up to 32 bytes of data. The 24C32A is

capable of both random and sequential reads up to the 32K boundary. Functional address lines allow

up to eight 24C32A devices on the same bus, for up to 256K bits address space. Advanced CMOS

technology and broad voltage range make this device ideal for low-power/low-voltage, non-volatile code

and data applications.

8. CLASS AB STEREO HEADPHONE DRIVER TDA1308

The TDA1308 is an integrated class AB stereo headphone driver contained in a DIP8 plastic package.

The device is fabricated in a 1 mm CMOS process and has been primarily developed for portable digital

audio applications.

9. IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM

TEA6415C

24C32

LM317T

ST24LC21

TLC7733

74LVC257A

74LVC14A

TEA6420D

LM1086

LM1117

DS90C385

TL431

MSP3411G

TDA7265

TDA1308

PI5V330

AD9883A

SAA7118E

TPS72501

TSOP1836

PCF8591

PW1231

PW181

SIL151B

SDRAM 4M x 16 (MT48LC4M16A2TG-75)

FLASH

2

Plasma TV Service Manual 11/01/2005

9.1.

TEA6415C

9.1.1. General Description

The main function of the IC is to switch 8 video input sources on 6 outputs. Each output can be

switched on only one of each input. On each input an alignment of the lowest level of the signal is made

(bottom of synch. top for CVBS or black level for RGB signals). Each nominal gain between any input

and output is 6.5dB. For D2MAC or Chroma signal the alignment is switched off by forcing, with an

external resistor bridge, 5 V

DC on the input. Each input can be used as a normal input or as a MAC or

Chroma input (with external resistor bridge). All the switching possibilities are changed through the

BUS. Driving 75" load needs an external transistor. It is possible to have the same input connected to

several outputs. The starting configuration upon power on (power supply: 0 to 10V) is undetermined. In

this case, 6 words of 16 bits are necessary to determine one configuration. In other case, 1 word of 16

bits is necessary to determine one configuration.

9.1.2. Features

• 20MHz Bandwidth

• Cascadable with another TEA6415C (Internal address can be changed by pin 7 voltage)

• 8 Inputs (CVBS, RGB, MAC, CHROMA,)

• 6 Outputs

• Possibility of MAC or chroma signal for each input by switching-off the clamp with an external resistor

bridge

• Bus controlled

• 6.5dB gain between any input and output

• 55dB crosstalk at 5 MHz

• Fully ESD protected

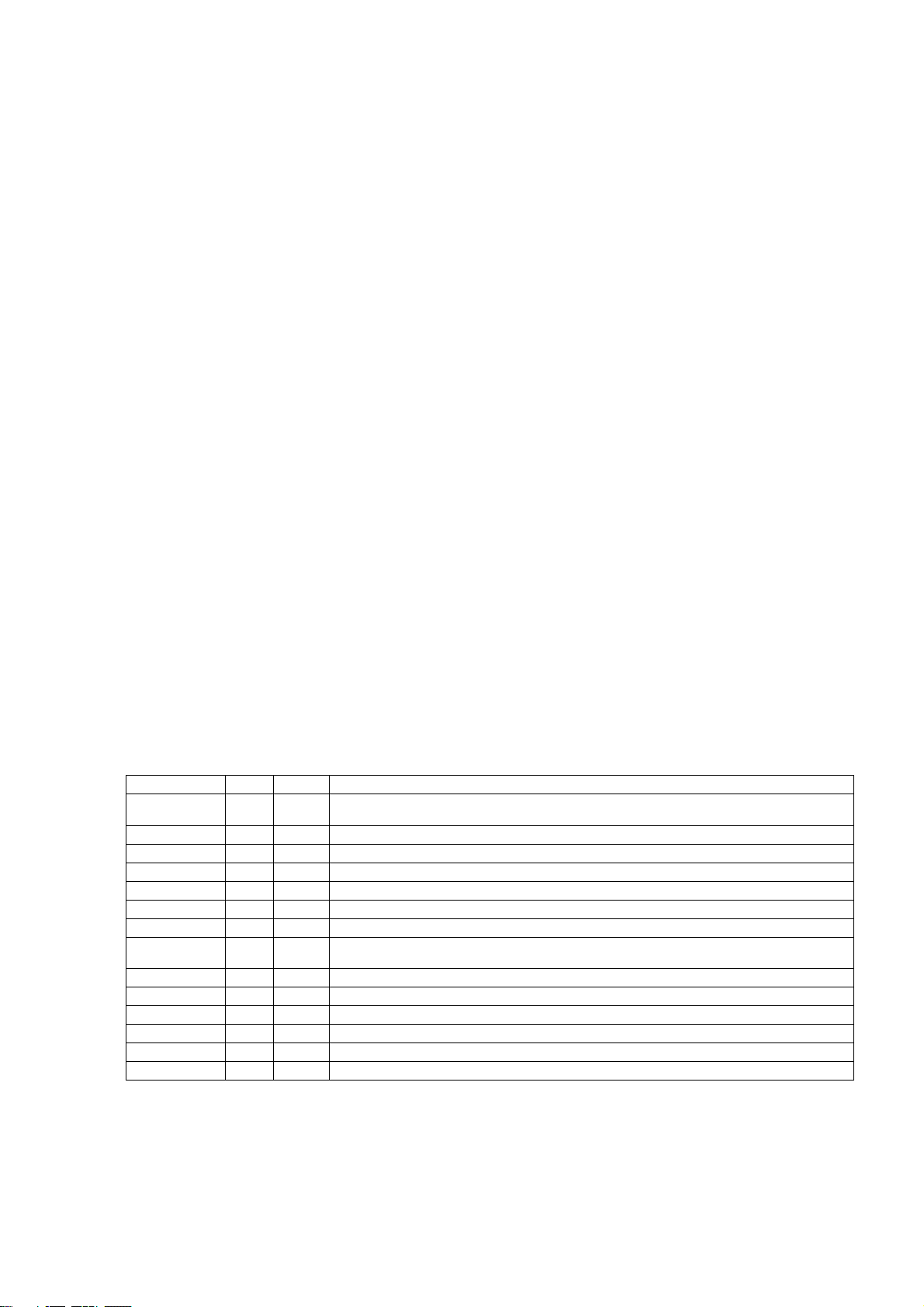

9.1.3. Pinning

1. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

2. Data : Low level : -0.3V Max: 1.5V,

High level : 3.0V Max : Vcc+0.5V

3. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

4. Clock : Low level : -0.3V Max: 1.5V,

High level : 3.0V Max : Vcc+0.5V

5. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

6. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

7. Prog

8. Input : Max : 2Vpp, Input Current: 1mA, Max: 3mA

9. Vcc : 12V

10. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

11. Input : Max : 2Vpp, Input Current: 1mA, Max : 3mA

12. Ground

13. Output : 5.5Vpp, Min: 4.5Vpp

14. Output : 5.5Vpp, Min: 4.5Vpp

15. Output : 5.5Vpp, Min: 4.5Vpp

16. Output : 5.5Vpp, Min: 4.5Vpp

17. Output : 5.5Vpp, Min: 4.5Vpp

18. Output : 5.5Vpp, Min: 4.5Vpp

19. Ground

20. Input : Max: 2Vpp, Input Current : 1mA, Max : 3mA

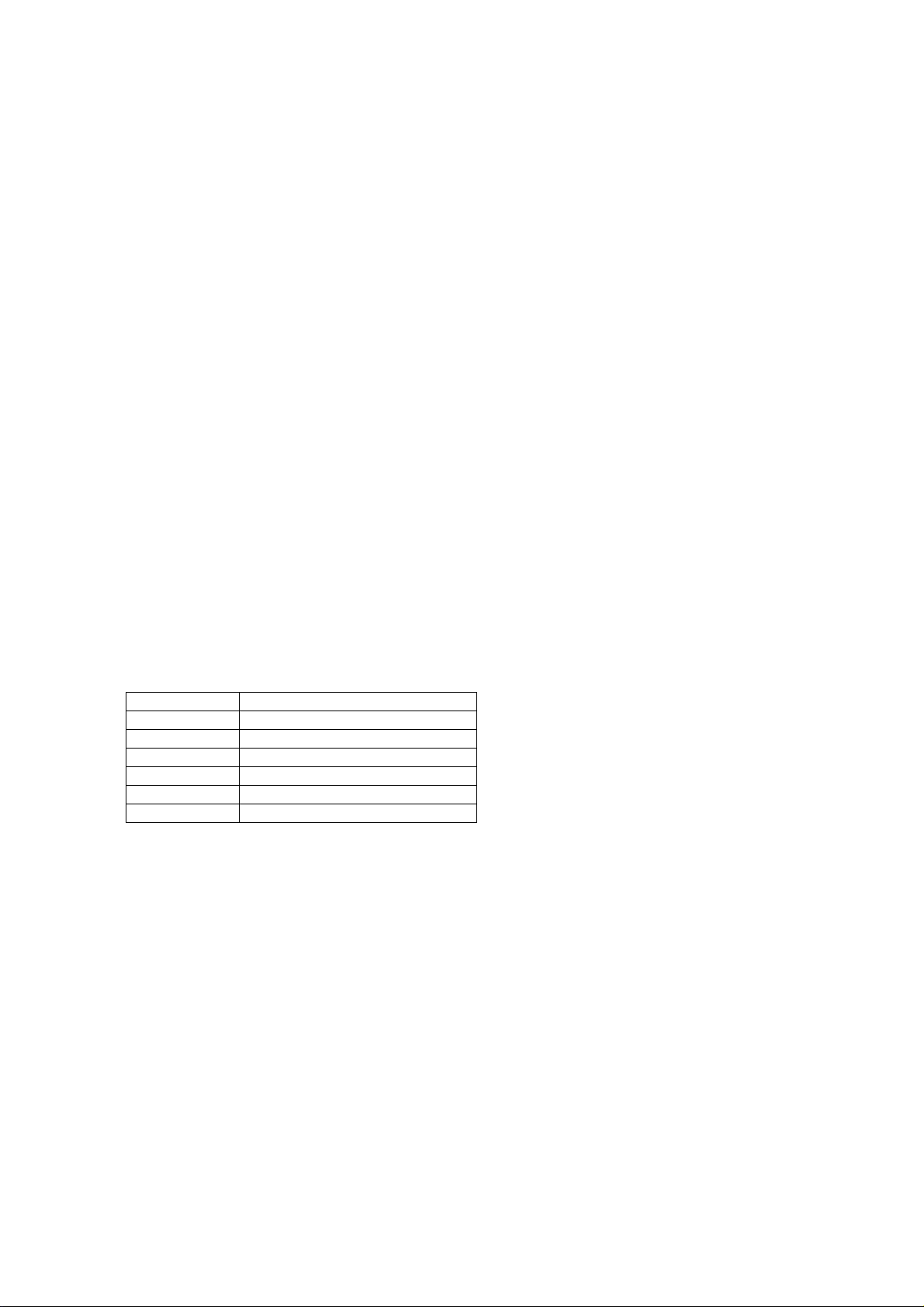

9.2.

24C32A

9.2.1. Features

• Voltage operating range: 4.5V to 5.5V

- Maximum write current 3 mA at 5.5V

3

Plasma TV Service Manual 11/01/2005

- Standby current 1 mA typical at 5.0V

• 2-wire serial interface bus, I

2CTM

compatible

• 100 kHz and 400 kHz compatibility

• Self-timed ERASE and WRITE cycles

• Power on/off data protection circuitry

• Hardware write protect

• 1,000,000 Erase/Write cycles guaranteed

• 32-byte page or byte write modes available

• Schmitt trigger filtered inputs for noise suppression

• Output slope control to eliminate ground bounce

• 2 ms typical write cycle time, byte or page

• Up to eight devices may be connected to the same bus for up to 256K bits total memory

• Electrostatic discharge protection > 4000V

• Data retention > 200 years

• 8-pin PDIP and SOIC packages

• Temperature ranges

- Commercial (C): 0°C to 70°C

- Industrial (I): -40°C to +85°C

- Automotive (E): -40°C to +125°C

9.2.2. Description

The Microchip Technology Inc. 24C32A is a 4K x 8 (32K bit) Serial Electrically Erasable PROM. It has

been developed for advanced, low power applications such as personal communications or data

acquisition. The 24C32A also has a page-write capability of up to 32 bytes of data. The 24C32A is

capable of both random and sequential reads up to the 32K boundary. Functional address lines allow

up to eight 24C32A devices on the same bus, for up to 256K bits address space. Advanced CMOS

technology and broad voltage range make this device ideal for low-power/low-voltage, non-volatile code

and data applications. The 24C32A is available in the standard 8-pin plastic DIP and both 150 mil and

200 mil SOIC packaging.

9.2.3. Pin Function table

Name Function

A0, A1, A2 User Configurable Chip Selects

Vss Ground

SDA Serial Address/Data I/O

SCL Serial Clock

WP Write Protect Input

Vcc +4.5V to 5.5V Power Supply

4

Plasma TV Service Manual 11/01/2005

9.2.4. Functional Descriptions

The 24C32A supports a Bi-directional 2-wire bus and data transmission protocol. A device that sends

data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus must be

controlled by a master device which generates the Serial Clock (SCL), controls the bus access, and

generates the START and STOP conditions, while the 24C32A works as slave. Both master and slave

can operate as transmitter or receiver but the master device determines which mode is activated.

9.3.

LM317

9.3.1. General Description

The LM117/LM217/LM317 are monolithic integrated circuit in TO-220, ISOWATT220, TO-3 and D

2

PAK packages intended for use as positive adjustable voltage regulators.

They are designed to supply more than 1.5A of load current with an output voltage adjustable over a

1.2 to 37V range.

The nominal output voltage is selected by means of only a resistive divider, making the device

exceptionally easy to use and eliminating the stocking of many fixed regulators.

9.3.2. Features

• Output voltage range: 1.2 to 37V

• Output current In excess of 1.5A

• 0.1% Line and Load Regulation

• Floating Operation for High Voltages

• Complete Series of Protections: Current Limiting, Thermal Shutdown And Soa Control

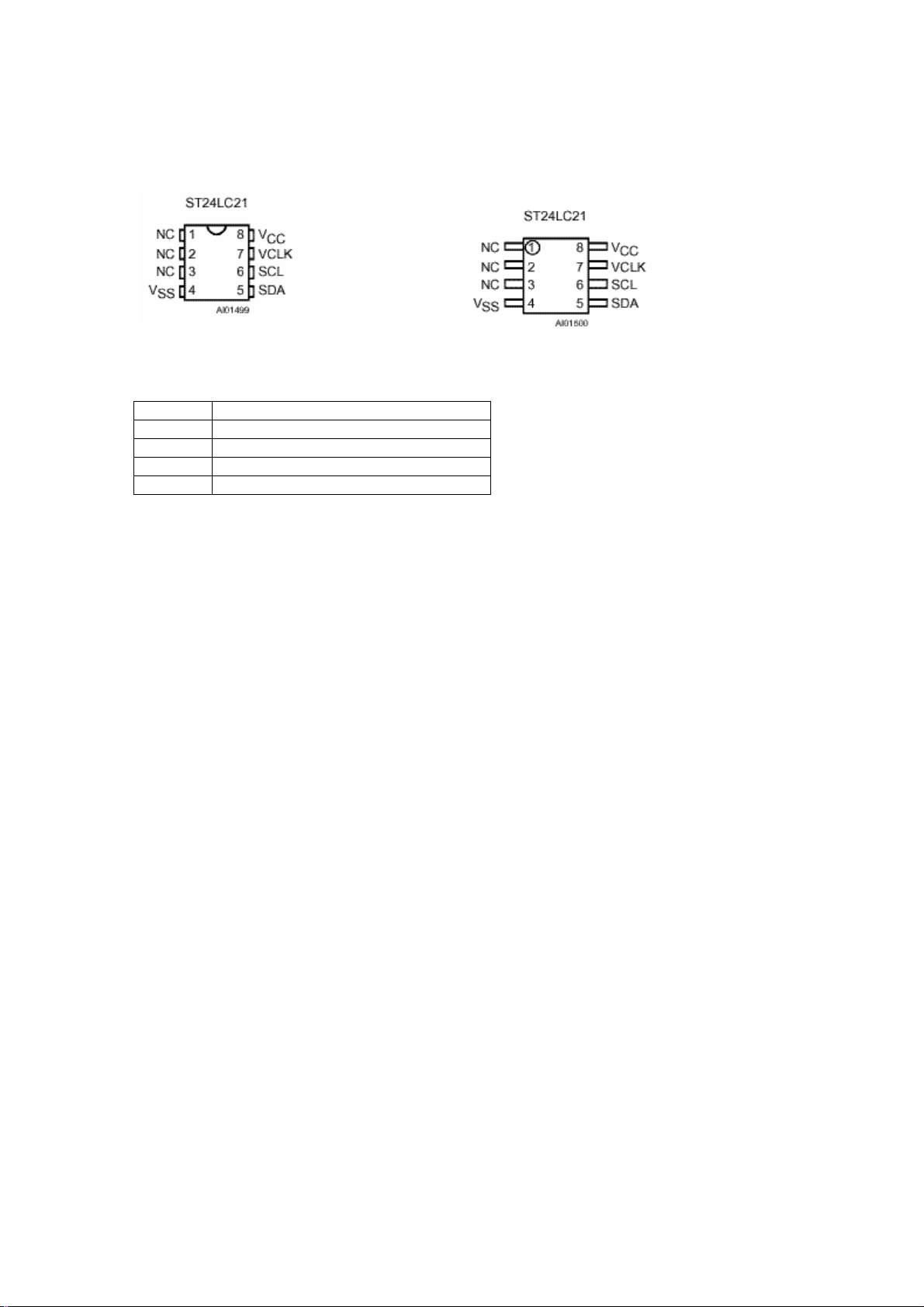

ST24LC21

9.4.

9.4.1. Description

The ST24LC21 is a 1K bit electrically erasable programmable memory (EEPROM), organized by 8 bits.

2

This device can operate in two modes: Transmit Only mode and I

C bidirectional mode. When powered,

the device is in Transmit Only mode with EEPROM data clocked out from the rising edge of the signal

2

applied on VCLK. The device will switch to the I

applied on SCL pin. The ST24LC21 can not switch from the I

C bidirectional mode upon the falling edge of the signal

2

C bidirectional mode to the Transmit Only

mode (except when the power supply is removed). The device operates with a power supply value as

low as 2.5V. Both Plastic Dual-in-Line and Plastic Small Outline packages are available.

9.4.2. Features

• 1 million Erase/Write cycles

• 40 years data retention

• 2.5V To 5.5V single supply voltage

• 400k Hz compatibility over the full range of supply voltage

• Two wire serial interface I

2

C bus compatible

• Page Write (Up To 8 Bytes)

• Byte, random and sequential read modes

• Self timed programming cycle

• Automatic address incrementing

• Enhanced ESD/Latch up

• Performances

5

Plasma TV Service Manual 11/01/2005

9.4.3. Pin connections

DIP Pin connections CO Pin connections

NC: Not connected

Signal names

SDA Serial data Address Input/Output

SCL Serial Clock (I2C mode)

Vcc Supply voltage

Vss Ground

VCLK Clock transmit only mode

9.5.

TLC7733

9.5.1. Description

The TLC77xx family of micro power supply voltage supervisors is designed for reset control, primarily in

microcomputer and microprocessor systems.

During power-on, RESET is asserted when V

reaches 1 V. After minimum V

DD

(. 2 V) is established,

DD

the circuit monitors SENSE voltage and keeps the reset outputs active as long as SENSE voltage

I(SENSE)

)

(V

remains below the threshold voltage. An internal timer delays return of the output to the inactive state to

ensure proper system reset. The delay time, t

= 2.1 x 10 4 x CT

t

d

, is determined by an external capacitor:

d

Where

is in farads

C

T

is in seconds

t

d

The TLC77xx has a fixed SENSE threshold voltage set by an internal voltage divider. When SENSE

voltage drops below the threshold voltage, the outputs become active and stay in that state until

SENSE voltage returns above threshold voltage and the delay time, t

, has expired.

d

In addition to the power-on-reset and under voltage-supervisor function, the TLC77xx adds power-down

control support for static RAM. When CONTROL is tied to GND, RESET will act as active high. The

voltage monitor contains additional logic intended for control of static memories with battery backup

during power failure. By driving the chip select (CS) of the memory circuit with the RESET output of the

TLC77xx and with the CONTROL driven by the memory bank select signal (CSH1) of the

microprocessor (see Figure 10), the memory circuit is automatically disabled during a power loss. (In

this application the TLC77xx power has to be supplied by the battery.)

The TLC77xxQ is characterized for operation over a temperature range of –40°C to 125°C, and the

TLC77xxI is characterized for operation over a temperature range of –40°C to 85°C.

6

Plasma TV Service Manual 11/01/2005

9.6.

74LVC257A

9.6.1. Features

Wide supply voltage range of 1.2 to 3.6 V

In accordance with JEDEC standard no. 8-1A

CMOS lower power consumption

Direct interface with TTL levels

Output drive capability 50 _ transmission lines at 85°C

5 Volt tolerant inputs/outputs, for interfacing with 5 Volt logic

9.6.2. Description

The 74LVC257A is a high-performance, low-power, low-voltage, Si-gate CMOS device and superior to

most advanced CMOS compatible TTL families.

Inputs can be driven from either 3.3V or 5.0V devices. In 3-State operation, outputs can handle 5V. This

feature allows the use of these devices as translators in a mixed 3.3V/5V environment.

The 74LVC257A is a quad 2-input multiplexer with 3-state outputs, which select 4 bits of data from two

sources and are controlled by a common data select input (S). The data inputs from source 0 (1l 0 to 4l

0 ) are selected when input S is LOW and the data inputs from source 1 (1l 1 to 4l 1 ) are selected

when S in HIGH. Data appears at the outputs (1Y to 4Y) in true (non-inverting) form from the selected

inputs. The 74LVC257A is the logic implementation of a 4-pole, 2-position switch, where the position of

the switch is determined by the logic levels applied to S. The outputs are forced to a high impedance

OFF-state when OE is HIGH.

9.6.3. Pin Description

PIN NUMBER SYMBOL DESCRIPTION

1 S Common data select input

2, 5, 11, 14

3, 6, 10, 13

1|

1|

to 4|

0

to 4|

1

Data inputs from source 0

0

Data outputs from source 1

1

4,7,9,12 1Y to 4Y 3-State multiplexer outputs

8 GND Ground (0V)

15 OE 3-State output enable input (active LOW)

16 Vcc Positive supply voltage

9.7. 74LVC14A

9.7.1. Features

• Wide supply voltage range of 1.2 to 3.6 V

• In accordance with JEDEC standard no. 8-1A

• Inputs accept voltages up to 5.5 V

• CMOS low power consumption

• Direct interface with TTL levels

9.7.2. Applications

• Wave and pulse shapers for highly noisy environments

• Astable multivibrators

• Monostable multivibrators

9.7.3. Description

The 74LVC14A is a high-performance, low power, low-voltage Si-gate CMOS device and superior to

most advanced CMOS compatible TTL families.

Inputs can be driven from either 3.3 V or 5 V devices. This feature allows the use of these devices as

translators in a mixed 3.3 V/5 V environment.

The 74LVC14A provides six inverting buffers with Schmitt-trigger action. It is capable of transforming

slowly changing input signals into sharply defined, jitter-free output signals.

7

Plasma TV Service Manual 11/01/2005

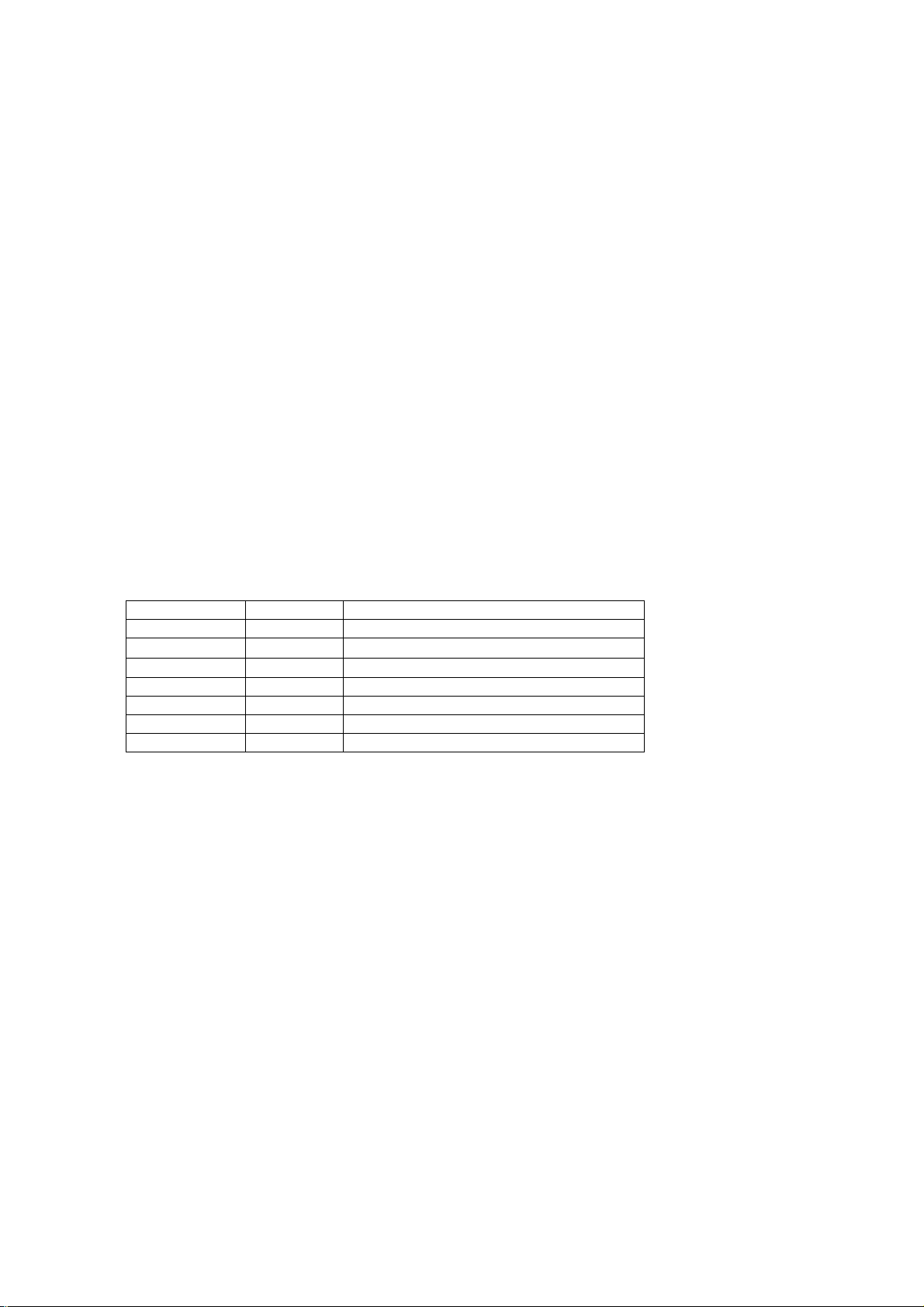

9.7.4. Pin Description

PIN NUMBER SYMBOL DESCRIPTION

1, 3, 5, 9, 11, 13 1A – 6A Data inputs

2, 4, 6, 8, 10, 12 1Y – 6Y Data outputs

7 GND Ground (0V)

14 Vcc Positive supply voltage

9.8.

TEA6420

9.8.1. Features

• 5 Stereo Inputs

• 4 Stereo Outputs

• Gain Control 0/2/4/6db/Mutefor Each Output

• Cascadable (2 Different Addresses)

• Serial Bus Controlled

• Very Low noise

• Very Low distortion

9.8.2. Description

The TEA6420 switches 5 stereo audio inputs on 4 stereo outputs.

2

All the switching possibilities are changed through the I

C bus.

9.9.

LM1086

9.9.1. Description

The LM1086 is a series of low dropout positive voltage regulators with a maximum dropout of 1.5V at

1.5A of load current. It has the same pin-out as National Semiconductor’s industry standard LM317.

The LM1086 is available in an adjustable version, which can set the output voltage with only two

external resistors. It is also available in five fixed voltages: 2.5V, 2.85V, 3.3V, 3.45V and 5.0V. The fixed

versions integrate the adjust resistors. The LM1086 circuit includes a zener trimmed band-gap

reference, current limiting and thermal shutdown.

9.9.2. Features

• Available in 2.5V, 2.85V, 3.3V, 3.45V, 5V and Adjustable Versions

• Current Limiting and Thermal Protection

• Output Current 1.5A

• Line Regulation 0.015% (typical)

• Load Regulation 0.1% (typical)

8

Plasma TV Service Manual 11/01/2005

9.9.3. Applications

• SCSI-2 Active Terminator

• High Efficiency Linear Regulators

• Battery Charger

• Post Regulation for Switching Supplies

• Constant Current Regulator

• Microprocessor Supply

9.9.4. Connection Diagrams

TO-220 TO-263

Top View

10094802

10094804

Top View

9.10. LM1117

9.10.1. General Description

The LM1117 is a series of low dropout voltage regulators with a dropout of 1.2V at 800mA of load

current. It has the same pin-out as National Semiconductor’s industry standard LM317. The LM1117 is

available in an adjustable version, which can set the output voltage from 1.25V to 13.8V with only two

external resistors. In addition, it is also available in five fixed voltages, 1.8V, 2.5V, 2.85V, 3.3V, and 5V.

The LM1117 offers current limiting and thermal shutdown. Its circuit includes a zener trimmed bandgap

reference to as-sure output voltage accuracy to within ±1%. The LM1117 series is available in SOT223, TO-220, and TO-252 D-PAK packages. A minimum of 10µF tantalum capacitor is required at the

output to improve the transient response and stability.

9.10.2. Features

• Available in 1.8V, 2.5V, 2.85V, 3.3V, 5V, and Adjustable Versions

• Space Saving SOT-223 Package

• Current Limiting and Thermal Protection

• Output Current 800mA

• Line Regulation 0.2% (Max)

• Load Regulation 0.4% (Max)

• Temperature Range

— LM1117 0°C to 125°C

— LM1117I -40°C to 125°C

9.10.3. Applications

• 2.85V Model for SCSI-2 Active Termination

• Post Regulator for Switching DC/DC Converter

• High Efficiency Linear Regulators

• Battery Charger

• Battery Powered Instrumentation

9.10.4. Connection Diagrams

SOT-223

Top

View

TO-220

Top

View

9

TO-252

Top

View

Plasma TV Service Manual 11/01/2005

9.11. DS90C385

9.11.1. General Description

The DS90C385 transmitter converts 28 bits of LVCMOS/LVTTL data into four LVDS (Low Voltage

Differential Signalling) data streams. A phase-locked transmit clock is transmitted in parallel with the

data streams over a fifth LVDS link.

Every cycle of the transmit clock 28 bits of input data are sampled and transmitted. At a transmit clock

frequency of 85 MHz, 24 bits of RGB data and 3 bits of LCD timing and control data (FPLINE,

FPFRAME, DRDY) are transmitted at a rate of 595 Mbps per LVDS data channel. Using an 85 MHz

clock, the data throughput is 297.5 Mbytes/sec. Also available is the DS90C365 that converts 21 bits of

LVCMOS/LVTTL data into three LVDS (Low Voltage Differential Signalling) data streams. Both

transmitters can be programmed for Rising edge strobe or falling edge strobe through a dedicated pin.

A Rising edge or Falling edge strobe transmitter will interoperate with a Falling edge strobe Receiver

(DS90CF386/DS90CF366) without any translation logic.

The DS90C385 is also offered in a 64 ball, 0.8mm fine pitch ball grid array (FBGA) package which

provides a 44 % reduction in PCB footprint compared to the TSSOP package. This chipset is an ideal

means to solve EMI and cable size problems associated with wide, high-speed TTL interfaces.

9.11.2. Features

• 20 to 85 MHz shift clock support

• Best–in–Class Set & Hold Times on TxINPUTs

• Tx power consumption <130 mW (typ) @85MHz Grayscale

• Tx Power-down mode <200µW (max)

• Supports VGA, SVGA, XGA and Dual Pixel SXGA.

• Narrow bus reduces cable size and cost

• Up to 2.38 Gbps throughput

• Up to 297.5 Megabytes/sec bandwidth

• 345 mV (typ) swing LVDS devices for low EMI

• PLL requires no external components

• Compatible with TIA/EIA-644 LVDS standard

• Low profile 56-lead or 48-lead TSSOP package

• DS90C385 also available in a 64 ball, 0.8mm fine pitch ball grid array (FBGA) package

9.11.3. Pin Description

DS90C385 MTD56 (TSSOP) Package Pin Description-FPD Link Transmitter

Pin Name I/O No. Description

TxIN

TxOUT+

TxOUT-

TxCLKIN

R_FB

TxCLK OUT+

TxCLK OUT-

PWR DOWN

Vcc

GND

PLL Vcc

PLL GND

LVDS Vcc

LVDS GND

I 28

O 4

O 4

I 1

I 1

O 1

O 1

I 1

I 3

I 4

I 1

I 2

I 1

I 3

TTL level input. This includes: 8 Red, 8 Green, 8 Blue, and 4 control lines —FPLINE,

FPFRAME and DRDY (also referred to as HSYNC, VSYNC, Data Enable).

Positive LVDS differentiaI data output.

Negative LVDS differential data output.

TTL Ievel clock input. Pin name TxCLK IN.

Programmable strobe select

Positive LVDS differential clock output.

Negative LVDS differential clock output.

TTL level input. Assertion (low input) TRI-STATES the outputs, ensuring low current at

power down.

Power supply pins for TTL inputs.

Ground pins for TTL inputs.

Power supply pin for PLL.

Ground pins for PLL.

Power supply pin for LVDS outputs.

Ground pins for LVDS outputs.

10

Plasma TV Service Manual 11/01/2005

DS90C385SLC SLC64A Package Pin Description-FPD Link Transmitter

Pin Name I/O No. Description

TxIN

TxOUT+

TxOUT-

TxCLKIN

R_FB

TxCLK OUT+

TxCLK OUT-

PWR DOWN

Vcc

GND

PLL Vcc

PLL GND

LVDS Vcc

LVDS GND

NC

I 28

O 4

O 4

I 1

I 1

O 1

O 1

I 1

I 3

I 5

I 1

I 2

I 2

I 4

6

TTL level input.

Positive LVDS differentiaI data output.

Negative LVDS differential data output.

TTL Ievel clock input. The rising edge acts as data strobe. Pin name TxCLK IN.

Programmable strobe select. HIGH = rising edge, LOW = falling edge.

Positive LVDS differential clock output.

Negative LVDS differential clock output.

TTL level input. Assertion (low input) TRI-STATES the outputs, ensuring low

current at power down.

Power supply pins for TTL inputs.

Ground pins for TTL inputs.

Power supply pin for PLL.

Ground pins for PLL.

Power supply pin for LVDS outputs.

Ground pins for LVDS outputs.

Pins not connected.

11

Plasma TV Service Manual 11/01/2005

9.12. MSP34X1G

MSP3411G

Multistandard Sound Processor Family

9.12.1. Introduction

The MSP 34x1G family of single-chip Multistandard Sound Processors covers the sound processing of

all analog TV-Standards worldwide, as well as the NICAM digital sound standards. The full TV sound

processing, starting with analog sound IF signal-in, down to processed analog AF-out, is performed on

a single chip. Figure shows a simplified functional block diagram of the MSP 34x1G.

The MSP 34x1G has all functions of the MSP 34x0G with the addition of a virtual surround sound

feature.

Surround sound can be reproduced to a certain extent with two loudspeakers. The MSP 34x1G

includes the Micronas virtualizer algorithm “3D-PANORAMA” which has been approved by the Dolby

1)

Laboratories for with the "Virtual Dolby Surround" technology. In addition, the MSP 34x1G includes the

“PAN-ORAMA” algorithm.

These TV sound processing ICs include versions for processing the multichannel television sound

(MTS) signal conforming to the standard recommended by the Broadcast Television Systems

Committee (BTSC). The DBX noise reduction, or alternatively, Micronas Noise Reduction (MNR) is

performed alignment free.

Other processed standards are the Japanese FM-FM multiplex standard (EIA-J) and the FM Stereo

Radio standard.

Current ICs have to perform adjustment procedures in order to achieve good stereo separation for

BTSC and EIA-J. The MSP 34x1G has optimum stereo performance without any adjustments.

The MSP 34x1G has built-in automatic functions: The IC is able to detect the actual sound standard

automat-ically (Automatic Standard Detection). Furthermore, pilot levels and identification signals can

be evaluated internally with subsequent switching between mono/stereo/bilingual; no I

2 C interaction is

necessary (Automatic Sound Selection).

Source Select

2

S bus interface consists of five pins:

I

2

S_DA_IN1, I2S_DA_IN2: For input, four channels (two channels per line, 2*16 bits) per sampling

1. I

cycle (32 kHz) are transmitted.

2

S _DA_OUT: For output, two channels (2*16 bits) per sampling cycle (32 kHz) are transmitted.

2. I

2

S _CL: Gives the timing for the transmission of I2S serial data (1.024 MHz).

3. I

2

S _WS: The I2S _WS word strobe line defines the left and right sample.

4. I

12

Plasma TV Service Manual 11/01/2005

9.12.2. Features

• 3D-PANORAMA virtualizer (approved by Dolby Laboratories) with noise generator

• PANORAMA virtualizer algorithm

• Standard Selection with single I

2

C transmission

• Automatic Sound Selection (mono/stereo/bilingual),

• Automatic Carrier Mute function

• Interrupt output programmable (indicating status change)

• Loudspeaker / Headphone channel with volume, balance, bass, treble, loudness

• AVC: Automatic Volume Correction

• Subwoofer output with programmable low-pass and complementary high-pass filter

• 5-band graphic equalizer for loudspeaker channel

• Spatial effect for loudspeaker channel, processing of all deemphasis filtering

• Two selectable sound IF (SIF) inputs

• Four Stereo SCART (line) inputs, one Mono input; two Stereo SCART outputs

• Complete SCART in/out switching matrix

• Two I

2

S inputs; one I2S output

• Automatic Standard Detection of terrestrial TV standards

• Demodulation of the BTSC multiplex signal and the SAP channel

• Alignment free digital DBX noise reduction

• BTSC stereo separation (MSP 3441G also EIA-J) significantly better than specification

• SAP and stereo detection for BTSC system

• Demodulation of the FM-Radio multiplex signal

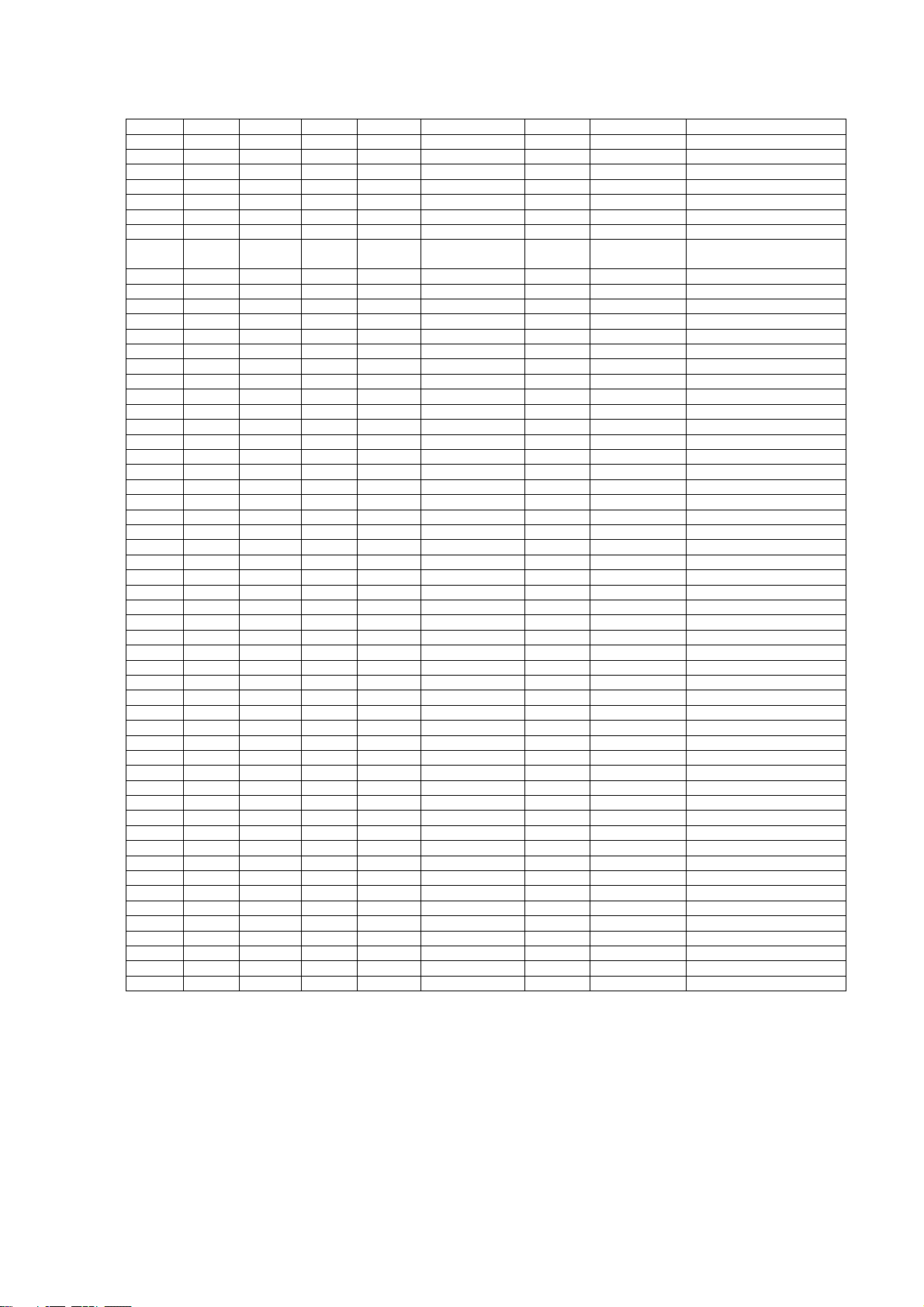

9.12.3. Pin connections

NC = not connected; leave vacant

LV = if not used, leave vacant

OBL = obligatory; connect as described in circuit diagram

DVSS: if not used, connect to DVSS

AHVSS: connect to AHVSS

Pin No. Pin Name Type

PLCC

68-pin

1 16 14 9 8 ADR_WS OUT LV ADR word strobe

2 - - - - NC LV Not connected

3 15 13 8 7 ADR_DA OUT LV ADR Data Output

4 14 12 7 6 I2S_DA_IN1 IN LV I2S1 data input

5 13 11 6 5 I2S_DA_OUT OUT LV I2S data output

6 12 10 5 4 I2S_WS IN/OUT LV I2S word strobe

7 11 9 4 3 I2S_CL IN/OUT LV I2S clock

8 10 8 3 2 I2C_DA IN/OUT OBL I2C data

9 9 7 2 1 I2C_CL IN/OUT OBL I2C clock

10 8 - 1 64 NC LV Not connected

11 7 6 80 63 STANDBYQ IN OBL Stand-by (low-active)

12 6 5 79 62 ADR_SEL IN OBL I2C bus address select

13 5 4 78 61 D_CTR_I/O_0 IN/OUT LV D_CTR_I/O_0

14 4 3 77 60 D_CTR_I/O_1 IN/OUT LV D_CTR_I/O_1

15 3 - 76 59 NC LV Not connected

16 2 - 75 58 NC LV Not connected

17 - - - - NC LV Not connected

18 1 2 74 57 AUD_CL_OUT OUT LV

19 64 1 73 56 TP LV Test pin

20 63 52 72 55 XTAL_OUT OUT OBL Crystal oscillator

21 62 51 71 54 XTAL_IN IN OBL Crystal oscillator

22 61 50 70 53 TESTEN IN OBL Test pin

23 60 49 69 52 ANA_IN2+ IN

24 59 48 68 51 ANA_IN- IN

25 58 47 67 50 ANA_IN1+ IN LV IF input 1

PSDIP

64-pin

PSDIP

52-pin

PQFP

80-pin

PLQFP

64-pin

Connection

(if not used)

AVSS via

56 pF/LV

AVSS via

56 pF/LV

Short Description

Audio clock output

(18.432 MHz)

IF Input 2 (can be left

vacant, only if IF input 1 is

also not in use)

IF common (can be left

vacant, only if IF input 1 is

also not in use)

13

Plasma TV Service Manual 11/01/2005

26 57 46 66 49 AVSUP OBL Analog power supply 5V

- - - 65 - AVSUP OBL Analog power supply 5V

- - - 64 - NC LV Not connected

- - - 63 - NC LV Not connected

27 56 45 62 48 AVSS OBL Analog ground

- - - 61 - AVSS OBL Analog ground

28 55 44 60 47 MONO_IN IN LV Mono input

- - - 59 - NC LV Not connected

29 54 43 58 46 VREFTOP OBL

30 53 42 57 45 SC1_IN_R IN LV SCART 1 input, right

31 52 41 56 44 SC1_IN_L IN LV SCART 1 input, left

32 51 - 55 43 ASG1 AHVSS Analog Shield Ground 1

33 50 40 54 42 SC2_IN_R IN LV SCART 2 input, right

34 49 39 53 41 SC2_IN_L IN LV SCART 2 input, left

35 48 - 52 40 ASG2 AHVSS Analog Shield Ground 2

36 47 38 51 39 SC3_IN_R IN LV SCART 3 input, right

37 46 37 50 38 SC3_IN_L IN LV SCART 3 input, left

38 45 - 49 37 ASG4 AHVSS Analog Shield Ground 4

39 44 - 48 36 SC4_IN_R IN LV SCART 4 input, right

40 43 - 47 35 SC4_IN_L IN LV SCART 4 input, left

41 - - 46 - NC LV or AHVSS Not connected

42 42 36 45 34 AGNDC OBL Analog reference voltage

43 41 35 44 33 AHVSS OBL Analog ground

- - - 43 - AHVSS OBL Analog ground

- - - 42 - NC LV Not connected

- - - 41 - NC LV Not connected

44 40 34 40 32 CAPL_M OBL Volume capacitor MAIN

45 39 33 39 31 AHVSUP OBL Analog power supply 8V

46 38 32 38 30 CAPL_A OBL Volume capacitor AUX

47 37 31 37 29 SC1_OUT_L OUT LV SCART output 1, left

48 36 30 36 28 SC1_OUT_R OUT LV SCART output 1, right

49 35 29 35 27 VREF1 OBL Reference ground 1

50 34 28 34 26 SC2_OUT_L OUT LV SCART output 2, left

51 33 27 33 25 SC2_OUT_R OUT LV SCART output 2, right

52 - - 32 - NC LV Not connected

53 32 - 31 24 NC LV Not connected

54 31 26 30 23 DACM_SUB OUT LV Subwoofer output

55 30 - 29 22 NC LV Not connected

56 29 25 28 21 DACM_L OUT LV Loudspeaker out, left

57 28 24 27 20 DACM_R OUT LV Loudspeaker out, right

58 27 23 26 19 VREF2 OBL Reference ground 2

59 26 22 25 18 DACA_L OUT LV Headphone out, left

60 25 21 24 17 DACA_R OUT LV Headphone out, right

- - - 23 - NC LV Not connected

- - - 22 - NC LV Not connected

61 24 20 21 16 RESETQ IN OBL Power-on-reset

62 23 - 20 15 NC LV Not connected

63 22 - 19 14 NC LV Not connected

64 21 19 18 13 NC LV Not connected

65 20 18 17 12 I2S_DA_IN2 IN LV I2S2-data input

66 19 17 16 11 DVSS OBL Digital ground

- - - 15 - DVSS OBL Digital ground

- - - 14 - DVSS OBL Digital ground

67 18 16 13 10 DVSUP OBL Digital power supply 5V

- - - 12 - DVSUP OBL Digital power supply 5V

- - - 11 - DVSUP OBL Digital power supply 5V

68 17 15 10 9 ADR_CL OUT LV ADR clock

Reference voltage IF A/D

converter

14

Plasma TV Service Manual 11/01/2005

9.13. TDA1308

9.13.1. General Description

The TDA1308 is an integrated class AB stereo headphone driver contained in an SO8 or a DIP8 plastic

package. The device is fabricated in a 1 mm CMOS process and has been primarily developed for

portable digital audio applications. It gets its input from two analog audio outputs (DACA_L and

DACA_R) of MSP 34x0G. The gain of the output is adjustable by the feedback resistor between the

inputs and outputs.

9.13.2. Features

Wide temperature range

•

• No switch ON/OFF clicks

• Excellent power supply ripple rejection

• Low power consumption

• Short-circuit resistant

• High performance

• high signal-to-noise ratio

• High slew rate

• Low distortion

• Large output voltage swing.

15

Plasma TV Service Manual 11/01/2005

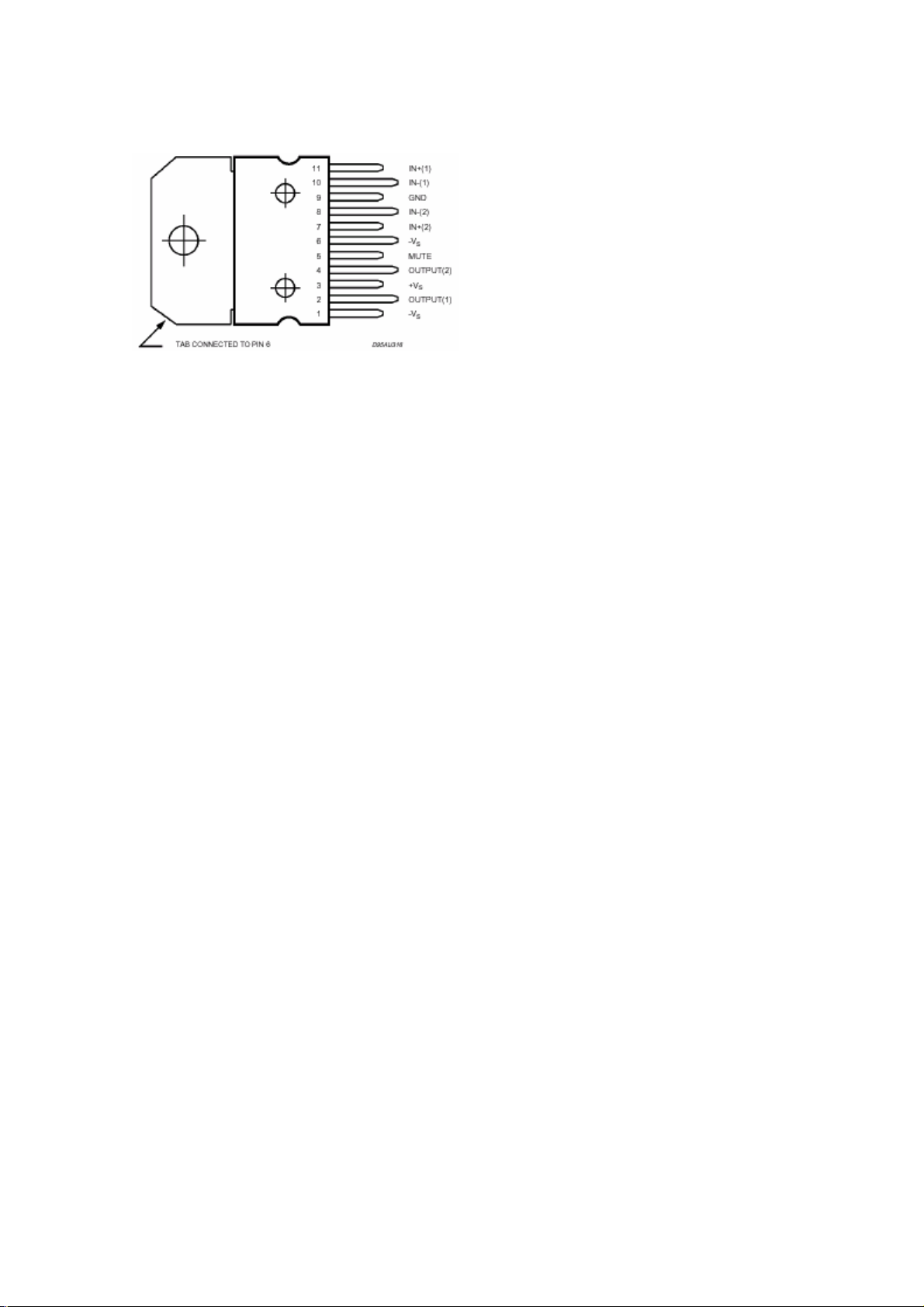

9.13.3. Pinning

SYMBOL PIN DESCRIPTION

OUTA 1 Output A

INA(neg) 2 Inverting input A

INA(pos) 3 Non-inverting input A

VSS 4 Negative supply

INB(pos) 5 Non-inverting input B

INB(neg) 6 Inverting input B

OUTB 7 Output B

VDD 8 Positive supply

9.14. PI5V330

9.14.1. General Description

The PI5V330 is well suited for video applications when switching composite or RGB analog. A picturein-picture application will be described in this brief. The pixel-rate creates video overlays so two or more

pictures can be viewed at the same time. An inexpensive NTSC titler can be implemented by

superimposing the output of a character generator on a standard composite video background.

9.15. AD9883A

9.15.1. General Description

The AD9883A is a complete 8-bit, 140 MSPS, monolithic analog interface optimized for capturing RGB

graphics signals from personal computers and workstations. Its 140 MSPS encode rate capability and

full power analog bandwidth of 300 MHz supports resolutions up to SXGA (1280 × 1024 at 75 Hz).

The AD9883A includes a 140 MHz triple ADC with internal 1.25 V reference, a PLL, and programmable

gain, offset, and clamp control. The user provides only a 3.3 V power supply, analog input, and Hsync

and COAST signals. Three-state CMOS outputs may be powered from 2.5 V to 3.3 V.

The AD9883A’s on-chip PLL generates a pixel clock from the Hsync input. Pixel clock output

frequencies range from 12 MHz to140 MHz. PLL clock jitter is 500 ps p-p typical at 140 MSPS. When

the COAST signal is presented, the PLL maintains its output frequency in the absence of Hsync. A

sampling phase adjustment is provided. Data, Hsync, and clock output phase relationships are

maintained. The AD9883A also offers full sync processing for composite sync and sync-on-green

applications. A clamp signal is generated internally or may be provided by the user through the CLAMP

input pin. This interface is fully programmable via a 2-wire serial interface.

Fabricated in an advanced CMOS process, the AD9883A is provided in a space-saving 80-lead LQFP

surface-mount plastic package and is specified over the –40.˚C to +85. ˚C temperature range.

9.15.2. Features

• Industrial Temperature Range Operation

• 140 MSPS Maximum Conversion Rate

• 300 MHz Analog Bandwidth

• 0.5 V to 1.0 V Analog Input Range

• 500 ps p-p PLL Clock Jitter at 110 MSPS

• 3.3 V Power Supply

• Full Sync Processing

• Sync Detect for Hot Plugging

• Midscale Clamping

• Power-Down Mode

• Low Power: 500 mW Typical

• 4:2:2 Output Format Mode

• APPLICATIONS

• RGB Graphics Processing

• LCD Monitors and Projectors

• Plasma Display Panels

• Scan Converters

• Microdisplays

• Digital TV

16

Plasma TV Service Manual 11/01/2005

9.15.3. Pin Descriptions

Complete Pinout list

Pin Type Mnemonic Function Value Pin No.

Inputs RAIN

GAIN

BAIN

HSYNC

VSYNC

SOGIN

CLAMP

COAST

Outputs Red [7:0]

Green [7:0]

Blue [7:0]

DATACK

HSOUT

VSOUT

SOGOUT

References REF BYPASS

MIDSCV

FILT

Power Supply VD

VDD

PVD

GND

Control SDA

SCL

A0

Analog Input for Converter R

Analog Input for Converter G

Analog Input for Converter B

Horizontal SYNC Input

Vertical SYNC Input

Input for Sync-on-Green

Clamp Input (External CLAMP Signal) PLL

COAST Signal Input

Outputs of Converter Red, Bit 7 is the MSB

Outputs of Converter Green, Bit 7 is the MSB

Outputs of Converter Blue, Bit 7 is the MSB

Data Output Clock

HSYNC Output (Phase-Aligned with DATACK)

VSYNC Output (Phase-Aligned with DATACK)

Sync-on-Green Slicer Output

Internal Reference Bypass

Internal Midscale Voltage Bypass

Connection for External Filter Components for

Internal PLL

Analog Power Supply

Output Power Supply

PLL Power Supply

Ground

Serial Port Data I/O

Serial Port Data Clock (100 kHz Maximum)

Serial Port Address Input 1

0.0 V to 1.0 V

0.0 V to 1.0 V

0.0 V to 1.0 V

3.3 V CMOS

3.3 V CMOS

0.0 V to 1.0 V

3.3 V CMOS

3.3 V CMOS

3.3 V CMOS

3.3 V CMOS

3.3 V CMOS

3.3 V CMOS

3.3 V CMOS

3.3 V CMOS

3.3 V CMOS

1.25 V 58

3.3 V

3.3 V

3.3 V

0 V

3.3 V CMOS

3.3 V CMOS

3.3 V CMOS

54

48

43

30

31

49

38

29

70–77

2–9

12–19

67

66

64

65

37

33

39, 42,

45, 46,

51, 52,

59, 62

11, 22,

23, 69,

78, 79

26, 27,

34, 35

1, 10,

20, 21,

24, 25,

28, 32,

36, 40,

41, 44,

47, 50,

53, 60,

61, 63,

68, 80

57

56

55

Pin Function Descriptions:

Pin Name Function

OUTPUTS

HSOUT

VSOUT

SOGOUT

Horizontal Sync Output

A reconstructed and phase-aligned version of the Hsync input. Both the polarity

and duration of this output can be programmed via serial bus registers. By

maintaining alignment with DATACK and Data, data timing with respect to

horizontal sync can always be determined.

Vertical Sync Output

A reconstructed and phase-aligned version of the video Vsync. The polarity of this

output can be controlled via a serial bus bit. The placement and duration in all

modes is set by the graphics transmitter.

Sync-On-Green Slicer Output

This pin outputs either the signal from the Sync-on-Green slicer comparator or an

unprocessed but delayed version of the Hsync input. See the Sync Processing

Block Diagram (Figure 12) to view how this pin is connected. (Note: Besides slicing

off SOG, the output from this pin gets no other additional processing on the

17

Plasma TV Service Manual 11/01/2005

SERIAL PORT (2-WIRE)

SDA

SCL

A0

DATA OUTPUTS

RED

GREEN

BLUE

DATA CLOCK OUTPUT

DATACK

INPUTS

RAIN

GAIN

BAIN

HSYNC

VSYNC

SOGIN

CLAMP

AD9883A. Vsync separation is performed via the sync separator.)

Serial Port Data I/O

Serial Port Data Clock

Serial Port Address Input 1

For a full description of the 2-wire serial register and how it works, refer to the 2Wire Serial Control Port section.

Data Output, Red Channel

Data Output, Green Channel

Data Output, Blue Channel

The main data outputs. Bit 7 is the MSB. The delay from pixel sampling time to

output is fixed. When the sampling time is changed by adjusting the PHASE

register, the output timing is shifted as well. The DATACK and HSOUT outputs are

also moved, so the timing relationship among the signals is maintained. For exact

timing information, refer to Figures 7, 8, and 9.

Data Output Clock

This is the main clock output signal used to strobe the output data and HSOUT into

external logic. It is produced by the internal clock generator and is synchronous

with the internal pixel sampling clock. When the sampling time is changed by

adjusting the PHASE register, the output timing is shifted as well. The Data,

DATACK, and HSOUT outputs are all moved, so the timing relationship among the

signals is maintained.

Analog Input for Red Channel

Analog Input for Green Channel

Analog Input for Blue Channel

High impedance inputs that accept the Red, Green, and Blue channel graphics

signals, respectively. (The three channels are identical, and can be used for any

colours, but colours are assigned for convenient reference.) They accommodate

input signals ranging from 0.5 V to 1.0 V full scale. Signals should be ac-coupled to

these pins to support clamp operation.

Horizontal Sync Input

This input receives a logic signal that establishes the horizontal timing reference

and provides the frequency reference for pixel clock generation. The logic sense of

this pin is controlled by serial register 0EH Bit 6 (Hsync Polarity). Only the leading

edge of Hsync is active; the trailing edge is ignored. When Hsync Polarity = 0, the

falling edge of Hsync is used. When Hsync Polarity = 1, the rising edge is active.

The input includes a Schmitt trigger for noise immunity, with a nominal input

threshold of 1.5 V.

Vertical Sync Input

This is the input for vertical sync.

Sync-on-Green Input

This input is provided to assist with processing signals with embedded sync,

typically on the Green channel. The pin is connected to a high speed comparator

with an internally generated threshold. The threshold level can be programmed in

10 mV steps to any voltage between 10 mV and 330 mV above the negative peak

of the input signal. The default voltage threshold is 150 mV. When connected to an

ac-coupled graphics signal with embedded sync, it will produce a noninverting

digital output on SOGOUT. (This is usually a composite sync signal, containing

both vertical and horizontal sync information that must be separated before

passing the horizontal sync signal to Hsync.) When not used, this input should be

left unconnected. For more details on this function and how it should be

configured, refer to the Sync-on-Green section.

External Clamp Input

This logic input may be used to define the time during which the input signal is

clamped to ground. It should be exercised when the reference dc level is known to

be present on the analog input channels, typically during the back porch of the

graphics signal. The CLAMP pin is enabled by setting control bit Clamp Function to

1, (register 0FH, Bit 7, default is 0). When disabled, this pin is ignored and the

clamp timing is determined internally by counting a delay and duration from the

18

Plasma TV Service Manual 11/01/2005

COAST

REF BYPASS

MIDSCV

FILT

POWER SUPPLY

VD

VDD

PVD

GND

trailing edge of the Hsync input. The logic sense of this pin is controlled by Clamp

Polarity register 0FH, Bit 6. When not used, this pin must be grounded and Clamp

Function programmed to 0.

Clock Generator Coast Input (Optional)

This input may be used to cause the pixel clock generator to stop synchronizing

with Hsync and continue producing a clock at its current frequency and phase.

This is useful when processing signals from sources that fail to produce horizontal

sync pulses during the vertical interval. The COAST signal is generally not

required for PC-generated signals. The logic sense of this pin is controlled by

Coast Polarity (register 0FH, Bit 3). When not used, this pin may be grounded and

Coast Polarity programmed to 1, or tied HIGH (to VD through a 10 k resistor) and

Coast Polarity programmed to 0. Coast Polarity defaults to 1 at power-up.

Internal Reference BYPASS

Bypass for the internal 1.25 V band gap reference. It should be connected to

ground through a 0.1 µF capacitor. The absolute accuracy of this reference is

±4%, and the temperature coefficient is ±50 ppm, which is adequate for most

AD9883A applications. If higher accuracy is required, an external reference may

be employed instead.

Midscale Voltage Reference BYPASS

Bypass for the internal midscale voltage reference. It should be connected to

ground through a 0.1 µF capacitor. The exact voltage varies with the gain setting

of the Blue channel.

External Filter Connection

For proper operation, the pixel clock generator PLL requires an external filter.

Connect the filter shown in Figure 6 to this pin. For optimal performance, minimize

noise and parasitics on this node.

Main Power Supply

These pins supply power to the main elements of the circuit. They should be

filtered and as quiet as possible.

Digital Output Power Supply

A large number of output pins (up to 25) switching at high speed (up to 110 MHz)

generates a lot of power supply transients (noise). These supply pins are identified

separately from the VD pins so special care can be taken to minimize output noise

transferred into the sensitive analog circuitry. If the AD9883A is interfacing with

lower voltage logic, V DD may be connected to a lower supply voltage (as low as

2.5 V) for compatibility.

Clock Generator Power Supply

The most sensitive portion of the AD9883A is the clock generation circuitry. These

pins provide power to the clock PLL and help the user design for optimal

performance. The designer should provide quiet, noise-free power to these pins.

Ground

The ground return for all circuitry on-chip. It is recommended that the AD9883A be

assembled on a single solid ground plane, with careful attention given to ground

current paths.

9.16. SAA7118E

9.16.1. General Description

The SAA7118E is a video capture device for applications at the image port of VGA controllers. Philips

X-VIP is a new multistandard comb filter video decoder chip with additional component processing,

providing high quality, optionally scaled, video.

The SAA7118E is a combination of a four-channel analog pre-processing circuit including source

selection, anti-aliasing filter and ADC, an automatic clamp and gain control, a Clock Generation Circuit

(CGC), a digital multistandard decoder containing two-dimensional chrominance/luminance separation

by an adaptive comb filter and a high performance scalar, including variable horizontal and vertical up

and downscaling and a brightness, contrast and saturation control circuit.

19

Plasma TV Service Manual 11/01/2005

It is a highly integrated circuit for desktop video and similar applications. The decoder is based on the

principle of line-locked clock decoding and is able to decode the colour of PAL, SECAM and NTSC

signals into ITU 601 compatible colour component values. The SAA7118E accepts CVBS or S-video

(Y/C) as analog inputs from TV or VCR sources, including weak and distorted signals as well as

baseband component signals Y-P

-PR or RGB. An expansion port (X-port) for digital video

B

(bidirectional half duplex, D1 compatible) is also supported to connect to MPEG or video phone codec.

At the so called image port (I-port) the SAA7118E supports 8 or 16-bit wide output data with auxiliary

reference data for interfacing to VGA controllers.

The target application for the SAA7118E is to capture and scale video images, to be provided as digital

video stream through the image port of a VGA controller, for capture to system memory, or just to

provide digital baseband video to any picture improvement processing.

9.16.2. Features

Video acquisition/clock

• Up to sixteen analog CVBS, split as desired (all of the CVBS inputs optionally can be used to convert

e.g. Vestigial Side Band (VSB) signals)

• Up to eight analog Y + C inputs, split as desired

• Up to four analog component inputs, with embedded or separate sync, split as desired

• Four on-chip anti-aliasing filters in front of the Analog-to-Digital Converters (ADCs)

• Automatic Clamp Control (ACC) for CVBS, Y and C (or VSB) and component signals

• Switchable white peak control

• Four 9-bit low noise CMOS ADCs running at twice the oversampling rate (27 MHz)

• Fully programmable static gain or Automatic Gain Control (AGC), matching to the particular signal

properties

• On-chip line-locked clock generation in accordance with “ITU 601”

• Requires only one crystal (32.11 or 24.576 MHz) for all standards

• Horizontal and vertical sync detection.

Video decoder

• Digital PLL for synchronization and clock generation from all standards and non-standard video

sources e.g. consumer grade VTR

• Automatic detection of any supported colour standard

• Luminance and chrominance signal processing for PAL B, G, D, H, I and N, combination PAL N, PAL

M, NTSC M, NTSC-Japan, NTSC 4.43 and SECAM

• Adaptive 2/4-line comb filter for two dimensional chrominance/luminance separation, also with VTR

signals

– Increased luminance and chrominance bandwidth for all PAL and NTSC standards

– Reduced cross colour and cross luminance artefacts

• PAL delay line for correcting PAL phase errors

• Brightness Contrast Saturation (BCS) adjustment, separately for composite and baseband signals

• User programmable sharpness control

• Detection of copy-protected signals according to the macrovision standard, indicating level of

protection

• Independent gain and offset adjustment for raw data path.

Component video processing

• RGB component inputs

-PR component inputs

• Y-P

B

• Fast blanking between CVBS and synchronous component inputs

• Digital RGB to Y-C

-CR matrix.

B

Video scalar

• Horizontal and vertical downscaling and up scaling to randomly sized windows

• Horizontal and vertical scaling range: variable zoom to 1/64 (icon) (note: H and V zoom are restricted

by the transfer data rates)

• Anti-alias and accumulating filter for horizontal scaling

• Vertical scaling with linear phase interpolation and accumulating filter for anti-aliasing (6-bit phase

accuracy)

• Horizontal phase correct up and downscaling for improved signal quality of scaled data, especially for

compression and video phone applications, with 6-bit phase accuracy (1.2 ns step width)

20

Plasma TV Service Manual 11/01/2005

• Two independent programming sets for scalar part, to define two ‘ranges’ per field or sequences over

frames

• Field wise switching between decoder part and expansion port (X-port) input

• Brightness, contrast and saturation controls for scaled outputs.

Vertical Blanking Interval (VBI) data decoder and slicer

• Versatile VBI-data decoder, slicer, clock regeneration and byte synchronization e.g. for World

Standard Teletext (WST), North-American Broadcast Text System (NABTS), close caption, Wide

Screen Signalling (WSS) etc.

Audio clock generation

• Generation of a field-locked audio master clock to support a constant number of audio clocks per

video field

• Generation of an audio serial and left/right (channel)

Digital I/O interfaces

• Real-time signal port (R port), inclusive continuous line-locked reference clock and real-time status

information supporting RTC level 3.1 (refer to document “RTC Functional Specification” for details)

• Bidirectional expansion port (X-port) with half duplex functionality (D1), 8-bit Y-C

-CR

B

– Output from decoder part, real-time and unscaled

– Input to scalar part, e.g. video from MPEG decoder (extension to 16-bit possible)

• Video image port (I-port) configurable for 8-bit data (extension to 16-bit possible) in master mode (own

clock), or slave mode (external clock), with auxiliary timing and handshake signals

• Discontinuous data streams supported

• 32-word ´ 4-byte FIFO register for video output data

• 28-word ´ 4-byte FIFO register for decoded VBI-data output

• Scaled 4 :2 :2, 4 :1 :1, 4 :2 :0, 4 :1 :0 Y-C

-CR output

B

• Scaled 8-bit luminance only and raw CVBS data output

• Sliced, decoded VBI-data output.

Miscellaneous

• Power-on control

• 5 V tolerant digital inputs and I/O ports

• Software controlled power saving standby modes supported

• Programming via serial I 2 C-bus, full read back ability by an external controller, bit rate up to 400

kbits/s

• Boundary scan test circuit complies with the “IEEE Std. 1149.b1 - 1994”

• BGA156 package.

9.16.3. Pinning

SYMBOL PIN TYPE DESCRIPTION

XTOUT A2 O crystal oscillator output signal; auxiliary signal

XTALO A3 O 24.576 MHz (32.11 MHz) crystal oscillator output; not

connected if TTL clock input of XTALI is used

V

A4 P ground for crystal oscillator

SS(xtal)

TDO A5 O test data output for boundary scan test; note 2

XRDY A6 O task flag or ready signal from scaler, controlled by XRQT

XCLK A7 I/O clock I/O expansion port

XPD0 A8 I/O LSB of expansion port data

XPD2 A9 I/O MSB - 5 of expansion port data

XPD4 A10 I/O MSB - 3 of expansion port data

XPD6 A11 I/O MSB - 1 of expansion port data

TEST1 A12 I/pu do not connect, reserved for future extensions and for testing:

scan input

TEST2 A13 I/pu do not connect, reserved for future extensions and for testing:

scan input

AI41 B1 I analog input 41

TEST3 B2 O do not connect, reserved for future extensions and for testing

V

XTALI B4 I input terminal for 24.576 MHz (32.11 MHz) crystal oscillator

B3 P Supply voltage for crystal oscillator

DD(xtal)

or connection of external oscillator with TTL compatible

21

Plasma TV Service Manual 11/01/2005

square wave clock signal

TDI B5 I/pu test data input for boundary scan test; note 2

TCK B6 I/pu test clock for boundary scan test; note 2

XDQ B7 I/O data qualifier for expansion port

XPD1 B8 I/O MSB - 6 of expansion port data

XPD3 B9 I/O MSB - 4 of expansion port data

XPD5 B10 I/O MSB - 2 of expansion port data

XTRI B11 I X-port output control signal, affects all X-port pins (XPD7 to

XPD0, XRH, XRV, XDQ and XCLK), enable and active

polarity is under software control (bits XPE in subaddress

83H)

TEST4 B12 O do not connect, reserved for future extensions and for testing:

scan output

TEST5 B13 NC do not connect, reserved for future extensions and for testing

TEST6 B14 NC do not connect, reserved for future extensions and for testing

VSSA4 C1 P ground for analog inputs AI4x

AGND C2 P analog ground

TEST7 C3 NC do not connect, reserved for future extensions and for testing

TEST8 C4 NC do not connect, reserved for future extensions and for testing

V

C5 P Digital supply voltage 1 (peripheral cells)

DDD1

TRST C6 I/pu test reset input (active LOW), for boundary scan test (with

internal pull-up); notes 2, 3 and 4

XRH C7 I/O horizontal reference I/O expansion port

V

C8 P Digital supply voltage 2 (core)

DDD2

V

C9 P Digital supply voltage 3 (peripheral cells)

DDD3

V

C10 P Digital supply voltage 4 (core)

DDD4

XPD7 C11 I/O MSB of expansion port data

TEST9 C12 NC do not connect, reserved for future extensions and for testing

TEST10 C13 NC do not connect, reserved for future extensions and for testing

TEST11 C14 I/pu do not connect, reserved for future extensions and for testing:

scan input

AI43 D1 I analog input 43

AI42 D2 I analog input 42

AI4D D3 I differential input for ADC channel 4 (pins AI41 to AI44)

V

D4 P analog supply voltage for analog inputs AI4x (3.3 V)

DDA4

V

D5 P Digital ground 1 (peripheral cells)

SSD1

TMS D6 I/pu test mode select input for boundary scan test or scan test;

note 2

V

D7 P Digital ground 2 (core; substrate connection)

SSD2

XRV D8 I/O vertical reference I/O expansion port

V

D9 P Digital ground 3 (peripheral cells)

SSD3

V

D10 P Digital ground 4 (core)

SSD4

V

D11 P Digital ground 5 (peripheral cells)

SSD5

V

D12 P Digital supply voltage 5 (peripheral cells)