HIT HM62V8512CLRR-5SL, HM62V8512CLRR-7, HM62V8512CLRR-7SL, HM62V8512CLTT-5, HM62V8512CLTT-5SL Datasheet

...

HM62V8512C Series

4 M SRAM (512-kword × 8-bit)

ADE-203-1210A (Z)

Rev. 1.0

Jan. 31, 2001

Description

The Hitachi HM62V8512C is a 4-Mbit static RAM organized 512-kword × 8-bit. It realizes higher density,

higher performance and low power consumption by employing CMOS process technology (6-transistor

memory cell). The device, packaged in a 525-mil SOP (foot print pitch width) or 400-mil TSOP TYPE II is

available for high density mounting. The HM62V8512C is suitable for battery backup system.

Features

• Single 3.0 V supply: 2.7 V to 3.6 V

• Access time: 55/70 ns (max)

• Power dissipation

Active: 6.0 mW/MHz (typ)

Standby: 2.4 µW (typ)

• Completely static memory. No clock or timing strobe required

• Equal access and cycle times

• Common data input and output: Three state output

• Directly LV-TTL compatible: All inputs

• Battery backup operation

HM62V8512C Series

Ordering Information

Type No. Access time Package

HM62V8512CLFP-5

HM62V8512CLFP-7

HM62V8512CLFP-5SL

HM62V8512CLFP-7SL

HM62V8512CLTT-5

HM62V8512CLTT-7

HM62V8512CLTT-5SL

HM62V8512CLTT-7SL

HM62V8512CLRR-5

HM62V8512CLRR-7

HM62V8512CLRR-5SL

HM62V8512CLRR-7SL

55 ns

70 ns

55 ns

70 ns

55 ns

70 ns

55 ns

70 ns

55 ns

70 ns

55 ns

70 ns

525-mil 32-pin plastic SOP (FP-32D)

400-mil 32-pin plastic TSOP II (TTP-32D)

400-mil 32-pin plastic TSOP II reverse (TTP-32DR)

2

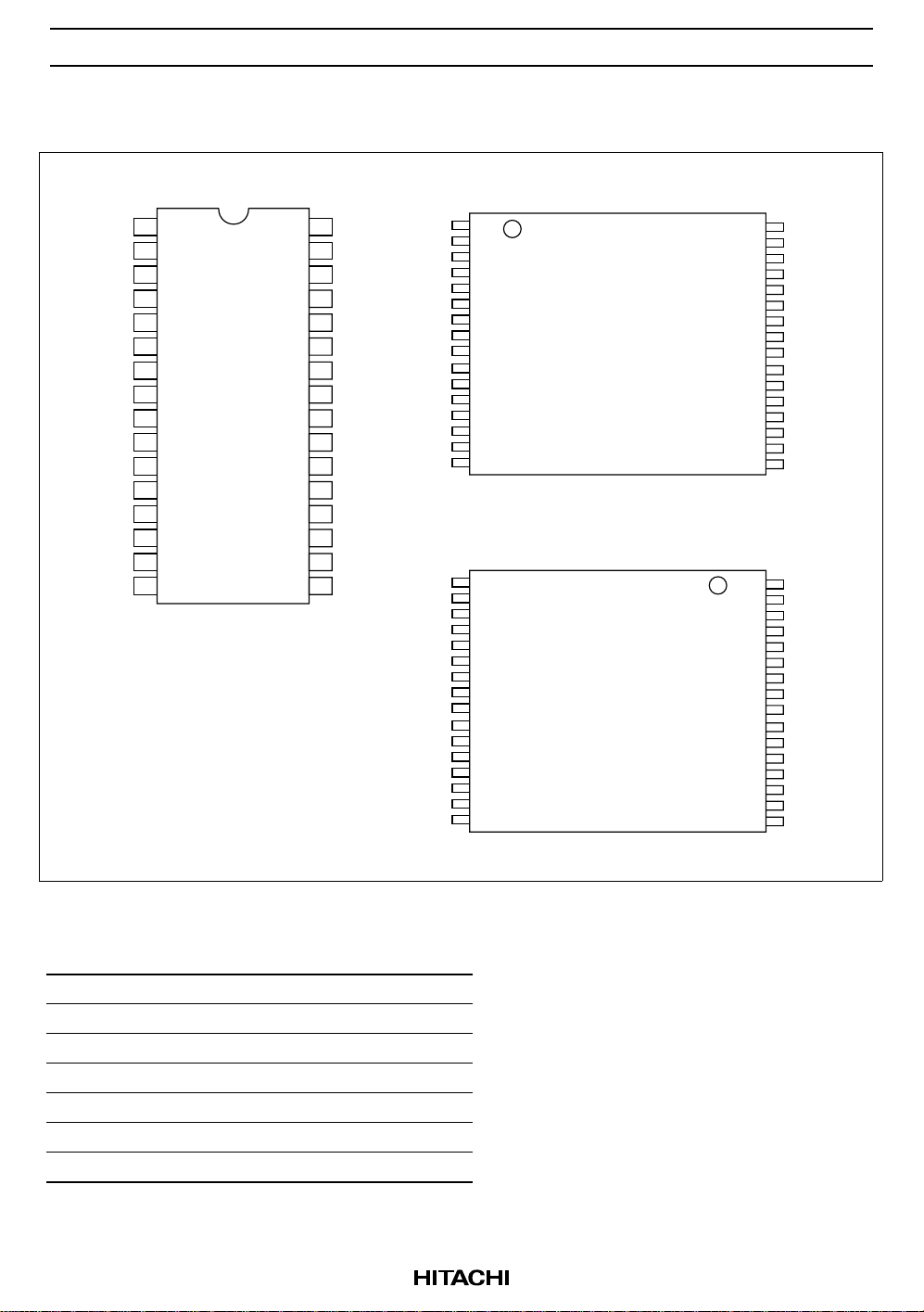

Pin Arrangement

32-pin SOP 32-pin TSOP

HM62V8512C Series

A18

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O0

I/O1

I/O2

V

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

(Top view)

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

V

CC

A15

A17

WE

A13

A8

A9

A11

OE

A10

CS

I/O7

I/O6

I/O5

I/O4

I/O3

A18

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O0

I/O1

I/O2

V

SS

V

CC

A15

A17

WE

A13

A8

A9

A11

OE

A10

CS

I/O7

I/O6

I/O5

I/O4

I/O3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

(Top view)

32-pin TSOP (reverse)

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

V

CC

A15

A17

WE

A13

A8

A9

A11

OE

A10

CS

I/O7

I/O6

I/O5

I/O4

I/O3

A18

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O0

I/O1

I/O2

V

SS

Pin Description

Pin name Function

A0 to A18 Address input

I/O0 to I/O7 Data input/output

CS Chip select

OE Output enable

WE Write enable

V

CC

V

SS

Power supply

Ground

(Top view)

3

HM62V8512C Series

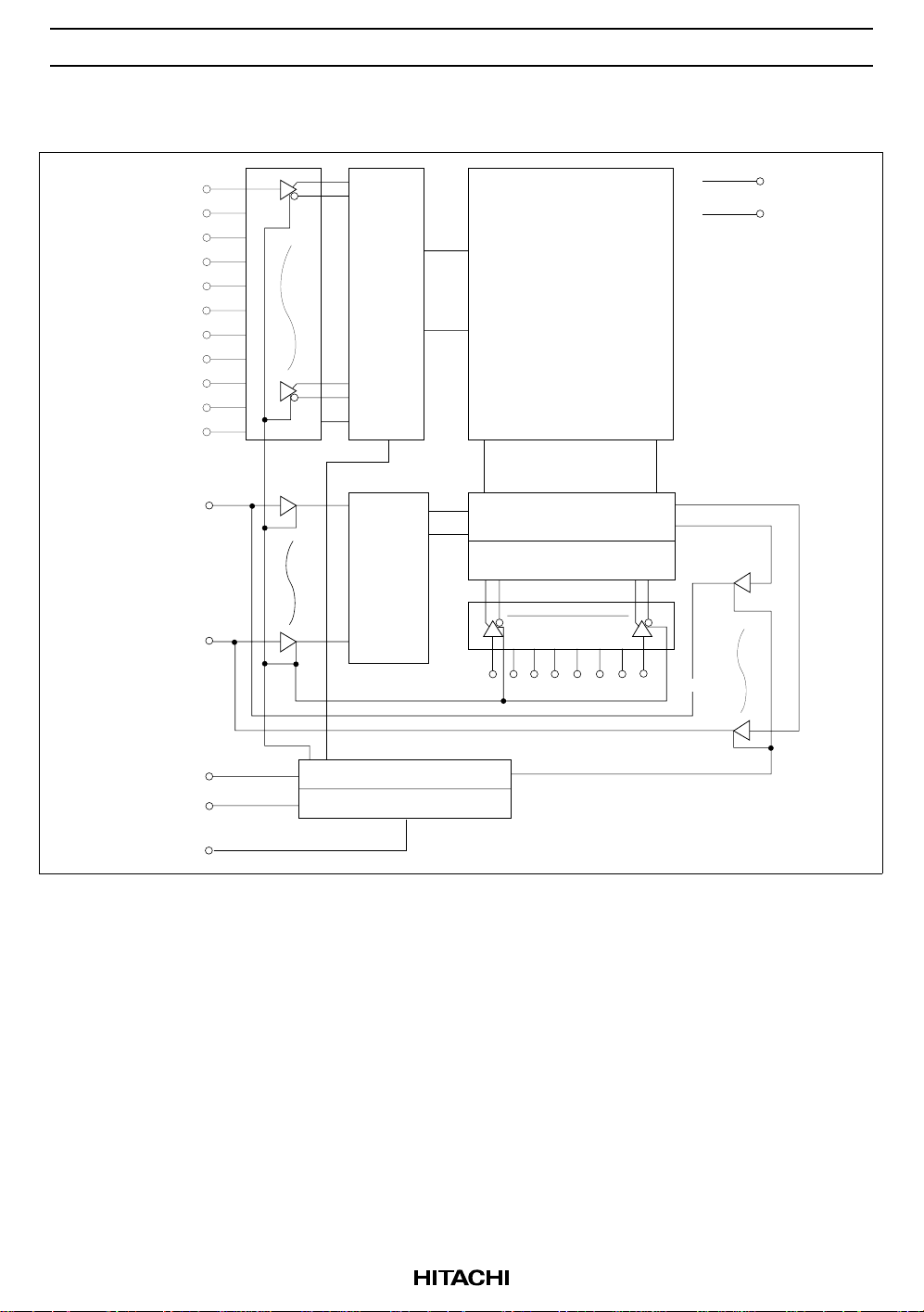

Block Diagram

LSB

MSB

A11

A9

A8

A15

A18

A10

A13

A17

A16

A14

A12

I/O0

I/O7

Row

Decoder

Input

Data

Control

•

•

•

•

•

•

•

LSB

Memory Matrix

2,048 2,048

Column Decoder

A3A2A1A0 A6A5

•

•

×

Column I/O

A4 A7

MSB

V

CC

V

SS

•

•

CS

WE

OE

4

Timing Pulse Generator

Read/Write Control

HM62V8512C Series

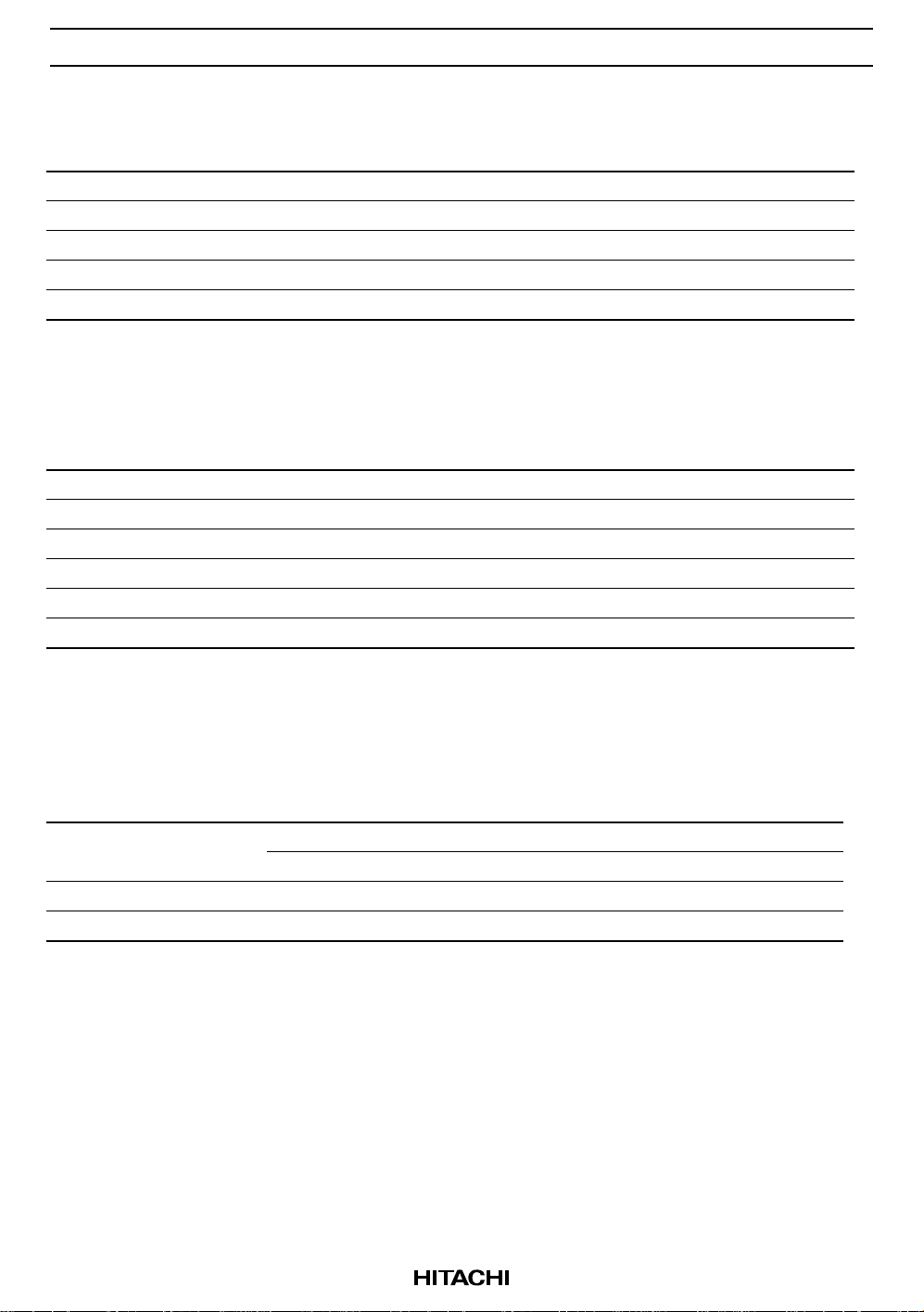

Function Table

WE CS OE Mode VCC current Dout pin Ref. cycle

× H × Not selected I

H L H Output disable I

H L L Read I

L L H Write I

L L L Write I

, I

SB

SB1

CC

CC

CC

CC

Note: ×: H or L

Absolute Maximum Ratings

Parameter Symbol Value Unit

Power supply voltage V

Voltage on any pin relative to V

SS

Power dissipation P

CC

V

T

T

Operating temperature Topr –20 to +70 °C

Storage temperature Tstg –55 to +125 °C

Storage temperature under bias Tbias –20 to +85 °C

Notes: 1. VT min: –3.0 V for pulse half-width ≤ 30 ns.

2. Maximum voltage is 4.6 V.

–0.5 to +4.6 V

–0.5*1 to VCC + 0.5*

1.0 W

High-Z —

High-Z —

Dout Read cycle

Din Write cycle (1)

Din Write cycle (2)

2

V

Recommended DC Operating Conditions (Ta = –20 to +70°C)

Parameter Symbol Min Typ Max Unit

Supply voltage V

Input high voltage V

Input low voltage V

CC

V

SS

IH

IL

Note: 1. VIL min: –3.0 V for pulse half-width ≤ 30 ns.

2.7 3.0 3.6 V

000V

2.0 — VCC + 0.3 V

1

–0.3*

— 0.8 V

5

Loading...

Loading...