HIT HM628511HJP-10, HM628511HJP-12, HM628511HJP-15, HM628511HLJP-10, HM628511HLJP-12 Datasheet

...

HM628511H Series

4M High Speed SRAM (512-kword × 8-bit)

ADE-203-762D (Z)

Rev. 1.0

Sep. 15, 1998

Description

The HM628511H Series is a 4-Mbit high speed static RAM organized 512-k word × 8-bit. It has realized

high speed access time by employing CMOS process (4-transistor + 2-poly resistor memory cell)and high

speed circuit designing technology. It is most appropriate for the application which requires high speed, high

density memory and wide bit width configuration, such as cache and buffer memory in system. It is packaged

in 400-mil 36-pin plastic SOJ.

Features

• Single 5.0 V supply : 5.0 V ± 10 %

• Access time 10 /12 /15 ns (max)

• Completely static memory

No clock or timing strobe required

• Equal access and cycle times

• Directly TTL compatible

All inputs and outputs

• Operating current : 180 / 160 / 140 mA (max)

• TTL standby current : 70 / 60 / 50 mA (max)

• CMOS standby current : 5 mA (max)

: 1.2 mA (max) (L-version)

• Data retension current: 0.8 mA (max) (L-version)

• Data retension voltage: 2 V (min) (L-version)

• Center VCC and VSS type pinout

HM628511H Series

Ordering Information

Type No. Access time Package

HM628511HJP-10

HM628511HJP-12

HM628511HJP-15

HM628511HLJP-10

HM628511HLJP-12

HM628511HLJP-15

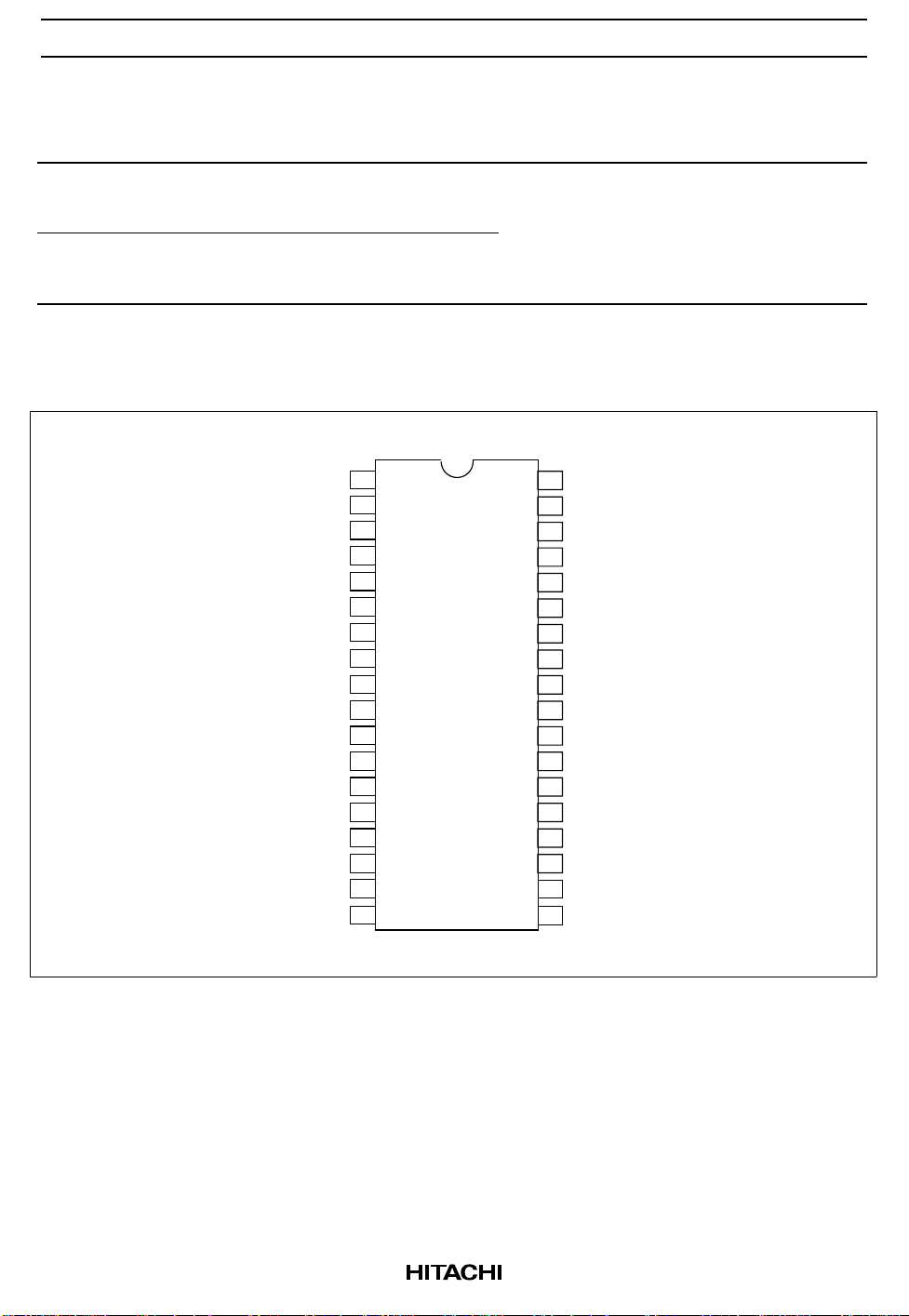

Pin Arrangement

10 ns

12 ns

15 ns

10 ns

12 ns

15 ns

400-mil 36-pin plastic SOJ (CP-36D)

HM628511HJP/HLJP Series

A0

A1

A2

A3

A4

CS

I/O1

I/O2

V

CC

V

SS

I/O3

I/O4

WE

A5

A6

A7

A8

A9

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

(T op Vie w)

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

NC

A18

A17

A16

A15

OE

I/O8

I/O7

V

SS

V

CC

I/O6

I/O5

A14

A13

A12

A11

A10

NC

2

Pin Description

Pin name Function

A0 to A18 Address input

I/O1 to I/O8 Data input/output

CS Chip select

OE Output enable

WE Write enable

V

CC

V

SS

Power supply

Ground

NC No connection

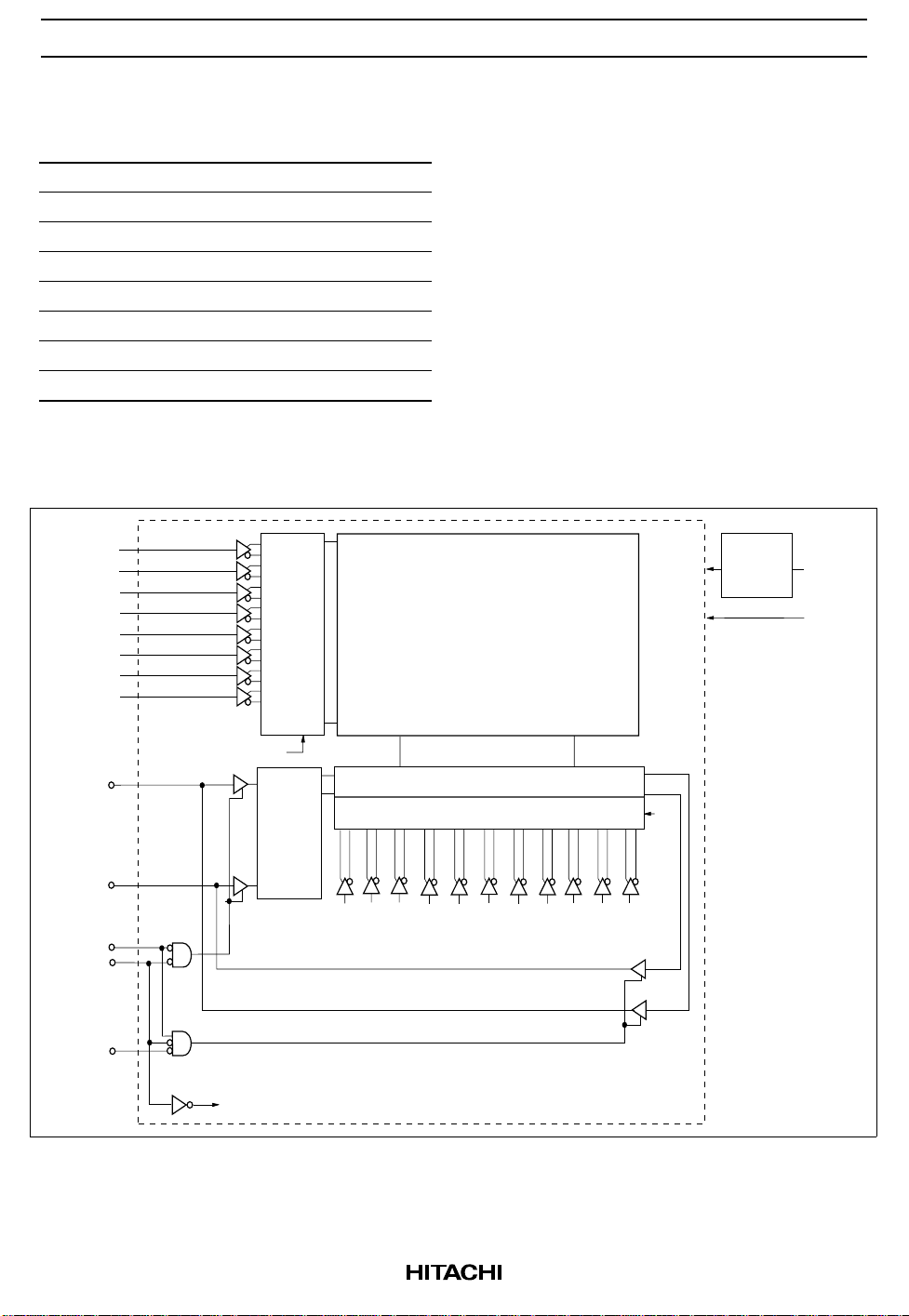

Block Diagram

HM628511H Series

(LSB)

A1

A17

A7

A11

A16

A2

A6

A5

(MSB)

I/O1

.

.

.

I/O8

WE

CS

OE

Row

decoder

CS

Input

data

control

Memory matrix

256 rows × 8 columns ×

256 blocks × 8 bit

(4,194,304 bits)

Column I/O

Column decoder

A10 A8 A9 A12 A13 A14 A0 A18 A15 A3 A4

(LSB)

(MSB)

CS

Internal

voltage

generater

V

CC

V

SS

CS

3

HM628511H Series

Operation Table

CS OE WE Mode VCC current I/O Ref. cycle

H ××Standby I

L H H Output disable I

L L H Read I

L H L Write I

L L L Write I

, I

SB

SB1

CC

CC

CC

CC

Note: ×: H or L

Absolute Maximum Ratings

Parameter Symbol Value Unit

Supply voltage relative to V

Voltage on any pin relative to V

SS

SS

Power dissipation P

Operating temperature Topr 0 to +70 °C

Storage temperature Tstg –55 to +125 °C

Storage temperature under bias Tbias –10 to +85 °C

Notes: 1. VT (min) = –2.0 V for pulse width (under shoot) ≤ 8 ns

2. V

(max) = VCC+2.0 V for pulse width (over shoot) ≤ 8 ns

T

V

CC

V

T

T

High-Z —

High-Z —

Dout Read cycle (1) to (3)

Din Write cycle (1)

Din Write cycle (2)

–0.5 to +7.0 V

–0.5*1 to VCC+0.5*

2

V

1.0 W

Recommended DC Operating Conditions (Ta = 0 to +70°C)

Parameter Symbol Min Typ Max Unit

3

Supply voltage V

Input voltage V

CC

VSS*

IH

V

IL

*

4

Notes: 1. VIL (min) = –2.0 V for pulse width (under shoot) ≤ 8 ns

2. V

(max) = VCC+2.0 V for pulse width (over shoot) ≤ 8 ns

IH

3. The supply voltage with all V

4. The supply voltage with all V

4

4.5 5.0 5.5 V

000V

2.2 — VCC + 0.5*

1

–0.5*

pins must be on the same level.

CC

pins must be on the same level.

SS

— 0.8 V

2

V

Loading...

Loading...