HIT HM6264BLFPI-10T, HM6264BLFPI-12T, HM6264BLPI-10, HM6264BLPI-12 Datasheet

HM6264BI Series

64k SRAM (8-kword × 8-bit)

Wide Temperature Range version

ADE-203-492C (Z)

Rev. 3.0

May. 8, 2000

Description

The Hitachi HM6264BI is 64k-bit static RAM organized 8-kword × 8-bit. It realizes higher performance and

low power consumption by 1.5 µm CMOS process technology. The device, packaged in 450 mil SOP (foot

print pitch width), 600 mil plastic DIP, is available for high density mounting.

Features

• Single 5 V supply: 5 V ± 10%

• Access time: 100/120 ns (max)

• Power dissipation:

Standby: 10 µW (typ)

Operation: 15 mW (typ) (f = 1 MHz)

• Completely static memory

No clock or timing strobe required

• Equal access and cycle times

• Common data input and output

Three state output

• Directly TTL compatible

All inputs and outputs

• Battery backup operation capability

• Operating temperature range: –40˚C to +85˚C

HM6264BI Series

Ordering Information

Type No. Access time Package

HM6264BLPI-10

HM6264BLPI-12

HM6264BLFPI-10T

HM6264BLFPI-12T

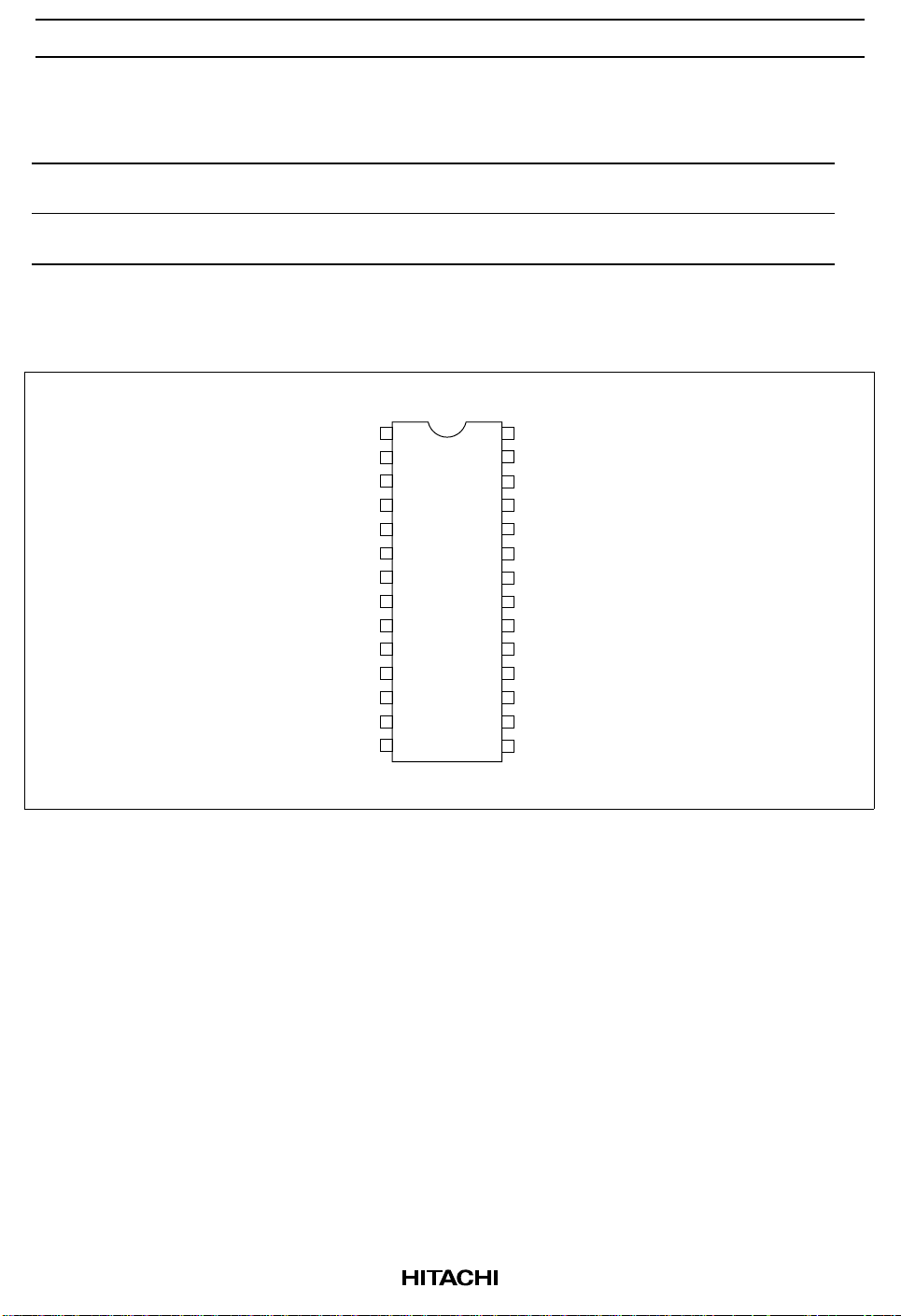

Pin Arrangement

100 ns

120 ns

100 ns

120 ns

600-mil, 28-pin plastic DIP (DP-28)

450-mil, 28-pin plastic SOP(FP-28DA)

HM6264BLPI/BLFPI Series

1

NC

A12

A7

A6

A4

A0

I/O1

I/O2

I/O3

V

SS

2

3

4

5A5

6

7A3

8A2

9A1

10

11

12

13

14

28

27

24

23

22

21

20

19

18

V

CC

WE

CS226

A825

A9

A11

OE

A10

CS1

I/O8

I/O7

I/O617

I/O516

I/O415

(Top view)

2

Pin Description

Pin name Function

A0 to A12 Address input

I/O1 to I/O8 Data input/output

CS1 Chip select 1

CS2 Chip select 2

WE Write enable

OE Output enable

NC No connection

V

CC

V

SS

Power supply

Ground

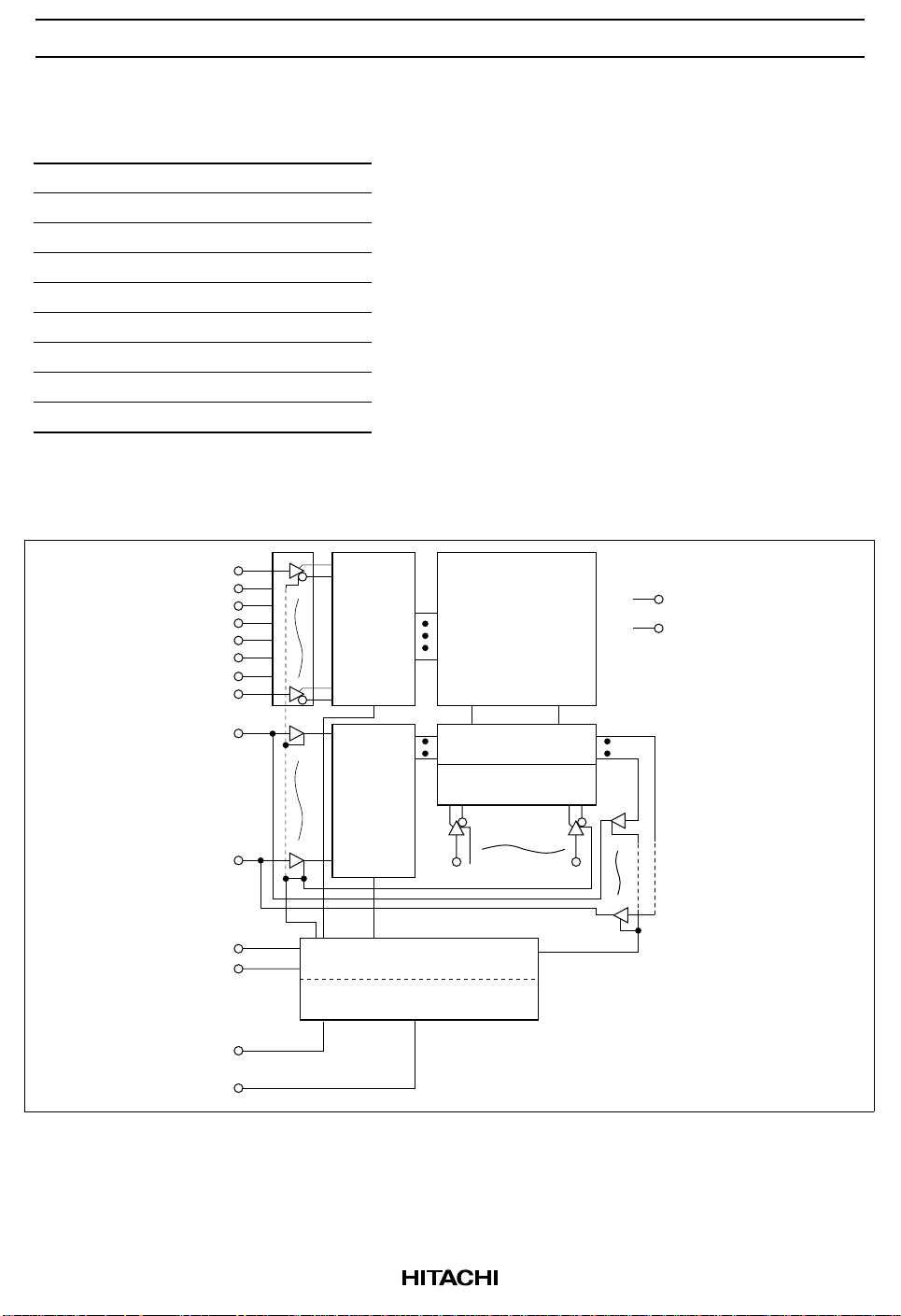

Block Diagram

A11

A8

A9

A7

A12

A5

A6

A4

Row

decoder

Memory array

256 × 256

HM6264BI Series

V

CC

V

SS

I/O1

I/O8

CS2

CS1

WE

OE

Column I/O

Input

data

Column decoder

control

A1 A3

A2 A0 A10

Timing pulse generator

Read, Write control

3

HM6264BI Series

Function Table

WE CS1 CS2 OE Mode VCC current I/O pin Ref. cycle

× H ××Not selected (power down) I

××L × Not selected (power down) ISB, I

H L H H Output disable I

H L H L Read I

L L H H Write I

L L H L Write I

, I

SB

SB1

SB1

CC

CC

CC

CC

Note: ×: H or L

Absolute Maximum Ratings

Parameter Symbol Value Unit

Power supply voltage*

Terminal voltage*

1

1

Power dissipation P

Operating temperature Topr –40 to +85 °C

Storage temperature Tstg –55 to +125 °C

Storage temperature under bias Tbias –40 to +85 °C

Notes: 1. Relative to V

SS

2. VT min: –3.0 V for pulse half-width ≤ 50 ns

3. Maximum voltage is 7.0 V

V

CC

V

T

T

–0.5 to +7.0 V

–0.5*2 to VCC + 0.3*3V

1.0 W

High-Z —

High-Z —

High-Z —

Dout Read cycle (1)–(3)

Din Write cycle (1)

Din Write cycle (2)

Recommended DC Operating Conditions (Ta = –40 to +85°C)

Parameter Symbol Min Typ Max Unit

Supply voltage V

Input high voltage V

Input low voltage V

CC

V

SS

IH

IL

Note: 1. VIL min: –3.0 V for pulse half-width ≤ 50 ns

4

4.5 5.0 5.5 V

000V

2.4 — VCC + 0.3 V

1

–0.3*

— 0.6 V

HM6264BI Series

DC Characteristics (Ta = –40 to +85°C, VCC = 5 V ±10%, VSS = 0 V)

Parameter Symbol Min Typ*1Max Unit Test conditions

Input leakage current |I

Output leakage current |ILO| ——2 µA CS1 = VIH or CS2 = VIL or OE = VIH or

Operating power supply

current

Average operating power

supply current

Standby power supply

current

Output low voltage V

Output high voltage V

Notes: 1. Typical values are at VCC = 5.0 V, Ta = +25°C and not guaranteed.

2. V

min = –0.3V

IL

| ——2 µA Vin = VSS to V

LI

WE = V

I

CCDC

— 7 20 mA CS1 = VIL, CS2 = VIH, I

others = V

I

CC1

— 30 50 mA Min cycle, duty = 100%,

CS1 = V

others = V

I

CC2

— 3 8 mA Cycle time = 1 µs, duty = 100%, I

CS1 ≤ 0.2 V, CS2 ≥ V

V

≥ VCC – 0.2 V, VIL ≤ 0.2 V

IH

I

SB

I

SB1

—13mACS1 = VIH, CS2 = V

2

*

— 2 200 µA CS1 ≥ VCC – 0.2 V, CS2 ≥ VCC – 0.2 V or

0 V ≤ CS2 ≤ 0.2 V, 0 V ≤ Vin

OL

OH

— — 0.4 V IOL = 2.1 mA

2.4 — — V IOH = –1.0 mA

CC

, V

= V

IL

I/O

IH/VIL

, CS2 = VIH, I

IL

IH/VIL

SS

to V

CC

IL

CC

= 0 mA

I/O

= 0 mA

I/O

– 0.2 V,

= 0 mA

I/O

Capacitance (Ta = 25°C, f = 1.0 MHz)

Parameter Symbol Min Typ Max Unit Test conditions

Input capacitance*

Input/output capacitance*

1

1

Note: 1. This parameter is sampled and not 100% tested.

Cin — — 5 pF Vin = 0 V

C

I/O

——7 pFV

= 0 V

I/O

5

HM6264BI Series

AC Characteristics (Ta = –40 to +85°C, VCC = 5 V ± 10%, unless otherwise noted.)

Test Conditions

• Input pulse levels: 0.6 V to 2.4 V

• Input and output timing reference level: 1.5 V

• Input rise and fall time: 10 ns

• Output load: 1 TTL Gate + CL (100 pF) (Including scope & jig)

Read Cycle

HM6264BI-10 HM6264BI-12

Parameter Symbol Min Max Min Max Unit Notes

Read cycle time t

Address access time t

Chip select access time CS1 t

CS2 t

Output enable to output valid t

Chip selection to output in low-Z CS1 t

CS2 t

Output enable to output in low-Z t

Chip deselection in to output in high-Z CS1 t

CS2 t

Output disable to output in high-Z t

Output hold from address change t

RC

AA

CO1

CO2

OE

LZ1

LZ2

OLZ

HZ1

HZ2

OHZ

OH

Notes: 1. tHZ is defined as the time at which the outputs achieve the open circuit conditions and are not

referred to output voltage levels.

2. At any given temperature and voltage condition, t

given device and from device to device.

3. Address must be valid prior to or simultaneously with CS1 going low or CS2 going high.

100 — 120 — ns

— 100 — 120 ns

— 100 — 120 ns

— 100 — 120 ns

— 50 — 60 ns

10 — 10 — ns 2

10 — 10 — ns 2

5—5—ns2

0 35 0 40 ns 1, 2

0 35 0 40 ns 1, 2

0 35 0 40 ns 1, 2

10 — 10 — ns

maximum is less than tLZ minimum both for a

HZ

6

Loading...

Loading...