HIT HM5212325FBP-B60 Datasheet

HM5212325F-B60

128M LVTTL interface SDRAM

100 MHz

1-Mword × 32-bit × 4-bank

PC/100 SDRAM

ADE-203-1053A (Z)

Rev. 1.0

Oct. 18, 1999

Description

The Hitachi HM5212325F is a 128-Mbit SDRAM organized as 1048576-word × 32-bit × 4-bank. All inputs

and outputs are referred to the rising edge of the clock input. It is packaged in standard 108 bump BGA.

Features

• Single chip wide bit solution (× 32)

• 3.3 V power supply

• Clock frequency: 100 MHz (max)

• LVTTL interface

• Extremely small foot print: 1.27 mm pitch

Package: BGA (BP-108)

• 4 banks can operate simultaneously and independently

• Burst read/write operation and burst read/single write operation capability

• Programmable burst length: 4/8/full page

• 2 variations of burst sequence

Sequential (BL = 4/8/full page)

Interleave (BL = 4/8)

• Programmable CAS latency: 2/3

• Byte control by DQMB

• Refresh cycles: 4096 refresh cycles/64 ms

• 2 variations of refresh

Auto refresh

Self refresh

HM5212325F-B60

2

• Full page burst length capability

Sequential burst

Burst stop capability

Ordering Information

Type No. Frequency CAS latency Package

HM5212325FBP-B60* 100 MHz 3 14 mm × 22 mm 108 bump BGA (BP-108)

Note: 66 MHz operation at CAS latency = 2.

HM5212325F-B60

3

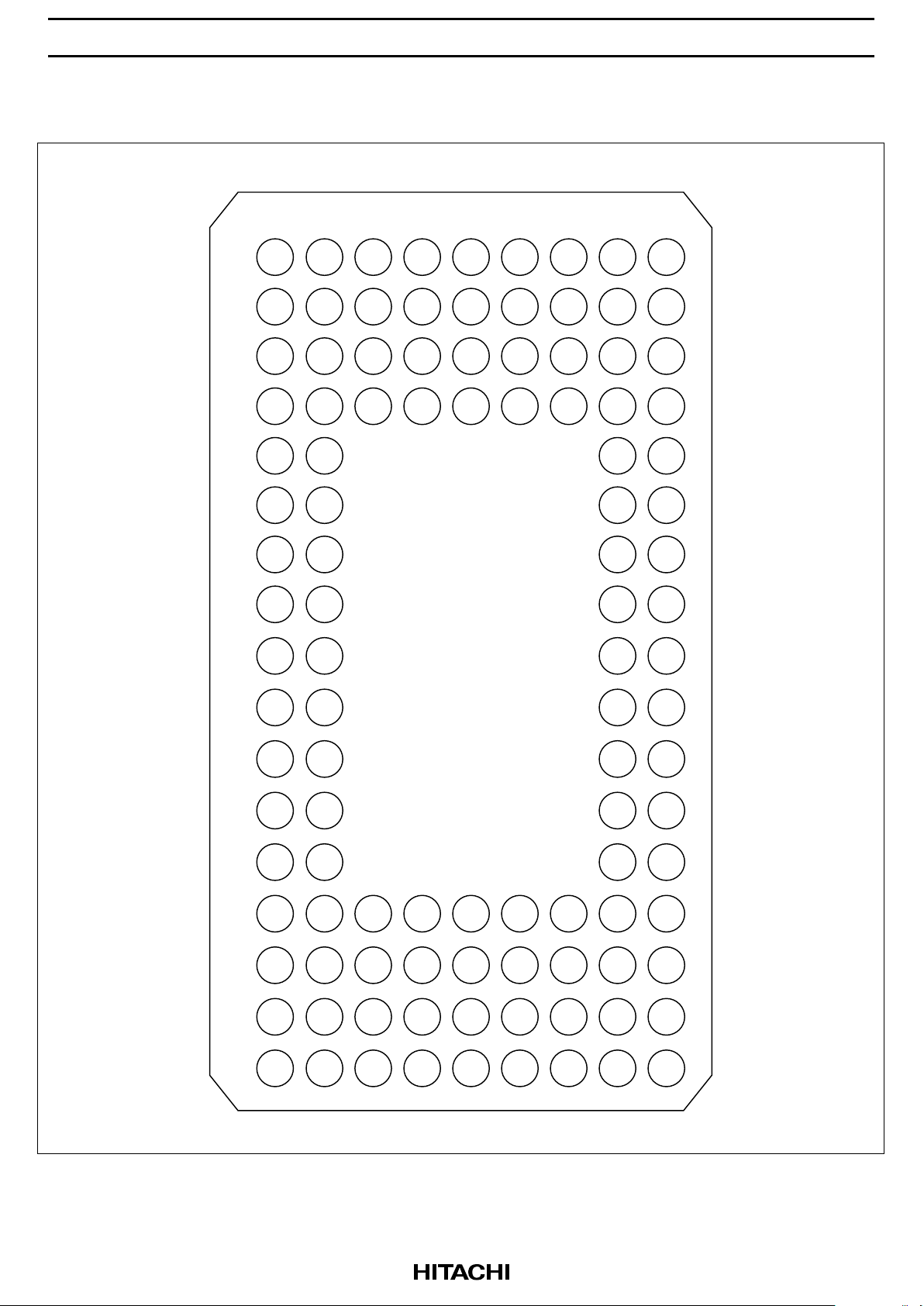

Pin Arrangement

(Top view)

108-bump BGA

A

B

C

D

E

F

G

H

J

K

L

M

N

R

T

P

U

1 2 3 4 5 6 7 8 9

DQ31

DQ30

DQ29

DQ28

DQ

MB3

CKE

A12

NC

NC

NC

NC

NC

V

CC

V

CC

A5

NC

NC

NC

NC DQ24

DQ25

DQ26

DQ27

DQ23

DQ22

DQ21

DQ20

NC

NC

NC

NC

NC

NC

NC

NC

NC

V

CC

DQ16

DQ17

DQ18

DQ19

WE

A13

A1

A7

V

SS

A2

A10

RAS

DQ

MB2

A3

A4

A6

V

SS

A0

A8

A11

V

SS

A9 CS

Open CLK V

CC

CAS

DQ

MB0

DQ

MB1

DQ3 NC NC DQ4 V

SS

DQ11 NC NC DQ12

DQ2 NC NC DQ5 V

CC

DQ10 NC NC DQ13

DQ1 NC NC DQ6 V

CC

DQ9 NC NC DQ14

DQ0 NC NC DQ7 V

SS

V

SS

V

CC

V

CC

V

SS

DQ8

NC NC DQ15

NC

NC

HM5212325F-B60

4

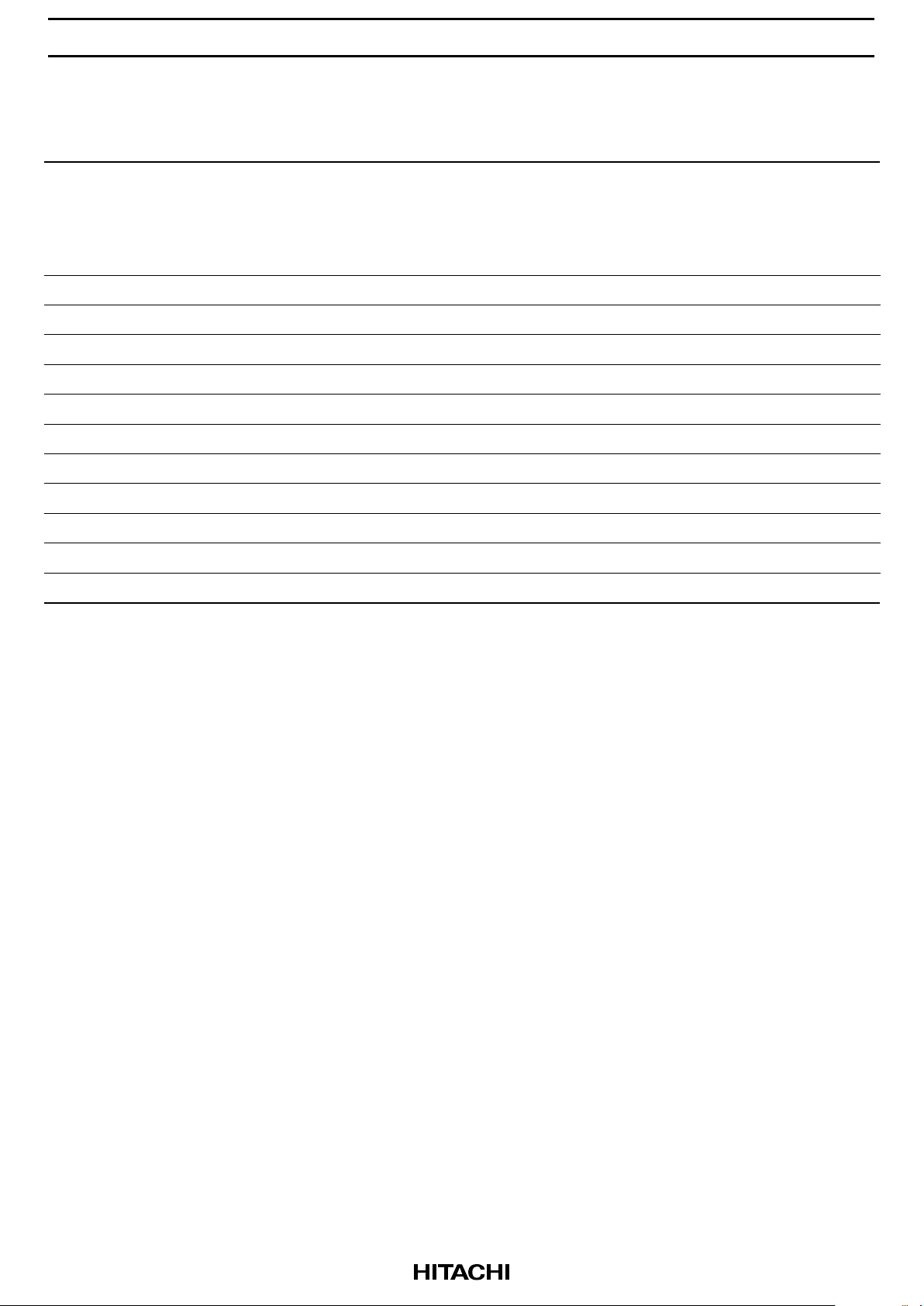

Pin Description

Pin name Function

A0 to A13 Address input

Row address A0 to A11

Column address A0 to A7

Bank select address A12/A13 (BS)

DQ0 to DQ31 Data-input/output

CS Chip select

RAS Row address strobe command

CAS Column address strobe command

WE Write enable

DQMB0 to DQMB3 Byte data mask*

1

CLK Clock input

CKE Clock enable

V

CC

Power supply

V

SS

Ground

Open Open*

2

Note: 1. DQMB0: DQ0 to DQ7

DQMB1: DQ8 to DQ15

DQMB2: DQ16 to DQ23

DQMB3: DQ24 to DQ31

2. Don’t connect. Internally connected with die.

Loading...

Loading...