HIT HD74LVC16374A Datasheet

HD74LVC16374A

16-bit D-type Flip Flops with 3-state Outputs

ADE-205-122B(Z)

3rd Edition

December 1996

Description

The HD74LVC16374A has sixteen edge trigger D type flip flops with three state outputs in a 48 pin

package. Data at the D inputs meeting set up reguirements, are transferred to the Q outputs on positive

going transitions of the clock input. When the latch enable goes low, data at the D inputs will be retained

at the outputs until latch enable returns high again. When a high logic level is applied to the output control

input, all outputs go to a high impedance state, regardless of what signals are present at the other inputs

and the state of the storage elements. Low voltage and high speed operation is suitable at the battery drive

product (note type personal computer) and low power consumption extends the life of a battery for long

time operation.

Features

• VCC = 2.0 V to 5.5 V

• All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V)

• All outputs V

• Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C)

• Typical VOH undershoot > 2.0 V (@VCC = 3.3 V, Ta = 25°C)

• High output current ±24 mA (@VCC = 3.0 V to 5.5 V)

(Max.) = 5.5 V (@VCC = 0 V or output off state)

OUT

HD74LVC16374A

Function Table

Inputs

G CK D Output Q

HXXZ

L↑ LL

L↑HH

LLXQ

H: High level

L: Low level

X: Immaterial

Z: High impedance

↑: Low to high transition

Q

: Level of Q before the indicated steady input conditions were established.

0

0

2

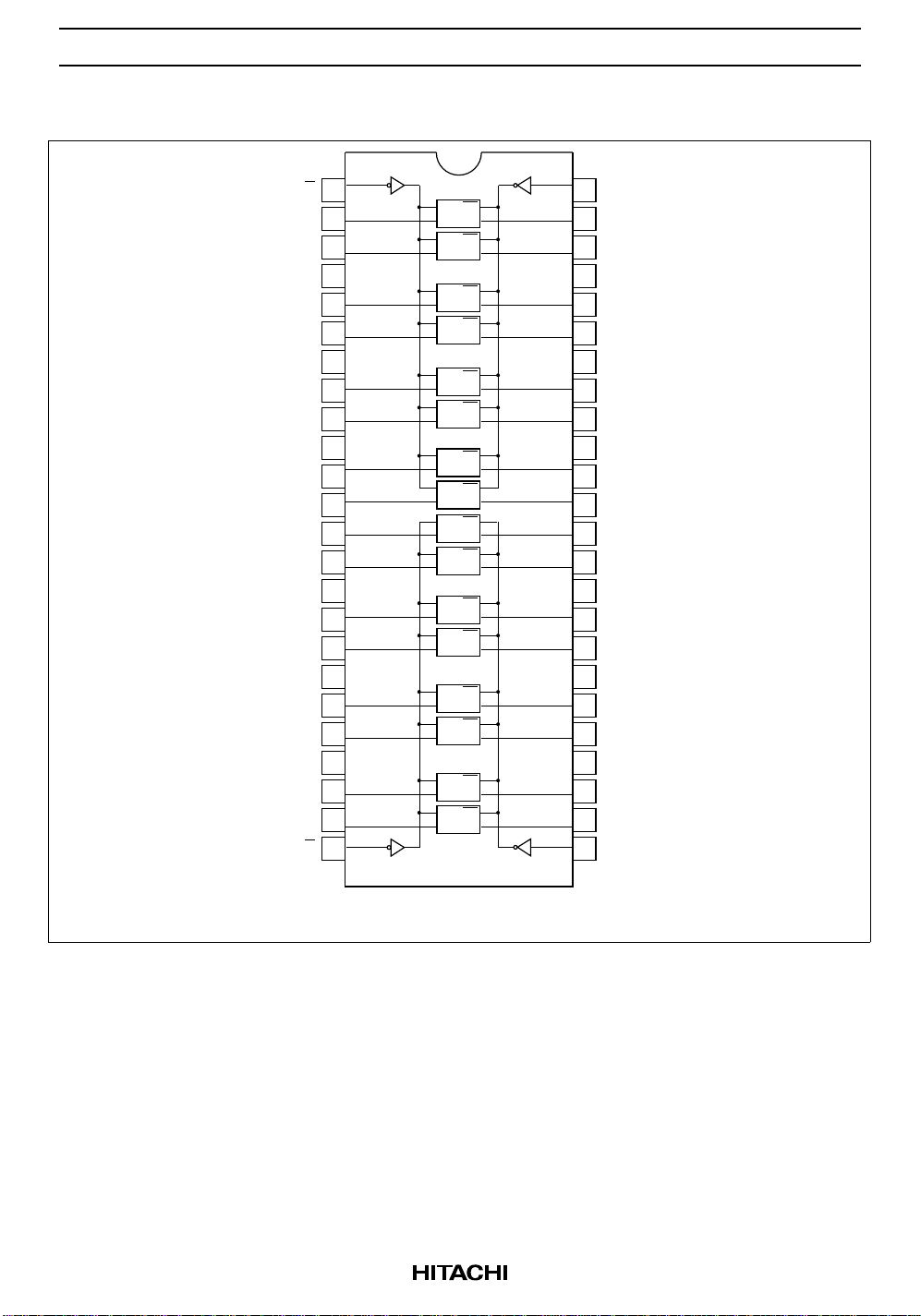

Pin Arrangement

1G

1Q1

1Q2

GND

1Q3

1Q4

V

CC

1Q5

1Q6

GND

1Q7

1Q8

2Q1

2Q2

GND

2Q3

2Q4

V

CC

2Q5

2Q6

GND

2Q7

2Q8

2G

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

HD74LVC16374A

1CK

1

2

3

4

5

6

7

8

9

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

G

CK

Q

D

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1D1

1D2

GND

1D3

1D4

V

CC

1D5

1D6

GND

1D7

1D8

2D1

2D2

GND

2D3

2D4

V

CC

2D5

2D6

GND

2D7

2D8

2CK

(Top view)

3

Loading...

Loading...