HIT HD74HC76 Datasheet

HD74HC76

Dual J-K Flip-Flops (with Preset and Clear)

Description

Each flip-flop has independent J, K, preset, clear, and clock inputs and Q and Q outputs. This device is

edge sensitive to the clock input and change state on the negative going transition of the clock pulse. Clear

and preset are independent of the clock and accomplished by a low logic level on the corresponding input.

Features

• High Speed Operation: tpd (Clock to Q) = 21 ns typ (CL = 50 pF)

• High Output Current: Fanout of 10 LSTTL Loads

• Wide Operating Voltage: VCC = 2 to 6 V

• Low Input Current: 1 µA max

• Low Quiescent Supply Current: ICC (static) = 2 µA max (Ta = 25°C)

Function Table

Inputs Outputs

Preset Clear Clock J K Q Q

LHXXXHL

HLXXXL H

LLXXXH*

HH L L No change

HH LHLH

HH HLHL

HH H H Toggle

H H L X X No change

H H H X X No change

HH X X No change

Note: 1. Q and Q will remain HIGH as long as Preset and Clear are Low, but Q and Q are unpredictable,

if Preset and Clear go HIGH simultaneously.

1

H*

1

HD74HC76

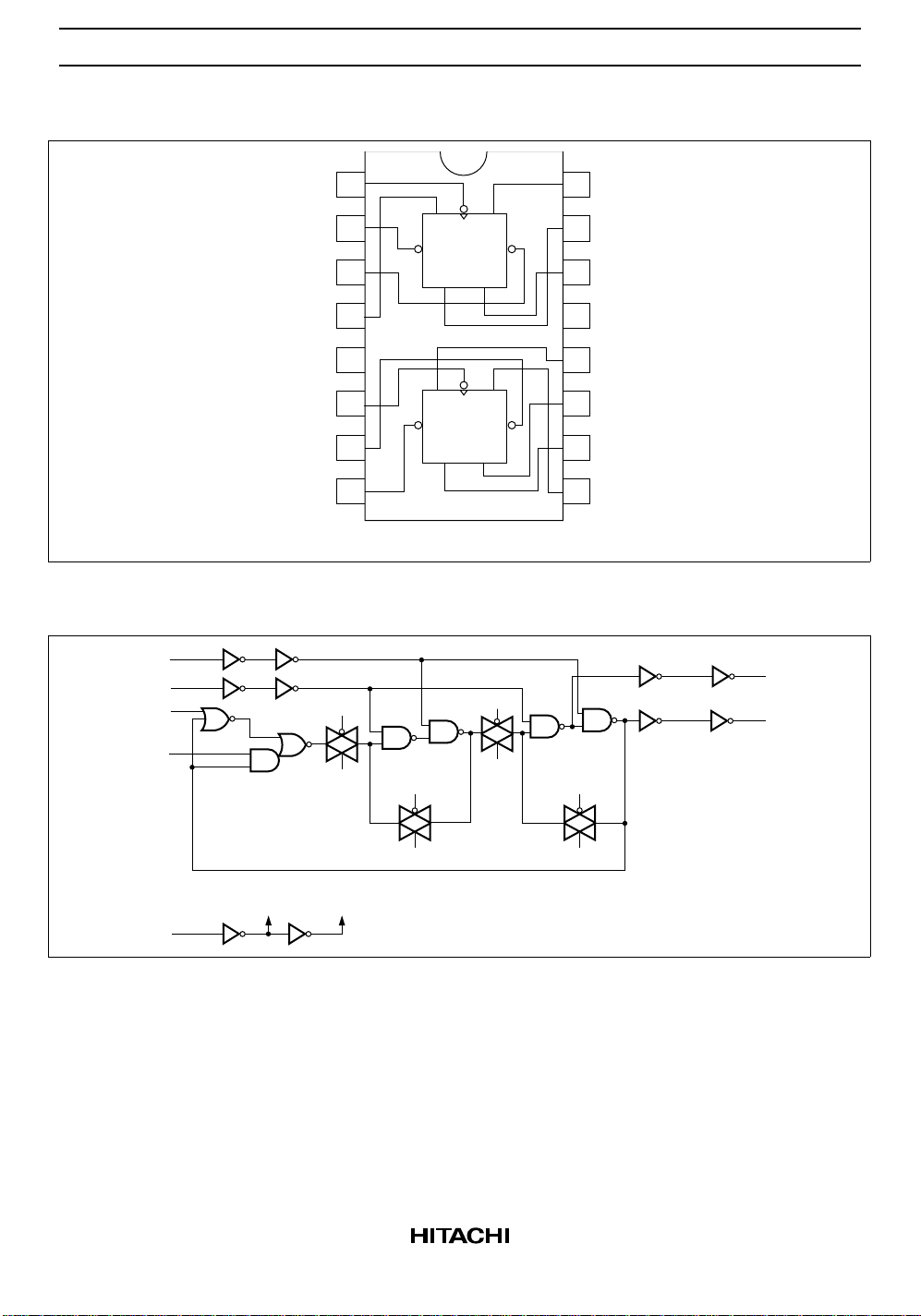

Pin Arrangement

1CK

1PR

1CLR

1J

V

CC

2CK

2PR

2CLR

16

15

14

13

12

11

10

1K

1Q

1Q

GND

2K

2Q

2Q

9

2J

1

JK

PR

Q Q

CK

CLR

2

3

4

5

KJ

CLR

Q Q

CK

PR

6

7

8

(Top view)

Block Diagram (1//2)

PR

CLR

J

K

#

CK

CK

Q

CK

CK

#

CK

CK

CK

#

CK

#

CK

#

Q

CK

CK

2

HD74HC76

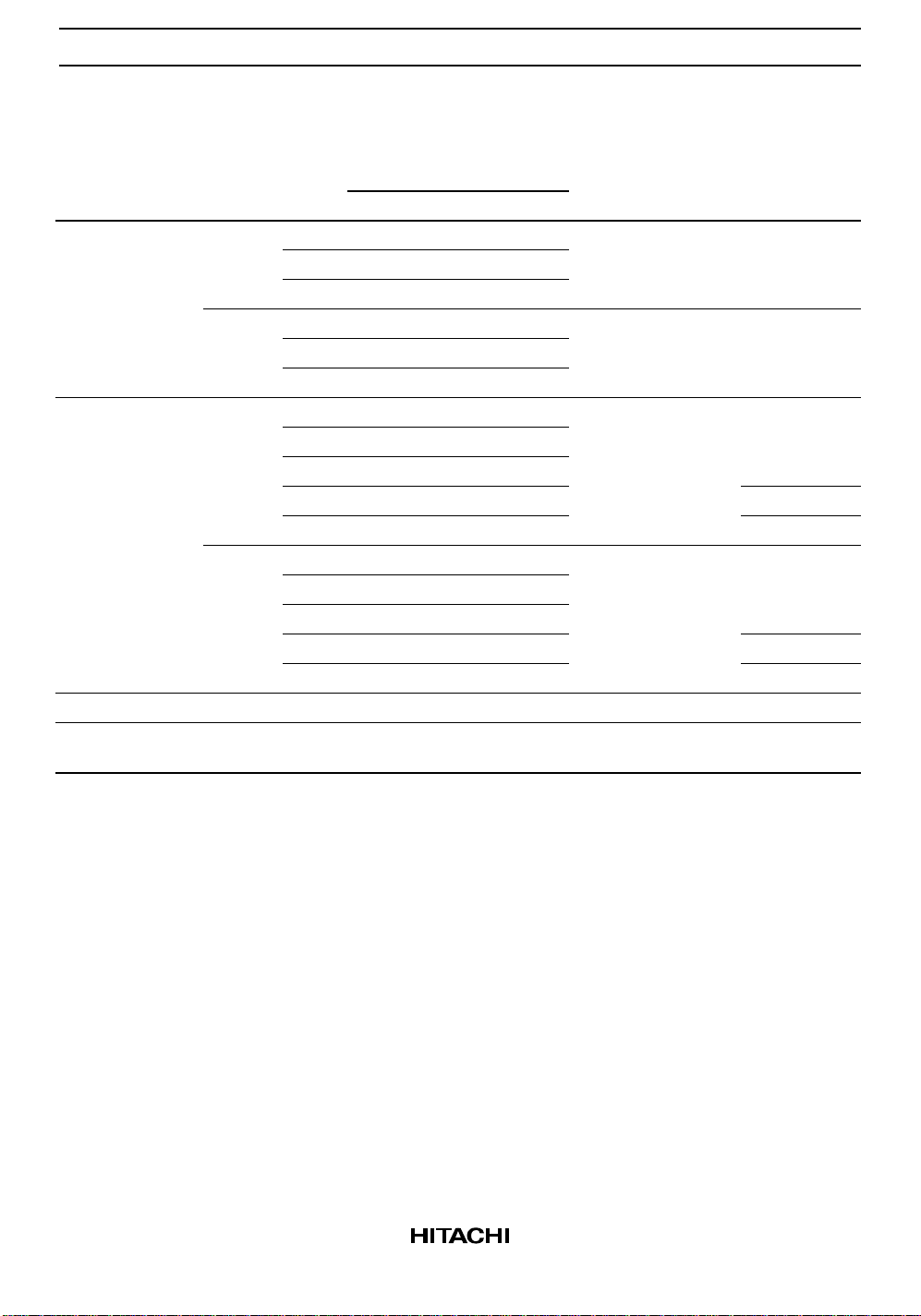

DC Characteristics

Ta = –40 to

Ta = 25°C

Item Symbol V

Input voltage V

IH

(V) Min Typ Max Min Max Unit Test Conditions

CC

2.0 1.5 — — 1.5 — V

4.5 3.15 — — 3.15 —

6.0 4.2 — — 4.2 —

V

IL

2.0 — — 0.5 — 0.5 V

4.5 — — 1.35 — 1.35

6.0 — — 1.8 — 1.8

Output voltage V

OH

2.0 1.9 2.0 — 1.9 — V Vin = VIH or VILIOH = –20 µA

4.5 4.4 4.5 — 4.4 —

6.0 5.9 6.0 — 5.9 —

4.5 4.18 — — 4.13 — IOH = –4 mA

6.0 5.68 — — 5.63 — IOH = –5.2 mA

V

OL

2.0 — 0.0 0.1 — 0.1 V Vin = VIH or VILIOL = 20 µA

4.5 — 0.0 0.1 — 0.1

6.0 — 0.0 0.1 — 0.1

4.5 — — 0.26 — 0.33 IOL = 4 mA

6.0 — — 0.26 — 0.33 IOL = 5.2 mA

Input current Iin 6.0 — — ±0.1 — ±1.0 µA Vin = VCC or GND

Quiescent supply

I

CC

6.0 — — 2.0 — 20 µA Vin = VCC or GND, Iout = 0 µA

current

+85°C

3

Loading...

Loading...