HIT HD74HC592 Datasheet

HD74HC592

8-bit Register/Binary Counter

Description

The HD74HC592 consists of a parallel input, 8-bit storage register feeding an 8-bit binary counter. Both

the register and the counter have individual positive edge-triggered clocks. In addition, the counter has

direct load and clear functions. Expansion is easily accomplished by connecting RCO of the first stage to

the count enable of the second stage, etc.

Features

• High Speed Operation: tpd (CCK to RCO) = 24 ns typ (CL = 50 pF)

• High Output Current: Fanout of 10 LSTTL Loads

• Wide Operating Voltage: VCC = 2 to 6 V

• Low Input Current: 1 µA max

• Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)

Function Table

Inputs

RCK CLoad CCLR CCKEN CCK Function

X L H X X Regiater data loaded into counter

X H L X X Counter clear

H H X X Input data A to H stored into register

H H X X No change in register

XHHL Count up

XHHL No count

X H H H X No cont

RCO = QA’•QB’•QC’•QD’•QE’•QF’•QG’•QH’• (CCKEN) (QA’ to QH’: Output of Internal Counter)

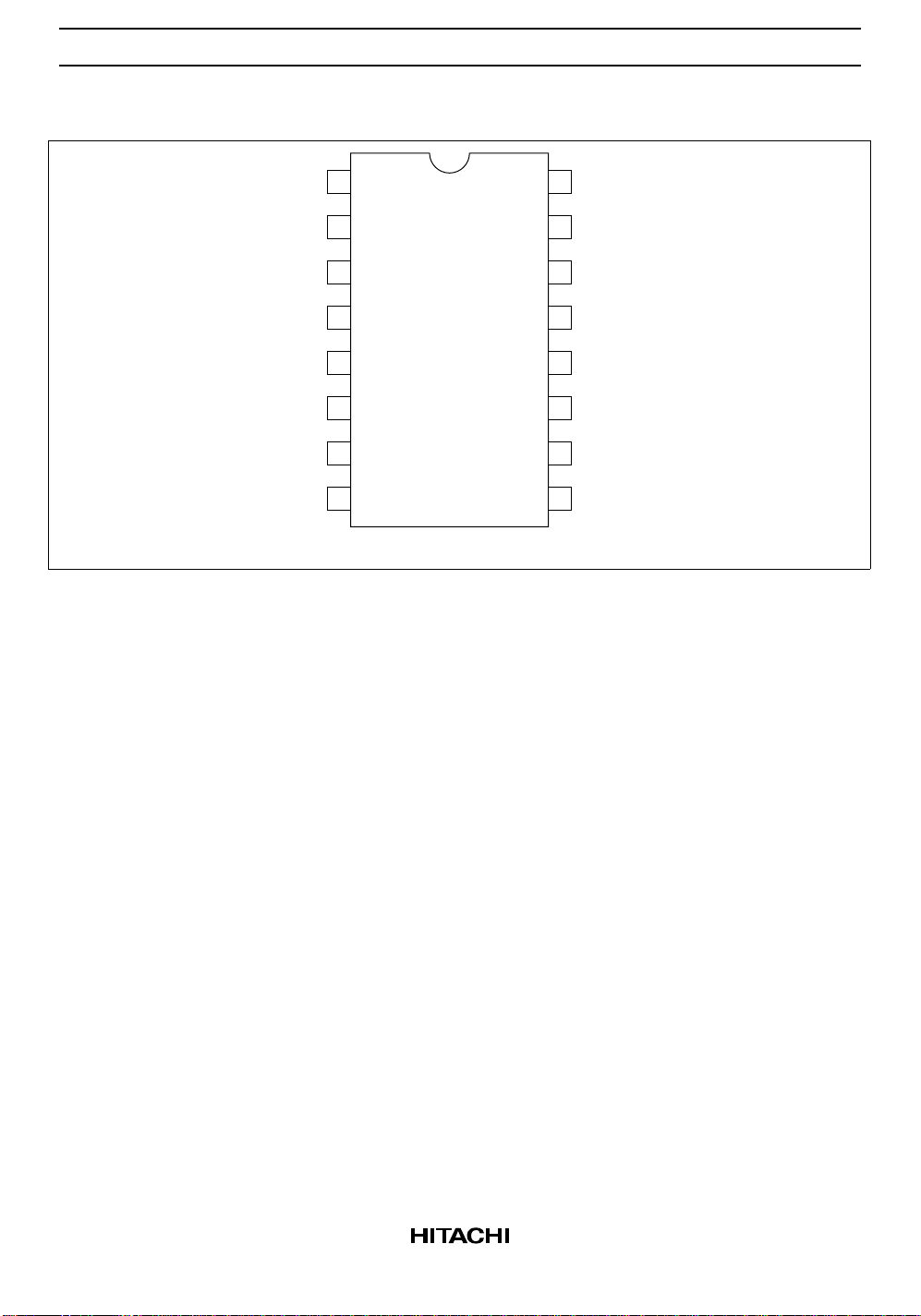

HD74HC592

Pin Arrangement

1

BV

2

C

3

D

4

E

F

5

G

6

7

H

89

GND

(Top view)

16

15

14

13

12

11

10

CC

A

C Load

RCK

CCKEN

CCK

CCLR

RCO

2

O

CCK

CCLR

CCKEN

CLOAD

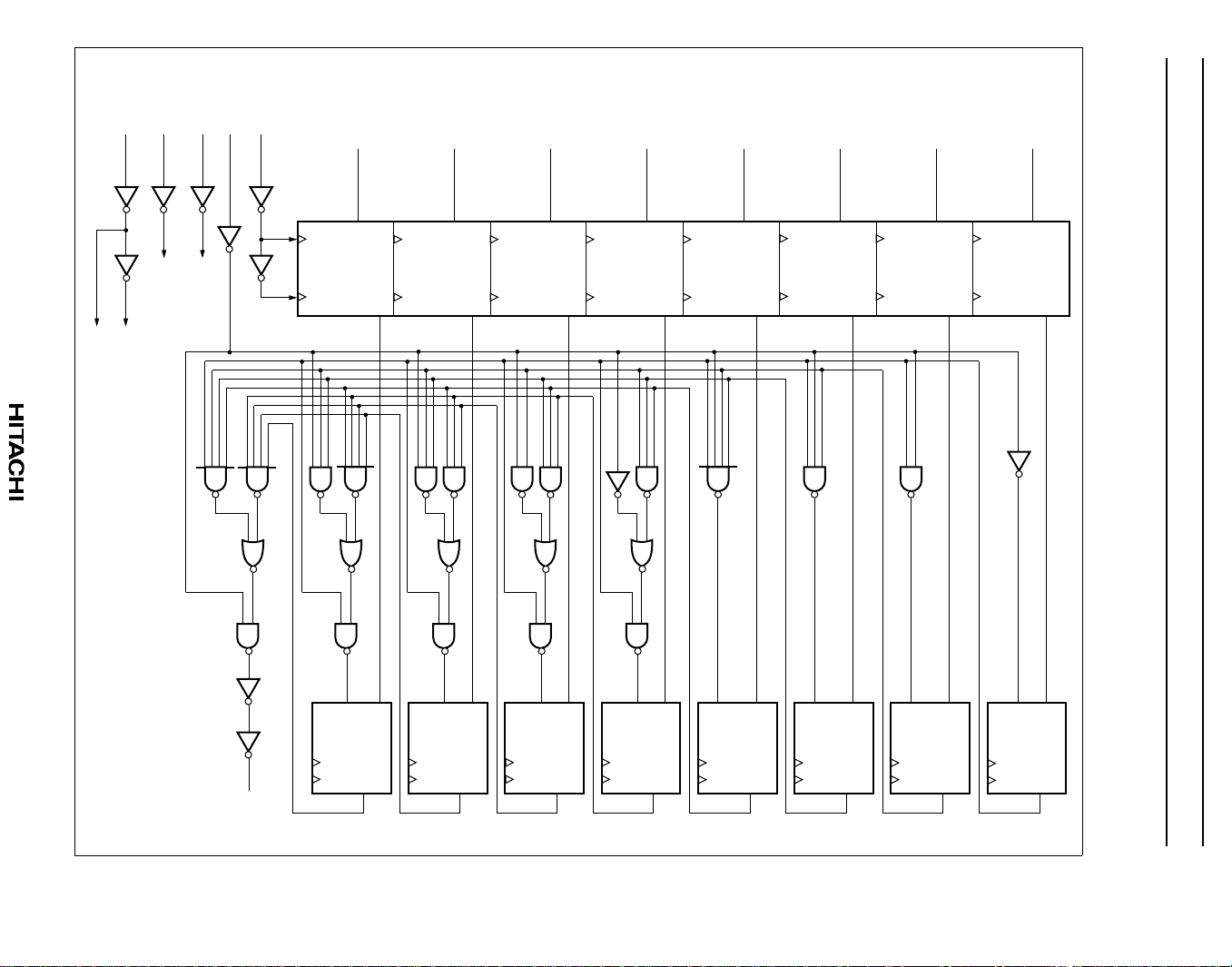

Logic Diagram

RCK

CCK

CCK

CLR

LD

RCK

RCK

RCK

RCK

G

D

F

D

RCK

RCK

E

D

RCK

RCK

H

D

D

D

RCK

RCK

RCK

RCK

C

D

B

D

RCK

RCK

A

D

RCK

RCK

D

LD

CLR

CCK

CCK

T

Q

T

LD

CLR

CCK

CCK

D

Q

T

LD

CLR

CCK

CCK

D

Q

T

LD

CLR

CCK

CCK

D

Q

T

LD

CLR

CCK

CCK

D

Q

HD74HC592

RC

LD

CLR

CCK

CCK

D

LD

CLR

CCK

CCK

T

Q

D

LD

CLR

CCK

CCK

T

Q

D

T

Q

Loading...

Loading...