HIT HD74HC373, HD74HC533 Datasheet

HD74HC373/HD74HC533

Octal D-type Transparent Latches (with 3-state outputs)

Octal D-type Transparent Latches (with inverted 3-state outputs)

Description

When the latch enable input is high, the Q outputs of HD74HC373 will follow the D inputs and the Q

outputs of HD74HC533 will follow the inversion of the D inputs. When the latch enable goes low, data at

the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is

applied to the output control input, all outputs go to a high impedance state, regardless of what signals are

present at the other inputs and the state of the storage elements.

Features

• High Speed Operation: tpd (D to Q) = 16 ns typ (CL = 50 pF)

• High Output Current: Fanout of 15 LSTTL Loads

• Wide Operating Voltage: VCC = 2 to 6 V

• Low Input Current: 1 µA max

• Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)

Function Table

Output Control Enable

GD

LH H H L

LH L L H

L L X No change No change

HX X Z Z

X : irrelevant

Z : Off (high-impedance) state of a 3-state output.

HD74HC373

Q

HD74HC533

Q

HD74HC373/HD74HC533

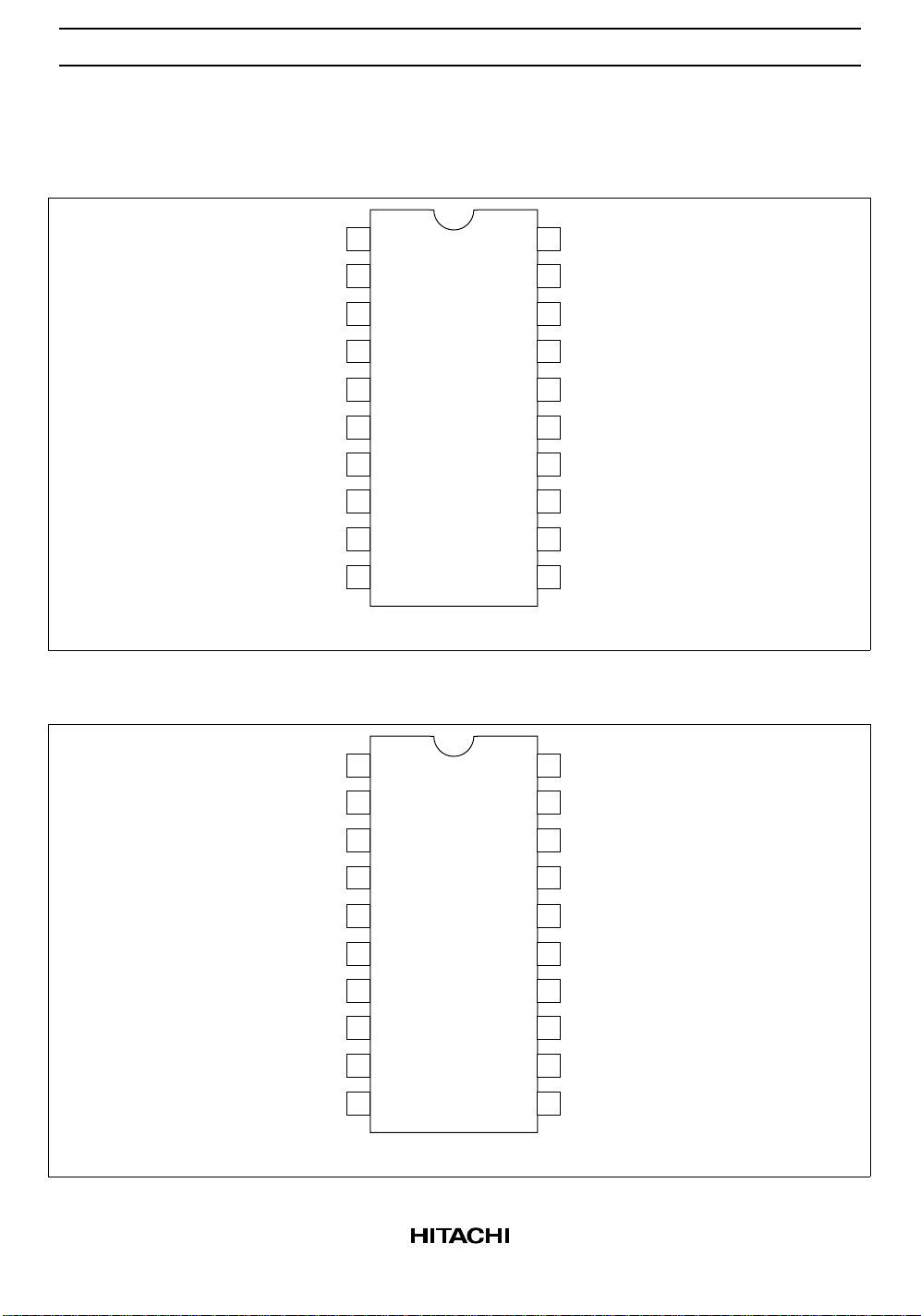

Pin Arrangement

HD74HC373

HD74HC533

Out put

Control

1Q

1D

2D

2Q

3Q

3D

4D

4Q

GND

Out put

Control

1Q

1

2

3

4

5

6

7

8

9

10 11

(Top view)

1

2

20

19

18

17

16

15

14

13

12

20

19

CC

V

8Q

8D

7D

7Q

6Q

6D

5D

5Q

Enable G

CC

V

8Q

1D

3

2D

4

2Q

5

3Q

6

3D

7

4D

8

9

4Q

GND

10 11

(Top view)

2

18

8D

17

7D

16

7Q

6Q

15

14

6D

13

5D

12

5Q

Enable G

HD74HC373/HD74HC533

Absolute Maximum Ratings

Item Symbol Rating Unit

Supply voltage range V

Input voltage V

Output voltage V

DC current drain per pin I

DC current drai per VCC GND ICC, I

DC input diode current I

DC output diode current I

Power Dissipation per package P

CC

IN

OUT

OUT

GND

IK

OK

T

Storage temperature Tstg –65 to +150 °C

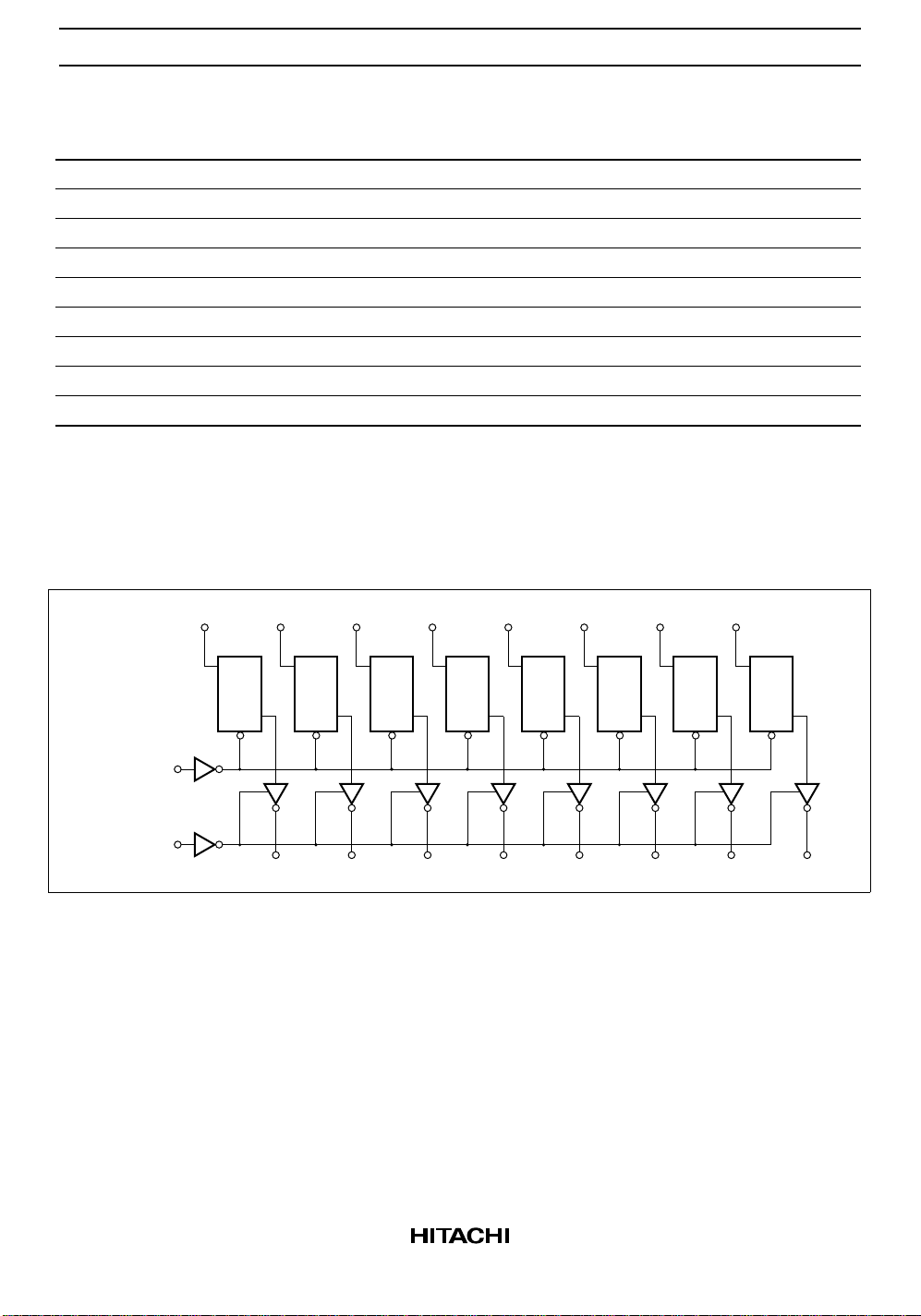

Block Diagram

HD74HC373

–0.5 to +7.0 V

–0.5 to VCC + 0.5 V

–0.5 to VCC + 0.5 V

±35 mA

±75 mA

±20 mA

±20 mA

500 mW

Enable G

Output

Control

1D

2D

D

Q

G

1Q

3D

D

Q

G

2Q

4D

D

Q

G

3Q

5D

D

Q

G

4Q

6D

D

Q

G

5Q

7D

D

Q

G

6Q

8D

D

G

D

Q

7Q

Q

G

8Q

3

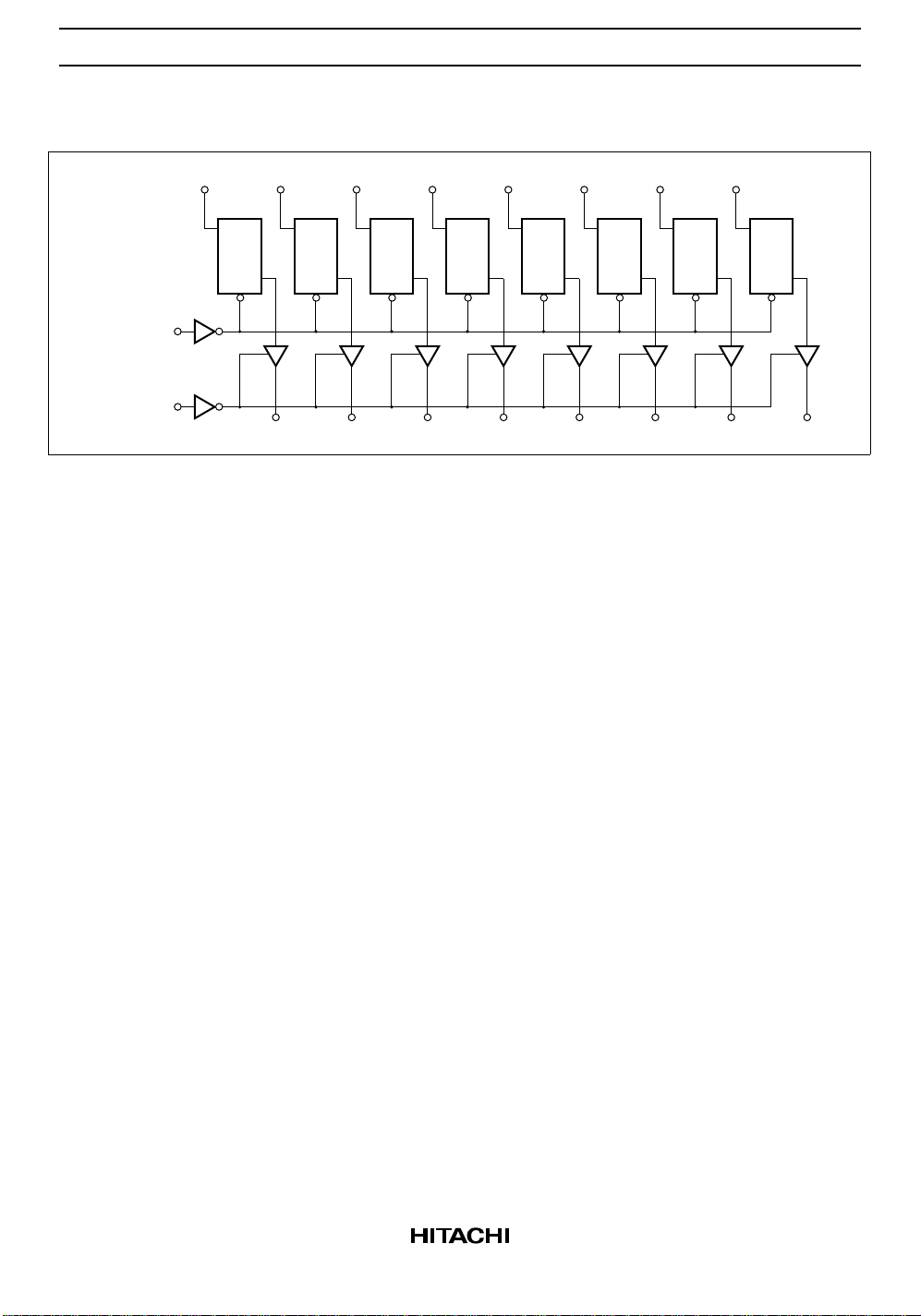

HD74HC373/HD74HC533

HD74HC533

Enable G

Output

Control

1D

2D

D

Q

G

1Q

3D

D

Q

G

2Q

4D

D

Q

G

3Q

5D

D

Q

G

4Q

6D

D

Q

G

5Q

7D

D

Q

G

6Q

8D

D

G

D

Q

7Q

Q

G

8Q

4

Loading...

Loading...