HIT HD74HC299 Datasheet

HD74HC299

8-bit Universal Shift/Storage Register (with 3-state outputs)

Description

The HD74HC299 features multiplexed inputs/outputs to achieve full 8-bit data handling in a single 20-pin

package. Due to the large output drive capability and 3-state feature, this device is ideally suited for

interfacing with bus lines in a bus oriented system. Two function select inputs and two output control

inputs are used to choose the mode of operation as listed in the function table. Synchronous parallel

loading is accomplished by taking both function select lines S0 and S1 high. This places the 3-state outputs

in a high impedance state, which permits data applied to the input/output lines to be clocked into the

register. Reading out of the register can be done while the outputs are enabled in any mode. A direct

overriding clear input is provided to clear the register whether the outputs are enabled or disabled.

Features

• High Speed Operation

• High Output Current: Fanout of 15 LSTTL Loads

• Wide Operating Voltage: VCC = 2 to 6 V

• Low Input Current: 1 µA max

• Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)

HD74HC299

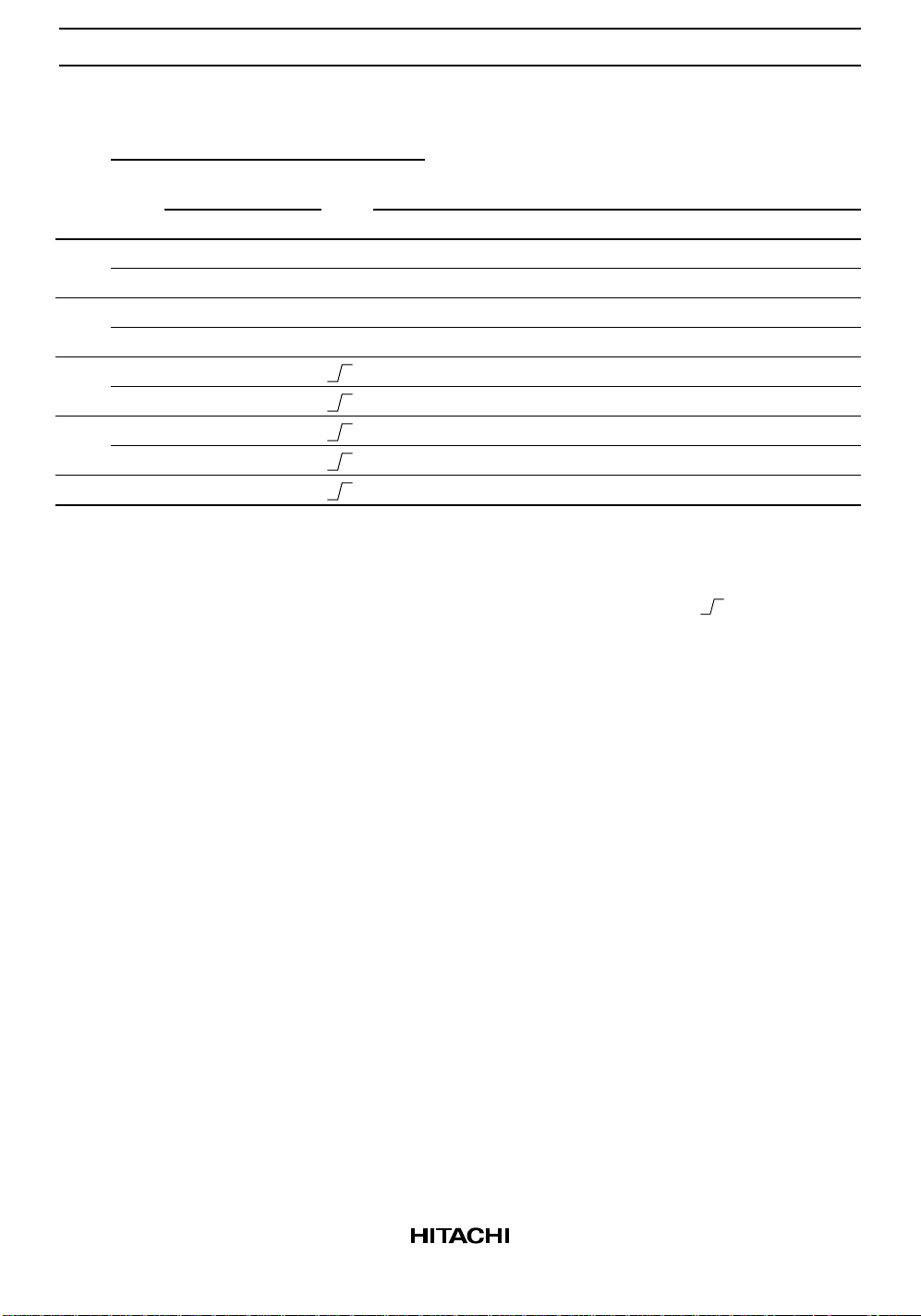

Function Table

Inputs

Function

Select

Mode Clear S1S0G1† G2† Clock SLSRA/QAB/QBC/QCD/QDE/QEF/QFG/QGH/QHQA’QH’

Clear L X L L L X X X L L L L L L L L L L

L LXLLX XXLLLLLLLLLL

Hold H LLLLX XXQA0QB0QC0QD0QE0QF0QG0QH0QA0Q

H XXLL L XXQA0QB0QC0QD0QE0QF0QG0QH0QA0Q

Shift H L H L L XHH QAnQBnQCnQDnQEnQFnQGnHQ

Right H L H L L XLL QAnQBnQCnQDnQEnQFnQGnLQ

Shift H H L L L HXQBnQCnQDnQEnQFnQGnQHnHQBnH

Left H H L L L LXQBnQCnQDnQEnQFnQGnQHnLQBnL

Load H H H X X XXabcdef ghah

Notes: 1. a to h; the level of steady-state input at inputs A through H, respectively. These data are

2. Q

to QH0; the level of QA through QH, respectively, before the indicated steady-state input

A0

3. Q

to QHn; the level of QA through QH, respectively, before the most-recent transition of the

An

4. † = ; When one or both output controls are high the eight input/output terminals are desabled to

the high-impedance state, however, sequential operation or clearing of the register is not

affected.

5. When clear is low, outputs of Q

Output

Control Serial Inputs/Outputs Outputs

loaded into the flip-flop outputs are isolated from the input/output terminals.

conditions were established.

clock.

’ and QH’ are low, in spite of other inputs.

A

H0

H0

Gn

Gn

2

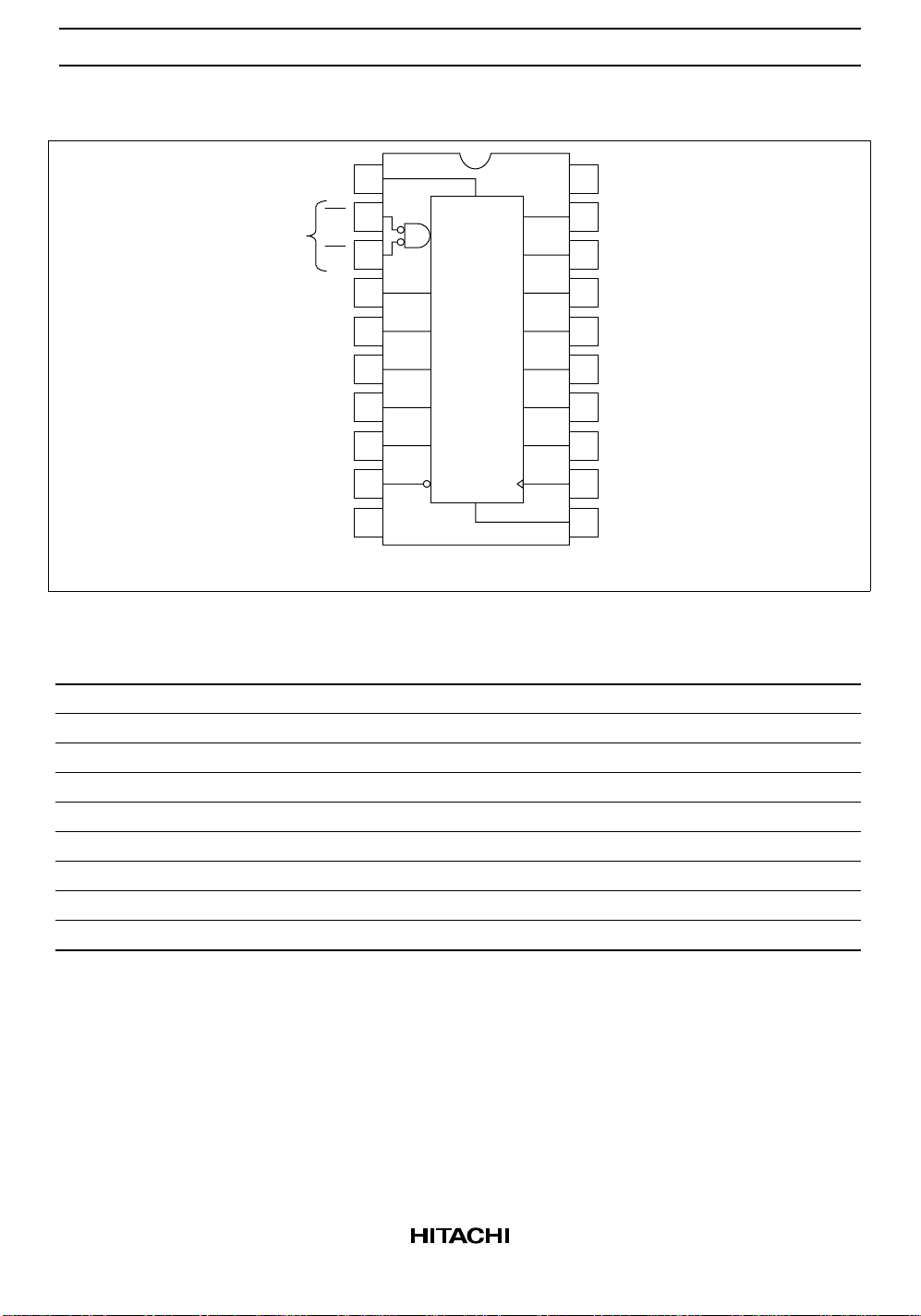

Pin Arrangement

Output

controls

G/Q

E/Q

S

G1

G

HD74HC299

1

1

0

S

0

2

2

G

3

3

2

4

4

C

5

5

E

G/Q

E/Q

S

1

SL

Q

H

G

H/Q

H

E

20

19

18

17

16

V

CC

S1

Shift left

SL

Q

H

H/Q

H

C/Q

A/Q

Q

Clear

GND

F/Q

6

6

C

7

7

A

8

8

A

9

9

10

10

C/Q

A/Q

Q

A

Clear

F

C

D/Q

D

A

B/Q

B

CK

SR

15

14

13

12

11

F/Q

F

D/Q

D

B/Q

B

Clock

Shift right

SR

(Top view)

Absolute Maximum Ratings

Item Symbol Rating Unit

Supply voltage range V

Input voltage V

Output voltage V

Output current I

DC current drain per VCC, GND ICC, I

DC input diode current I

DC output diode current I

Power dissipation per package P

CC

IN

OUT

OUT

GND

IK

OK

T

Storage temperature Tstg –65 to +150 °C

–0.5 to +7.0 V

–0.5 to VCC + 0.5 V

–0.5 to VCC + 0.5 V

±35 mA

±75 mA

±20 mA

±20 mA

500 mW

3

HD74HC299

Block Diagram

Sift

right

serial-input

S

1

S

0

Sift

left

serial-input

Clear

Clock

D

CC CLR

G

2

G

1

Q

A

D

Q

CC CLR

A Q

A

D

Q

CC CLR

B Q

B

D

Q

CC CLR

C Q

C

D

Q

CC CLR

D Q

D

D

Q

CC CLR

E Q

E

D

Q

CC CLR

F Q

F

D

Q

Q

CC CLR

G Q

G

H Q

Q

H

H

4

Loading...

Loading...