HIT HD74HC166 Datasheet

HD74HC166

Parallel-load 8-bit Shift Register

Description

This device is an 8-bit shift register with an output from the last stage. Data may be loaded into the register

either in parallel or in serial form. When the Shift/Load input is low, the data is loaded asynchronously in

parallel. When the Shift/Load input is high, the data is loaded serially on the rising edge of either clock

inhibit or Clock. Clear is asynchronous and active-low.

The 2-input NOR clock may be used either by combining two independent clock sources or by designating

one of the clock inputs to act as a clock inhibit.

Features

• High Speed Operation: tpd (Clock to QH) = 14 ns typ (CL = 50 pF)

• High Output Current: Fanout of 10 LSTTL Loads

• Wide Operating Voltage: VCC = 2 to 6 V

• Low Input Current: 1 µA max

• Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)

Function Table

Inputs

Parallel Internal Outputs Output

Clear Shift/Load Clock Inhibit Clock Serial A ··· H Q

L X X XXXLLL

H X L LXXQA0Q

HL L X a ··· h a b h

HH L HXHQAnQ

HH L LXLQAnQ

HX H XXQA0Q

A

Q

B

B0

B0

Q

H

Q

H0

Gn

Gn

Q

H0

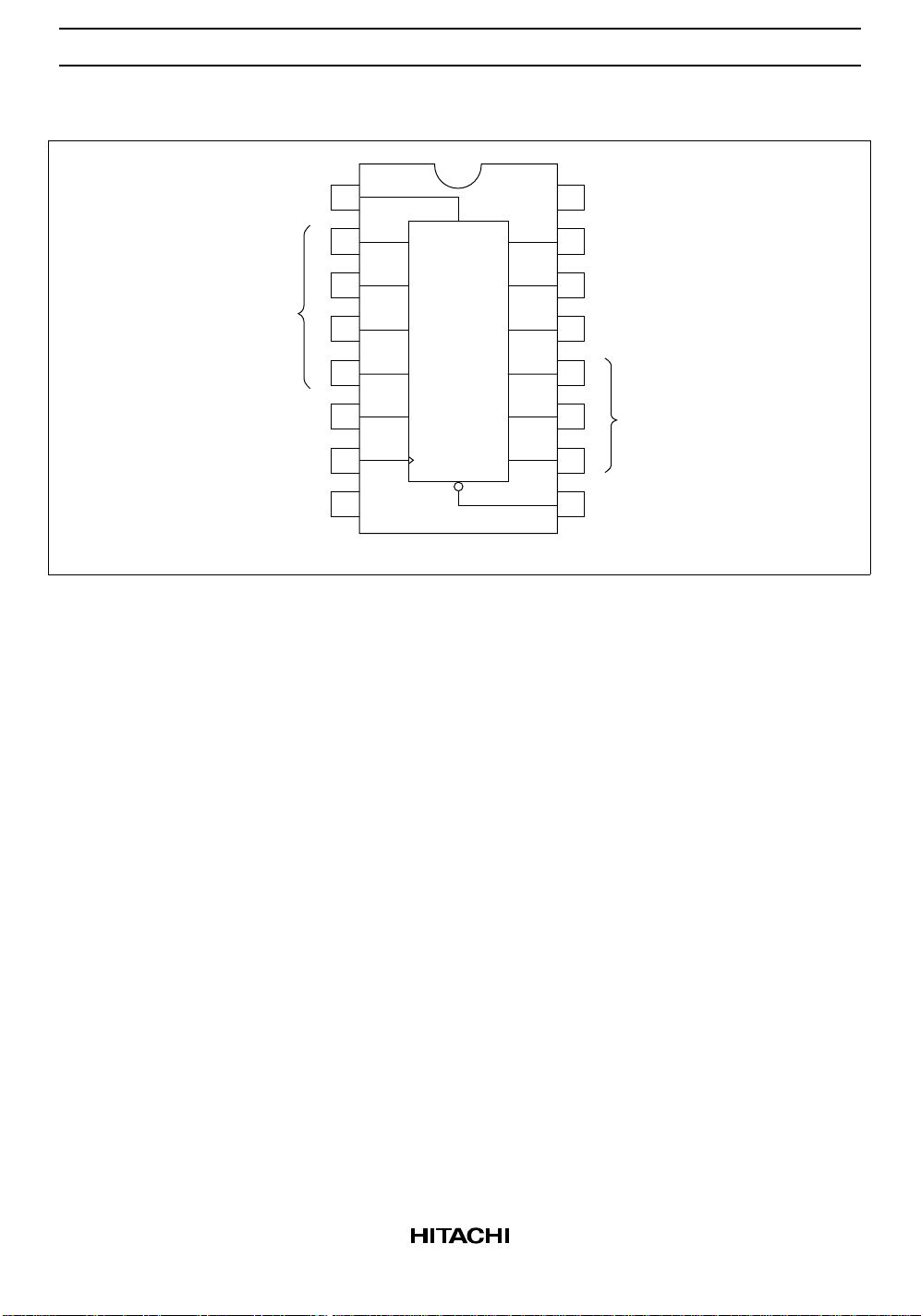

HD74HC166

Pin Arrangement

Serial

Input

Parallel

Inputs

Clock

Inhibit

Clock

GND

16

1

2

A

3

B

4

C

5

D

6

7

8

(Top view)

V

15

Shift/Load

Parallel

14

Input H

Output

13

Q

12

G

11

F

10

E

9

Clear

CC

H

Parallel

Inputs

2

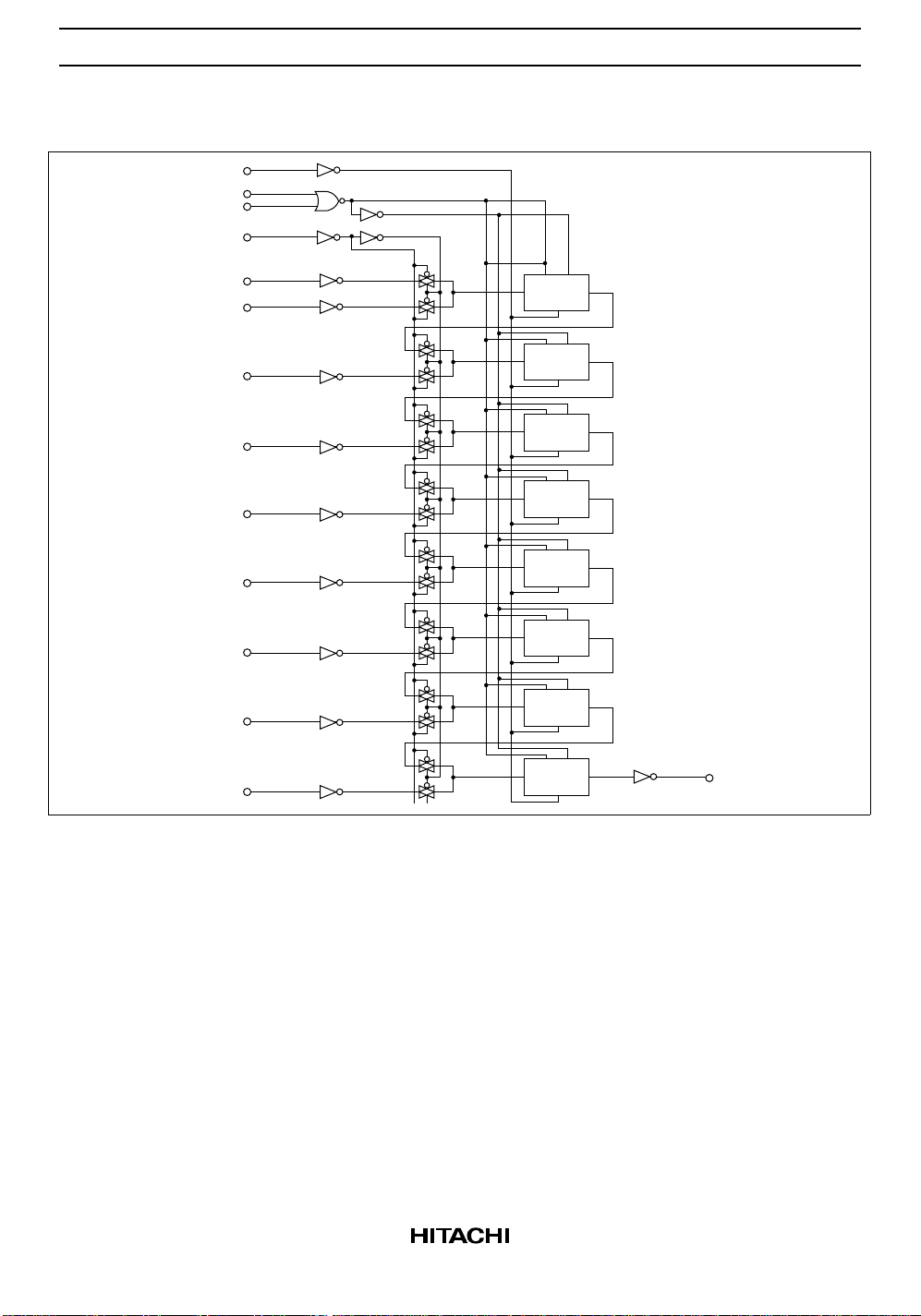

Logic Diagram

Clear

Clock

Clock

Inhibit

Shift/

Load

Serial

Input

HD74HC166

CK

CK

D Q

A

B

C

D

E

CLK

CK

CK

D Q

CLK

CK

CK

D Q

CLK

CK

CK

D Q

CLK

CK

CK

D Q

CLK

H

CK

CK

D Q

F

G

CLK

CK

CK

D Q

CLK

CK

CK

D Q

CLK

H

Q

3

Loading...

Loading...