HIT HD74BC373A Datasheet

HD74BC373A

Octal D Type Transparent Latches With 3 State Outputs

ADE-205-009A(Z)

Rev. 1

March 1993

Description

The HD74BC373A provides high drivability and operation equal to or better than high speed bipolar

standard logic IC by using Bi-CMOS process. The device features low power dissipation that is about 1/5

of high speed bipolar logic IC, when the frequency is 10 MHz. The device has eight D type latches with

three state outputs in a 20 pin package. When the latch enable input is high, the Q outputs will follow the

D inputs. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch

enable returns high again. When a high logic level is applied to the output control input, all outputs go to a

high impedance state, regardless of what signals are present at the other inputs and the state of the storage

elements.

Features

• Input/Output are at high impedance state when power supply is off.

• Built in input pull up circuit can make input pins be open, when not used.

• TTL level input

• Wide operating temperature range input pins

Ta = –40 to + 85°C

Function Table

Inputs

G LE D Output Q

HX X Z

LH L L

LH H H

L L X No change

H : High level

L : Low level

X : Immaterial

Z : High impedance

HD74BC373A

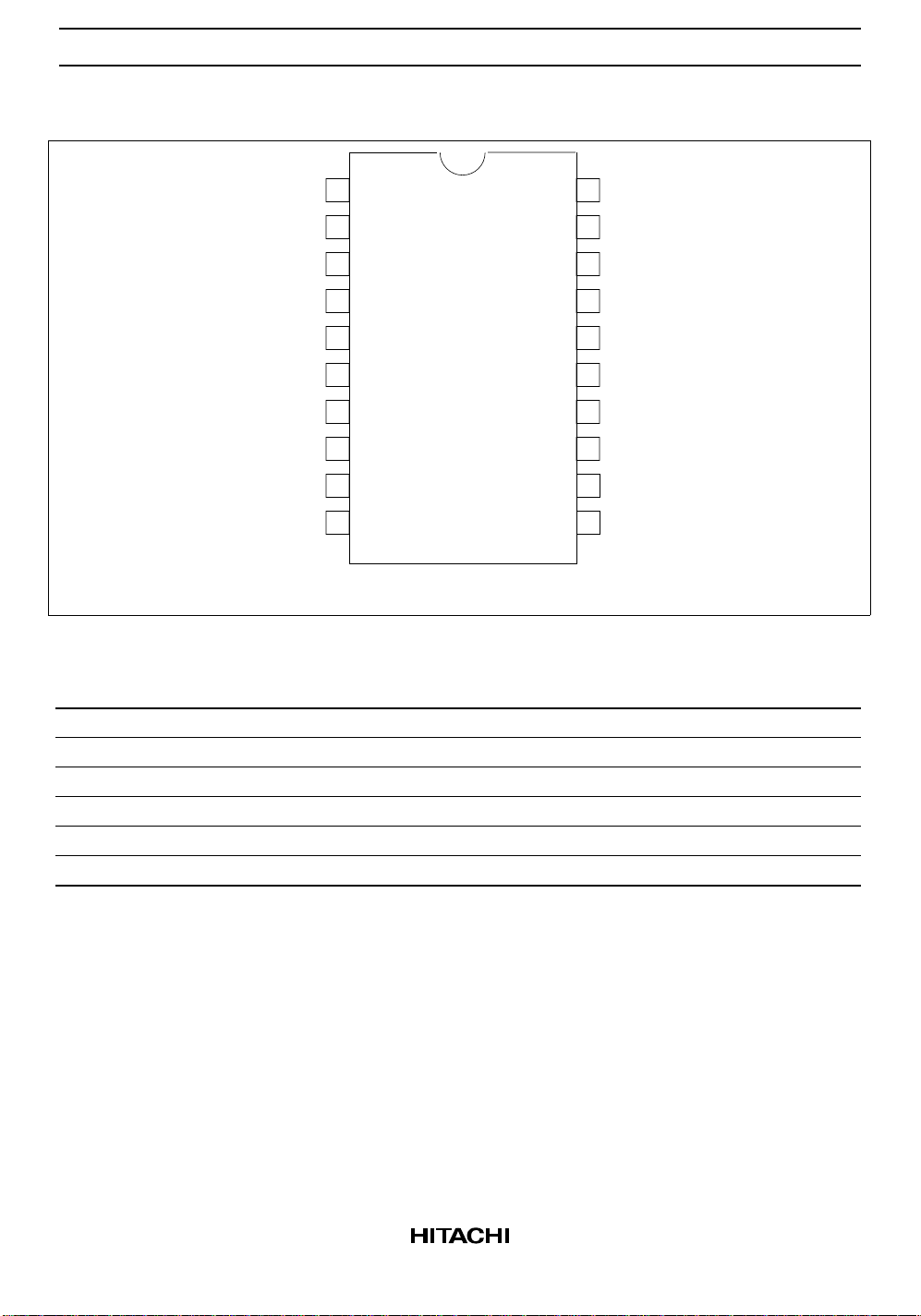

Pin Arrangement

G

1Q

1D

2D

2Q

3Q

3D

4D

4Q

GND

10

1

2

3

4

5

6

7

8

9

20

19

18

17

16

15

14

13

12

11

V

8Q

8D

7D

7Q

6Q

6D

5D

5Q

LE

CC

(Top view)

Absolute Maximum Ratings

Item Symbol Rating Unit

Supply voltage V

Input diode current I

Input voltage V

Output voltage V

Off state output voltage V

CC

IK

IN

OUT

OUT(off)

Storage temperature Tstg –65 to +150 °C

Note: 1. The absolute maximum ratings are values which must not individually be exceeded, and

furthermore, no two of which may be realized at the same time.

–0.5 to +7.0 V

±30 mA

–0.5 to +7.5 V

–0.5 to +7.5 V

–0.5 to +5.5 V

2

HD74BC373A

Recommended Operating Conditions

Item Symbol Min Typ Max Unit

Supply voltage V

Input voltage V

Output voltage V

CC

IN

OUT

Operating temperature Topr –40 — 85 °C

Input rise/fall time*

1

tr, t

f

Note: 1. This item guarantees maximum limit when one input switches.

Waveform: Refer to test circuit of switching characteristics.

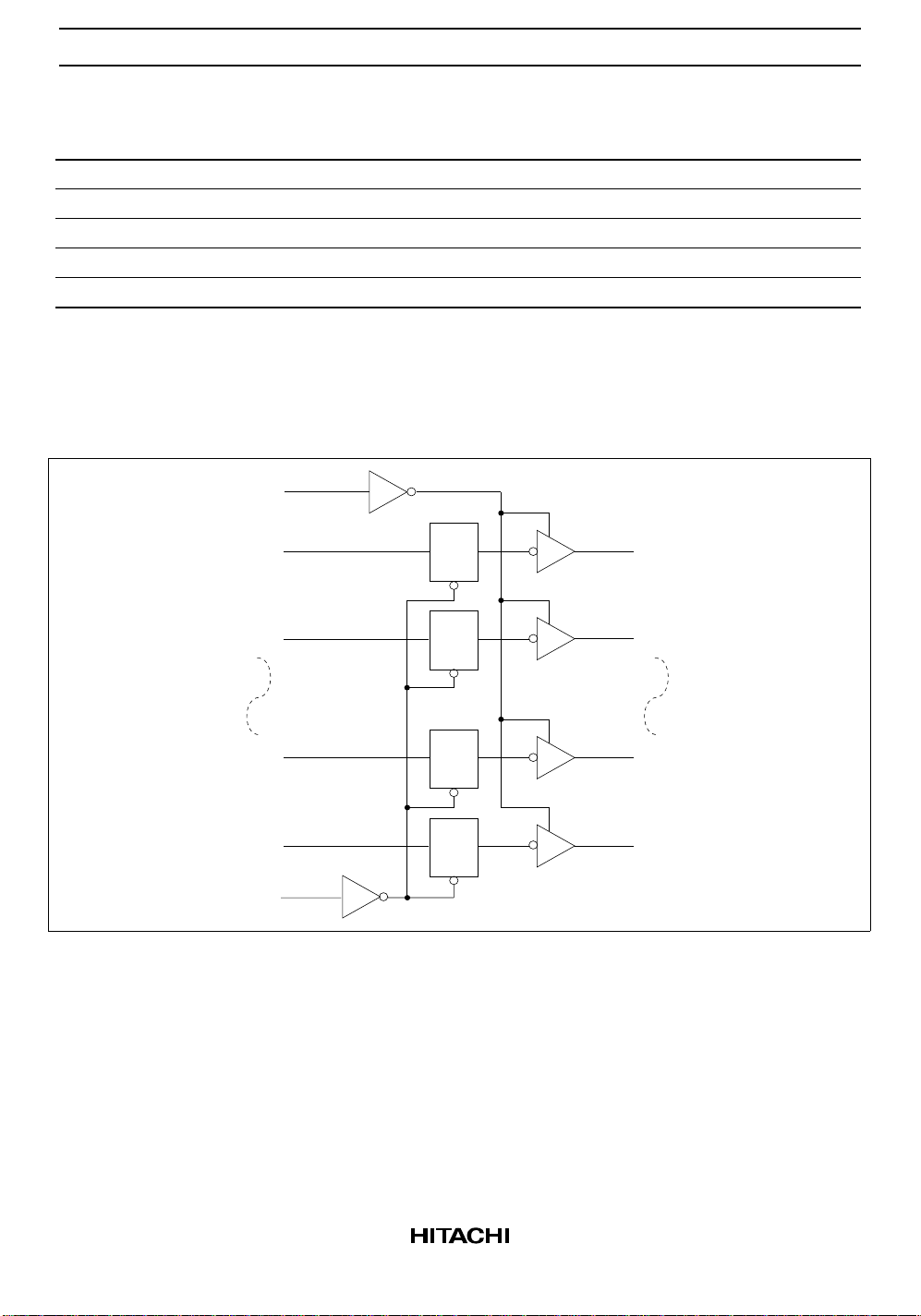

Logic Diagram

G

4.5 5.0 5.5 V

0—VCCV

0—VCCV

0 — 8 ns/V

1D

2D

7D

8D

LE

D Q

D Q

D Q

D Q

1Q

2Q

7Q

8Q

3

Loading...

Loading...