HIT HD74ALVCH16334 Datasheet

HD74ALVCH16334

16-bit Universal Bus Driver with 3-state Outputs

ADE-205-212 (Z)

Preliminary

1st. Edition

December 1997

Description

This HD74ALVCH16334 is a 16-bit universal bus driver is designed for 2.3 V to 3.6 V VCC operation.

Data flow from A to Y is controlled by the output enable (OE) input. The device operates in the

transparent mode when the latch enable (LE) input is low. When LE is high, the A data is latched if the

clock (CLK) input is held at a high or low logic level. If LE is high, the A data is stored in the latch/flip

flop on the low to high transition of CLK. When OE is high, the outputs are in the high impedance state.

To ensure the high impedance state during power up or power down, OE should be tied to VCC through a

pullup resistor; the minimum value of the resistor is determined by the current sinking capability of the

driver.

Active bus hold circuitry is provided to hold unused or floating inputs at a valid logic level.

Features

• VCC = 2.3 V to 3.6 V

• Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C)

• Typical VOH undershoot > 2.0 V (@VCC = 3.3 V, Ta = 25°C)

• High output current ±24 mA (@VCC = 3.0 V)

• Bus hold on data inputs eliminates the need for external pullup / pulldown resistors

HD74ALVCH16334

Function Table

Inputs Output Y

OE LE CLK A

HX XXZ

LL XLL

LL XHH

LH ↑LL

LH ↑HH

L H L or H X Y0

H : High level

L : Low level

X : Immaterial

Z : High impedance

↑ : Low to high transition

Note: 1. Output level before the indicated steady state input conditions were established.

*1

2

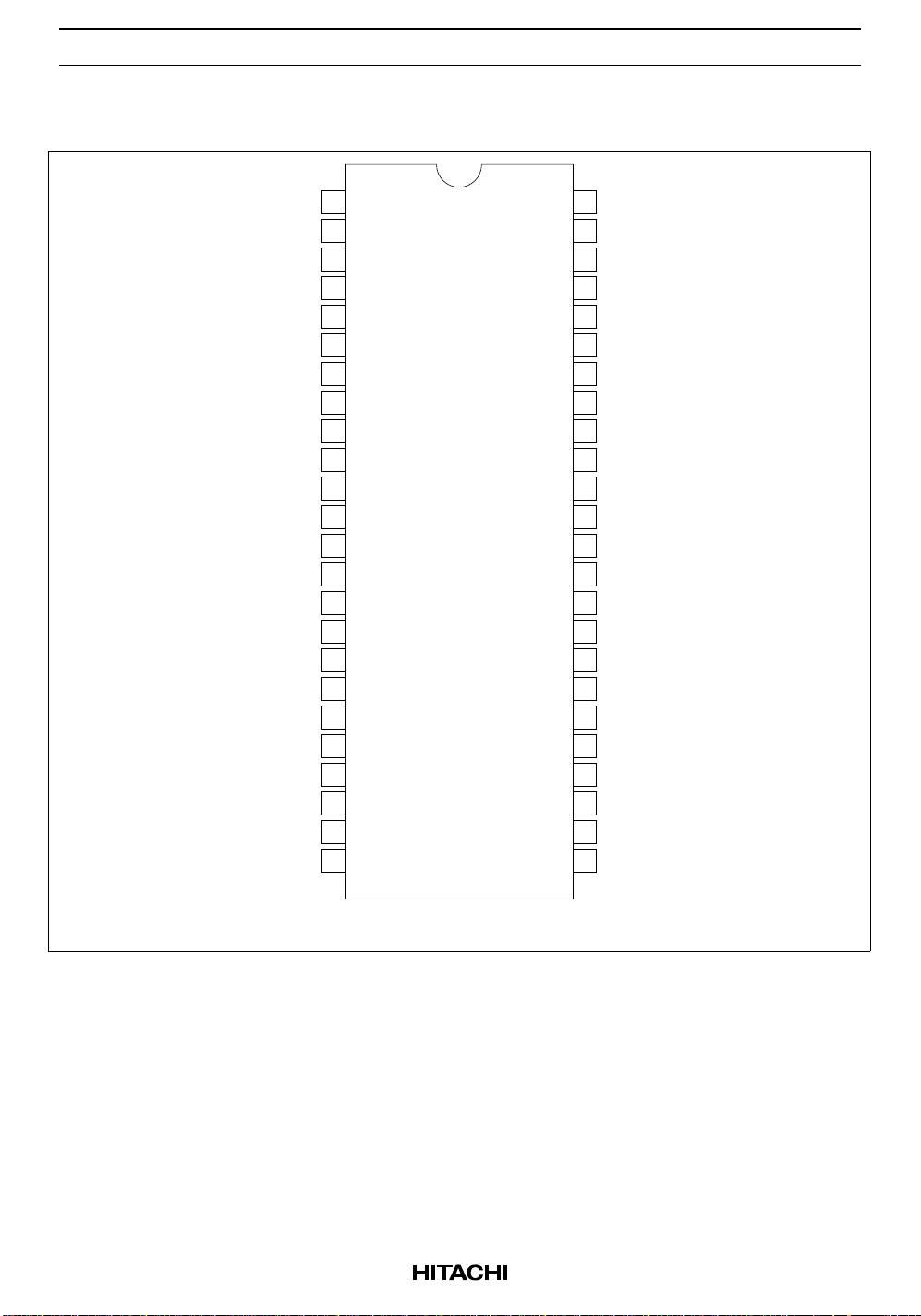

Pin Arrangement

HD74ALVCH16334

OE

Y1

Y2

GND

Y3

Y4

V

CC

Y5

Y6

GND

Y7

Y8

Y9

Y10

GND

Y11

Y12

V

CC

Y13

Y14

GND

Y15

Y16

NC

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

CLK

1

2

3

4

5

6

7

8

9

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

A1

A2

GND

A3

A4

V

CC

A5

A6

GND

A7

A8

A9

A10

GND

A11

A12

V

CC

A13

A14

GND

A15

A16

LE

(Top view)

3

HD74ALVCH16334

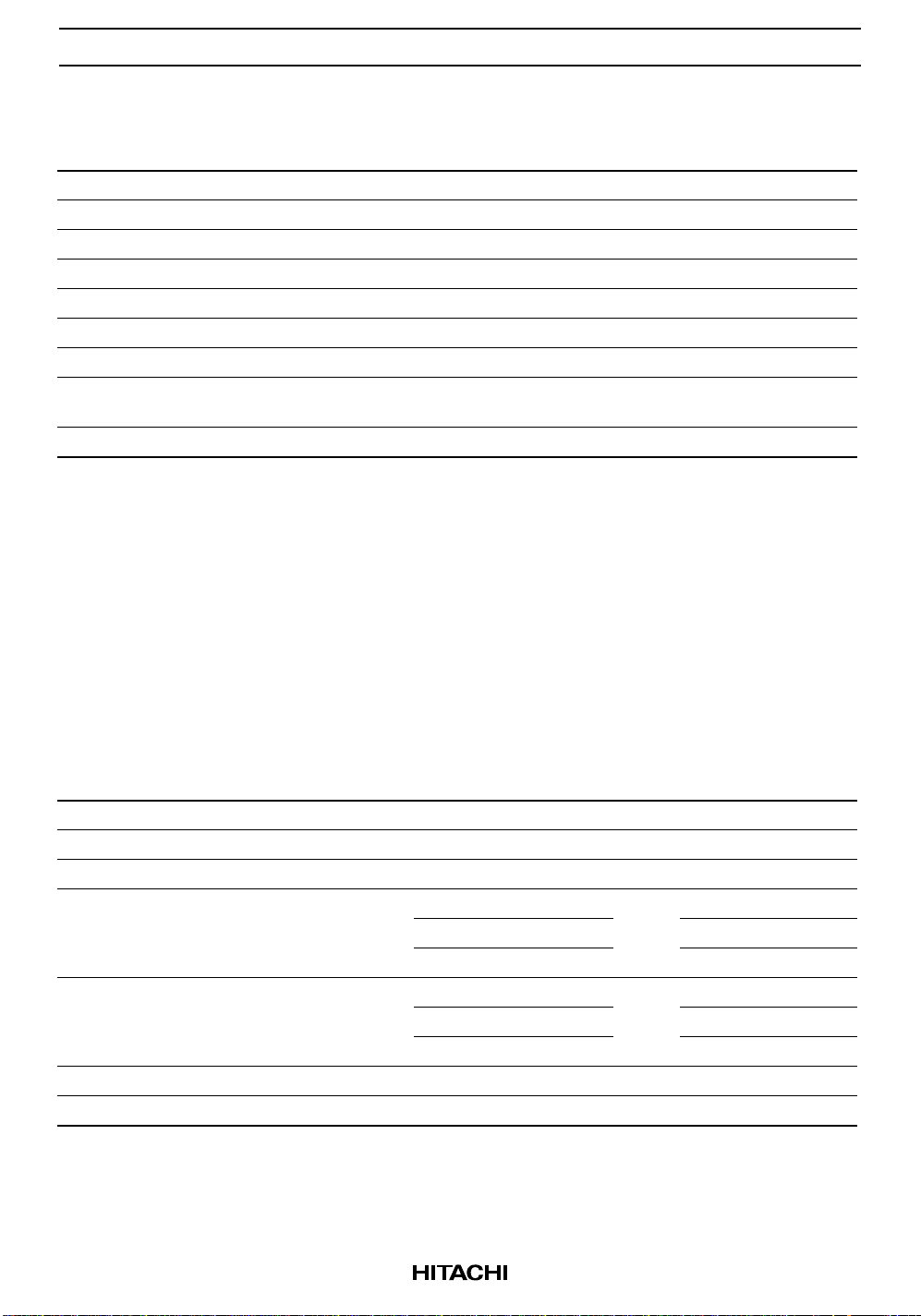

Absolute Maximum Ratings

Item Symbol Ratings Unit Conditions

Supply voltage V

Input voltage

Output voltage

*1

*1, 2

Input clamp current I

Output clamp current I

Continuous output current I

VCC, GND current / pin ICC or I

Maximum power dissipation

at Ta = 55°C (in still air)

*3

Storage temperature T

CC

V

I

V

O

IK

OK

O

GND

P

T

stg

Notes: Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage

to the device. These are stress ratings only, and functional operation of the device at these or

any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute maximum rated conditions for extended periods may affect device

reliability.

1. The input and output negative voltage ratings may be exceeded if the input and output clamp

current ratings are observed.

2. This value is limited to 4.6 V maximum.

3. The maximum package power dissipation is calculated using a junction temperature of 150°C

and a board trace length of 750 mils.

–0.5 to 4.6 V

–0.5 to 4.6 V

–0.5 to VCC +0.5 V

–50 mA VI < 0

±50 mA VO < 0 or VO > V

±50 mA VO = 0 to V

CC

±100 mA

0.85 W TSSOP

–65 to 150 °C

CC

Recommended Operating Conditions

Item Symbol Min Max Unit Conditions

Supply voltage V

Input voltage V

Output voltage V

High level output current I

Low level output current I

CC

I

O

OH

OL

Input transition rise or fall rate ∆t / ∆v 0 10 ns / V

Operating temperature T

a

Note: Unused control inputs must be held high or low to prevent them from floating.

2.3 3.6 V

0VCCV

0VCCV

— –12 mA VCC = 2.3 V

— –12 VCC = 2.7 V

— –24 VCC = 3.0 V

—12mAV

—12 V

—24 V

= 2.3 V

CC

= 2.7 V

CC

= 3.0 V

CC

–40 85 °C

4

Loading...

Loading...