HIT HD74ALVCH162244 Datasheet

HD74ALVCH162244

16-bit Buffers / Drivers with 3-state Outputs

ADE-205-173A (Z)

Preliminary

2nd. Edition

January 1998

Description

The HD74ALVCH162244 is designed specifically to improve both the performance and density of 3-state

memory address drivers, clock drivers, and bus oriented receivers and transmitters. The device can be used

as four 4-bit buffers, two 8-bit buffers, or one 16-bit buffer. It provides true outputs and symmetrical

active-low output-enable (OE) inputs.

To ensure the high impedance state during power up or power down, OE should be tied to VCC through a

pullup resistor; the minimum value of the resistor is determined by the current sinking capability of the

driver.

Active bus hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

All outputs, which are designed to sink up to 12 mA, include 26 Ω resistors to reduce overshoot and

undershoot.

Features

• VCC = 2.3 V to 3.6 V

• Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C)

• Typical VOH undershoot > 2.0 V (@VCC = 3.3 V, Ta = 25°C)

• High output current ±12 mA (@VCC = 3.0 V)

• Bus hold on data inputs eliminates the need for external pullup / pulldown resistors

• All outputs have equivalent 26 Ω series resistors, so no external resistors are required.

HD74ALVCH162244

Function Table

Inputs Output Y

OE A

LHH

LLL

HXZ

H : High level

L : Low level

X : Immaterial

Z : High impedance

2

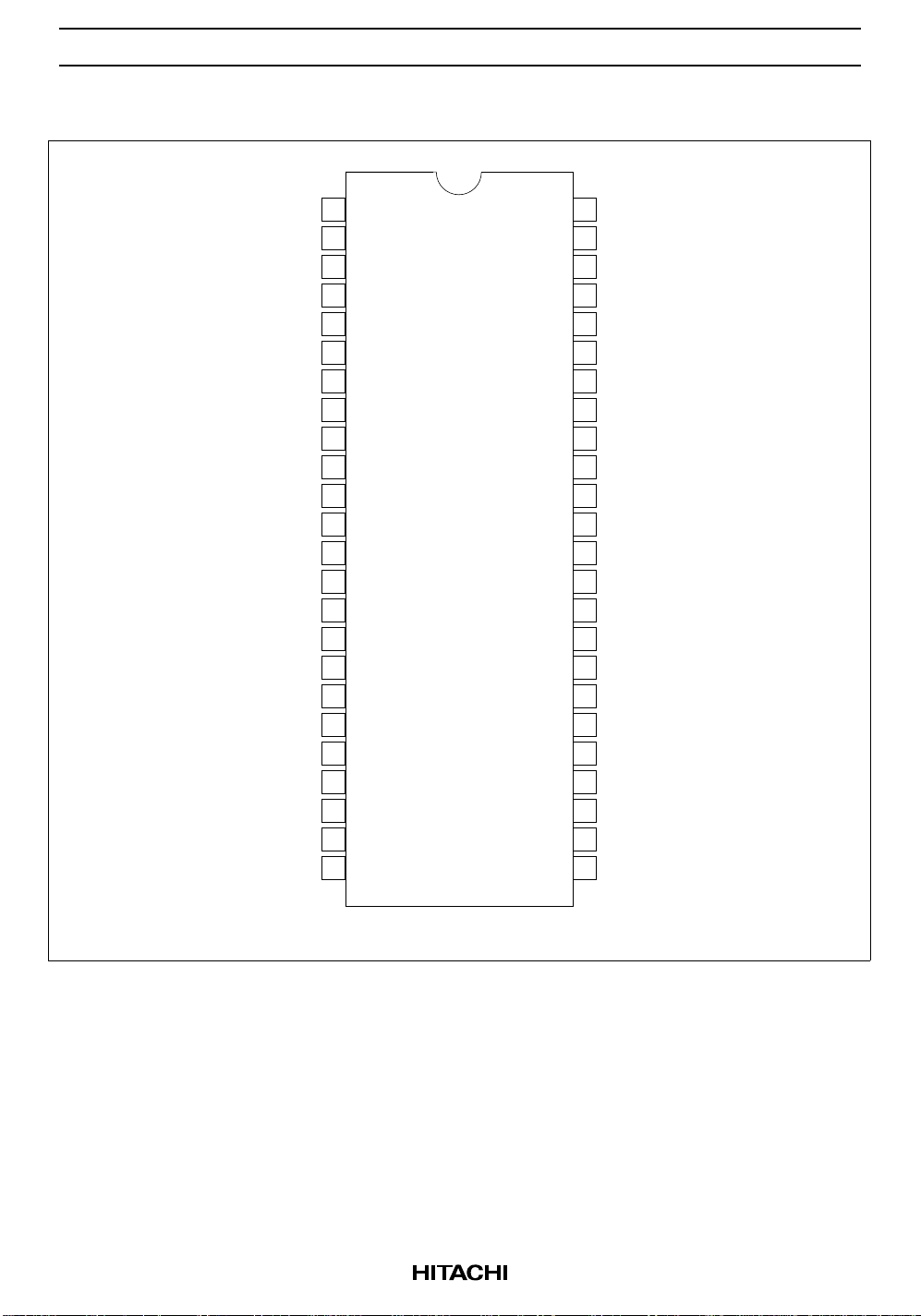

Pin Arrangement

1OE

1Y1

1Y2

GND

1Y3

1Y4

V

CC

2Y1

2Y2

GND

2Y3

2Y4

3Y1

3Y2

GND

3Y3

3Y4

V

CC

4Y1

4Y2

GND

4Y3

4Y4

4OE

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

HD74ALVCH162244

2OE

1

2

3

4

5

6

7

8

9

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1A1

1A2

GND

1A3

1A4

V

CC

2A1

2A2

GND

2A3

2A4

3A1

3A2

GND

3A3

3A4

V

CC

4A1

4A2

GND

4A3

4A4

3OE

(Top view)

3

Loading...

Loading...