HIT HD74AC273 Datasheet

HD74AC273

Octal D Flip-Flop

Description

The HD74AC273 has eight edge-triggered D-type flip-flops with individual D inputs and Q outputs. The

common buffered Clock (CP) and Master Reset (MR) inputs load and reset (clear) all flip-flops

simultaneously.

The register is fully edge-triggered. The state of each D input, one setup time before the Low-to-High

clock transition, is transferred to the corresponding flip-flops’s Q output

All outputs will be forced Low independently of Clock or Data inputs by a Low voltage level on the MR

input. The device is useful for applications where the true output only is required and the Clock and Master

Reset are common to all storage elements.

Features

• Ideal Buffer for MOS Microprocessor or Memory

• Eight Edge-Triggered D Flip-Flops

• Buffered Common Clock

• Buffered, Asynchronous Master Reset

• See HD74AC373 for Transparent Latch Version

• See HD74AC374 for 3-State Version

• Outputs Source/Sink 24 mA

HD74AC273

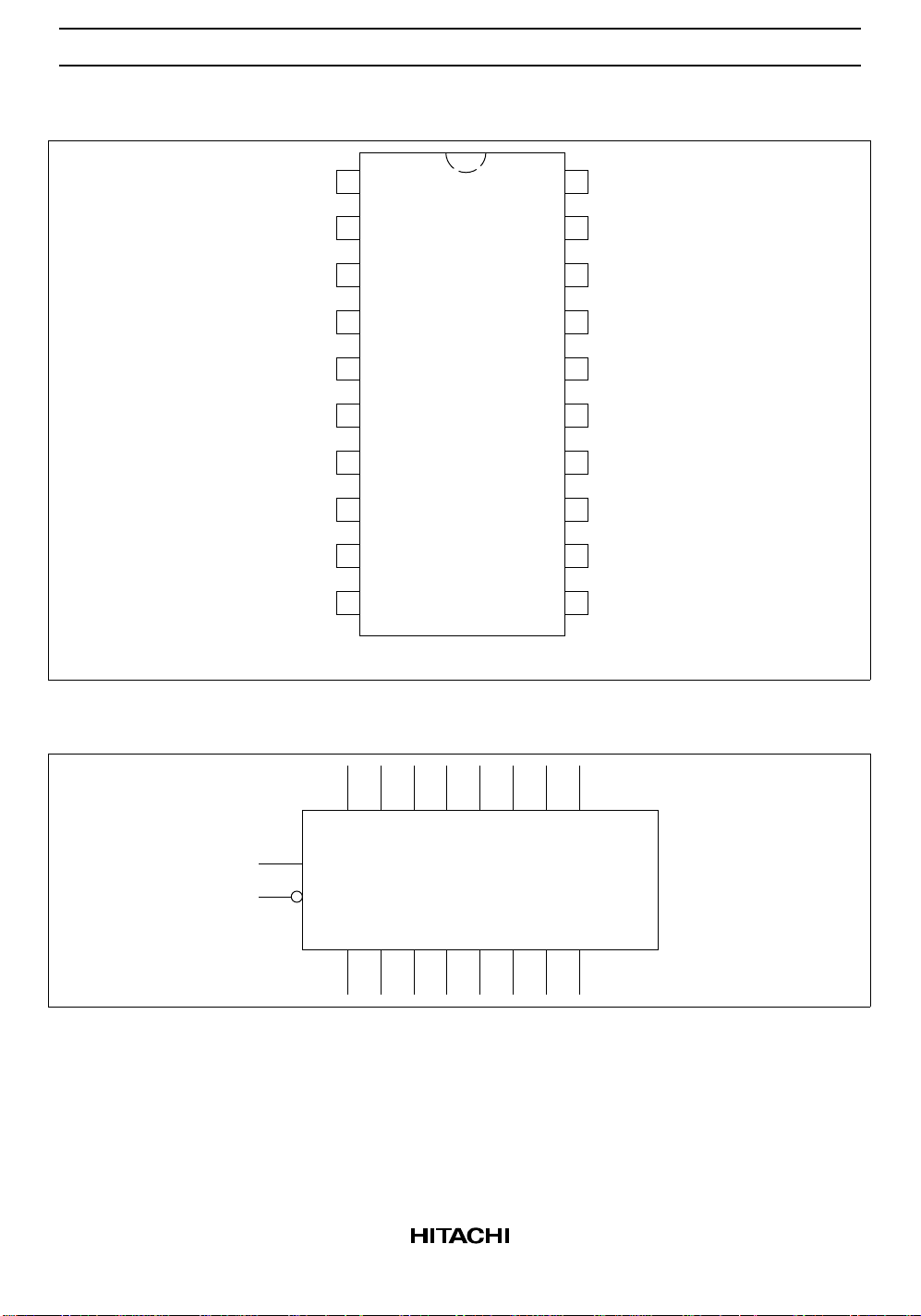

Pin Arrangement

MR

1

20

V

CC

Logic Symbol

2

0

Q

D0

3

D1

4

Q1

5

Q2

6

7

D2

D3

8

Q3

9

10 11

Gnd

(Top view)

19

18

17

16

15

14

13

12

Q7

D7

D6

Q6

Q5

D

D4

Q4

CP

5

Pin Names

D0 – D7Data Inputs

MR Master Reset

CP Clock Pulse Input

Q0 – Q7Data Outputs

2

D0 D1 D2 D3 D4 D5 D6 D7

CP

MR

Q

0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

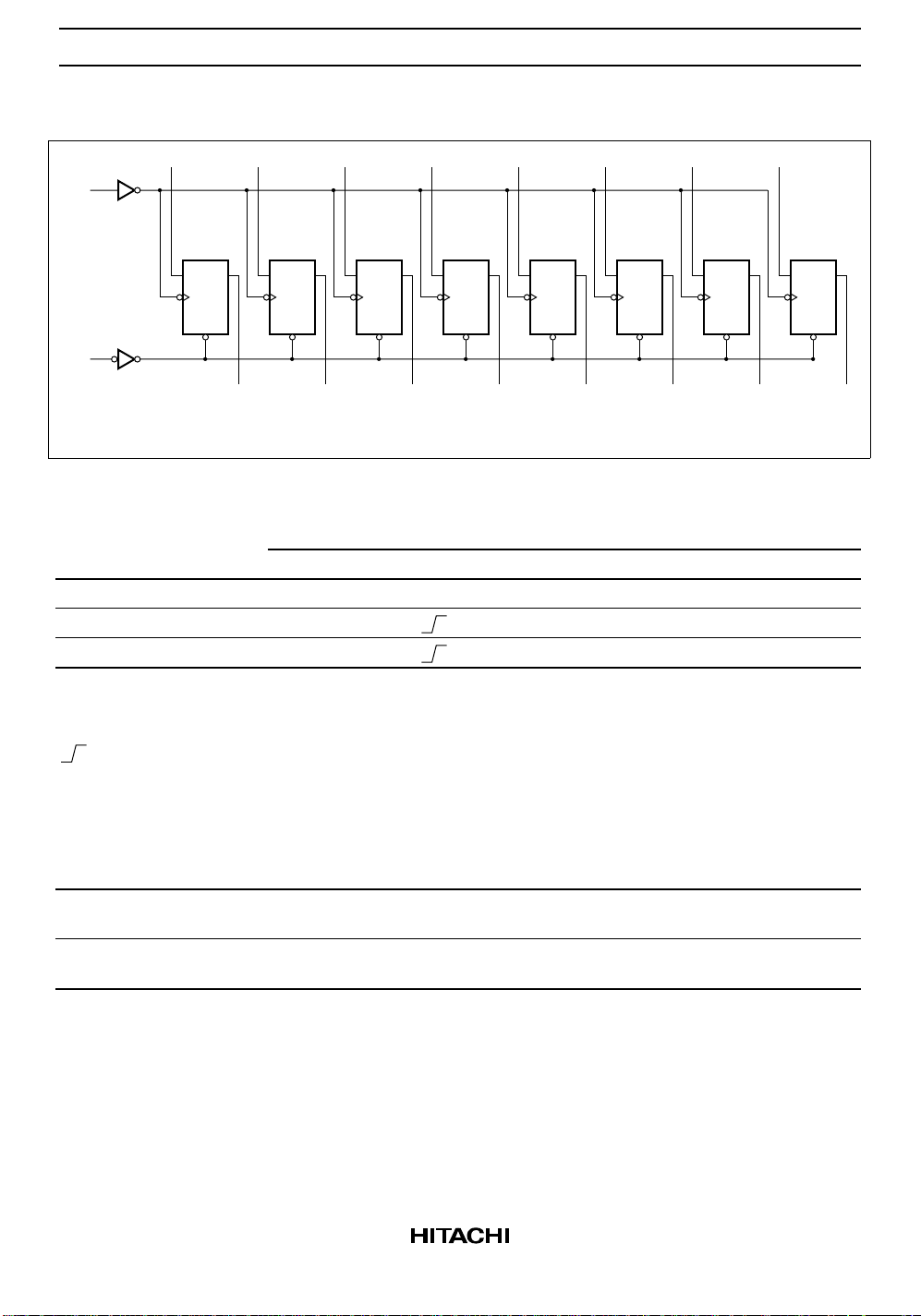

Logic Diagram

D0 D1 D2 D3 D4 D5 D6 D7

CP

HD74AC273

MR

DQ

CP

D

R

DQ

CP

D

R

DQ

CP

D

R

DQ

CP

D

R

DQ

CP

D

R

DQ

CP

D

R

DQ

CP

D

R

DQ

CP

D

R

Q7Q6Q5Q4Q3Q2Q1Q0

Please note that this diagram is provided only for the understanding of logic operations and should not be

used to estimate propagation delays.

Mode Select-Truth Table

Inputs Outputs

Operating Mode MR CP D

n

Reset (Clear) L X X L

Load “1” H HH

Load “0” H LL

H : High Voltage Level

L : Low Voltage Level

X : Immaterial

: Low-to-High Clock Transition

Q

n

DC Characteristics (unless otherwise specified)

Item Symbol Max Unit Condition

Maximum quiescent supply current I

Maximum quiescent supply current I

CC

CC

80 µAV

8.0 µAV

= VCC or ground, VCC = 5.5 V,

IN

Ta = Worst case

= VCC or ground, VCC = 5.5 V,

IN

Ta = 25°C

3

Loading...

Loading...