HIT HD74ACT182, HD74AC182 Datasheet

HD74AC182/HD74ACT182

Carry Lookhead Generator

Description

The HD74AC182/HD74ACT182 is a high-speed carry lookahead generator. It is generally used with the

HD74AC181 or HD74AC381 4-bit arithmetic logic unit to provide high-speed lookahead over word

lengths of more than four bits.

Features

• Outputs Source/Sink 24 mA

• HD74ACT182 has TTL-Compatible Inputs

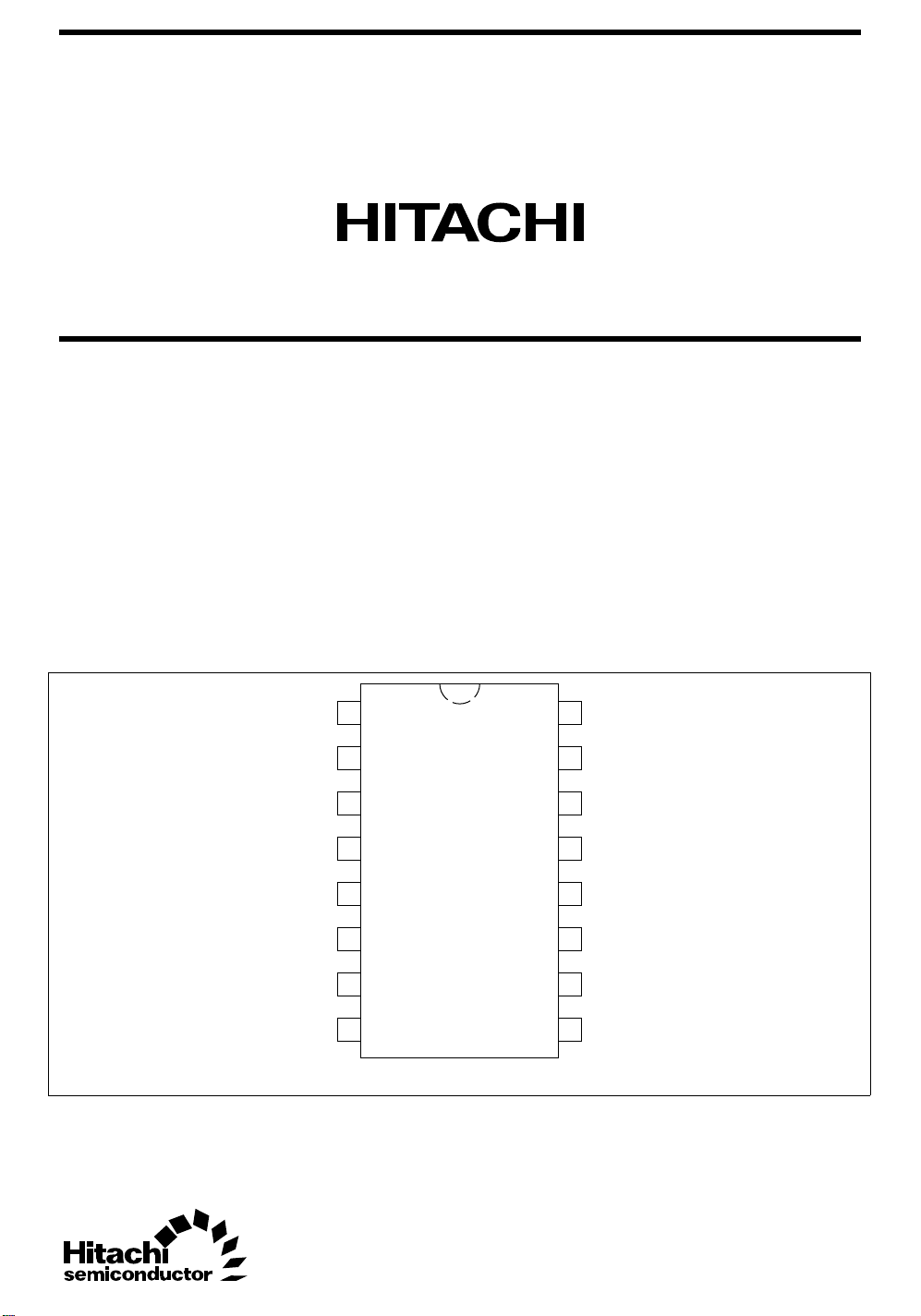

Pin Arrangement

G

P1

G0

P0

G3

P

GND

1

1

2

3

4

5

3

6

7

P

8

(Top view)

16

15

14

13

12

11

10

CC

V

P2

G2

Cn

Cn+X

Cn+y

G

9

n+z

C

HD74AC182/HD74ACT182

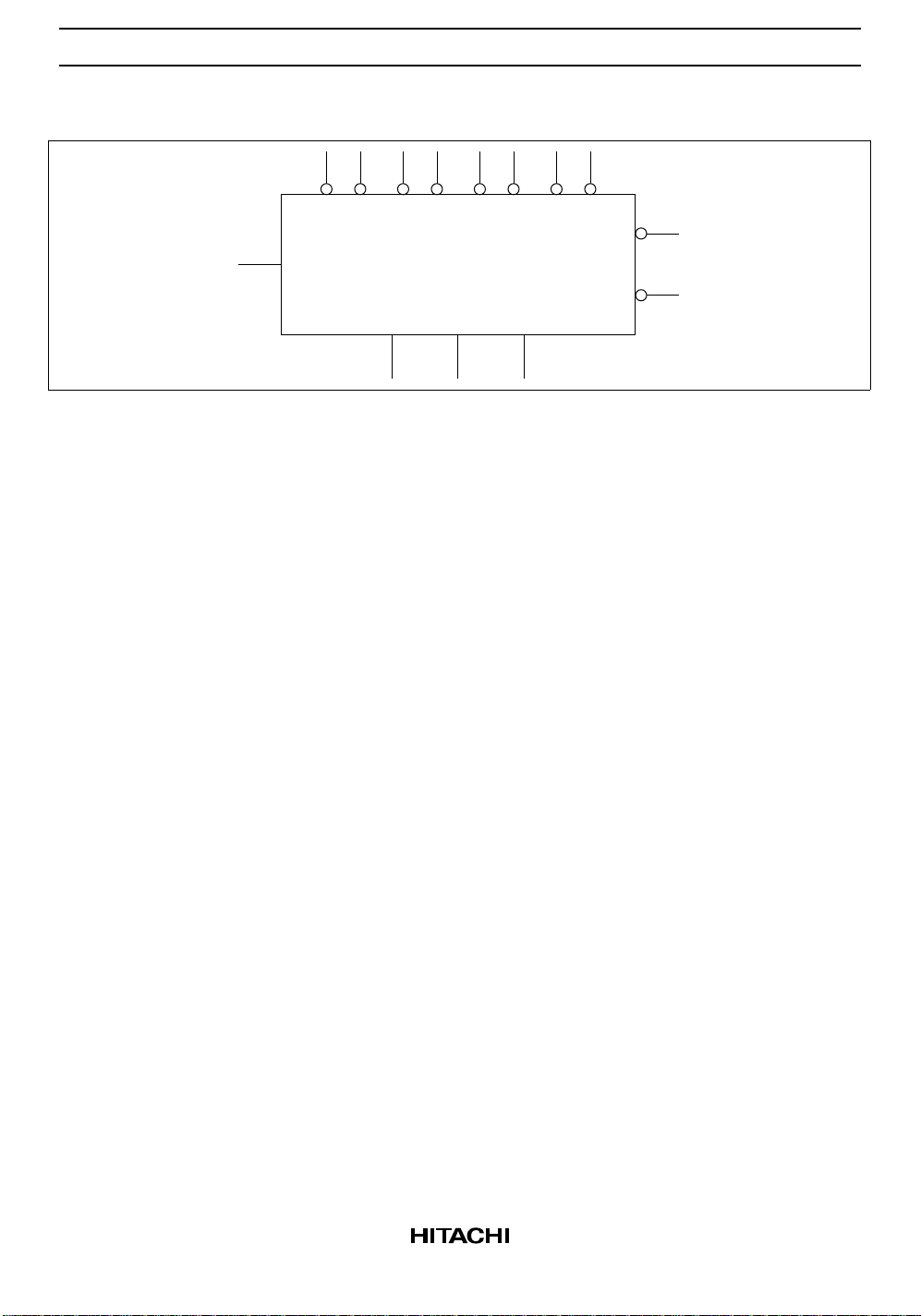

Logic Symbol

P

0

G0 P1 G1

Cn

Cn+x Cn+y Cn+z

Pin Names

Cn Carry Input

G0, G

2

G

1

G

3

P0, P

1

P

2

P

3

C

to C

n + x

n + z

G Carry Generate Output (Active Low)

P Carry Propagate Output (Active Low)

Carry Generate Inputs (Active Low)

Carry Generate Input (Active Low)

Carry Generate Input (Active Low)

Carry Propagate Inputs (Active Low)

Carry Propagate Input (Active Low)

Carry Propagate Input (Active Low)

Carry Outputs

P2 G2

P3 G3

G

P

2

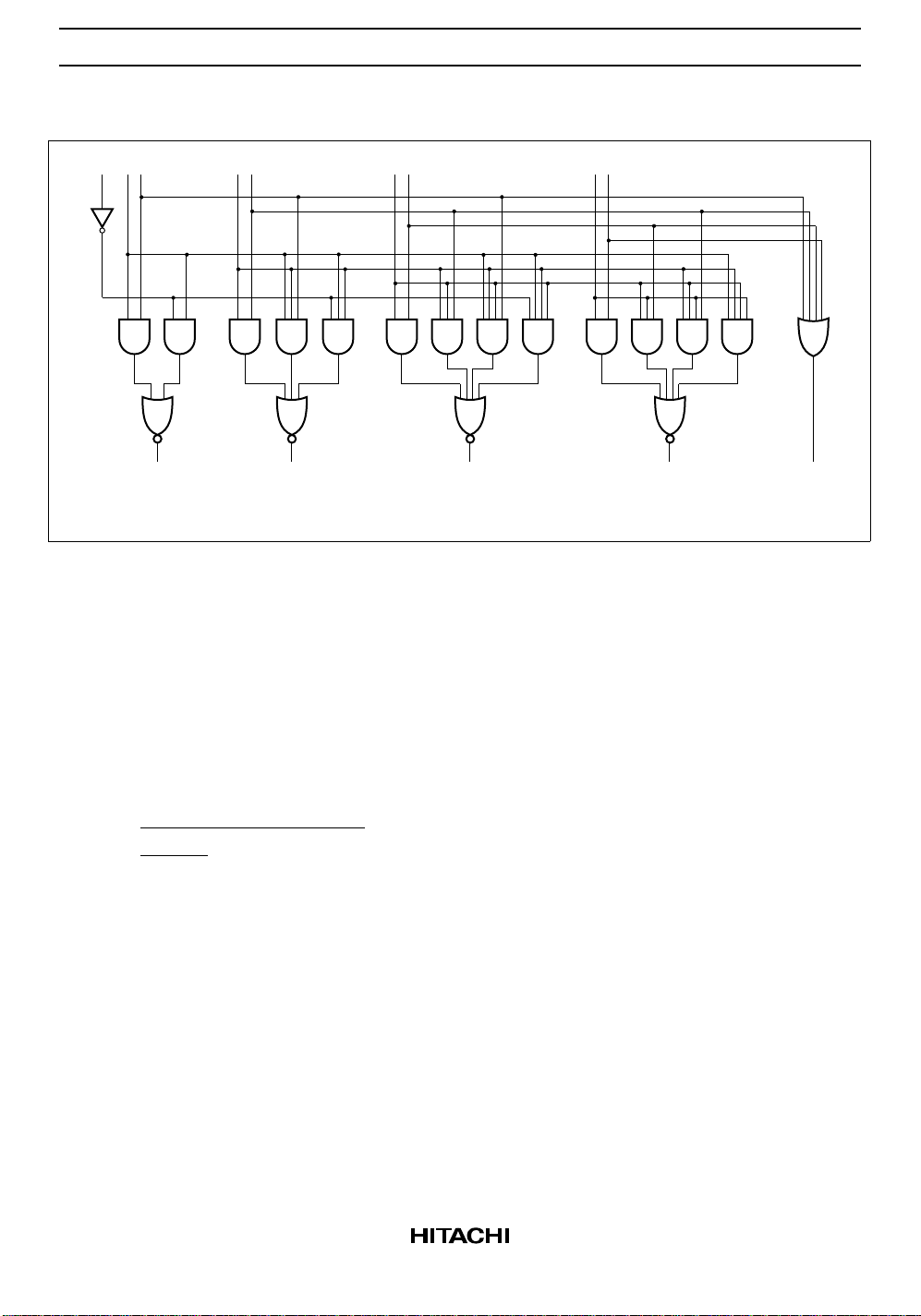

Logic Diagram

Cn

G0 P0 G1

HD74AC182/HD74ACT182

P1 G2P2 G3P3

Cn+x Cn+y Cn+z

GP

Please note that this diagram is provided only for the understanding of logic operations and should not be

used to estimate propagation delays.

Functional Description

The HD74AC182/HD74ACT182 carry lookahead generator accepts up to four pairs of Active Low Carry

Propagate (P0 to P3) and Carry Generate (G0 to G3) signals and an Active High Carry input (Cn) and

provides anticipated Active High carries (C

HD74AC182/HD74ACT182 also has Active Low Carry Propagate ( P) and Carry Generate (G) outputs

which may be used for further level of lookahead. The logic equations provided at the outputs are:

C

= G0 + P0C

n + x

C

= G1 + P1G0 + P1P0C

n + y

C

= G2 + P2G1 + P2P1G0 + P2P1P0C

n + z

G= G3 + P3G2 + P3P2G1 + P3P2P1G

P= P3P2P1P

n

n

n

0

0

Also, the HD74AC182/HD74ACT182 can be used with binary ALUs in an active Low or active High input

operand mode. The connections (Figure a) to and from the ALU to the carry lookahead generator are

identical in both cases. Carries are rippled between lookahead blocks. The critical speed path follows the

circled numbers. There are several possible arrangements for the carry interconnects, but all achieve about

the same speed. A 28-bit ALU is formed by dropping the last HD74AC182/HD74ACT182.

n + x

, C

n + y

, C

) across four groups of binary adders. The

n + z

3

HD74AC182/HD74ACT182

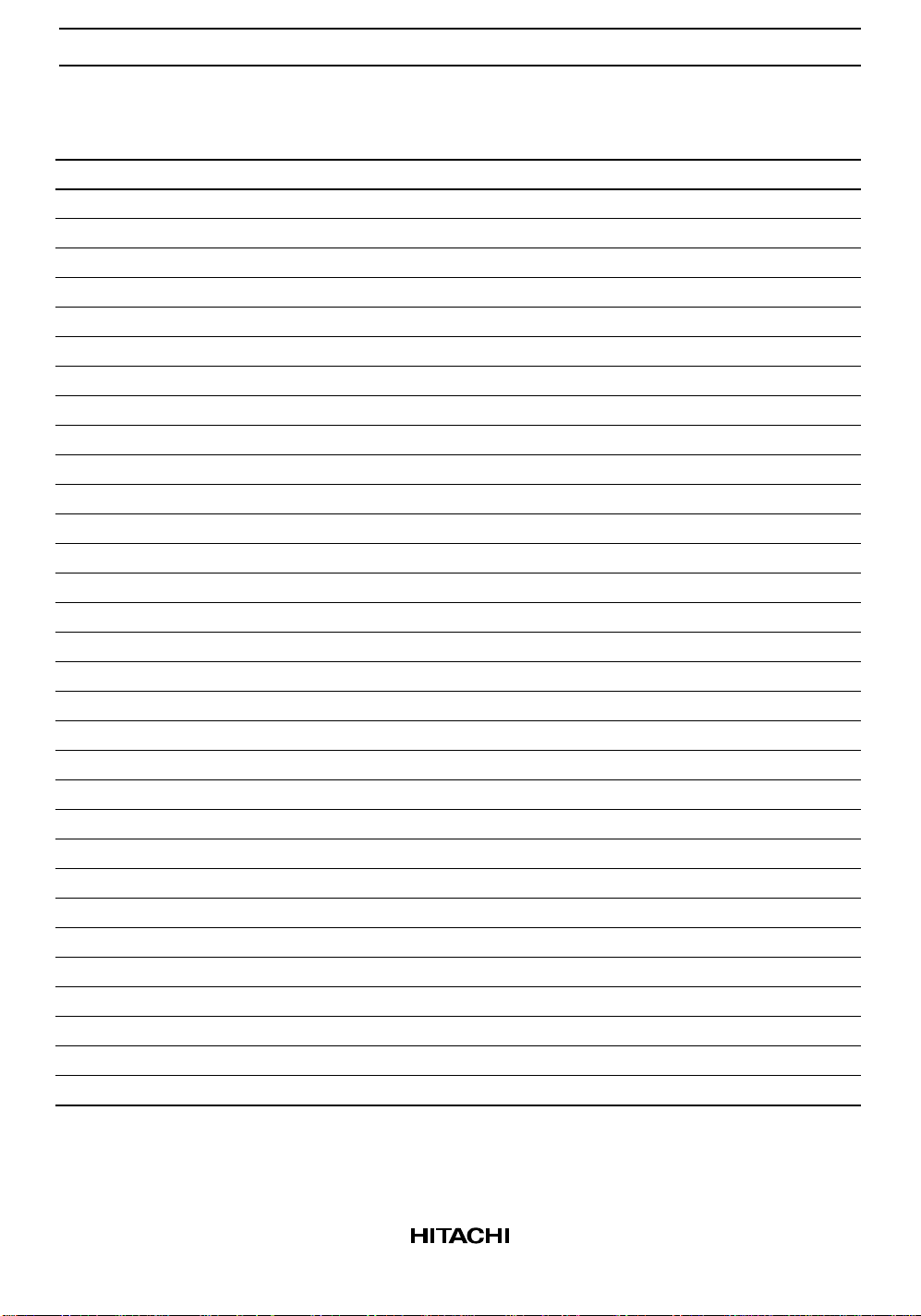

Truth Table

Inputs Outputs

G

C

n

XH H L

LH X L

XL X H

HX L H

XXXHH L

XHHHX L

LH X H X L

XXXLX H

XL X X L H

HX L X L H

XXXXXHH L

XXXHHHX L

XHHHXHX L

LHXHXHX L

XXXXXLX H

XXXLXXL H

XL X X L X L H

HXLXLXL H

X XXXXHH H

XXXHHHX H

X HHHXHX H

HHXHXHX H

X XXXXLX L

XXXLXXL L

X LXXLXL L

LXLXLXL L

H : High Voltage Level

L : Low Voltage Level

X : Immaterial

P

0

G

0

P

1

G

1

P

2

G

2

P

3

C

3

n + xCn + y

C

GP

n + z

HXXX H

XHXX H

XXHX H

XXXH H

LLLL L

4

Loading...

Loading...