HD74AC123A

Dual Retriggerable Resettable Multivibrator

Description

Each half of the HD74AC123A features retriggerable capability, complementary dc level triggering and

overriding Direct Clear. When a circuit is in the quasi-stable (delay) state, another trigger applied to the

inputs (per the Truth Table) will cause the delay period to start again, without disturbing the outputs. By

repeating this process, the output pulse period (Q High, Q Low) can be made as long as desired.

Alternatively, a delay period can be terminated at any time by a Low signal on CD, which also inhibits

triggering. An internal connection from CD to the input gate makes it possible to trigger the circuit by a

positive-going signal on CD, as shown in the Truth Table. For timing capacitor values greater than 1000

pF, the output pulse width is defined as follows.

Where tw is in ns, RX is in k and CX is in pF.

tw = RXC

X

Feature

• Outputs Source/Sink 24 mA

HD74AC123A

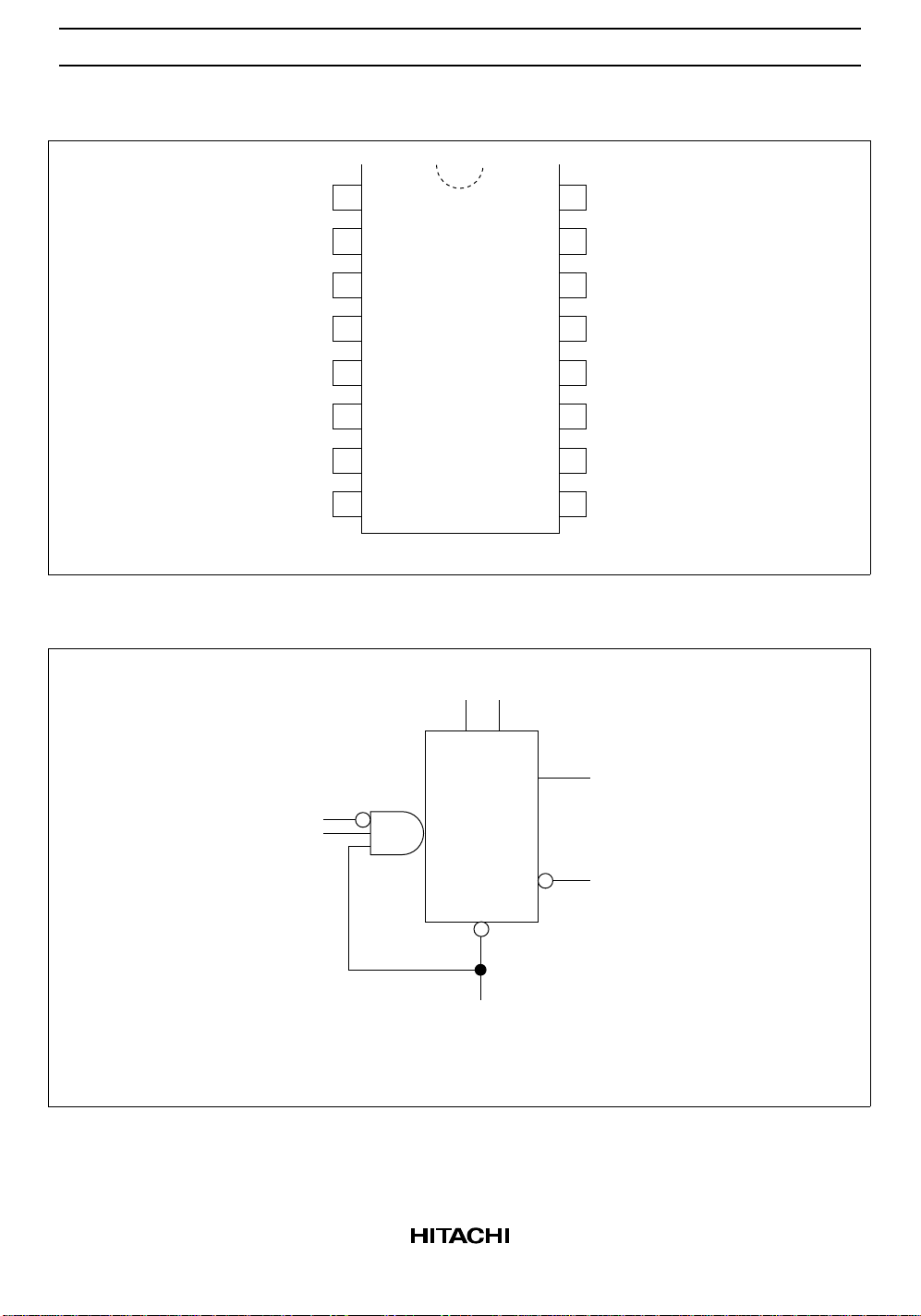

Pin Arrangement

A

1

1

16

V

CC

Logic Symbol

RX2C

GND

2

B

1

3

C

D1

4

Q

1

5

Q

2

6

C

X2

7

X2

8

15

14

13

12

11

10

9

RX1C

C

X1

Q

1

Q

2

C

D2

B

2

A

2

X1

(Top view)

7

6

(15)

(14)

R

XCX

C

X

5(13)

12(4)

9(1)

10(2)

Q

A

B

Q

C

D

11

(3)

V

= Pin16

CC

GND = Pin8

2

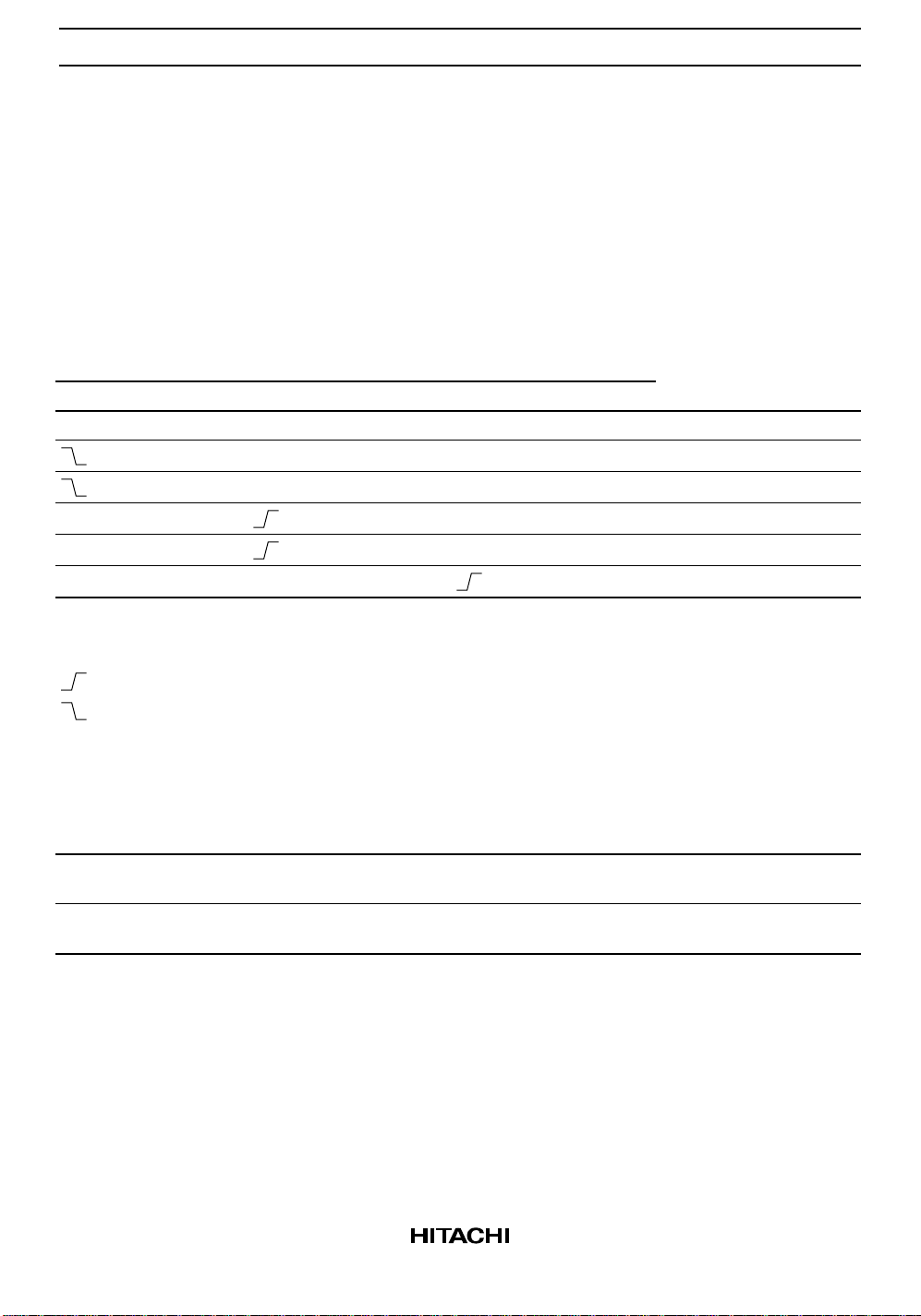

Pin Names

HD74AC123A

A1, A

B1, B

Trigger Inputs (Active Falling Edge)

2

Trigger Inputs (Active Rising Edge)

2

CD1, CD2Direct Clear Inputs (Active Low)

Q1, Q

Q1, Q

Positive Pulse Outputs

2

Negative Pulse Outputs

2

Triggering Truth Table

Inputs

AB C

D

X X L No trigger

L X No trigger

H H Trigger

H X No trigger

L H Trigger

LH Trigger

H : High Voltage Level

L : Low Voltage Level

X : Immaterial

: Low-to-High Transition

: High-to-Low Transition

Response

DC Characteristics (unless otherwise specified)

Item Symbol Max Unit Condition

Maximum quiescent supply current I

Maximum quiescent supply current I

CC

CC

80 µAV

8.0 µAV

= VCC or ground, VCC = 5.5 V,

IN

Ta = Worst case

= VCC or ground, VCC = 5.5 V,

IN

Ta = 25°C

3

Loading...

Loading...