H8/532 Hardware Manual

Preface

The H8/532 is a high-performance single-chip Hitachi-original microcomputer, featuring a highspeed CPU with 16-bit internal data paths and a full complement of on-chip supporting modules.

The H8/532 is an ideal microcontroller for a wide variety of medium-scale devices, including both

office and industrial equipment and consumer products.

Its highly orthogonal instruction set is designed for fast execution of programs coded in the highlevel C language.

On-chip facilities include large RAM and ROM memories, numerous timers, serial I/O, an A/D

converter, I/O ports, and other functions for compact implementation of high-performance

application systems.

The H8/532 is available in both a ZTAT version* with on-chip PROM, ideal for the early stages

of production or for products with frequently-changing specifications, and a masked-ROM version

suitable for volume production.

This manual gives a hardware description of the H8/532. For details of the instruction set, refer to

the H8/500 Series Programming Manual, which applies to all chips in the H8/500 Series.

* ZTAT (Zero Turn-Around Time) is a registered trademark of Hitachi, Ltd.

Contents

Section 1 Overview

1.1 Features ··································································································································1

1.2 Block Diagram ·······················································································································4

1.3 Pin Arrangements and Functions ···························································································5

1.3.1 Pin Arrangement ·········································································································5

1.3.2 Pin Functions ··············································································································8

Section 2 MCU Operating Modes and Address Space

2.1 Overview ······························································································································23

2.2 Mode Descriptions ···············································································································24

2.3 Address Space Map ··············································································································25

2.3.1 Page Segmentation ····································································································25

2.3.2 Page 0 Address Allocations ······················································································27

2.4 Mode Control Register (MDCR) ·························································································29

Section 3 CPU

3.1 Overview ······························································································································31

3.1.1 Features ·····················································································································31

3.1.2 Address Space ···········································································································32

3.1.3 Register Configuration ······························································································33

3.2 CPU Register Descriptions ··································································································34

3.2.1 General Registers ······································································································34

3.2.2 Control Registers ······································································································35

3.2.3 Initial Register Values ·······························································································40

3.3 Data Formats ························································································································41

3.3.1 Data Formats in General Registers ···········································································41

3.3.2 Data Formats in Memory ··························································································42

3.4 Instructions ···························································································································44

3.4.1 Basic Instruction Formats ·························································································44

3.4.2 Addressing Modes ····································································································45

3.4.3 Effective Address Calculation ···················································································47

3.5 Instruction Set ······················································································································50

3.5.1 Overview ···················································································································50

3.5.2 Data Transfer Instructions ·························································································52

3.5.3 Arithmetic Instructions ·····························································································53

3.5.4 Logic Operations ·······································································································54

3.5.5 Shift Operations ········································································································55

3.5.6 Bit Manipulations ······································································································56

3.5.7 Branching Instructions ······························································································57

3.5.8 System Control Instructions ······················································································59

3.5.9 Short-Format Instructions ·························································································62

3.6 Operating Modes ··················································································································62

3.6.1 Minimum Mode ········································································································62

3.6.2 Maximum Mode ········································································································63

3.7 Basic Operational Timing ····································································································63

3.7.1 Overview ···················································································································63

3.7.2 On-Chip Memory Access Cycle ···············································································64

3.7.3 Pin States during On-Chip Memory Access ·····························································65

3.7.4 Register Field Access Cycle (Addresses H'FF80 to H'FFFF) ···································66

3.7.5 Pin States during Register Field Access (Addresses H'FF80 to H'FFFF) ·················67

3.7.6 External Access Cycle ·······························································································68

3.8 CPU States ···························································································································69

3.8.1 Overview ···················································································································69

3.8.2 Program Execution State ···························································································71

3.8.3 Exception-Handling State ·························································································71

3.8.4 Bus-Released State ····································································································72

3.8.5 Reset State ·················································································································77

3.8.6 Power-Down State ····································································································77

3.9 Programming Notes ·············································································································78

3.9.1 Restriction on Address Location ···············································································78

3.9.2 Note on MULXU Instruction·····················································································79

Section 4 Exception Handling

4.1 Overview ······························································································································81

4.1.1 Types of Exception Handling and Their Priority ······················································81

4.1.2 Hardware Exception-Handling Sequence ·································································82

4.1.3 Exception Factors and Vector Table ··········································································82

4.2 Reset ····································································································································85

4.2.1 Overview ···················································································································85

4.2.2 Reset Sequence ·········································································································85

4.2.3 Stack Pointer Initialization ························································································86

4.3 Address Error ·······················································································································89

4.3.1 Illegal Instruction Prefetch ························································································89

4.3.2 Word Data Access at Odd Address ···········································································89

4.3.3 Off-Chip Address Access in Single-Chip Mode ·······················································89

4.4 Trace ····································································································································90

4.5 Interrupts ······························································································································90

4.6 Invalid Instruction ················································································································92

4.7 Trap Instructions and Zero Divide ·······················································································92

4.8 Cases in Which Exception Handling is Deferred ·································································92

4.8.1 Instructions that Disable Interrupts ···········································································92

4.8.2 Disabling of Exceptions Immediately after a Reset ··················································93

4.8.3 Disabling of Interrupts after a Data Transfer Cycle ··················································93

4.9 Stack Status after Completion of Exception Handling ························································94

4.9.1 PC Value Pushed on Stack for Trace,

Interrupts, Trap Instructions, and Zero Divide Exceptions ·······································96

4.9.2 PC Value Pushed on Stack for Address Error and Invalid

Instruction Exceptions ······························································································96

4.10 Notes on Use of the Stack ····································································································96

Section 5 Interrupt Controller

5.1 Overview ······························································································································97

5.1.1 Features ·····················································································································97

5.1.2 Block Diagram ··········································································································98

5.1.3 Register Configuration ······························································································99

5.2 Interrupt Types ·····················································································································99

5.2.1 External Interrupts ····································································································99

5.2.2 Internal Interrupts ····································································································101

5.2.3 Interrupt Vector Table ·····························································································101

5.3 Register Descriptions ·········································································································103

5.3.1 Interrupt Priority Registers A to D (IPRA to IPRD) ···············································103

5.3.2 Timing of Priority Setting ·······················································································104

5.4 Interrupt Handling Sequence ·····························································································104

5.4.1 Interrupt Handling Flow ··························································································104

5.4.2 Stack Status after Interrupt Handling Sequence ·····················································107

5.4.3 Timing of Interrupt Exception-Handling Sequence ················································108

5.5 Interrupts During Operation of the Data Transfer Controller ············································108

5.6 Interrupt Response Time ····································································································111

Section 6 Data Transfer Controller

6.1 Overview ····························································································································113

6.1.1 Features ···················································································································113

6.1.2 Block Diagram ········································································································113

6.1.3 Register Configuration ····························································································114

6.2 Register Descriptions ·········································································································115

6.2.1 Data Transfer Mode Register (DTMR) ···································································115

6.2.2 Data Transfer Source Address Register (DTSR) ····················································116

6.2.3 Data Transfer Destination Register (DTDR) ·························································116

6.2.4 Data Transfer Count Register (DTCR) ···································································116

6.2.5 Data Transfer Enable Registers A to D (DTEA to DTED) ·····································117

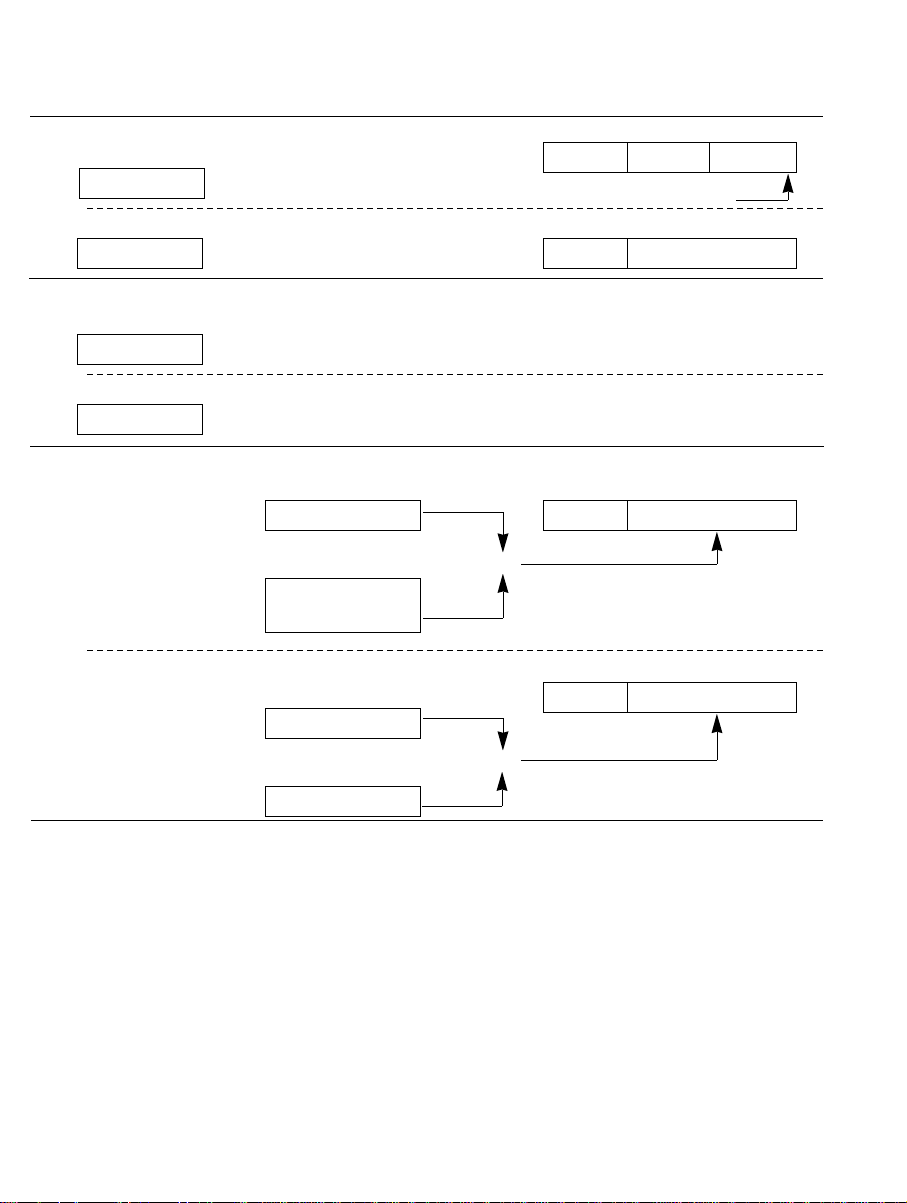

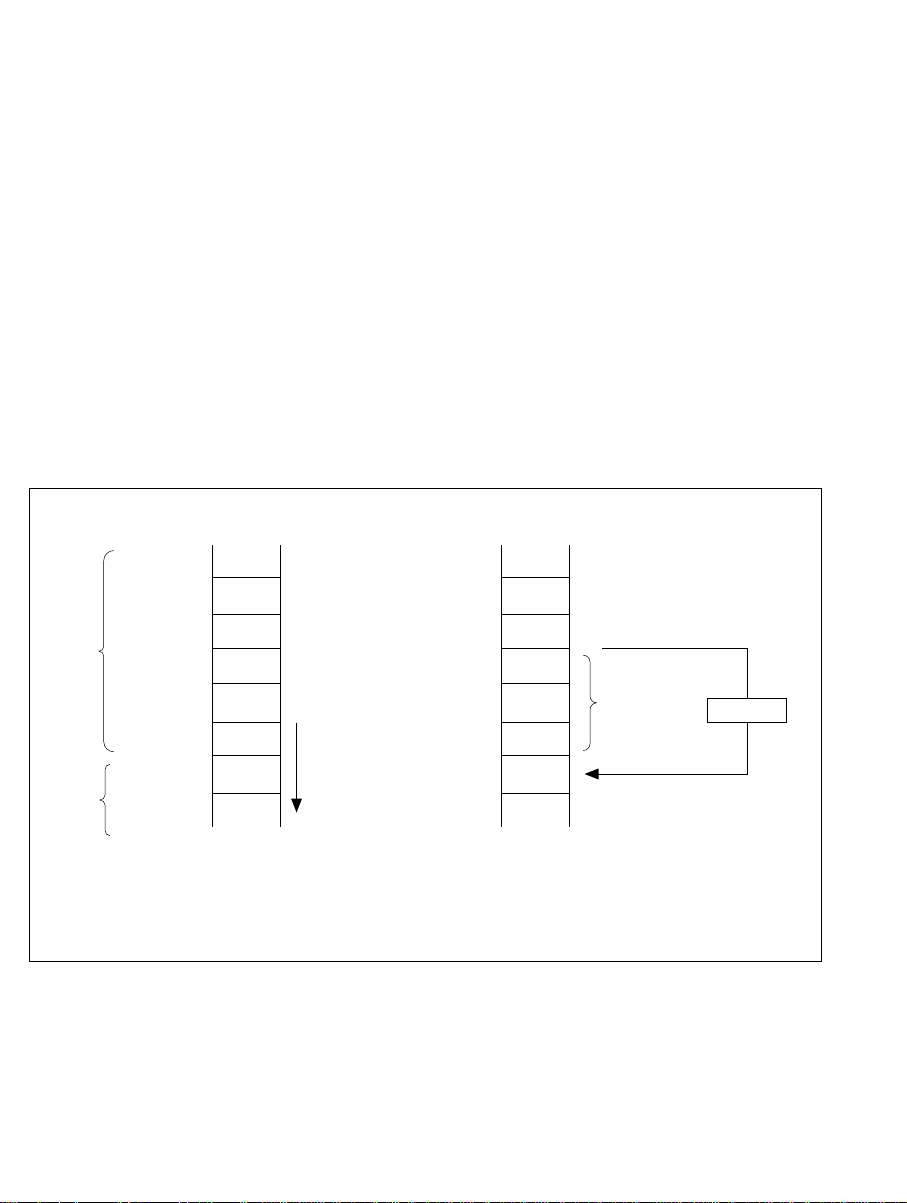

6.3 Data Transfer Operation ·····································································································118

6.3.1 Data Transfer Cycle ································································································118

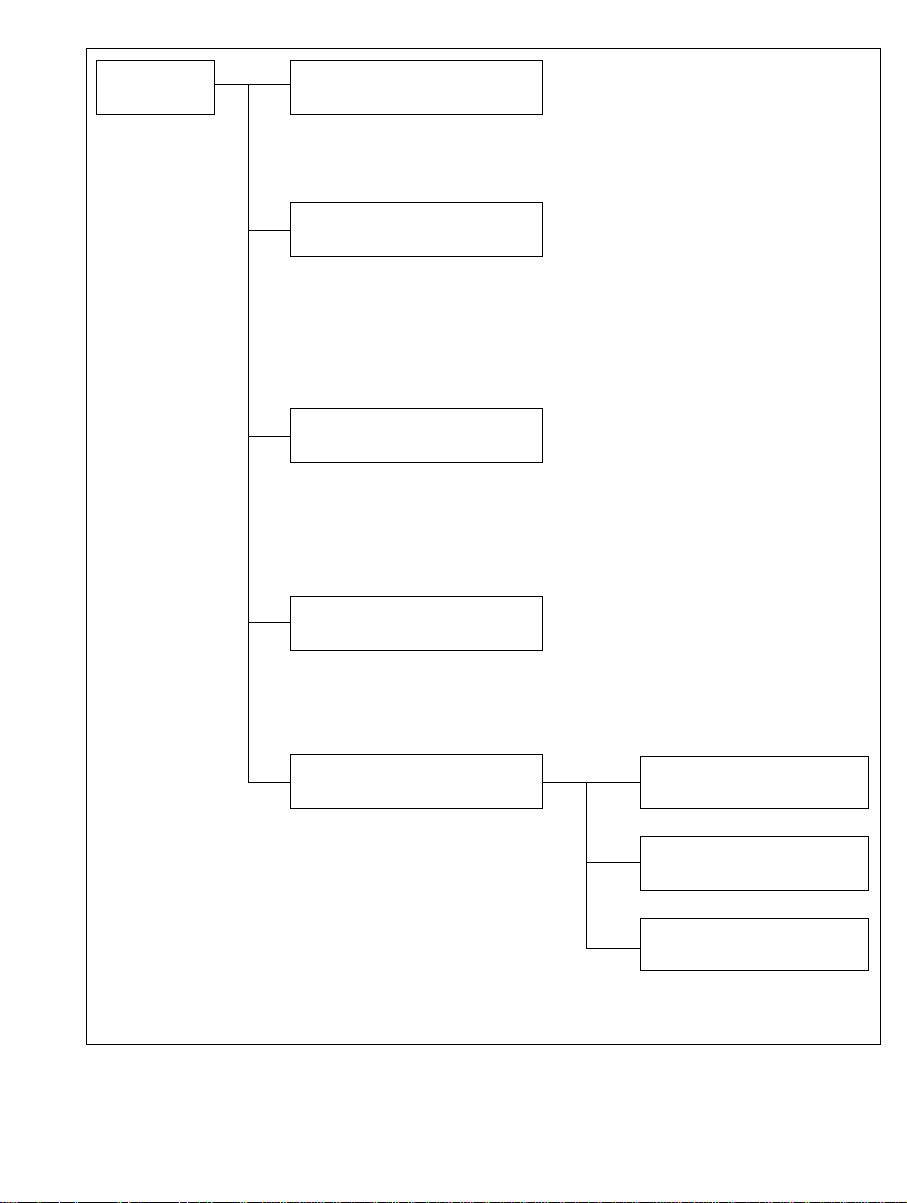

6.3.2 DTC Vector Table ···································································································120

6.3.3 Location of Register Information in Memory ·························································122

6.3.4 Length of Data Transfer Cycle ················································································122

6.4 Procedure for Using the DTC ····························································································124

6.5 Example ·····························································································································125

Section 7 Wait-State Controller

7.1 Overview ····························································································································127

7.1.1 Features ···················································································································127

7.1.2 Block Diagram ········································································································128

7.1.3 Register Configuration ····························································································128

7.2 Wait-State Control Register ·······························································································129

7.3 Operation in Each Wait Mode ····························································································130

7.3.1 Programmable Wait Mode ······················································································130

7.3.2 Pin Wait Mode ········································································································131

7.3.3 Pin Auto-Wait Mode ·······························································································133

Section 8 Clock Pulse Generator

8.1 Overview ····························································································································135

8.1.1 Block Diagram ········································································································135

8.2 Oscillator Circuit ················································································································135

8.3 System Clock Divider ········································································································138

Section 9 I/O Ports

9.1 Overview ····························································································································139

9.2 Port 1 ··································································································································142

9.2.1 Overview ·················································································································142

9.2.2 Port 1 Registers ·······································································································142

9.2.3 Pin Functions in Each Mode ···················································································145

9.3 Port 2 ··································································································································148

9.3.1 Overview ·················································································································148

9.3.2 Port 2 Registers ·······································································································149

9.3.3 Pin Functions in Each Mode ···················································································150

9.4 Port 3 ··································································································································151

9.4.1 Overview ·················································································································151

9.4.2 Port 3 Registers ·······································································································152

9.4.3 Pin Functions in Each Mode ···················································································153

9.5 Port 4 ··································································································································154

9.5.1 Overview ·················································································································154

9.5.2 Port 4 Registers ·······································································································155

9.5.3 Pin Functions in Each Mode ···················································································156

9.6 Port 5 ··································································································································157

9.6.1 Overview ·················································································································157

9.6.2 Port 5 Registers ·······································································································158

9.6.3 Pin Functions in Each Mode ···················································································159

9.6.4 Built-in MOS Pull-Up ·····························································································161

9.7 Port 6 ··································································································································163

9.7.1 Overview ·················································································································163

9.7.2 Port 6 Registers ·······································································································164

9.7.3 Pin Functions in Each Mode ···················································································165

9.7.4 Built-in MOS Pull-Up ·····························································································167

9.8 Port 7 ··································································································································167

9.8.1 Overview ·················································································································167

9.8.2 Port 7 Registers ·······································································································168

9.8.3 Pin Functions ··········································································································169

9.9 Port 8 ··································································································································172

9.9.1 Overview ·················································································································172

9.9.2 Port 8 Registers ·······································································································172

9.10 Port 9 ··································································································································173

9.10.1 Overview ·················································································································173

9.10.2 Port 9 Registers ·······································································································173

9.10.3 Pin Functions ··········································································································174

Section 10 16-Bit Free-Running Timers

10.1 Overview ····························································································································177

10.1.1 Features ···················································································································177

10.1.2 Block Diagram ········································································································178

10.1.3 Input and Output Pins ·····························································································179

10.1.4 Register Configuration ····························································································180

10.2 Register Descriptions ·········································································································181

10.2.1 Free-Running Counter (FRC) - H'FF92, H'FFA2, H'FFB2 ····································181

10.2.2 Output Compare Registers A and B (OCRA and OCRB) - H'FF94

and H'FF96, H'FFA4 and H'FFA6, H'FFB4 and H'FFB6 ·······································182

10.2.3 Input Capture Register (ICR) - H'FF98, H'FFA8, H'FFB8 ·····································182

10.2.4 Timer Control Register (TCR) ················································································183

10.2.5 Timer Control/Status Register (TCSR) ···································································185

10.3 CPU Interface ·····················································································································188

10.4 Operation ····························································································································190

10.4.1 FRC Incrementation Timing ···················································································190

10.4.2 Output Compare Timing ·························································································191

10.4.3 Input Capture Timing ······························································································193

10.4.4 Setting of FRC Overflow Flag (OVF) ·····································································195

10.5 CPU Interrupts and DTC Interrupts ···················································································195

10.6 Synchronization of Free-Running Timers 1 to 3 ································································196

10.6.1 Synchronization after a Reset ·················································································196

10.6.2 Synchronization by Writing to FRCs ······································································196

10.7 Sample Application ············································································································200

10.8 Application Notes ··············································································································200

Section 11 8-Bit Timer

11.1 Overview ····························································································································207

11.1.1 Features ···················································································································207

11.1.2 Block Diagram ········································································································208

11.1.3 Input and Output Pins ·····························································································209

11.1.4 Register Configuration ····························································································209

11.2 Register Descriptions ·········································································································209

11.2.1 Timer Counter (TCNT) - H'FFD4 ···········································································209

11.2.2 Time Constant Registers A and B

(TCORA and TCORB) - H'FFD2 and H'FFD3 ······················································210

11.2.3 Timer Control Register (TCR) - H'FFD0 ································································210

11.2.4 Timer Control/Status Register (TCSR) ···································································212

11.3 Operation ····························································································································214

11.3.1 TCNT Incrementation Timing ················································································214

11.3.2 Compare Match Timing ··························································································215

11.3.3 External Reset of TCNT ·························································································217

11.3.4 Setting of TCNT Overflow Flag ·············································································218

11.4 CPU Interrupts and DTC Interrupts ···················································································218

11.5 Sample Application ············································································································219

11.6 Application Notes ··············································································································220

Section 12 PWM Timer

12.1 Overview ····························································································································227

12.1.1 Features ···················································································································227

12.1.2 Block Diagram ········································································································227

12.1.3 Input and Output Pins ·····························································································228

12.1.4 Register Configuration ····························································································229

12.2 Register Descriptions ·········································································································229

12.2.1 Timer Counter (TCNT) - H'FFC2, H'FFC4, H'FFCA ············································229

12.2.2 Duty Register (DTR) - H'FFC1, H'FFC5, H'FFC9 ·················································230

12.2.3 Timer Control Register (TCR) - H'FFC0, H'FFC4, H'FFC8 ··································230

12.3 Operation ····························································································································232

12.4 Application Notes ··············································································································234

Section 13 Watchdog Timer

13.1 Overview ····························································································································235

13.1.1 Features ···················································································································235

13.1.2 Block Diagram ········································································································236

13.1.3 Register Configuration ····························································································236

13.2 Register Descriptions ·········································································································237

13.2.1 Timer Counter TCNT - H'FFED ·············································································237

13.2.2 Timer Control/Status Register (TCSR) - H'FFEC (Read), H'FFED (Write) ··········237

13.2.3 Notes on Register Access ························································································239

13.3 Operation ····························································································································240

13.3.1 Watchdog Timer Mode ···························································································240

13.3.2 Interval Timer Mode ·······························································································241

13.3.3 Operation in Software Standby Mode ·····································································242

13.3.4 Setting of Overflow Flag ·························································································243

13.4 Application Notes ··············································································································243

Section 14 Serial Communication Interface

14.1 Overview ····························································································································245

14.1.1 Features ···················································································································245

14.1.2 Block Diagram ········································································································246

14.1.3 Input and Output Pins ·····························································································247

14.1.4 Register Configuration ····························································································247

14.2 Register Descriptions ·········································································································247

14.2.1 Receive Shift Register (RSR) ··················································································247

14.2.2 Receive Data Register (RDR) - H'FFDD ································································248

14.2.3 Transmit Shift Register (TSR) ················································································248

14.2.4 Transmit Data Register (TDR) - H'FFDB ·······························································248

14.2.5 Serial Mode Register (SMR) - H'FFD8 ··································································249

14.2.6 Serial Control Register (SCR) - H'FFDA ·······························································251

14.2.7 Serial Status Register (SSR) - H'FFDC ··································································253

14.2.8 Bit Rate Register (BRR) - H'FFD9 ·········································································255

14.3 Operation ····························································································································259

14.3.1 Overview ·················································································································259

14.3.2 Asynchronous Mode ·······························································································260

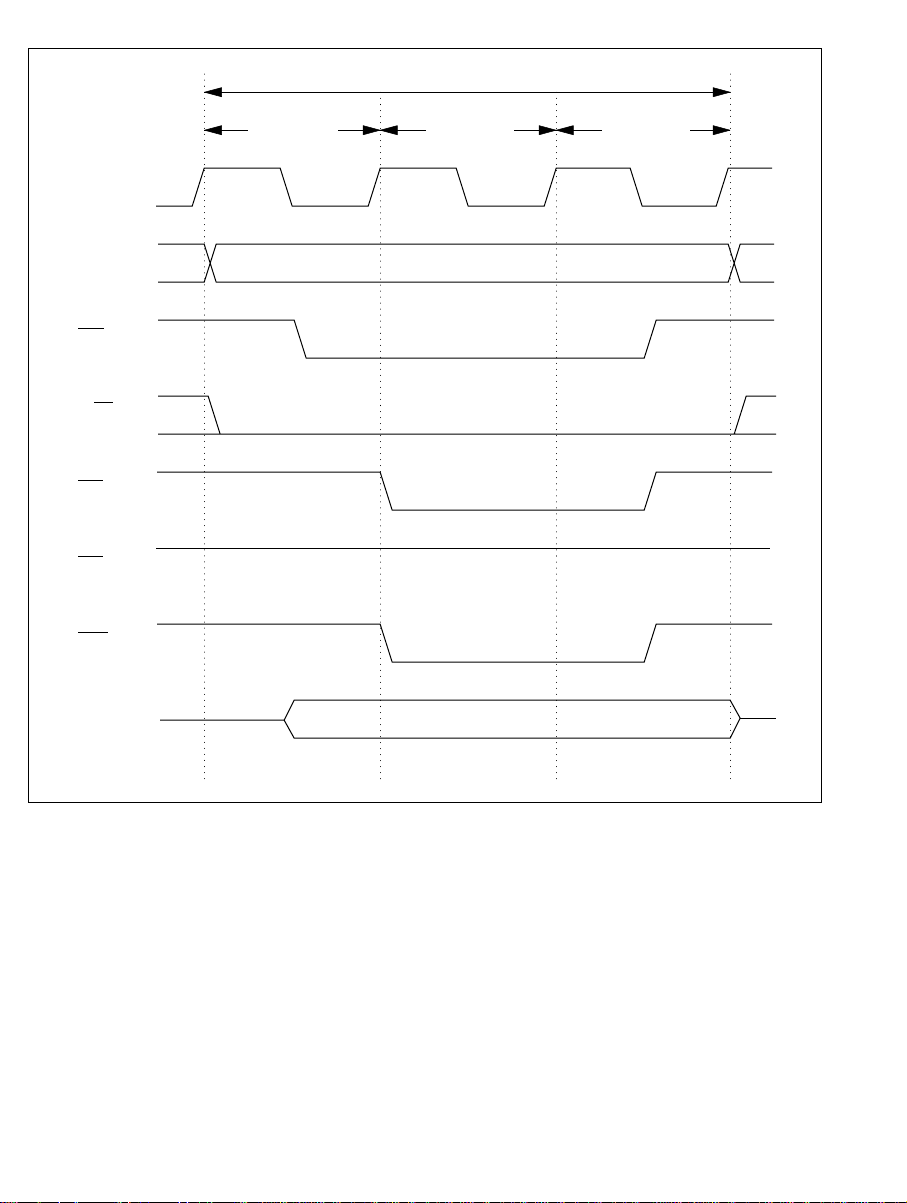

14.3.3 Synchronous Mode ·································································································264

14.4 CPU Interrupts and DTC Interrupts ···················································································268

14.5 Application Notes ··············································································································269

Section 15 A/D Converter

15.1 Overview ····························································································································273

15.1.1 Features ···················································································································273

15.1.2 Block Diagram ········································································································274

15.1.3 Input Pins ················································································································275

15.1.4 Register Configuration ····························································································275

15.2 Register Descriptions ·········································································································276

15.2.1 A/D Data Registers (ADDR) - H'FFE0 to H'FFE7 ·················································276

15.2.2 A/D Control/Status Register (ADCSR) - H'FFE8 ··················································277

15.3 CPU Interface ·····················································································································279

15.4 Operation ····························································································································280

15.4.1 Single Mode ············································································································281

15.4.2 Scan Mode ··············································································································284

15.5 Input Sampling Time and A/D Conversion Time ·······························································287

15.6 Interrupts and the Data Transfer Controller ·······································································289

Section 16 RAM

16.1 Overview ····························································································································291

16.1.1 Block Diagram ········································································································291

16.1.2 Register Configuration ····························································································292

16.2 RAM Control Register (RAMCR) ·····················································································292

16.3 Operation ····························································································································292

16.3.1 Expanded Modes (Modes 1, 2, 3, and 4) ································································292

16.3.2 Single-Chip Mode (Mode 7) ···················································································293

Section 17 ROM

17.1 Overview ····························································································································295

17.1.1 Block Diagram ········································································································295

17.2 PROM Modes ·····················································································································296

17.2.1 PROM Mode Setup ·································································································296

17.2.2 Socket Adapter Pin Arrangements and Memory Map ············································297

17.3 Programming ······················································································································299

17.3.1 Writing and Verifying ·····························································································299

17.3.2 Notes on Writing ·····································································································302

17.3.3 Reliability of Written Data ······················································································303

17.3.4 Erasing of Data ·······································································································304

17.4 Handling of Windowed Packages ······················································································304

Section 18 Power-Down State

18.1 Overview ····························································································································307

18.2 Sleep Mode ························································································································308

18.2.1 Transition to Sleep Mode ························································································308

18.2.2 Exit from Sleep Mode ·····························································································308

18.3 Software Standby Mode ·····································································································308

18.3.1 Transition to Software Standby Mode ····································································308

18.3.2 Software Standby Control Register (SBYCR) ························································309

18.3.3 Exit from Software Standby Mode ·········································································310

18.3.4 Sample Application of Software Standby Mode ····················································310

18.3.5 Application Notes ···································································································311

18.4 Hardware Standby Mode ····································································································312

18.4.1 Transition to Hardware Standby Mode ···································································312

18.4.2 Recovery from Hardware Standby Mode ·······························································312

18.4.3 Timing Sequence of Hardware Standby Mode ·······················································313

Section 19 E Clock Interface

19.1 Overview ····························································································································315

Section 20 Electrical Specifications

20.1 Absolute Maximum Ratings ······························································································319

20.2 Electrical Characteristics ····································································································319

20.2.1 DC Characteristics ··································································································319

20.2.2 AC Characteristics ··································································································322

20.2.3 A/D Converter Characteristics ················································································326

20.3 MCU Operatinal Timing ····································································································326

20.3.1 Bus Timing ··············································································································327

20.3.2 Control Signal Timing ····························································································330

20.3.3 Clock Timing ··········································································································331

20.3.4 I/O Port Timing ·······································································································333

20.3.5 16-Bit Free-Running Timer Timing ········································································334

20.3.6 8-Bit Timer Timing ·································································································335

20.3.7 Pulse Width Modulation Timer Timing ··································································336

20.3.8 Serial Communication Interface Timing ·································································336

Appendix A Instructions

A.1 Instruction Set ····················································································································337

A.2 Instruction Codes ···············································································································342

A.3 Operation Code Map ··········································································································353

A.4 Instruction Execution Cycles ·····························································································358

A.4.1 Calculation of Instruction Execution States ····························································358

A.4.2 Tables of Instruction Execution Cycles ··································································359

Appendix B Register Field

B.1 Register Addresses and Bit Names ····················································································367

B.2 Register Descriptions ·········································································································372

Appendix C I/O Port Schematic Diagrams

C.1 Schematic Diagram of Port 1 ·····························································································407

C.2 Schematic Diagram of Port 2 ·····························································································413

C.3 Schematic Diagram of Port 3 ·····························································································414

C.4 Schematic Diagram of Port 4 ·····························································································415

C.5 Schematic Diagram of Port 5 ·····························································································416

C.6 Schematic Diagram of Port 6 ·····························································································417

C.7 Schematic Diagram of Port 7 ·····························································································418

C.8 Schematic Diagram of Port 8 ·····························································································423

C.9 Schematic Diagram of Port 9 ·····························································································424

Appendix D Memory Map ·································································································429

Appendix E Pin State

E.1 Port State of Each Pin State ·······························································································431

E.2 Pin Stattus in the Reset State ······························································································434

Appendix F

Timing of Entry to and Recovery from Hardware Standby Mode

········449

Appendix G Package Dimensions ····················································································451

Figures

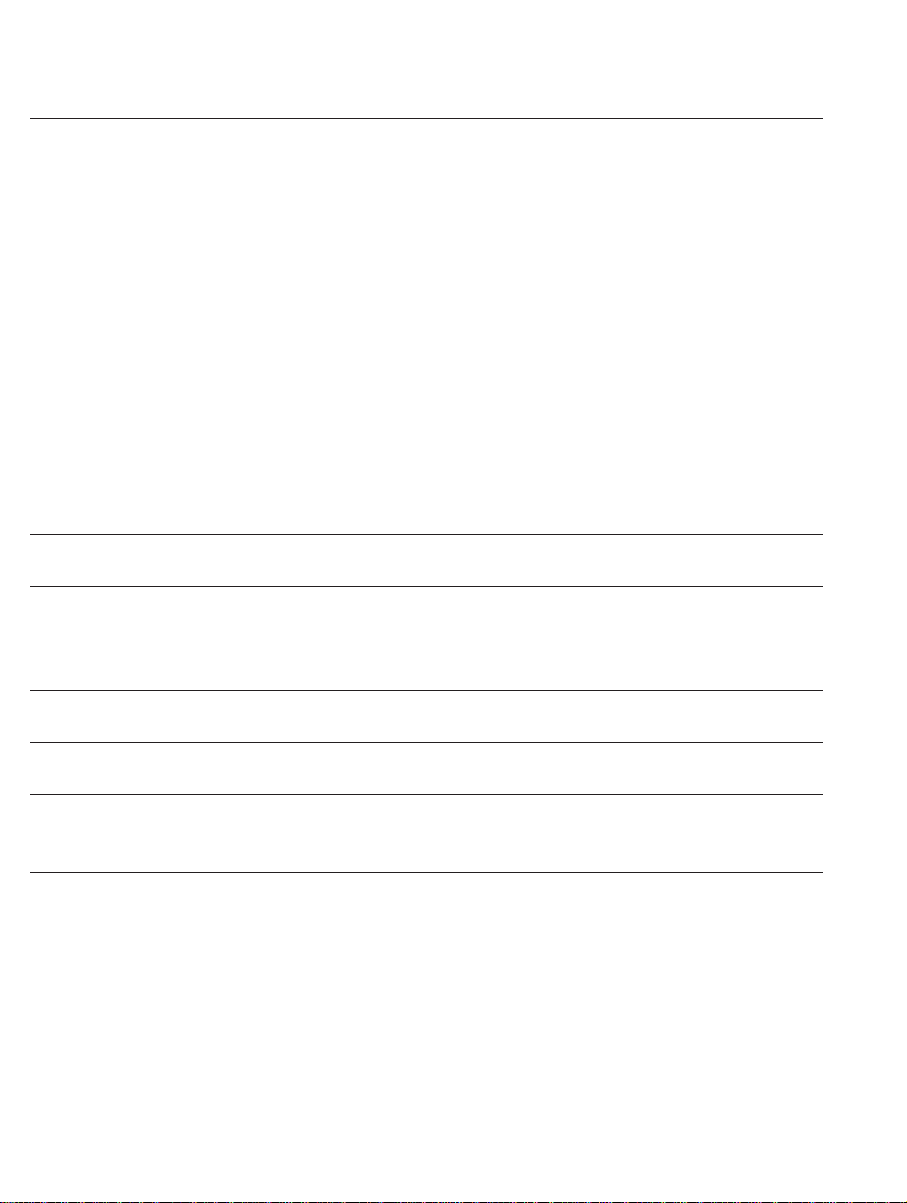

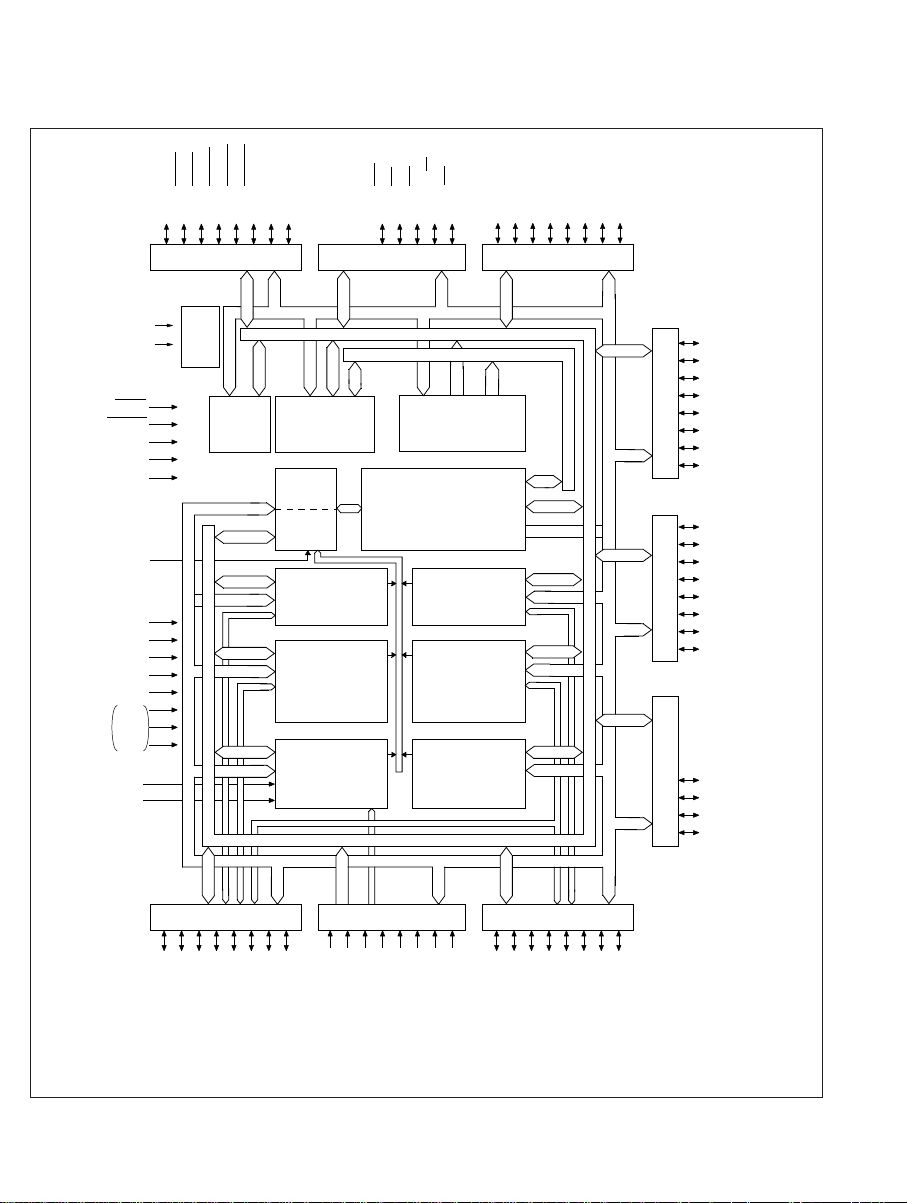

1-1 Block Diagram ···················································································································4

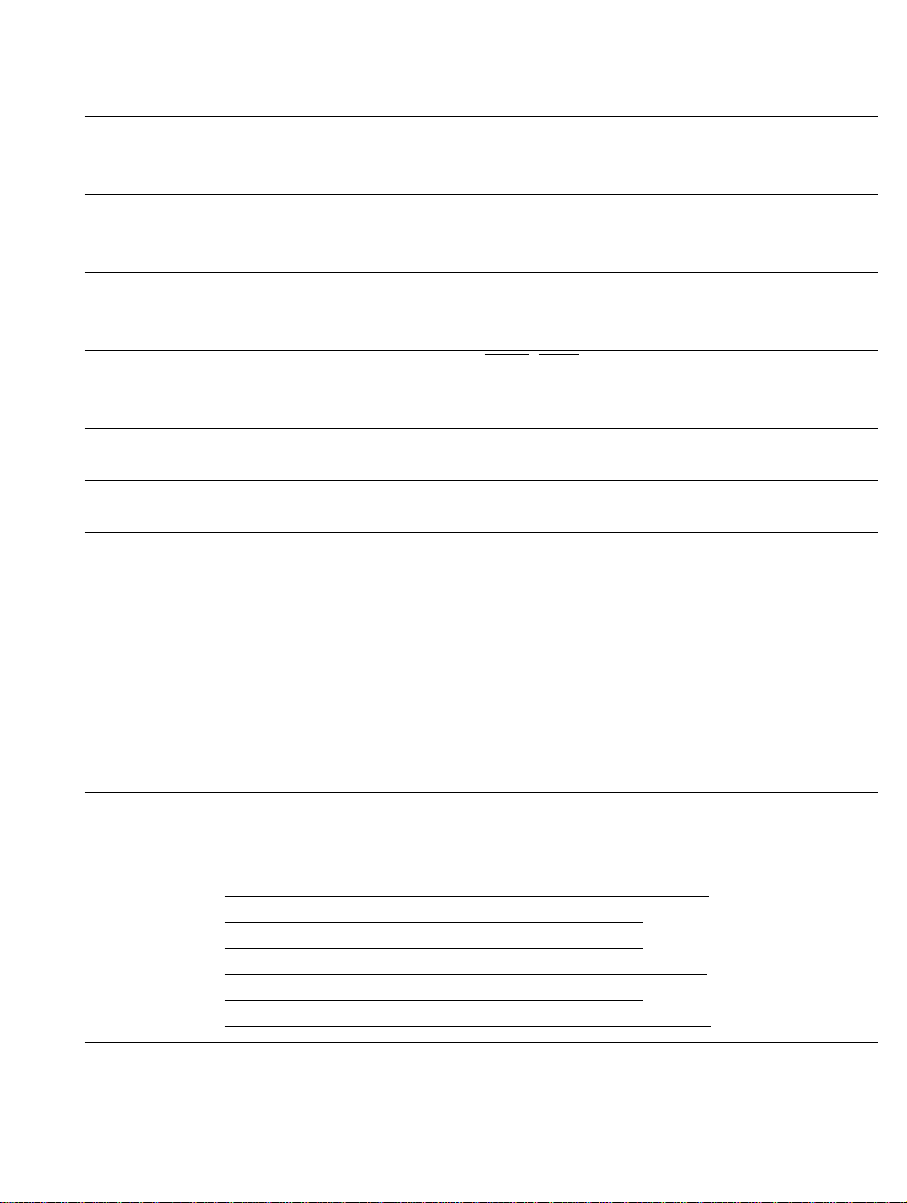

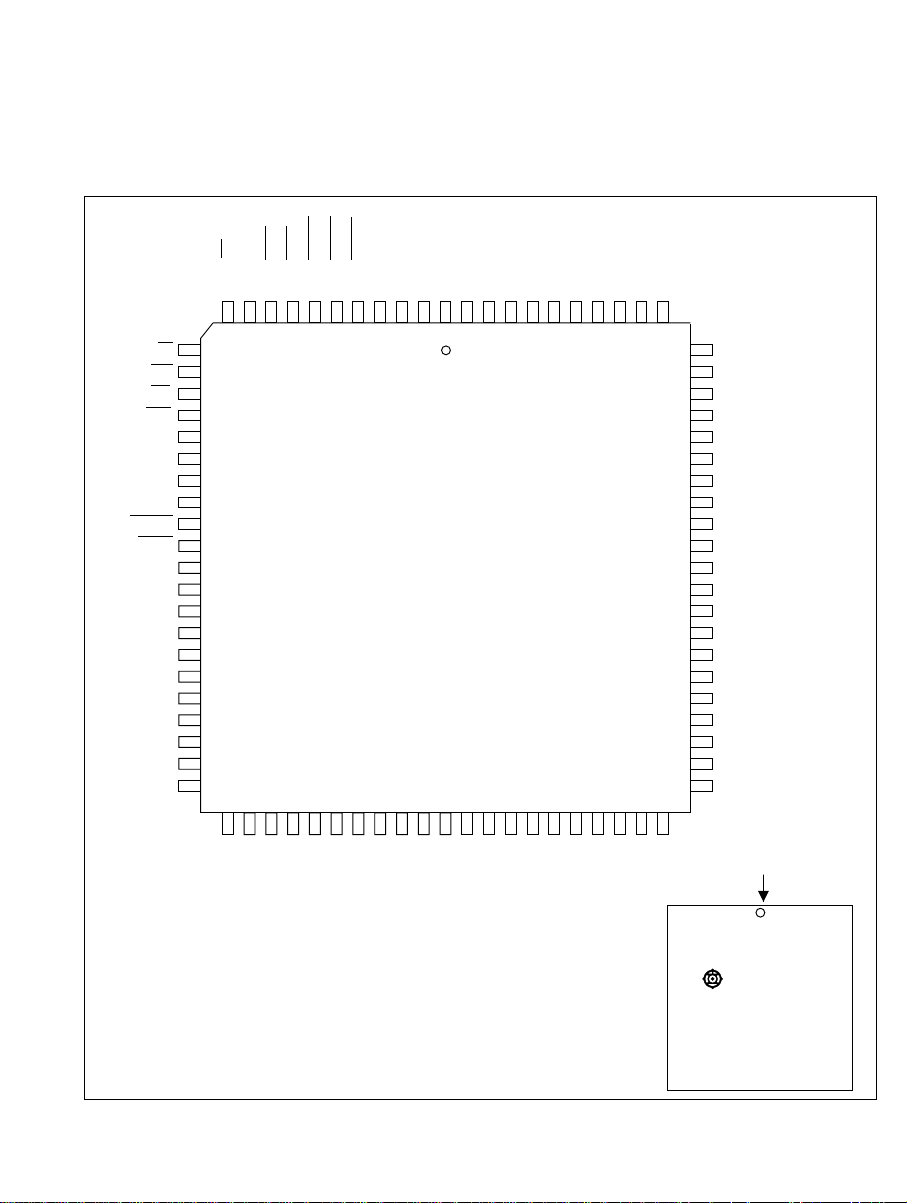

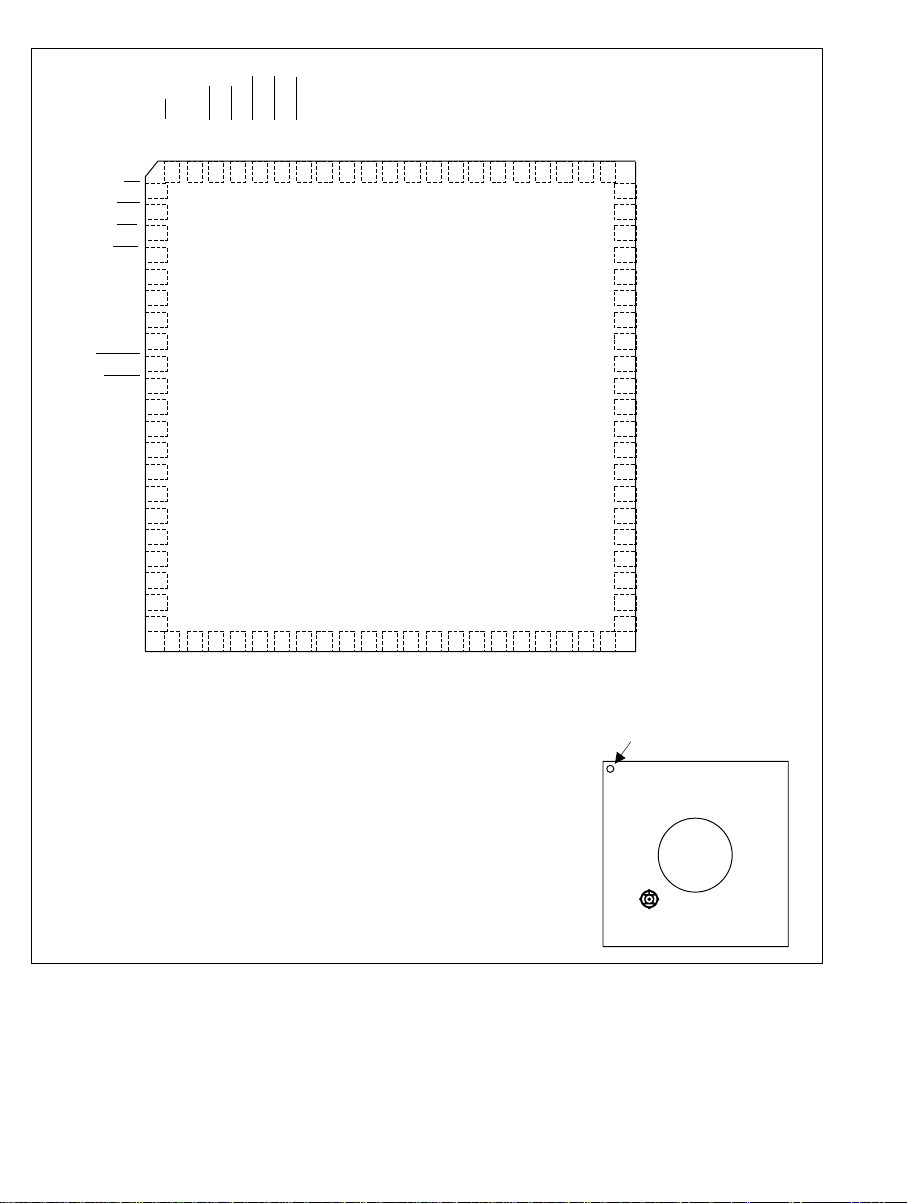

1-2 Pin Arrangement (CP-84, Top View) ·················································································5

1-3 Pin Arrangement (CG-84, Top View) ················································································6

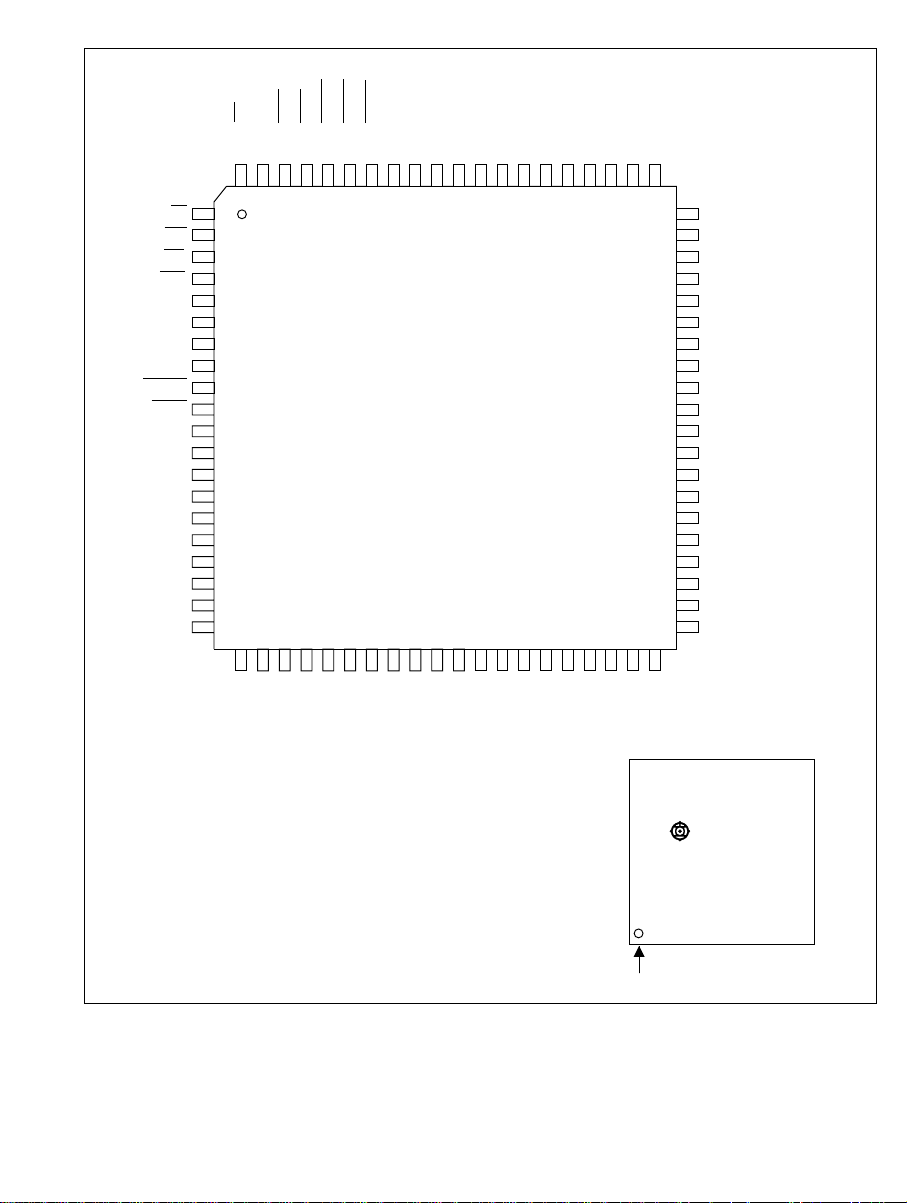

1-4 Pin Arrangement (FP-80A, Top View) ··············································································7

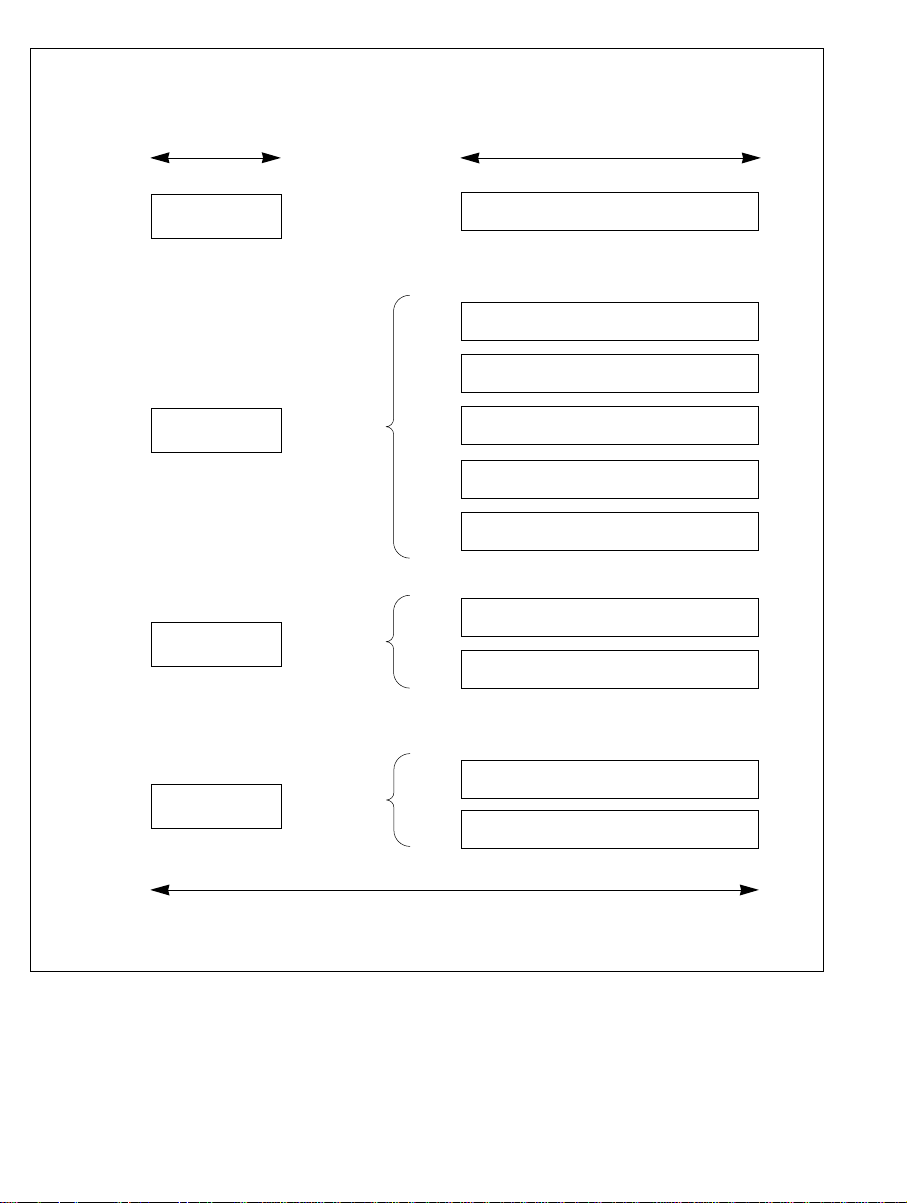

2-1 Address Space in Each Mode ··························································································26

2-2 Map of Page 0 ··················································································································28

3-1 CPU Operating Modes ·····································································································32

3-2 Registers in the CPU ········································································································33

3-3 Stack Pointer ····················································································································34

3-4 Combinations of Page Registers with Other Registers ····················································38

3-5 Short Absolute Addressing Mode and Base Register ······················································39

3-6 On-Chip Memory Access Timing ····················································································64

3-7 Pin States during Access to On-Chip Memory ································································65

3-8 Register Field Access Timing ··························································································66

3-9 Pin States during Register Field Access ··········································································67

3-10 (a) External Access Cycle (Read Access) ·············································································68

3-10 (b) External Access Cycle (Write Access) ············································································69

3-11 Operating States ···············································································································70

3-12 State Transitions ··············································································································71

3-13 Bus-Right Release Cycle (During On-chip Memory Access Cycle) ·······························73

3-14 Bus-Right Release Cycle (During External Access Cycle) ·············································74

3-15 Bus-Right Release Cycle (During Internal CPU Operation) ···········································75

4-1 Types of Factors Causing Exception Handling ································································83

4-2 Reset Vector ·····················································································································86

4-3 Reset Sequence (Minimum Mode, On-Chip Memory) ···················································87

4-4 Reset Sequence (Maximum Mode, External Memory) ···················································88

4-5 Interrupt Sources (and Number of Interrupt Types) ························································91

5-1 Interrupt Controller Block Diagram ················································································98

5-2 Interrupt Handling Flowchart ························································································106

5-3 (a) Stack before and after Interrupt Exception-Handling (Minimum Mode) ······················107

5-3 (b) Stack before and after Interrupt Exception-Handling (Maximum Mode) ·····················108

5-4 Interrupt Sequence (Minimum Mode, On-Chip Memory) ············································109

5-5 Interrupt Sequence (Maximum Mode, External Memory) ············································110

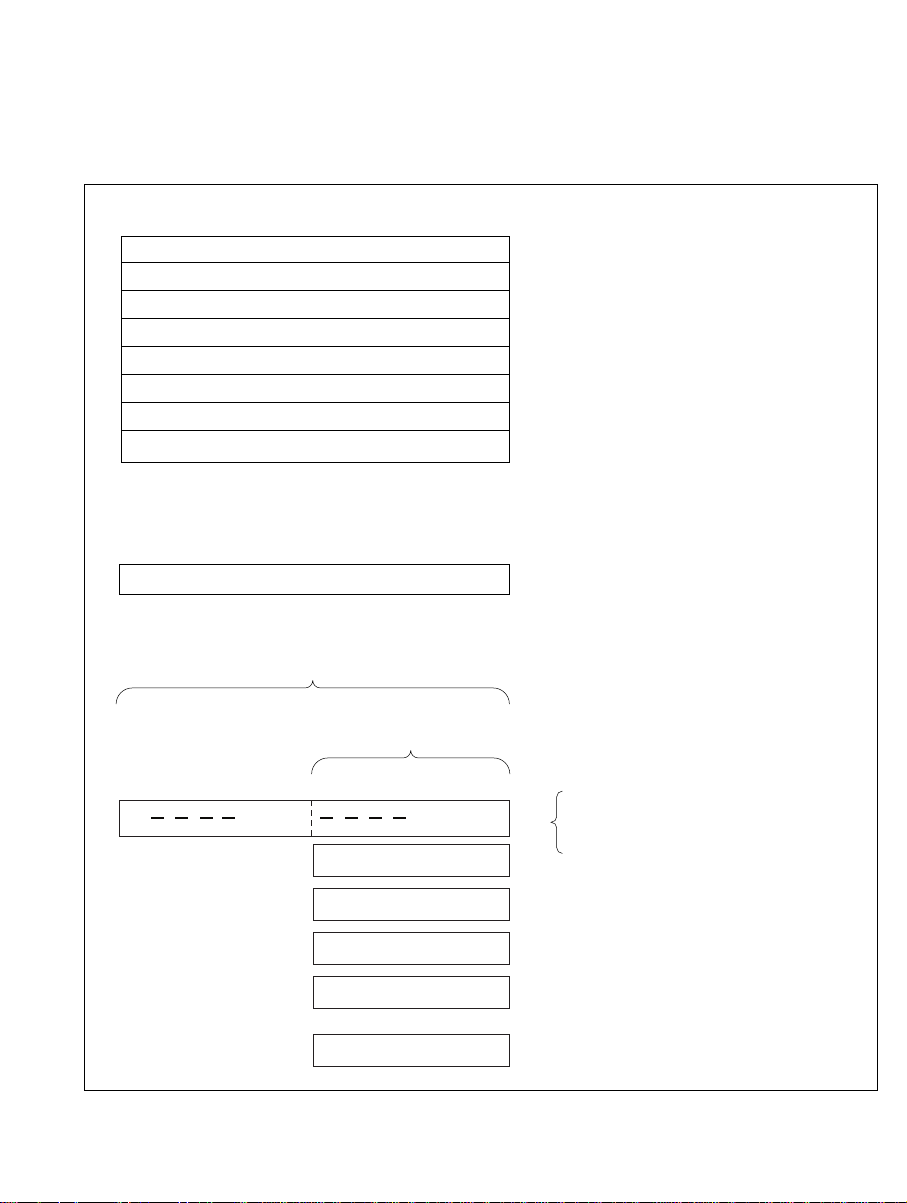

6-1 Block Diagram of Data Transfer Controller ··································································114

6-2 Flowchart of Data Transfer Cycle ··················································································119

6-3 DTC Vector Table ··········································································································120

6-4 DTC Vector Table Entry ································································································121

6-5 Order of Register Information ·······················································································122

6-6 Use of DTC to Receive Data via Serial Communication Interface ·······························126

7-1 Block Diagram of Wait-State Controller ·······································································128

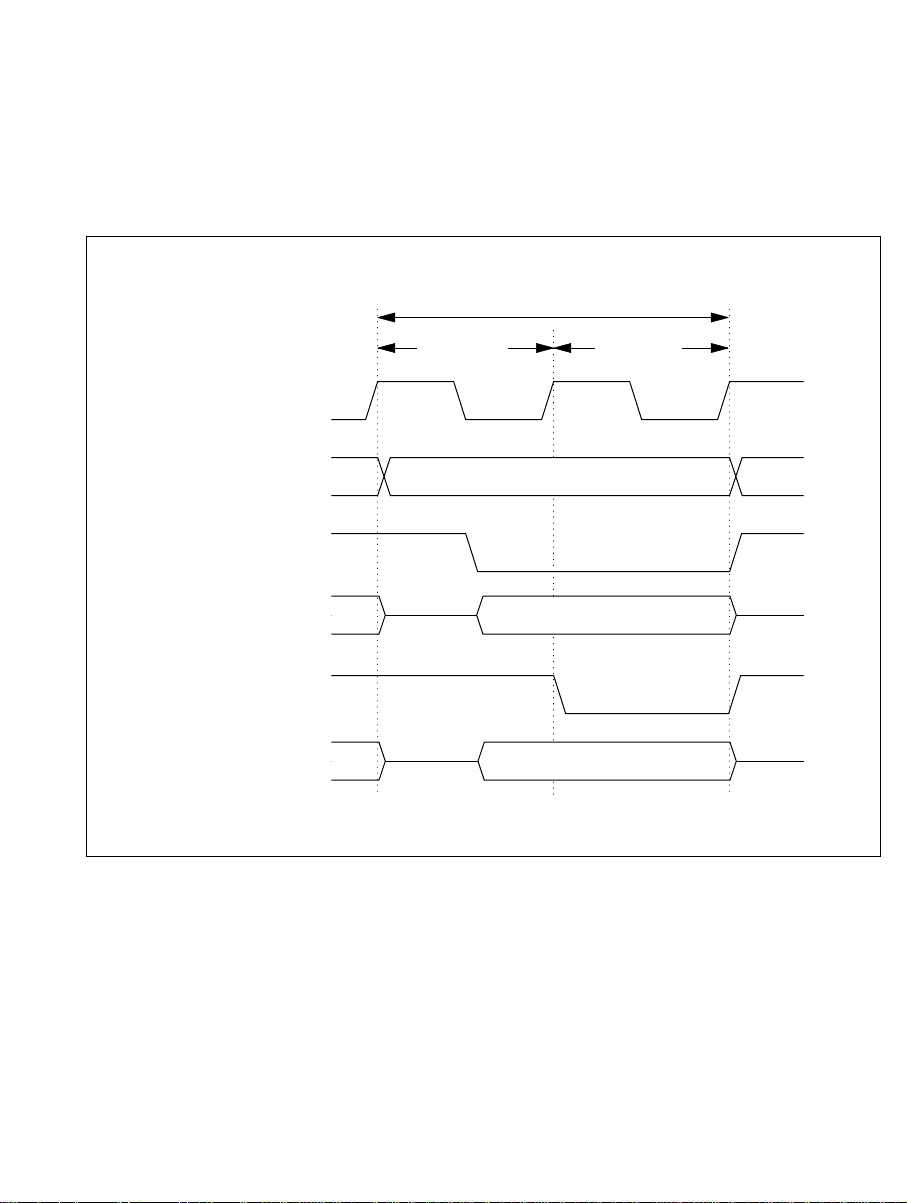

7-2 Programmable Wait Mode ·····························································································131

7-3 Pin Wait Mode ···············································································································132

7-4 Pin Auto-Wait Mode ······································································································133

8-1 Block Diagram of Clock Pulse Generator ·····································································135

8-2 Connection of Crystal Oscillator (Example) ·································································136

8-3 Crystal Oscillator Equivalent Circuit ·············································································136

8-4 Notes on Board Design around External Crystal ···························································137

8-5 External Clock Input (Example) ····················································································137

8-6 Phase Relationship of ø Clock and E clock ···································································138

9-1 Pin Functions of Port 1 ··································································································142

9-2 Pin Functions of Port 2 ··································································································148

9-3 Port 2 Pin Functions in Expanded Modes ······································································150

9-4 Port 2 Pin Functions in Single-Chip Mode ····································································151

9-5 Pin Functions of Port 3 ··································································································151

9-6 Port 3 Pin Functions in Expanded Modes ······································································153

9-7 Port 3 Pin Functions in Single-Chip Mode ····································································154

9-8 Pin Functions of Port 4 ··································································································154

9-9 Port 4 Pin Functions in Expanded Modes ······································································156

9-10 Port 4 Pin Functions in Single-Chip Mode ····································································157

9-11 Pin Functions of Port 5 ··································································································157

9-12 Port 5 Pin Functions in Modes 1 and 3 ··········································································159

9-13 Port 5 Pin Functions in Modes 2 and 4 ··········································································160

9-14 Port 5 Pin Functions in Single-Chip Mode ····································································160

9-15 Pin Functions of Port 6 ··································································································164

9-16 Port 6 Pin Functions in Mode 3 ·····················································································166

9-17 Port 6 Pin Functions in Mode 4 ·····················································································166

9-18 Port 6 Pin Functions in Modes 7, 2, and 1 ·····································································167

9-19 Pin Functions of Port 7 ··································································································168

9-20 Pin Functions of Port 8 ··································································································172

9-21 Pin Functions of Port 9 ··································································································173

10-1 Block Diagram of 16-Bit Free-Running Timer ·····························································178

10-2 (a) Write Access to FRC (When CPU Writes H'AA55) ·····················································189

10-2 (b) Read Access to FRC (When FRC Contains H'AA55) ···················································190

10-3 Increment Timing for External Clock Input ··································································191

10-4 Setting of Output Compare Flags ··················································································192

10-5 Timing of Output Compare A ························································································192

10-6 Clearing of FRC by Compare-Match A ·········································································193

10-7 Input Capture Timing (Usual Case) ···············································································193

10-8 Input Capture Timing (1-State Delay) ···········································································194

10-9 Setting of Input Capture Flag ························································································194

10-10 Setting of Overflow Flag (OVF) ····················································································195

10-11 Square-Wave Output (Example) ····················································································200

10-12 FRC Write-Clear Contention ·························································································201

10-13 FRC Write-Increment Contention ·················································································202

10-14 Contention between OCR Write and Compare-Match ··················································203

11-1 Block Diagram of 8-Bit Timer ·······················································································208

11-2 Count Timing for External Clock Input ·········································································215

11-3 Setting of Compare-Match Flags ···················································································216

11-4 Timing of Timer Output ·································································································216

11-5 Timing of Compare-Match Clear ··················································································217

11-6 Timing of External Reset ·······························································································217

11-7 Setting of Overflow Flag (OVF) ····················································································218

11-8 Example of Pulse Output ·······························································································219

11-9 TCNT Write-Clear Contention ······················································································220

11-10 TCNT Write-Increment Contention ··············································································221

11-11 Contention between TCOR Write and Compare-Match ···············································222

12-1 Block Diagram of PWM Timer ·····················································································228

12-2 PWM Timing ·················································································································233

13-1 Block Diagram of Timer Counter ··················································································236

13-2 Writing to TCNT and TCSR ··························································································239

13-3 Operation in Watchdog Timer Mode ·············································································241

13-4 Operation in Interval Timer Mode ·················································································242

13-5 Setting of OVF Bit ·········································································································243

13-6 TCNT Write-Increment Contention ··············································································244

14-1 Block Diagram of Serial Communication Interface ······················································246

14-2 Data Format in Asynchronous Mode ·············································································260

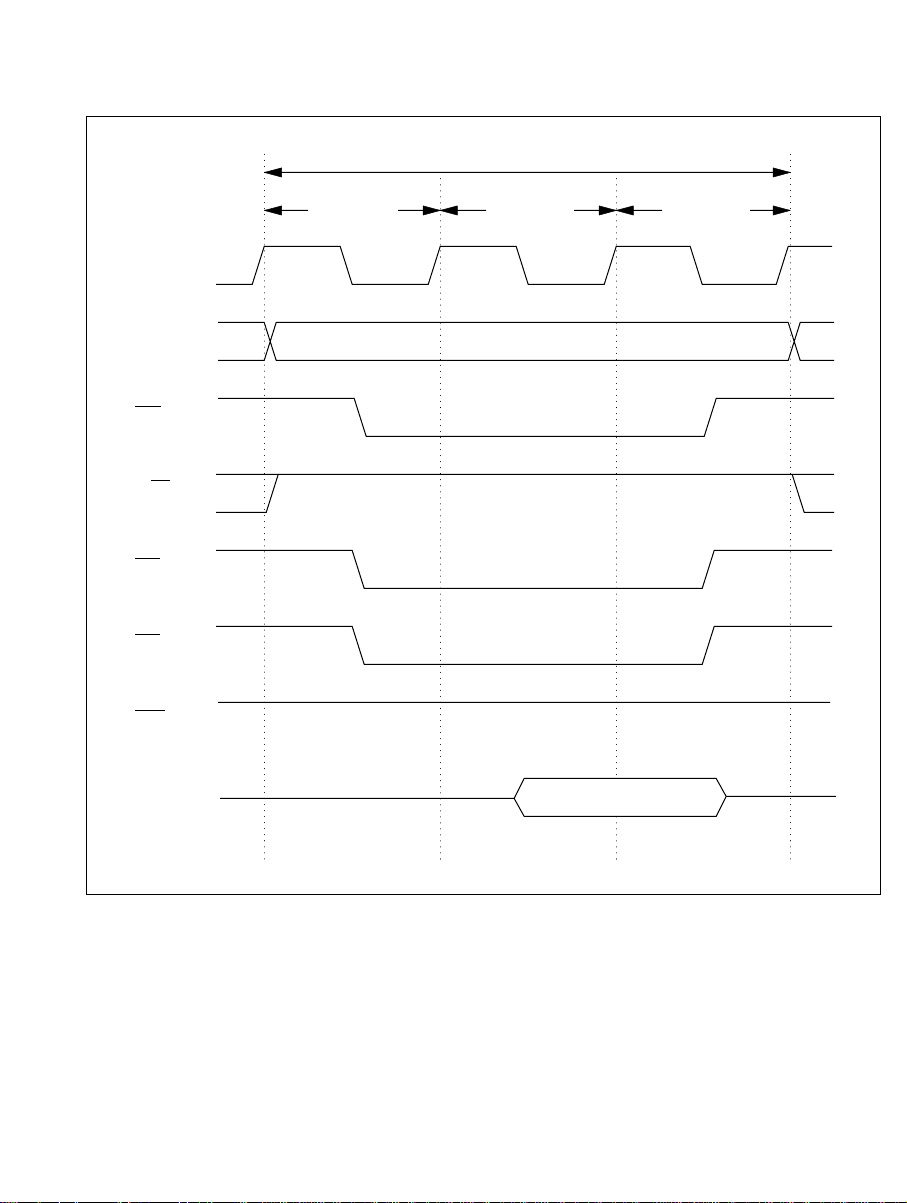

14-3 Phase Relationship between Clock Output and Transmit Data ·····································261

14-4 Data Format in Synchronous Mode ···············································································265

14-5 Sampling Timing (Asynchronous Mode) ······································································271

15-1 Block Diagram of A/D Converter ··················································································274

15-2 Read Access to A/D Data Register (When Register Contains H'AA40) ·······················280

15-3 A/D Operation in Single Mode (When Channel 1 is Selected) ·····································283

15-4 A/D Operation in Scan Mode (When Channels 0 to 2 are Selected) ·····························286

15-5 A/D Conversion Timing ·································································································288

16-1 Block Diagram of On-Chip RAM ·················································································291

17-1 Block Diagram of On-Chip ROM ·················································································296

17-2 Socket Adapter Pin Arrangements ·················································································298

17-3 Memory Map in PROM Mode ·······················································································299

17-4 High-Speed Programming Flowchart ············································································300

17-5 PROM Write/Verify Timing ··························································································302

17-6 Recommended Screening Procedure ·············································································303

18-1 NMI Timing of Software Standby Mode (Application Example) ·································311

18-2 Hardware Standby Sequence ·························································································313

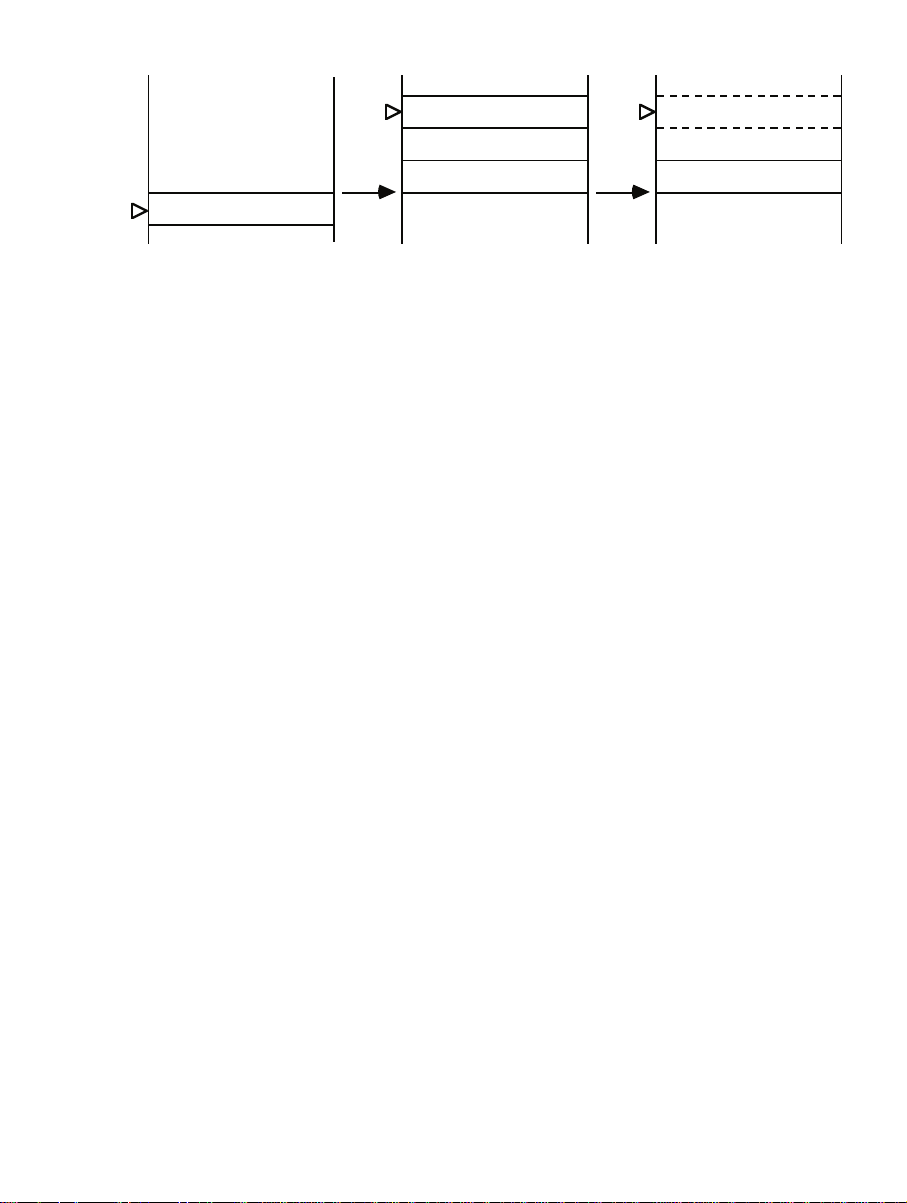

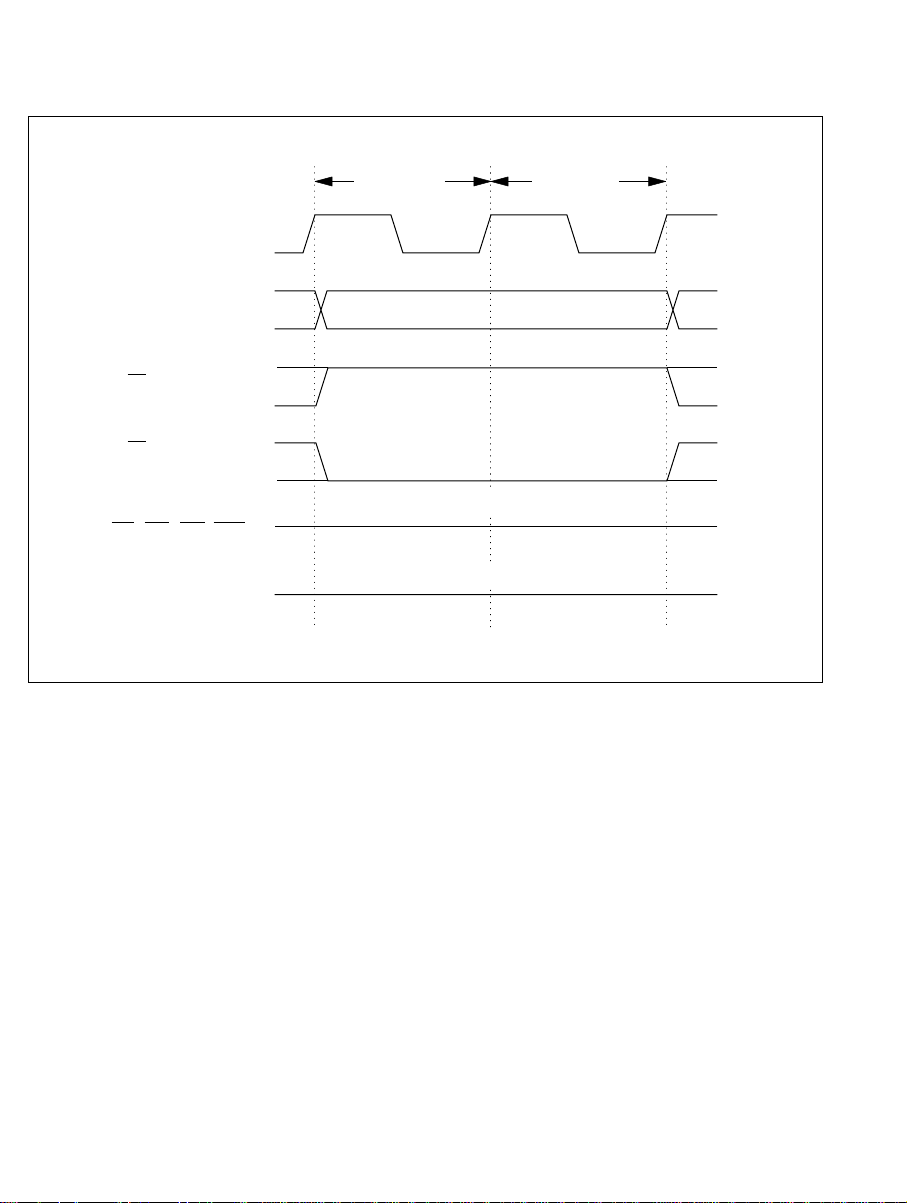

19-1 Execution Cycle of Instruction Synchronized with E Clock in Expanded Modes

(Maximum Synchronization Delay) ··············································································316

19-2 Execution Cycle of Instruction Synchronized with E Clock in Expanded Modes

(Minimum Synchronization Delay) ···············································································317

20-1 Example of Circuit for Driving a Darlington Transistor Pair ········································322

20-2 Example of Circuit for Driving an LED ········································································322

20-3 Output Load Circuit ·······································································································325

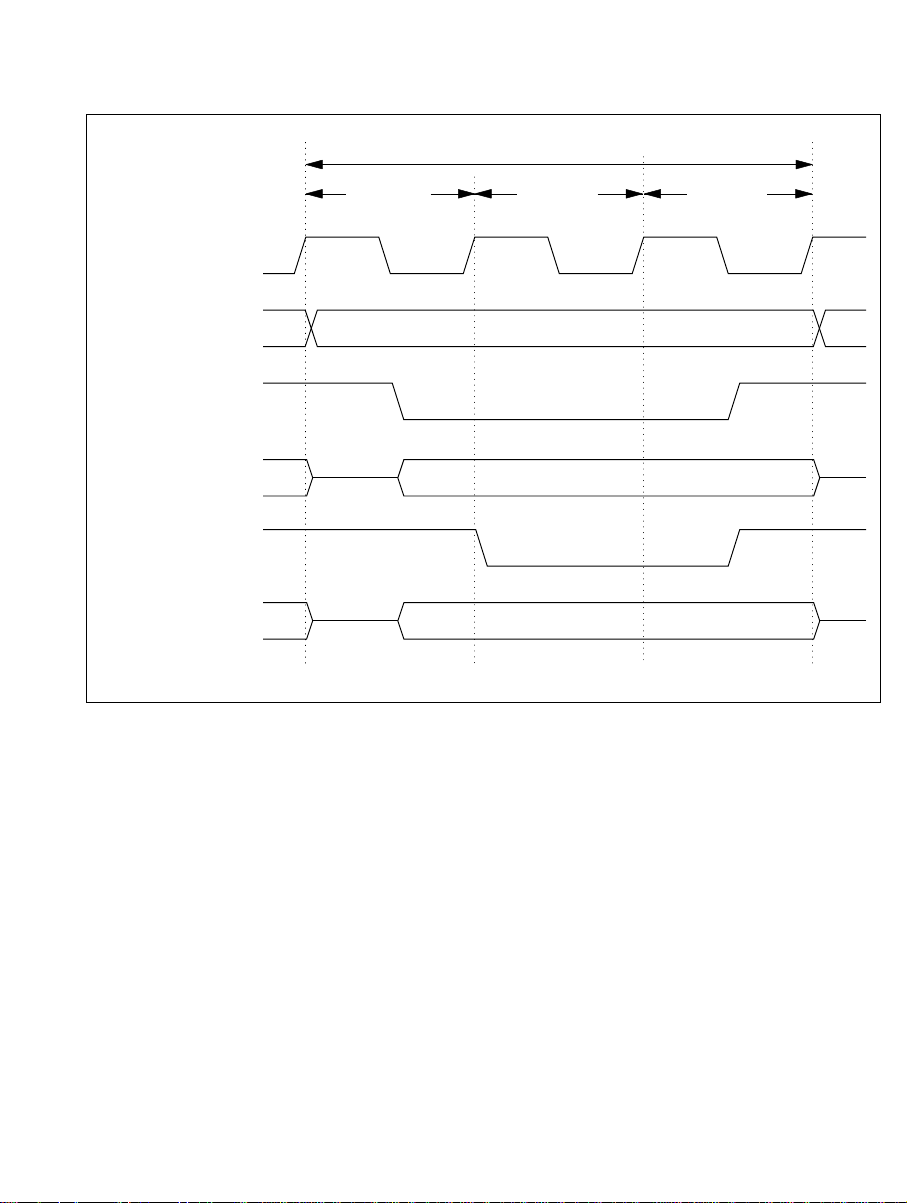

20-4 Basic Bus Cycle (without Wait States) in Expanded Modes ·········································327

20-5 Basic Bus Cycle (with 1 Wait State) in Expanded Modes ·············································328

20-6 Bus Cycle Synchronized with E Clock ··········································································329

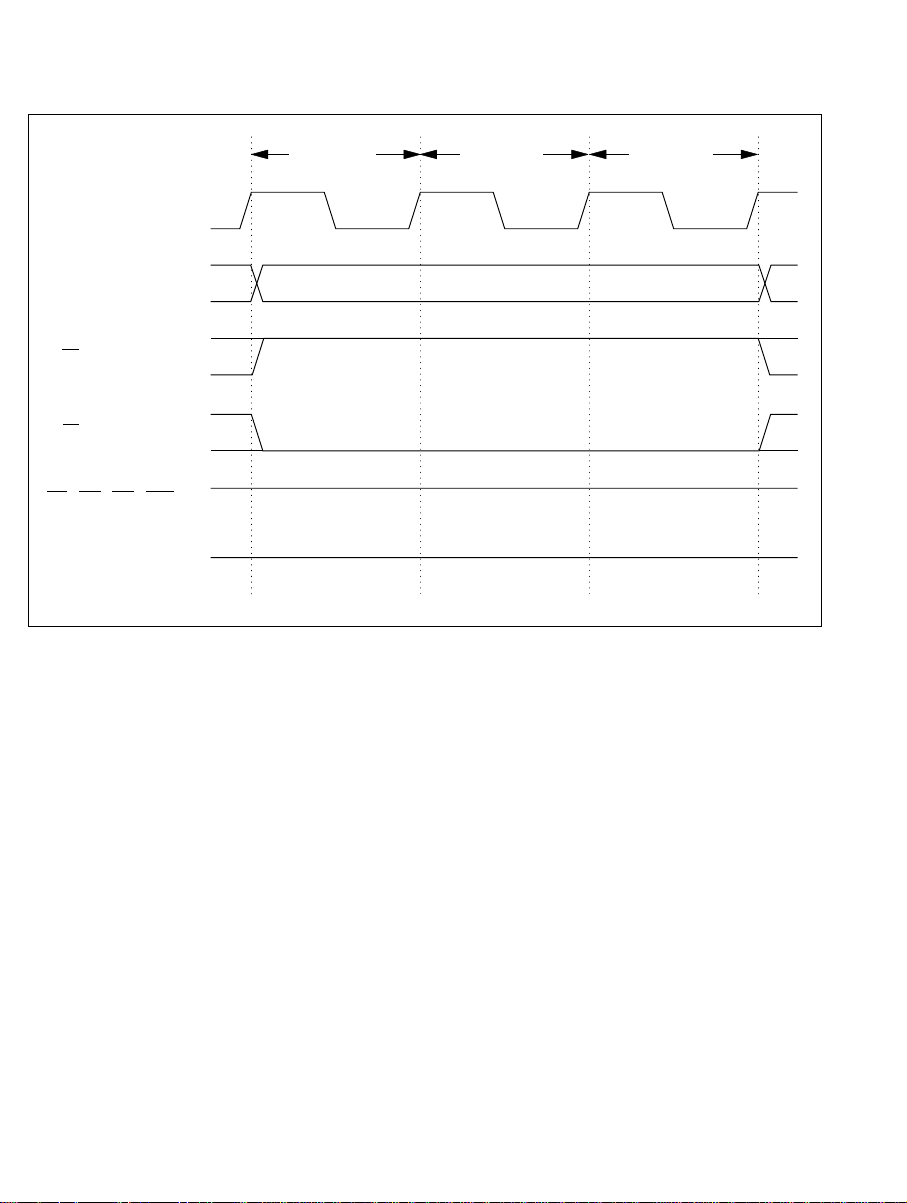

20-7 Reset Input Timing········································································································ 330

20-8 Interrupt Input Timing ···································································································330

20-9 NMI Pulse Width (for Recovery from Software Standby Mode) ··································330

20-10 Bus Release State Timing ······························································································331

20-11 E Clock Timing ··············································································································331

20-12 Clock Oscillator Stabilization Timing ···········································································332

20-13 I/O Port Input/Output Timing ························································································333

20-14 Free-Running Timer Input/Output Timing ····································································334

20-15 External Clock Input Timing for Free-Running Timers ················································334

20-16 8-Bit Timer Output Timing ····························································································335

20-17 8-Bit Timer Clock Input Timing ····················································································335

20-18 8-Bit Timer Reset Input Timing ····················································································335

20-19 PWM Timer Output Timing ··························································································336

20-20 SCI Input Clock Timing ································································································336

20-21 SCI Input/Output Timing (Synchronous Mode) ····························································336

C-1 (a) Schematic Diagram of Port 1, Pin P10 ··········································································407

C-1 (b) Schematic Diagram of Port 1, Pin P11 ··········································································407

C-1 (c) Schematic Diagram of Port 1, Pin P12 ···········································································408

C-1 (d) Schematic Diagram of Port 1, Pin P13 ··········································································409

C-1 (e) Schematic Diagram of Port 1, Pin P14 ···········································································410

C-1 (f) Schematic Diagram of Port 1, Pins P15 and P16 ···························································411

C-1 (g) Schematic Diagram of Port 1, Pin P17 ··········································································412

C-2 Schematic Diagram of Port 2 ·························································································413

C-3 Schematic Diagram of Port 3 ·························································································414

C-4 Schematic Diagram of Port 4 ·························································································415

C-5 Schematic Diagram of Port 5 ·························································································416

C-6 Schematic Diagram of Port 6 ·························································································417

C-7 (a) Schematic Diagram of Port 7, Pin P70 ··········································································418

C-7 (b) Schematic Diagram of Port 7, Pins P71 and P72 ···························································419

C-7 (c) Schematic Diagram of Port 7, Pin P73 ··········································································420

C-7 (d) Schematic Diagram of Port 7, Pins P74, P75 and P76 ····················································421

C-7 (e) Schematic Diagram of Port 7, Pin P77 ··········································································422

C-8 Schematic Diagram of Port 8 ·························································································423

C-9 (a) Schematic Diagram of Port 9, Pins P90 and P91 ···························································424

C-9 (b) Schematic Diagram of Port 9, Pins P92, P93 and P94 ····················································425

C-9 (c) Schematic Diagram of Port 9, Pin P95 ··········································································426

C-9 (d) Schematic Diagram of Port 9, Pin P96 ··········································································427

C-9 (e) Schematic Diagram of Port 9, Pin P97 ··········································································428

E-1 Reset during Memory Access (Mode 1) ········································································435

E-2 Reset during Memory Access (Mode 1) ········································································436

E-3 Reset during Memory Access (Mode 2) ········································································438

E-4 Reset during Memory Access (Mode 2) ········································································439

E-5 Reset during Memory Access (Mode 3) ········································································441

E-6 Reset during Memory Access (Mode 3) ········································································442

E-7 Reset during Memory Access (Mode 4) ········································································444

E-8 Reset during Memory Access (Mode 4) ········································································445

E-9 Reset during Memory Access (Mode 7) ········································································446

E-10 Reset during Memory Access (Mode 7) ········································································447

G-1 Package Dimensions (CP-84) ························································································451

G-2 Package Dimensions (CG-84) ·······················································································451

G-3 Package Dimensions (FP-80A) ······················································································452

Tables

1-1 Features ······························································································································2

1-2 Pin Arrangements in Each Operating Mode (CP-84, CG-84) ···········································8

1-3 Pin Arrangements in Each Operating Mode (FP-80A) ····················································12

1-4 Pin Functions ···················································································································16

2-1 Operating Modes ·············································································································23

2-2 Mode Control Register ····································································································29

3-1 Interrupt Mask Levels ······································································································36

3-2 Interrupt Mask Bits after an Interrupt is Accepted ··························································36

3-3 Initial Values of Registers ································································································41

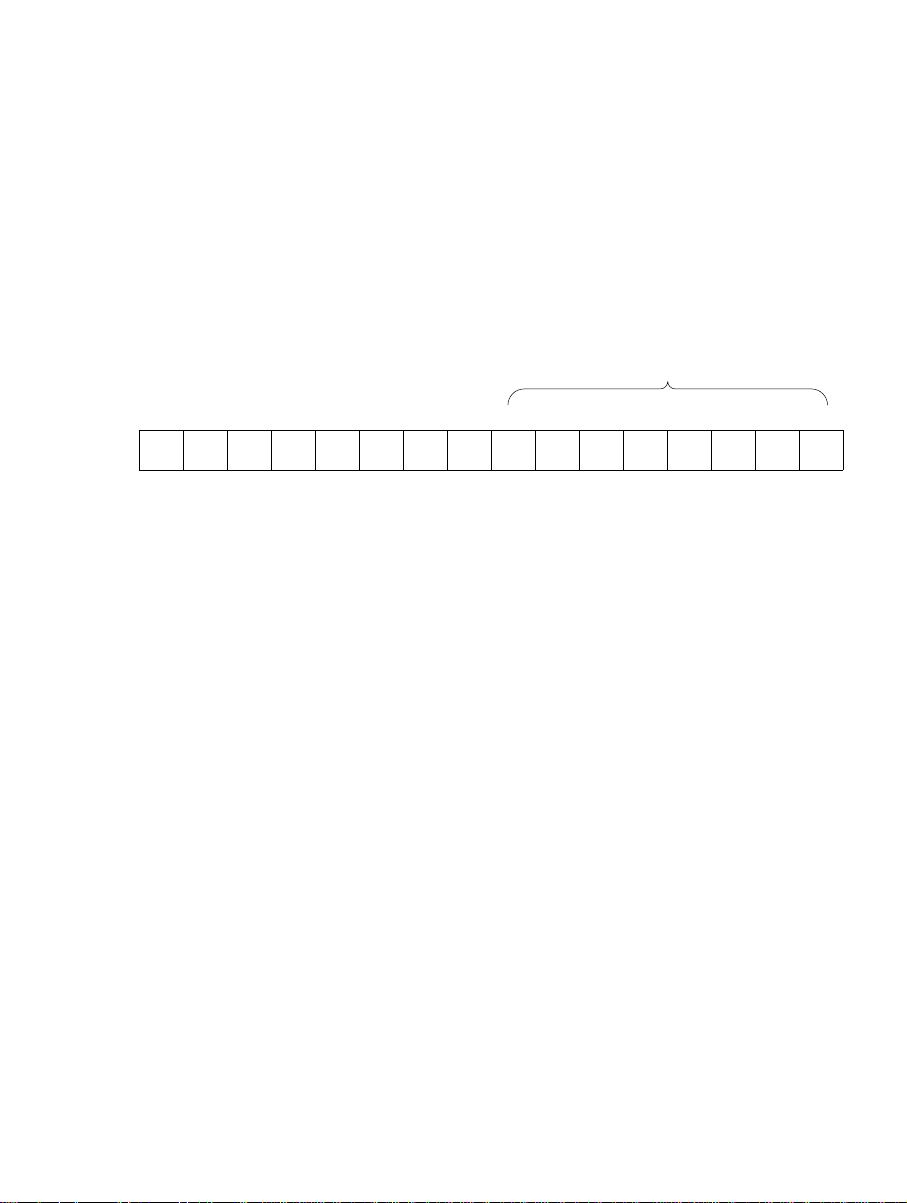

3-4 General Register Data Formats ························································································42

3-5 Data Formats in Memory ·································································································43

3-6 Data Formats on the Stack ·······························································································44

3-7 Addressing Modes ···········································································································46

3-8 Effective Address Calculation ·························································································47

3-9 Instruction Classification ·································································································50

3-10 Data Transfer Instructions ·······························································································52

3-11 Arithmetic Instructions ····································································································53

3-12 Logic Operation Instructions ···························································································54

3-13 Shift Instructions ··············································································································55

3-14 Bit-Manipulation Instructions ··························································································56

3-15 Branching Instructions ·····································································································57

3-16 System Control Instructions ····························································································59

3-17 Short-Format Instructions and Equivalent General Formats ···········································62

4-1 (a) Exceptions and Their Priority ··························································································81

4-1 (b) Instruction Exceptions ······································································································81

4-2 Exception Vector Table ····································································································84

4-3 Stack after Exception Handling Sequence ·······································································94

5-1 Interrupt Controller Registers ··························································································99

5-2 Interrupts, Vectors, and Priorities ··················································································102

5-3 Assignment of Interrupt Priority Registers ····································································103

5-4 Number of States before Interrupt Service ····································································111

6-1 Internal Control Registers of the DTC ···········································································114

6-2 Data Transfer Enable Registers ·····················································································115

6-3 Assignment of Data Transfer Enable Registers ·····························································117

6-4 Addresses of DTC Vectors ·····························································································121

6-5 Number of States per Data Transfer ··············································································123

6-6 Number of States before Interrupt Service ····································································124

6-7 DTC Control Register Information Set in RAM ···························································125

7-1 Register Configuration ···································································································128

7-2 Wait Modes ····················································································································130

8-1 External Crystal Parameters ··························································································136

9-1 Input/Output Port Summary ··························································································140

9-2 Port 1 Registers ··············································································································142

9-3 Port 1 Pin Functions in Expanded Modes ······································································145

9-4 Port 1 Pin Functions in Single-Chip Modes ··································································147

9-5 Port 2 Registers ··············································································································149

9-6 Port 3 Registers ··············································································································152

9-7 Port 4 Registers ··············································································································155

9-8 Port 5 Registers ··············································································································158

9-9 Status of MOS Pull-Ups for Port 5 ················································································161

9-10 Port 6 Registers ··············································································································164

9-11 Status of MOS Pull-Ups for Port 5 ················································································167

9-12 Port 7 Registers ··············································································································168

9-13 Port 7 Pin Functions ·······································································································170

9-14 Port 8 Registers ··············································································································172

9-15 Port 9 Registers ··············································································································173

9-16 Port 9 Pin Functions ·······································································································175

10-1 Input and Output Pins of Free-Running Timer Module ················································179

10-2 Register Configuration ···································································································180

10-3 Free-Running Timer Interrupts ······················································································195

10-4 Synchronization by Writing to FRCs ············································································196

10-5 Effect of Changing Internal Clock Sources ···································································204

11-1 Input and Output Pins of 8-Bit Timer ············································································209

11-2 8-Bit Timer Registers ·····································································································209

11-3 8-Bit Timer Interrupts ····································································································218

11-4 Priority Order of Timer Output ······················································································223

11-5 Effect of Changing Internal Clock Sources ···································································223

12-1 Output Pins of PWM Timer Module ·············································································228

12-2 PWM Timer Registers ···································································································229

12-3 PWM Timer Parameters for 10MHz System Clock ······················································232

13-1 Register Configuration ···································································································236

13-2 Read Addresses of TCNT and TCSR ············································································240

14-1 SCI Input/Output Pins ····································································································247

14-2 SCI Registers ·················································································································247

14-3 Examples of BRR Settings in Asynchronous Mode (1) ················································255

14-3 Examples of BRR Settings in Asynchronous Mode (2) ················································256

14-3 Examples of BRR Settings in Asynchronous Mode (3) ················································256

14-3 Examples of BRR Settings in Asynchronous Mode (4) ················································257