HIT HD6417708STF60, HD6417708SF60, HD6417708RF100, HD6417708F60 Datasheet

SH7708 Series

SH7708, SH7708S, SH7708R

Hardware Manual

ADE-602-105E

Rev.6.0

5/5/99

Hitachi, Ltd.

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party’s

rights, including intellectual property rights, in connection with use of the information

contained in this document.

2. Products and product specifications may be subject to change without notice. Confirm that you

have received the latest product standards or specifications before final design, purchase or use.

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability.

However, contact Hitachi’s sales office before using the product in an application that demands

especially high quality and reliability or where its failure or malfunction may directly threaten

human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power,

combustion control, transportation, traffic, safety equipment or medical equipment for life

support.

4. Design your application so that the product is used within the ranges guaranteed by Hitachi

particularly for maximum rating, operating supply voltage range, heat radiation characteristics,

installation conditions and other characteristics. Hitachi bears no responsibility for failure or

damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider

normally foreseeable failure rates or failure modes in semiconductor devices and employ

systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does

not cause bodily injury, fire or other consequential damage due to operation of the Hitachi

product.

5. This product is not designed to be radiation resistant.

6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document

without written approval from Hitachi.

7. Contact Hitachi’s sales office for any questions regarding this document or Hitachi

semiconductor products.

Preface

The SH7708, SH7708S, and SH7708R(SH7708 Series) use a RISC (reduced instruction set

computer) type CPU to achieve high-performance computational processing. Also incorporating

the peripheral functions required for system configuration plus power-down features essential for

microcontroller application systems, the SH7708 Series is a new-generation RISC microcontroller

(SuperH RISC engine).

The SH7708 Series have a RISC type instruction set, with basic instructions executed in one

state, offering a drastic improvement in instruction execution speed. It also has an on-chip 32-bit

multiplier (producing a 64-bit result) capable of high-speed multiply-and-accumulate operations.

The SH7708 Series’s instructions are upward-compatible with those of the SH-1 and SH-2,

facilitating migration from these series to the SH7708 Series.

SH7708R is completely pin compatible with the SH7708S. On-chip supporting modules that

enable a user system to be configured with a minimum of components include oscillation circuits,

an interrupt controller (INTC), timers, a realtime clock (RTC), and a serial communication

interface (SCI). A user break controller (UBC) is provided as an on-chip module supporting

program development, allowing easy configuration of a simple debugger.

On-chip cache memory improves CPU processing performance, and a built-in memory

management unit (MMU) performs address translation between a 4-gigabyte virtual space and

physical space. An on-chip bus state controller (BSC) provides more efficient external memory

access, and enables direct connection to synchronous DRAM, DRAM, and pseudo-SRAM without

the need for glue logic.

This hardware manual describes the hardware of the SH7708 Series. Details of instructions can be

found in the programming manual.

Related Manuals

SH7708Series instructions

SH-3/SH-3E/SH3-DSP Programming Manual

Please consult your Hitachi sales representative for details of development environment system.

Contents

Section 1 Overview and Pin Functions ...............................................1

1.1 SH7708 Series Features ........................................................................................1

1.2 Block Diagram....................................................................................................6

1.3 Pin Description ...................................................................................................7

1.3.1 Pin Arrangement......................................................................................7

1.3.2 SH7708 Series Pin Functions.....................................................................8

Section 2 CPU .......................................................................... 13

2.1 Register Configuration..........................................................................................13

2.1.1 Privileged Mode and Banks.........................................................................13

2.1.2 General Registers .....................................................................................16

2.1.3 System Registers .....................................................................................17

2.1.4 Control Registers .....................................................................................17

2.2 Data Formats ......................................................................................................19

2.2.1 Data Format in Registers ...........................................................................19

2.2.2 Data Format in Memory ............................................................................19

2.3 Instruction Features..............................................................................................20

2.3.1 Execution Environment .............................................................................20

2.3.2 Addressing Modes.....................................................................................22

2.3.3 Instruction Formats ..................................................................................26

2.4 Instruction Set.....................................................................................................29

2.4.1 Instruction Set Classified by Function..........................................................29

2.4.2 Instruction Code Map................................................................................45

2.5 Processor States and Processor Modes......................................................................48

2.5.1 Processor States .......................................................................................48

2.5.2 Processor Modes ......................................................................................49

Section 3 Memory Management Unit (MMU)....................................... 51

3.1 Overview............................................................................................................51

3.1.1 Features..................................................................................................51

3.1.2 Role of MMU .........................................................................................51

3.1.3 SH7708 Series MMU ...............................................................................54

3.1.4 Register Configuration..............................................................................57

3.2 Register Description.............................................................................................58

3.3 TLB Functions ....................................................................................................60

3.3.1 Configuration of the TLB ..........................................................................60

3.3.2 TLB Indexing..........................................................................................62

3.3.3 TLB Address Comparison..........................................................................63

3.3.4 Page Management Information....................................................................65

1

3.4 MMU Functions .................................................................................................66

3.4.1 MMU Hardware Management..................................................................... 66

3.4.2 MMU Software Management .....................................................................66

3.4.3 MMU Instruction (LDLTB) .......................................................................67

3.4.4 Avoiding Synonym Problems ....................................................................68

3.5 MMU Exceptions ................................................................................................ 70

3.5.1 TLB Miss Exception ................................................................................70

3.5.2 TLB Protection Violation Exception............................................................71

3.5.3 TLB Invalid Exception..............................................................................72

3.5.4 Initial Page Write Exception ......................................................................73

3.5.5 Processing Flow in Event of MMU Exception (Same Processing Flow for Address

Error) .........................................................................................................75

3.6 Memory-Mapped TLB..........................................................................................77

3.6.1 Address Array..........................................................................................77

3.6.2 Data Array..............................................................................................78

3.6.3 Usage Examples ......................................................................................80

3.7 Usage Note.........................................................................................................80

Section 4 Exception Handling.........................................................81

4.1 Overview...........................................................................................................81

4.1.1 Features .................................................................................................81

4.1.2 Register Configuration..............................................................................81

4.2 Exception Handling Function.................................................................................81

4.2.1 Exception Handling Flow..........................................................................81

4.2.2 Exception Handling Vector Addresses...........................................................82

4.2.3 Acceptance of Exceptions.......................................................................... 84

4.2.4 Exception Codes......................................................................................86

4.2.5 Exception Request Masks..........................................................................87

4.2.6 Returning from Exception Handling ............................................................88

4.3 Register Description.............................................................................................88

4.4 Exception Handler Operation..................................................................................89

4.4.1 Reset ..................................................................................................... 89

4.4.2 Interrupts................................................................................................89

4.4.3 General Exceptions...................................................................................89

4.5 Individual Exception Operations.............................................................................90

4.5.1 Resets....................................................................................................90

4.5.2 General Exceptions...................................................................................91

4.5.3 Interrupts................................................................................................94

4.6 Cautions ............................................................................................................95

Section 5 Cache .........................................................................97

5.1 Overview...........................................................................................................97

5.1.1 Features .................................................................................................97

2

5.1.2 Cache Structure........................................................................................97

5.1.3 Register Configuration..............................................................................99

5.2 Register Description.............................................................................................99

5.2.1 Cache Control Register (CCR) ...................................................................99

5.3 Cache Operation..................................................................................................100

5.3.1 Searching the Cache..................................................................................100

5.3.2 Read Access............................................................................................102

5.3.3 Write Access ...........................................................................................102

5.3.4 Write-Back Buffer.....................................................................................102

5.3.5 Coherency of Cache and External Memory....................................................103

5.3.6 RAM Mode.............................................................................................103

5.4 Memory-Mapped Cache.........................................................................................103

5.4.1 Address Array..........................................................................................103

5.4.2 Data Array..............................................................................................104

5.5 Usage Examples ..................................................................................................106

5.5.1 Invalidating Specific Entries.......................................................................106

5.5.2 Reading the Data of a Specific Entry............................................................106

Section 6 Interrupt Controller (INTC)................................................ 107

6.1 Overview............................................................................................................107

6.1.1 Features..................................................................................................107

6.1.2 Block Diagram.........................................................................................108

6.1.3 Pin Configuration ....................................................................................109

6.1.4 Register Configuration..............................................................................109

6.2 Interrupt Sources..................................................................................................109

6.2.1 NMI Interrupts.........................................................................................110

6.2.2 IRL Interrupts..........................................................................................110

6.2.3 On-Chip Supporting Module Interrupts ........................................................112

6.2.4 Interrupt Exception Handling and Priority.....................................................112

6.3 INTC Registers ...................................................................................................115

6.3.1 Interrupt Priority Registers A and B (IPRA–IPRB).........................................115

6.3.2 Interrupt Control Register (ICR) .................................................................116

6.4 INTC Operation...................................................................................................117

6.4.1 Interrupt Sequence....................................................................................117

6.4.2 Multiple Interrupts ...................................................................................119

6.5 Interrupt Response Time .......................................................................................120

Section 7 User Break Controller (UBC)............................................. 123

7.1 Overview............................................................................................................123

7.1.1 Features..................................................................................................123

7.1.2 Block Diagram.........................................................................................123

7.1.3 Register Configuration..............................................................................125

7.1.4 Break Conditions and Register Settings ........................................................125

3

7.2 UBC Register Functions ....................................................................................... 126

7.2.1 Break Address Register A (BARA)...............................................................126

7.2.2 Break Address Register B (BARB)............................................................... 126

7.2.3 Break ASID Register A (BASRA)...............................................................127

7.2.4 Break ASID Register B (BASRB)................................................................ 127

7.2.5 Break Address Mask Register A (BAMRA)................................................... 127

7.2.6 Break Address Mask Register B (BAMRB).................................................... 128

7.2.7 Break Bus Cycle Register A (BBRA)...........................................................128

7.2.8 Break Bus Cycle Register B (BBRB)............................................................ 129

7.2.9 Break Data Register B (BDRB)................................................................... 130

7.2.10 Break Data Mask Register B (BDMRB)......................................................131

7.2.11 Break Control Register (BRCR)................................................................132

7.3 UBC Operation ...................................................................................................134

7.3.1 User Break Operation Flow........................................................................134

7.3.2 Instruction Fetch Cycle Break.....................................................................135

7.3.3 Data Access Cycle Break........................................................................... 136

7.3.4 Saved Program Counter (PC) Value.............................................................137

7.3.5 Examples of Use......................................................................................138

7.3.6 Cautions ................................................................................................140

Section 8 Power-Down Modes........................................................141

8.1 Overview...........................................................................................................141

8.1.1 Power-Down Modes................................................................................. 141

8.1.2 Register Configuration..............................................................................142

8.1.3 Pin Configuration .................................................................................... 143

8.2 Register Description.............................................................................................143

8.2.1 Standby Control Register (STBCR).............................................................143

8.3 Sleep Mode ........................................................................................................145

8.3.1 Transition to Sleep Mode ..........................................................................145

8.3.2 Canceling Sleep Mode ..............................................................................145

8.4 Standby Mode.....................................................................................................145

8.4.1 Transition to Standby Mode.......................................................................145

8.4.2 Canceling Standby Mode...........................................................................146

8.4.3 Clock Pause Function...............................................................................147

8.5 Module Standby Function .....................................................................................147

8.5.1 Transition to Module Standby Function ....................................................... 147

8.5.2 Clearing the Module Standby Function........................................................148

8.6 Timing of STATUS Pin Changes...........................................................................148

8.6.1 Timing for Resets .................................................................................... 148

8.6.2 Timing for Canceling Standbys ..................................................................150

8.6.3 Timing for Canceling Sleep Mode...............................................................151

8.7 Hardware Standby Mode........................................................................................153

8.7.1 Transition to Hardware Standby Mode.......................................................... 153

4

8.7.2 Canceling Hardware Standby Mode..............................................................154

8.7.3 Hardware Standby Mode Timing..................................................................154

Section 9 On-Chip Oscillation Circuits............................................... 157

9.1 Overview............................................................................................................157

9.1.1 Features..................................................................................................157

9.2 Overview of the CPG ...........................................................................................158

9.2.1 CPG Block Diagram.................................................................................158

9.2.2 CPG Pin Configuration.............................................................................161

9.2.3 CPG Register Configuration ......................................................................161

9.3 Clock Operating Modes.........................................................................................162

9.4 Register Descriptions............................................................................................170

9.4.1 Frequency Control Register (FRQCR)..........................................................170

9.5 Changing the Frequency........................................................................................174

9.5.1 Changing the Multiplication Rate ...............................................................174

9.5.2 Changing the Division Ratio......................................................................174

9.6 PLL Standby Function..........................................................................................175

9.6.1 Overview of the PLL Standby Function........................................................175

9.6.2 Usage.....................................................................................................175

9.7 Controlling Clock Output .....................................................................................176

9.7.1 Clock Modes 0–2 .....................................................................................176

9.7.2 Clock Modes 3 and 4 ................................................................................176

9.8 Overview of the Watchbog Timer (WDT).................................................................177

9.8.1 Block Diagram of the WDT........................................................................177

9.8.2 Register Configurations.............................................................................177

9.9 WDT Registers....................................................................................................178

9.9.1 Watchdog Timer Counter (WTCNT)............................................................178

9.9.2 Watchdog Timer Control/Status Register (WTCSR) .......................................178

9.9.3 Notes on Register Access...........................................................................180

9.10 Using the WDT .................................................................................................181

9.10.1 Canceling Standbys.................................................................................181

9.10.2 Changing the Frequency...........................................................................181

9.10.3 Using Watchdog Timer Mode....................................................................182

9.10.4 Using Interval Timer Mode.......................................................................182

9.10.5 Usage Notes ..........................................................................................183

9.11 Notes on Board Design........................................................................................184

Section 10 Bus State Controller (BSC) .............................................. 187

10.1 Overview..........................................................................................................187

10.1.1 Features ................................................................................................187

10.1.2 Block Diagram.......................................................................................188

10.1.3 Pin Configuration...................................................................................190

10.1.4 Register Configuration ............................................................................192

5

10.1.5 Area Overview.......................................................................................193

10.1.6 PCMCIA Support .................................................................................. 196

10.2 BSC Registers...................................................................................................200

10.2.1 Bus Control Register 1 (BCR1) ................................................................200

10.2.2 Bus Control Register 2 (BCR2) ................................................................203

10.2.3 Wait State Control Register 1 (WCR1) ......................................................204

10.2.4 Wait State Control Register 2 (WCR2) ......................................................205

10.2.5 Individual Memory Control Register (MCR) ...............................................208

10.2.6 DRAM Control Register (DCR) ...............................................................213

10.2.7 PCMCIA Control Register (PCR).............................................................215

10.2.8 Synchronous DRAM Mode Register (SDMR) .............................................216

10.2.9 Refresh Timer Control/Status Register (RTCSR).........................................217

10.2.10 Refresh Timer Counter (RTCNT) ............................................................219

10.2.11 Refresh Time Constant Register (RTCOR)................................................220

10.2.12 Refresh Count Register (RFCR)..............................................................220

10.2.13 Cautions on Accessing Refresh Control Related Registers............................221

10.3 BSC Operation..................................................................................................222

10.3.1 Endian/Access Size and Data Alignment.....................................................222

10.3.2 Description of Areas ...............................................................................228

10.3.3 Basic Interface........................................................................................231

10.3.4 DRAM Interface.....................................................................................237

10.3.5 Synchronous DRAM Interface..................................................................253

10.3.6 Pseudo-SRAM Direct Connection ............................................................. 269

10.3.7 Burst ROM Interface............................................................................... 278

10.3.8 PCMCIA Interface..................................................................................281

10.3.9 Waits between Access Cycles...................................................................293

10.3.10 Bus Arbitration ....................................................................................294

Section 11 Timer (TMU)...............................................................297

11.1 Overview..........................................................................................................297

11.1.1 Features................................................................................................297

11.1.2 Block Diagram.......................................................................................297

11.1.3 Pin Configuration ..................................................................................299

11.1.4 Register Configuration............................................................................299

11.2 TMU Registers..................................................................................................300

11.2.1 Timer Output Control Register (TOCR).....................................................300

11.2.2 Timer Start Register (TSTR) .................................................................... 301

11.2.3 Timer Control Register (TCR)..................................................................302

11.2.4 Timer Constant Register (TCOR)..............................................................305

11.2.5 Timer Counters (TCNT)..........................................................................306

11.2.6 Input Capture Register (TCPR2) ............................................................... 307

11.3 TMU Operation.................................................................................................308

11.3.1 Overview..............................................................................................308

6

11.3.2 Basic Functions......................................................................................308

11.4 Interrupts..........................................................................................................312

11.4.1 Status Flag Set Timing ...........................................................................312

11.4.2 Status Flag Clear Timing.........................................................................313

11.4.3 Interrupt Sources and Priorities..................................................................313

11.5 Usage Notes......................................................................................................314

11.5.1 Writing to Registers................................................................................314

11.5.2 Reading Registers...................................................................................314

11.5.3 Clearing UNF in the TCR Register............................................................314

Section 12 Realtime Clock (RTC) .................................................... 315

12.1 Overview..........................................................................................................315

12.1.1 Features ................................................................................................315

12.1.2 Block Diagram.......................................................................................315

12.1.3 Pin Configuration...................................................................................317

12.1.4 RTC Register Configuration.....................................................................318

12.2 RTC Registers...................................................................................................318

12.2.1 64-Hz Counter (R64CNT)........................................................................318

12.2.2 Second Counter (RSECCNT)....................................................................319

12.2.3 Minute Counter (RMINCNT) ...................................................................319

12.2.4 Hour Counter (RHRCNT) ........................................................................320

12.2.5 Day of the Week Counter (RWKCNT)........................................................320

12.2.6 Date Counter (RDAYCNT) ......................................................................321

12.2.7 Month Counter (RMONCNT)...................................................................322

12.2.8 Year Counter (RYRCNT).........................................................................322

12.2.9 Second Alarm Register (RSECAR)............................................................323

12.2.10 Minute Alarm Register (RMINAR)..........................................................323

12.2.11 Hour Alarm Register (RHRAR)...............................................................324

12.2.12 Day of the Week Alarm Register (RWKAR) ..............................................324

12.2.13 Date Alarm Register (RDAYAR).............................................................325

12.2.14 Month Alarm Register (RMONAR).........................................................326

12.2.15 RTC Control Register 1 (RCR1) .............................................................326

12.2.16 RTC Control Register 2 (RCR2) .............................................................328

12.3 RTC Operation ..................................................................................................329

12.3.1 Initial Settings of Registers after Power-On.................................................329

12.3.2 Setting the Time ....................................................................................329

12.3.3 Reading the Time ...................................................................................331

12.3.4 Alarm Function......................................................................................332

12.3.5 Crystal Oscillator Circuit .........................................................................333

12.4 Usage Notes......................................................................................................334

12.4.1 Flag Clearing.........................................................................................334

Section 13 Serial Communication Interface (SCI).................................. 335

7

13.1 Overview..........................................................................................................335

13.1.1 Features................................................................................................335

13.1.2 Block Diagram.......................................................................................336

13.1.3 Pin Configuration ..................................................................................337

13.1.4 Register Configuration............................................................................337

13.2 Register Descriptions..........................................................................................338

13.2.1 Receive Shift Register (SCRSR)...............................................................338

13.2.2 Receive Data Register (SCRDR) ............................................................... 338

13.2.3 Transmit Shift Register (SCTSR) .............................................................338

13.2.4 Transmit Data Register (SCTDR)..............................................................339

13.2.5 Serial Mode Register (SCSMR) ................................................................ 339

13.2.6 Serial Control Register (SCSCR)..............................................................342

13.2.7 Serial Status Register (SCSSR) ................................................................ 345

13.2.8 Serial Port Register (SCSPTR).................................................................349

13.2.9 Bit Rate Register (SCBRR)......................................................................350

13.3 Operation .........................................................................................................358

13.3.1 Overview..............................................................................................358

13.3.2 Operation in Asynchronous Mode..............................................................360

13.3.3 Multiprocessor Communication ................................................................ 370

13.3.4 Synchronous Operation ...........................................................................378

13.4 SCI Interrupt Sources ......................................................................................... 388

13.5 Usage Notes......................................................................................................388

Section 14 Smart Card Interface.......................................................393

14.1 Overview..........................................................................................................393

14.1.1 Features................................................................................................393

14.1.2 Block Diagram.......................................................................................394

14.1.3 Pin Configuration ..................................................................................395

14.1.4 Register Configuration............................................................................395

14.2 Register Descriptions..........................................................................................395

14.2.1 Smart Card Mode Register (SCSCMR) ......................................................396

14.2.2 Serial Status Register (SCSSR) ................................................................ 397

14.3 Operation .........................................................................................................398

14.3.1 Overview..............................................................................................398

14.3.2 Pin Connections ....................................................................................399

14.3.3 Data Format .......................................................................................... 400

14.3.4 Register Settings....................................................................................401

14.3.5 Clock...................................................................................................403

14.3.6 Data Transmission and Reception..............................................................405

14.4 Usage Notes......................................................................................................412

14.4.1 Receive Data Timing and Receive Margin in Asynchronous Mode...................412

14.4.2 Retransmission (Receive and Transmit Modes)............................................. 414

8

Section 15 I/O Ports.................................................................... 417

15.1 Overview..........................................................................................................417

15.1.1 Features ................................................................................................417

15.1.2 Block Diagram.......................................................................................417

15.1.3 Pin Configuration...................................................................................420

15.1.4 Register Configuration ............................................................................421

15.2 Register Descriptions..........................................................................................421

15.2.1 Port Control Register (PCTR) ..................................................................421

15.2.2 Port Data Register (PDTR).......................................................................422

15.2.3 Serial Port Register (SCSPTR) .................................................................423

Section 16 Electrical Characteristics(-SH7708, SH7708S-)....................... 425

16.1 Absolute Maximum Ratings ................................................................................425

16.2 DC Characteristics..............................................................................................426

16.3 AC Characteristics..............................................................................................427

16.3.1 Clock Timing ........................................................................................428

16.3.2 Control Signal Timing ............................................................................438

16.3.3 AC Bus Timing Specifications..................................................................442

16.3.4 Basic Timing .........................................................................................446

16.3.5 Burst ROM Timing ................................................................................449

16.3.6 DRAM Timing ......................................................................................452

16.3.7 Synchronous DRAM Timing....................................................................462

16.3.8 Pseudo-SRAM Timing ............................................................................473

16.3.9 PCMCIA Timing ...................................................................................478

16.3.10 Peripheral Module Signal Timing ............................................................485

16.3.11 AC Characteristics Test Conditions..........................................................488

Section 17 Electrical Characteristics (-SH7708R-)................................. 489

17.1 Absolute Maximum Ratings ................................................................................489

17.2 DC Characteristics..............................................................................................490

17.3 AC Characteristics..............................................................................................491

17.3.1 Clock Timing ........................................................................................492

17.3.2 Control Signal Timing ............................................................................498

17.3.3 AC Bus Timing Specifications..................................................................502

17.3.4 Basic Timing .........................................................................................506

17.3.5 Burst ROM Timing ................................................................................510

17.3.6 DRAM Timing ......................................................................................513

17.3.7 Synchronous DRAM Timing....................................................................523

17.3.8 Pseudo-SRAM Timing ............................................................................534

17.3.9 PCMCIA Timing ...................................................................................539

17.3.10 Peripheral Module Signal Timing ............................................................546

17.3.11 AC Characteristics Test Conditions..........................................................549

9

Appendix A Pin Functions.............................................................551

A.1 Pin States..........................................................................................................551

A.2 Pin Specifications ............................................................................................... 554

A.3 Handling of Unused Pins......................................................................................557

A.4 Pin States in Access to Each Address Space............................................................. 558

Appendix B Control Registers.........................................................594

B.1 Register Address Map...........................................................................................594

B.2 Register Bit List .................................................................................................598

B.3 Register States in Reset and Power-Down States.......................................................604

Appendix C Delay Time Variation Due to Load Capacitance......................608

Appendix D Package Dimensions.....................................................609

10

Section 1 Overview and Pin Functions

1.1 SH7708 Series Features

The SH7708, SH7708S, and SH7708R(SH7708 Series) are 32-bit RISC (reduced instruction set

computer) microcomputers, featuring object code upward-compatibility with SH-1 and SH-2

microcomputers. The SH7708R is completely pin compatible with the SH7708S. It includes an 8kbyte cache with a choice of write-back or write-through mode, and an MMU (memory

management unit) with a 128-entry 4-way set associative TLB (translation lookaside buffer).

The SH7708 Series have an on-chip bus state controller (BSC) that allows direct connection to

DRAM, synchronous DRAM (SDRAM), and pseudo-SRAM (PSRAM) without external circuitry.

Its 16-bit fixed-length instruction set enables program code size to be reduced by almost 50%

compared with 32-bit instructions.

The features of the SH7708 Series are summarized in table 1.1.

1

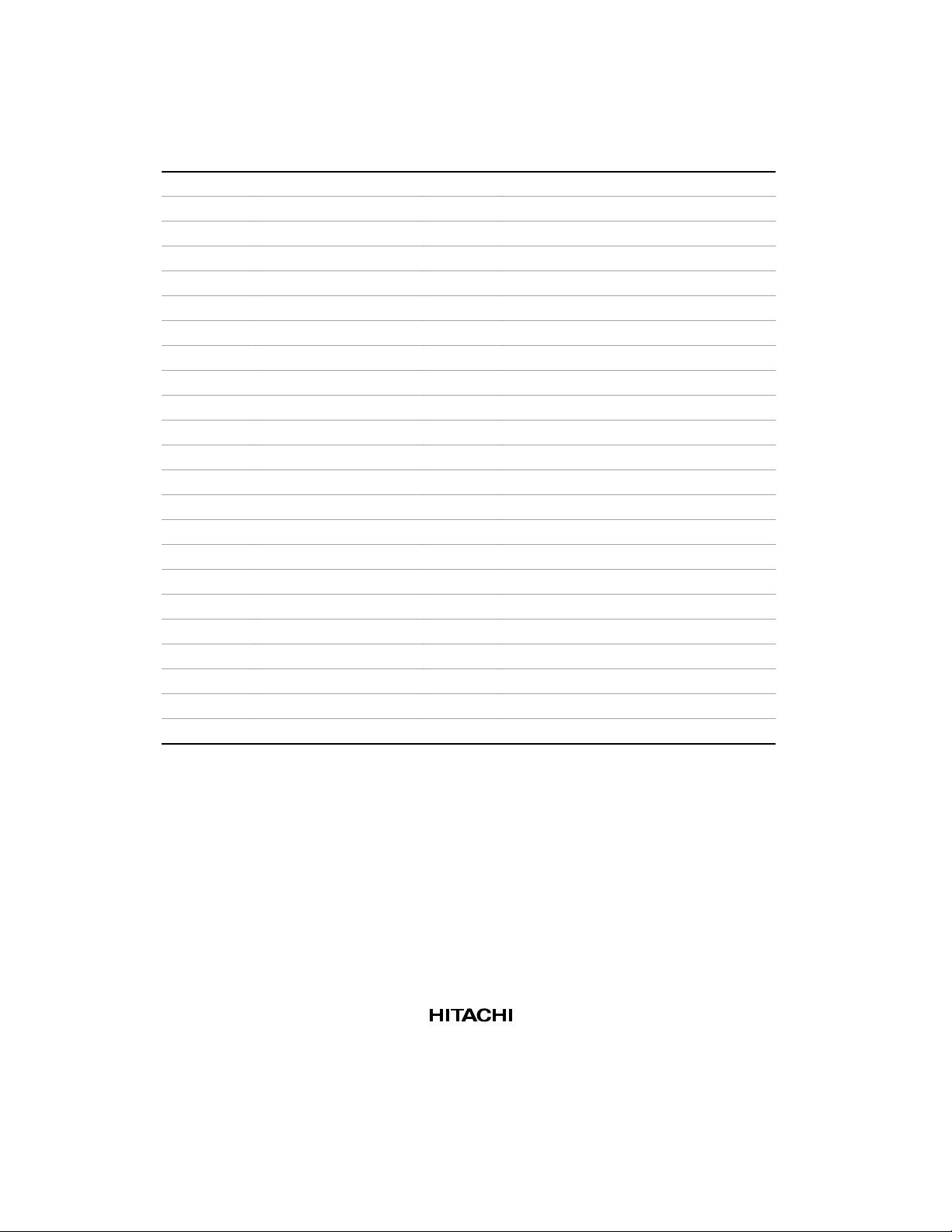

Table 1.1 SH7708 Series Features

Item Features

CPU

Operating modes,

clock pulse

generator

• Original Hitachi SuperH RISC engine architecture

• 32-bit internal data bus

• General-register machine

Sixteen 32-bit general registers (eight 32-bit bank registers)

Five 32-bit control registers

Four 32-bit system registers

• RISC-type instruction set (upward compatibility with the SH-1 and SH-2

series)

Instruction length: 16-bit fixed length for improved code efficiency

Load-store architecture

Delayed branch instructions

C-oriented instruction set

• Instruction execution time: one instruction/cycle for basic instructions

• Logical address space: 4 Gbytes (448-Mbyte actual memory space)

• Space identifier ASID: 8 bits, 256 logical address spaces

• On-chip multiplier

• Five-stage pipeline

• Clock mode: selected from an on-chip oscillator module, a frequency-

doubling circuit, or a clock output by combining them by PLL synchronization

• Processing states:

Power-on reset state

Manual reset state

Exception processing state

Program execution state

Power-down state

Bus-released state

• Power-down modes:

Sleep mode

Standby mode

Hardware Standby mode(SH7708S, SH7708R only)

• On-chip clock pulse generator

• One watchdog timer channel

2

Table 1.1 SH7708 Series Features (cont)

Item Features

Memory

management

unit (MMU)

Cache memory

Interrupt

controller

(INTC)

User break

controller

(UBC)

• 4 Gbytes of address space, 256 address spaces (8-bit ASID)

• Supports single virtual memory mode and multiple virtual memory mode

• Paging system

• Supports multiple page sizes: 1 or 4 kbytes

• 128-entry, 4-way set associative TLB

• Supports software selection of replacement method and random-replacement

algorithms

• Contents of TLB are directly accessible by address mapping

• Choice of operating mode

Normal mode (8-kbyte cache)

RAM mode (4-kbyte cache + 4-kbyte RAM)

• Mixed instruction/data, 128 entries, 16-byte block length

4-way set associative (8-kbyte cache)

2-way set associative (4-kbyte cache)

• Selectable write method (write-back/write-through), LRU (least recently used)

replacement algorithm

• Single-stage write-back buffer

• Contents of TLB can be accessed directly by address mapping (can be used

as on-chip memory)

• 5 external interrupt pins (NMI, IRL0 to IRL3)

• Encoded input of 15 external interrupt sources via pins IRL0 to IRL3

• On-chip peripheral interrupts: priority levels set for each module

• Supports debugging by user break interrupts

• 2 break channels

• Addresses, data values, type of access, and data size can all be set as

break conditions

• Supports a sequential break function

3

Table 1.1 SH7708 Series Features (cont)

Item Features

Bus state

controller

(BSC)

Timer

Realtime clock

(RTC)

Serial communication interface

(SCI)

Package

Note: SH7708S only

• Supports external memory access

32/16/8-bit external data bus

• Physical address space divided into seven areas, each a maximum 64

Mbytes, with the following features settable for each area:

Bus size (8, 16, or 32 bits)

Number of wait cycles (also supports a hardware wait function)

Setting the type of space enables direct connection to DRAM,

synchronous DRAM, pseudo-SRAM, and burst ROM

Supports fast page mode and EDO for DRAM

Supports PCMCIA interface

Outputs chip select signal (CS0–CS6) for corresponding area

• DRAM/synchronous DRAM/pseudo-SRAM refresh function

Programmable refresh interval

Supports CAS-before-RAS refresh and self-refresh modes

• DRAM/synchronous DRAM/pseudo-SRAM burst access function

• Usable as either big- or little-endian machine

• 3-channel auto-reload type 32-bit timer

• Input capture function

• 6 types of counter input clock can be selected

• Maximum resolution: 2 MHz

• On-chip clock and calendar functions

• On-chip 32-kHz crystal oscillator circuit with a maximum resolution (interrupt

cycle) of 1/256 second

• Selection of asynchronous or synchronous mode

• Full-duplex communication

• Supports smart card interface

• 144-pin plastic QFP(FP-144)

• 144-pin plastic TQFP (TFP-144) *

4

Table 1.1 SH7708 Series Features (cont)

Item Features

Product Line-up

Product

Number

SH7708 3.3V±0.3V60MHz HD6417708F60 144-pin

SH7708S 3.3V±0.3V60MHz HD6417708SF60

SH7708R 3.15-3.6V

On-chip

Voltage

(typ.)

Operation

Frequency

100MHz HD6417708RF100 144-pin

Model Package

Plastic LQFP

(FP-144F)

HD6417708STF60 144-pin

Plastic TQFP

(TFP-144)

Plastic L-QFP

(FP-144F)

5

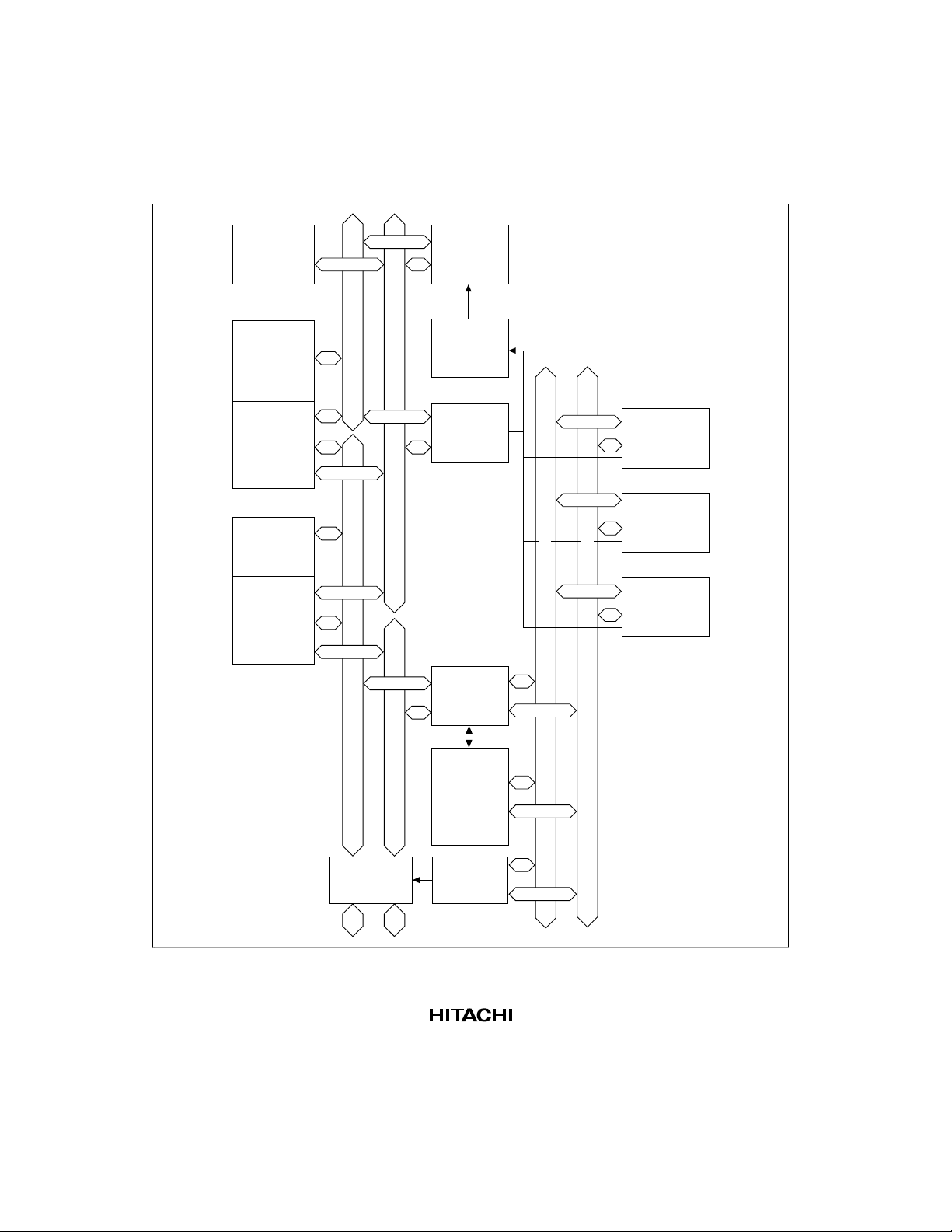

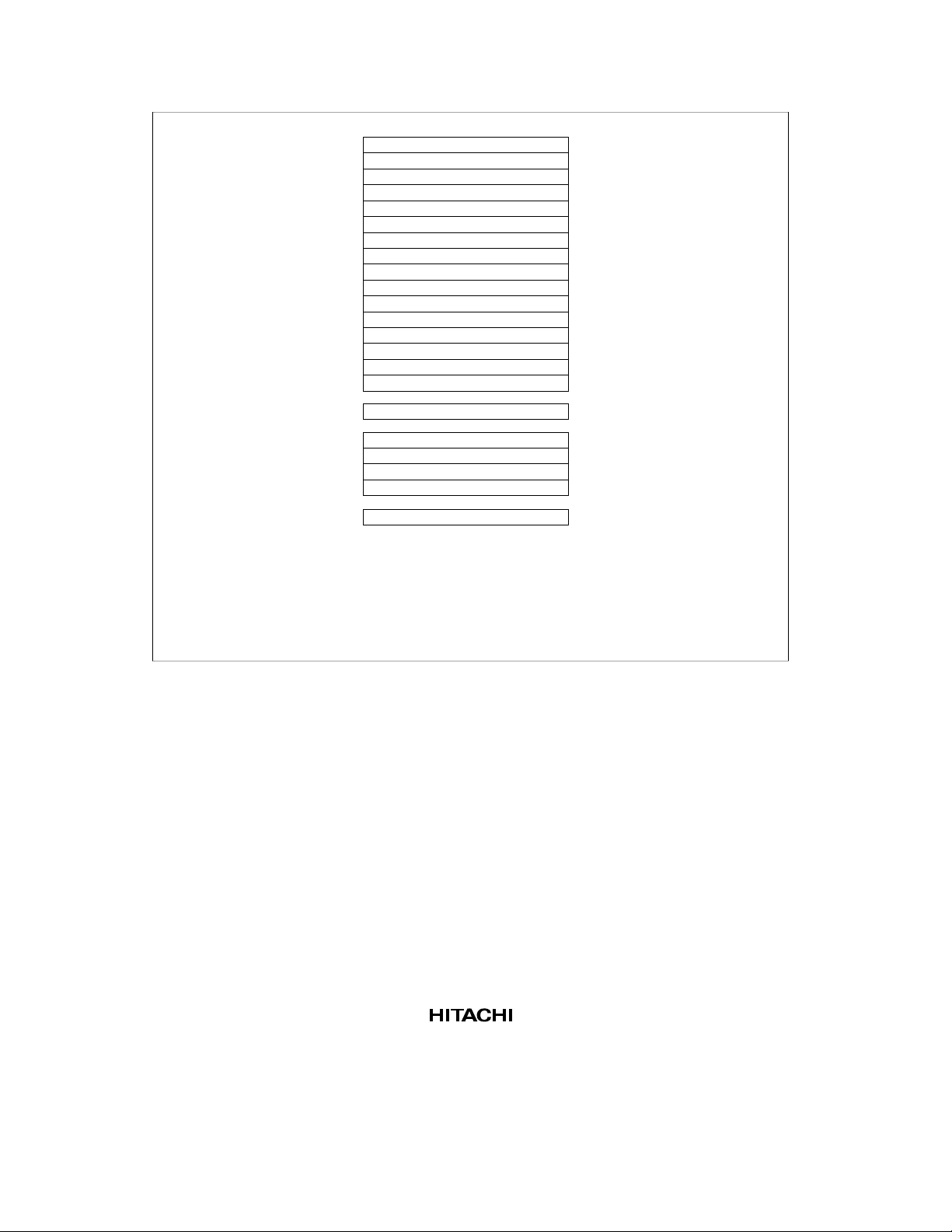

1.2 Block Diagram

Figure 1.1 shows a block diagram of the SH7708 Series.

Multiplier

MMU

(memory

management

unit)

Mixed

instruction/

data TLB

Cache

controller

Mixed

instruction/

data cache

memory

CPU

Interrupt

controller

32-bit data bus

32-bit virtual address bus

User break

controller

(2 channels)

Bus state

controller

SCI (serial

communication

interface)

Realtime

clock

Peripheral address bus

16-bit peripheral data bus

Timer

(3 channels)

PLL built-in

32-bit data bus

32-bit physical address bus

External bus

interface

clock

oscillator

WDT

(watchdog

timer)

I/O ports

Figure 1.1 SH7708 Series Block Diagram

6

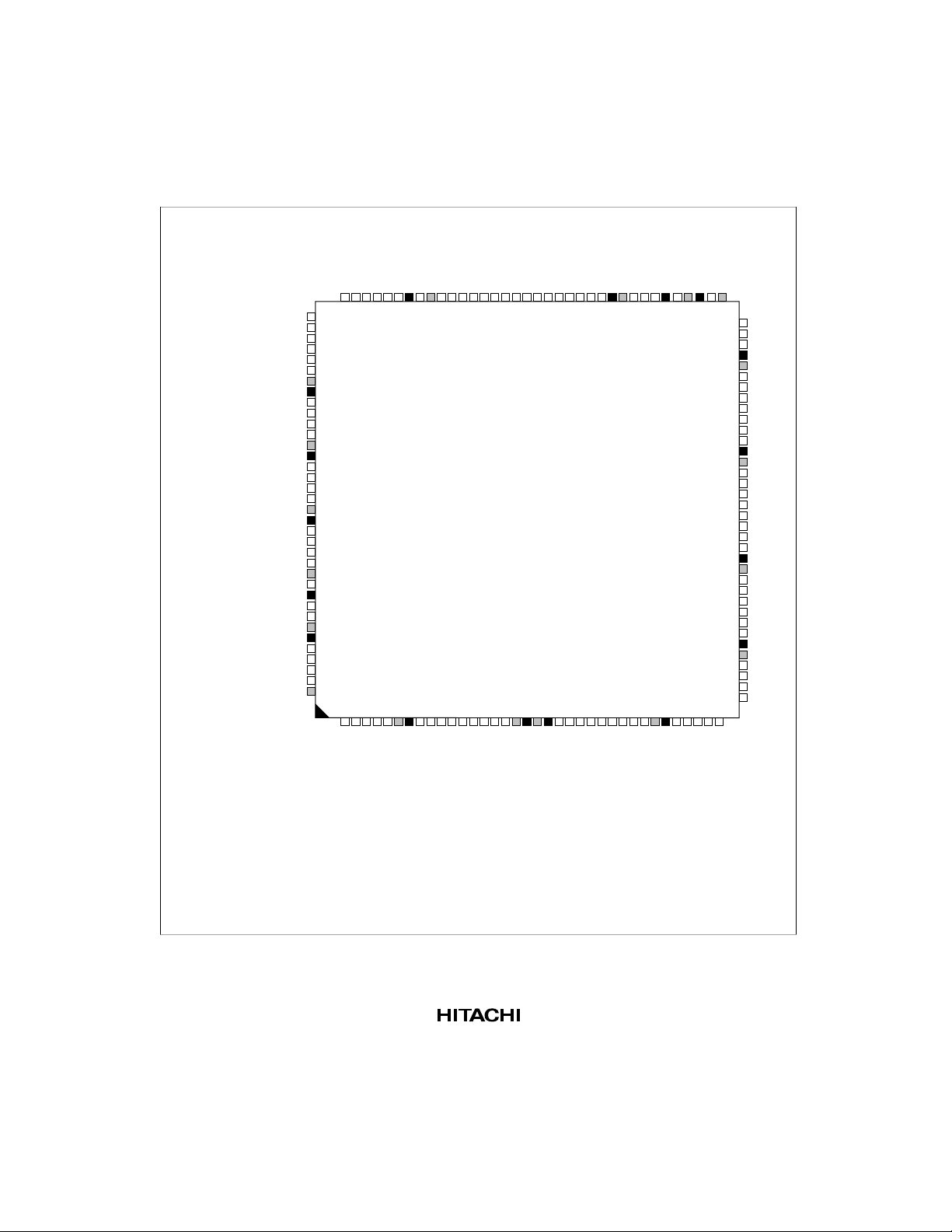

1.3 Pin Description

1.3.1 Pin Arrangement

CS6/CE1BRDRDWR

MD3/CE2A

MD4/CE2B

Vcc

CKIO

Vss

1

*

NC

STATUS0

STATUS1

BACK

IRQOUT

IOIS16

IRL0

IRL1

IRL2

IRL3

NMIBSRESET

BREQ

MD0/SCK

MD1/TXD

MD2/RXD

Vcc

Vss

4

*

XTAL

EXTAL

2

2

2

*

*

*

Vcc (PLL2)

CAP2

Vss (PLL2)

Vcc (PLL1)

2

*

CAP1

Vss (PLL1)

CS5/CE1A

CS4

CS3

CS2

CS1

CS0

Vss

WE3/DQMUU/ICIOWR

WE2/DQMUL/ICIORD

CASHH/CAS2H

CASHL/CAS2L

WE1/DQMLU

CASLL/CAS/OE

Vcc

Vss

Vcc

WE0/DQMLL

CASLH

Vss

Vcc

RAS/CE

MD5/RAS2

CKE

WAIT

Vss

TCLK

Vcc (RTC)

XTAL2

EXTAL2

Vss (RTC)

Vcc

D31

D30

D29

D28

Vss

100

90

120

SH7708(FP-144F)

SH7708S(TFP-144, FP-144F)

130

*2

*2

SH7708R(FP-144F)

Top view

140

144

1

D27

D26

D25

D24

Vss

Vcc

10

D15

D14

Vss

Vcc

Vss

20

Vcc

D13

D12

D11

D10

80

D9D8D7D6D5

30

D4D3D2D1D0

Vss

Vcc

70

60

50

40

A25

A24

A23

Vcc

Vss

A22

A21

A20

A19

A18

A17

A16

Vcc

Vss

A15

A14

A13

Vcc

Vss

A12

A11

A10

Vcc

Vss

A9

A8

A7

A6

A5

A4

Vcc

Vss

A3

A2

A1

A0

D17/Port1

D20/Port4

D19/Port3

D18/Port2

D16/Port0

Notes:

1.Make no connection.

D23/Port7

D22/Port6

D21/Port5

2.Power supply pins for the on-chip RTC and on-chip PLL. These pins must be

connected to the power supply even if the RTC or PLL are not used.

3.Power supply pins for the on-chip PLL. Except in hardware standby mode,

these pins must be connected to the power supply even if the PLL is not used.

4. SH7708:Vcc

SH7708S,SH7708R:CA

Figure 1.2 Pin Arrangement

7

1.3.2 SH7708 Series Pin Functions

Table 1.2 SH7708 Series Pin Functions

No. Terminal I/O Description

1 D27 I/O Data bus

2 D26 I/O Data bus

3 D25 I/O Data bus

4 D24 I/O Data bus

5 D23/Port7 I/ O Data bus/port

6V

7V

SS

CC

8 D22/Port6 I/ O Data bus/port

9 D21/Port5 I/ O Data bus/port

10 D20/Port4 I/ O Data bus/port

11 D19/Port3 I/ O Data bus/port

12 D18/Port2 I/ O Data bus/port

13 D17/Port1 I/ O Data bus/port

14 D16/Port0 I/ O Data bus/port

15 D15 I/O Data bus

16 D14 I/O Data bus

17 V

18 V

19 V

20 V

SS

CC

SS

CC

21 D13 I/O Data bus

22 D12 I/O Data bus

23 D11 I/O Data bus

24 D10 I/O Data bus

25 D9 I/O Data bus

26 D8 I/O Data bus

27 D7 I/O Data bus

28 D6 I/O Data bus

29 D5 I/O Data bus

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

8

Table 1.2 SH7708 Series Pin Functions (cont)

No. Terminal I/O Description

30 V

31 V

SS

CC

32 D4 I/O Data bus

33 D3 I/O Data bus

34 D2 I/O Data bus

35 D1 I/O Data bus

36 D0 I/O Data bus

37 A0 O Address bus

38 A1 O Address bus

39 A2 O Address bus

40 A3 O Address bus

41 V

42 V

SS

CC

43 A4 O Address bus

44 A5 O Address bus

45 A6 O Address bus

46 A7 O Address bus

47 A8 O Address bus

48 A9 O Address bus

49 V

50 V

SS

CC

51 A10 O Address bus

52 A11 O Address bus

53 A12 O Address bus

54 V

55 V

SS

CC

56 A13 O Address bus

57 A14 O Address bus

58 A15 O Address bus

59 V

60 V

SS

CC

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

9

Table 1.2 SH7708 Series Pin Functions (cont)

No. Terminal I/O Description

61 A16 O Address bus

62 A17 O Address bus

63 A18 O Address bus

64 A19 O Address bus

65 A20 O Address bus

66 A21 O Address bus

67 A22 O Address bus

68 V

69 V

SS

CC

70 A23 O Address bus

71 A24 O Address bus

72 A25 O Address bus

73 VSS(PLL1)*

2

74 CAP1 O External capacitance pin for PLL1

75 VCC(PLL1)*

76 VSS(PLL2)*

2

2

77 CAP2 O External capacitance pin for PLL2

78 VCC(PLL2)*

2

79 EXTAL I External clock/crystal oscillator pin

80 XTAL O Crystal oscillator pin

81(SH7708) V

81(SH7708S,

CC

CA I Chip active

SH7708R)

82 V

83 V

SS

CC

84 MD2/RXD I Operating mode pin/serial data input

85 MD1/TXD I/O Operating mode pin/serial data output

86 MD0/SCK I/O Operating mode pin/serial clock

87 BREQ I Bus request

88 RESET I Reset

89 NMI I Nonmaskable interrupt request

90 IRL3 I External interrupt source input

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V) for PLL1

Power Power (3.3 V) for PLL1

Power Power (0 V) for PLL2

Power Power (3.3 V) for PLL2

Power Power(3.3V)

Power Power (0 V)

Power Power (3.3 V)

10

Table 1.2 SH7708 Series Pin Functions (cont)

No. Terminal I/O Description

91 IRL2 I External interrupt source input

92 IRL1 I External interrupt source input

93 IRL0 I External interrupt source input

94 IOIS16 I IO16-bit instruction

95 IRQOUT O Bus request notification output

96 BACK O Bus acknowledge

97 STATUS1 O Processor status

98 STATUS0 O Processor status

99 NC O Leave unconnected

100 V

SS

101 CKIO I /O System clock I/O

102 V

CC

103 MD4/CE2B I/O Operating mode pin/PCMCIA CE pin

104 MD3/CE2A I/O Operating mode pin/PCMCIA CE pin

105 BS O Bus cycle start

106 RD/WR O Read/write

107 RD O Read pulse

108 CS6/CE1B O Chip select 6/PCMCIA CE pin

109 CS5/CE1A O Chip select 5/PCMCIA CE pin

110 CS4 O Chip select 4

111 CS3 O Chip select 3

112 CS2 O Chip select 2

113 CS1 O Chip select 1

114 CS0 O Chip select 0

115 V

116 V

SS

CC

117 WE3/DQMUU/ICIOWR O D31–D24 selection signal/IO write

118 WE2/DQMUL/ICIORD O D23–D16 selection signal/IO read

119 CASHH/CAS2H O D31–D24/D15–D8 selection signal

120 CASHL/CAS2L O D23–D16/D7–D0 selection signal

121 V

SS

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

11

Table 1.2 SH7708 Series Pin Functions (cont)

No. Terminal I/O Description

122 V

CC

123 WE1/DQMLU O D15–D8 selection signal

124 WE0/DQMLL O D7–D0 selection signal

125 CASLH O D15–D8 selection signal

126 CASLL/CAS/OE O D7–D0 selection/memory selection signal

127 V

128 V

SS

CC

129 RAS/CE O RAS for DRAM, SDRAM/CE for PSRAM

130 MD5/RAS2 I/O Operating mode pin/RAS for DRAM

131 CKE O Clock enable control for SDRAM

132 WAIT I Hardware wait request

133 V

SS

134 TCLK I/O Clock I/O for TMU/RTC

135 VCC (RTC)*

3

136 XTAL2 O Crystal oscillator pin for on-chip RTC

137 EXTAL2 I Crystal oscillator pin for on-chip RTC

138 VSS (RTC)*

139 V

CC

3

140 D31 I/O Data bus

141 D30 I/O Data bus

142 D29 I/O Data bus

143 D28 I/O Data bus

144 V

SS

Notes: 1. Except in hardware standby mode, connect all VCC and VSS pins to the system power

supply (power should be supplied constantly). In hardware standby mode, power should

be supplied at least to V

pins other than VCC (RTC) and VSS (RTC), hold the CA pin low.

2. Power should be supplied regardless of whether or not the on-chip PLL is used.

3. Power should be supplied regardless of whether or not the RTC is used.

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

Power Power (3.3 V)

Power Power (0 V)

(RTC) and VSS (RTC). If power is not supplied to VCC and V

CC

SS

12

Section 2 CPU

2.1 Register Configuration

2.1.1 Privileged Mode and Banks

Processor Modes: There are two processor modes: user mode and privileged mode. The

SH7708 Series normally operates in user mode, and enters privileged mode when an exception

occurs or an interrupt is accepted. There are three kinds of registers—general registers, system

registers, and control registers—and the registers that can be accessed differ in the two processor

modes.

General Registers: There are 16 general registers, designated R0 to R15. General registers R0

to R7 are banked registers which are switched by a processor mode change. In privileged mode, the

register bank bit (RB) in the status register (SR) defines which banked register set is accessed as

general registers, and which set is accessed only through the load control register (LDC) and store

control register (STC) instructions.

When the RB bit is 1, BANK1 general registers R0_BANK1–R7_BANK1 and non-banked general

registers R8–R15 function as the general register set, with BANK0 general registers R0_BANK0–

R7_BANK0 accessed only by the LDC/STC instructions.

When the RB bit is 0, BANK0 general registers R0_BANK0–R7_BANK0 and nonbanked general

registers R8–R15 function as the general register set, with BANK1 general registers R0_BANK1–

R7_BANK1 accessed only by the LDC/STC instructions. In user mode, the 16 registers

comprising bank 0 general registers R0_BANK0–R7_BANK0 and non-banked registers R8–R15

can be accessed as general registers R0–R15, and bank 1 general registers R0_BANK1–

R7_BANK1 cannot be accessed.

Control Registers: Control registers comprise the global base register (GBR) and status

register (SR) which can be accessed in both processor modes, and the saved status register (SSR),

saved program counter (SPC), and vector base register (VBR) which can only be accessed in

privileged mode. Some bits of the status register (such as the RB bit) can only be accessed in

privileged mode.

System Registers: System registers comprise the multiply and accumulate registers

(MACL/MACH), the procedure register (PR), and the program counter (PC). Access to these

registers does not depend on the processor mode.

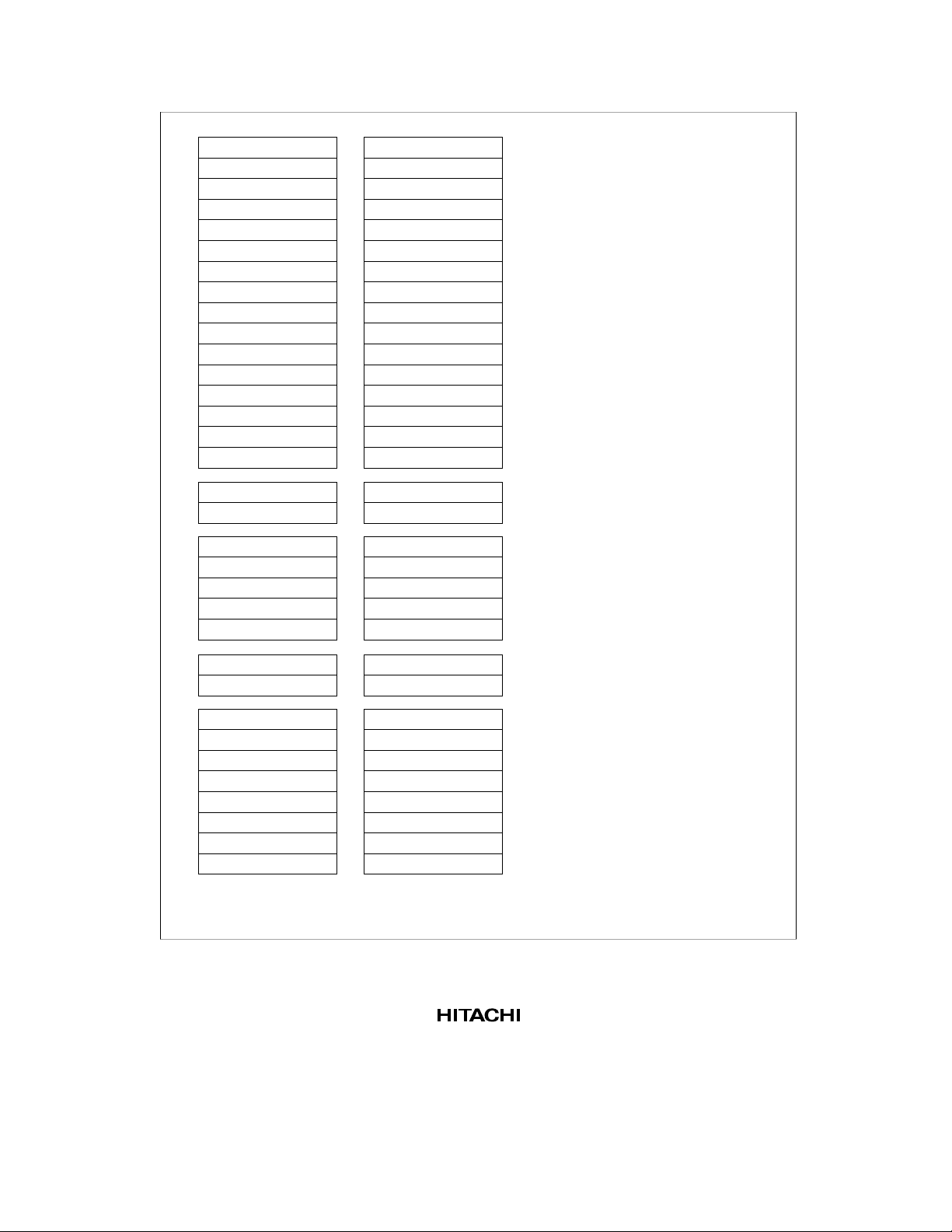

The register configuration in each mode is shown in figures 2.1 and 2.2.

Switching between user mode and privileged mode is controlled by the processor mode bit (MD) in

the status register.

13

31 0

R0_BANK0*

R1_BANK0*

R2_BANK0*

R3_BANK0*

R4_BANK0*

R5_BANK0*

R6_BANK0*

R7_BANK0*

1, *2

2

2

2

2

2

2

2

R8

R9

R10

R11

R12

R13

R14

R15

SR

GBR

MACH

MACL

PR

PC

User mode register configuration

14

Notes: 1.

R0 functions as an index register in the indexed register-indirect addressing

mode and indexed GBR-indirect addressing mode.

2.

Banked register

Figure 2.1 User Mode Register Configuration

31 0

R0_BANK1*

R1_BANK1*

R2_BANK1*

R3_BANK1*

R4_BANK1*

R5_BANK1*

R6_BANK1*

R7_BANK1*

1, *2

2

2

2

2

2

2

2

R8

R9

R10

R11

R12

R13

R14

R15

31 0

R0_BANK0*

R1_BANK0*

R2_BANK0*

R3_BANK0*

R4_BANK0*

R5_BANK0*

R6_BANK0*

R7_BANK0*

1, *3

3

3

3

3

3

3

3

R8

R9

R10

R11

R12

R13

R14

R15

SR

SSR

GBR

MACH

MACL

PR

VBR

PC

SPC

R0_BANK0*

R1_BANK0*

R2_BANK0*

R3_BANK0*

R4_BANK0*

R5_BANK0*

R6_BANK0*

R7_BANK0*

1, *3

3

3

3

3

3

3

3

a. Privileged mode

register configuration

(RB = 1)

SR

SSR

GBR

MACH

MACL

PR

VBR

PC

SPC

R0_BANK1*

R1_BANK1*

R2_BANK1*

R3_BANK1*

R4_BANK1*

R5_BANK1*

1, *2

2

2

2

2

2

R6_BANK1*2

R7_BANK1*

2

b. Privileged mode

register configuration

(RB = 0)

Notes:

R0 functions as an index

1.

register in the indexed

register-indirect addressing

mode and indexed GBR-

indirect addressing mode.

Banked register

2.

When the RB bit of the SR

register is 1, the register can

be accessed for general use.

When the RB bit is 0, it can

only be accessed with the

LDC/STC instruction.

Banked register

3.

When the RB bit of the SR

register is 0, the register can

be accessed for general use.

When the RB bit is 1, it can

only be accessed with the

LDC/STC instruction.

Figure 2.2 Privileged Mode Register Configuration

15

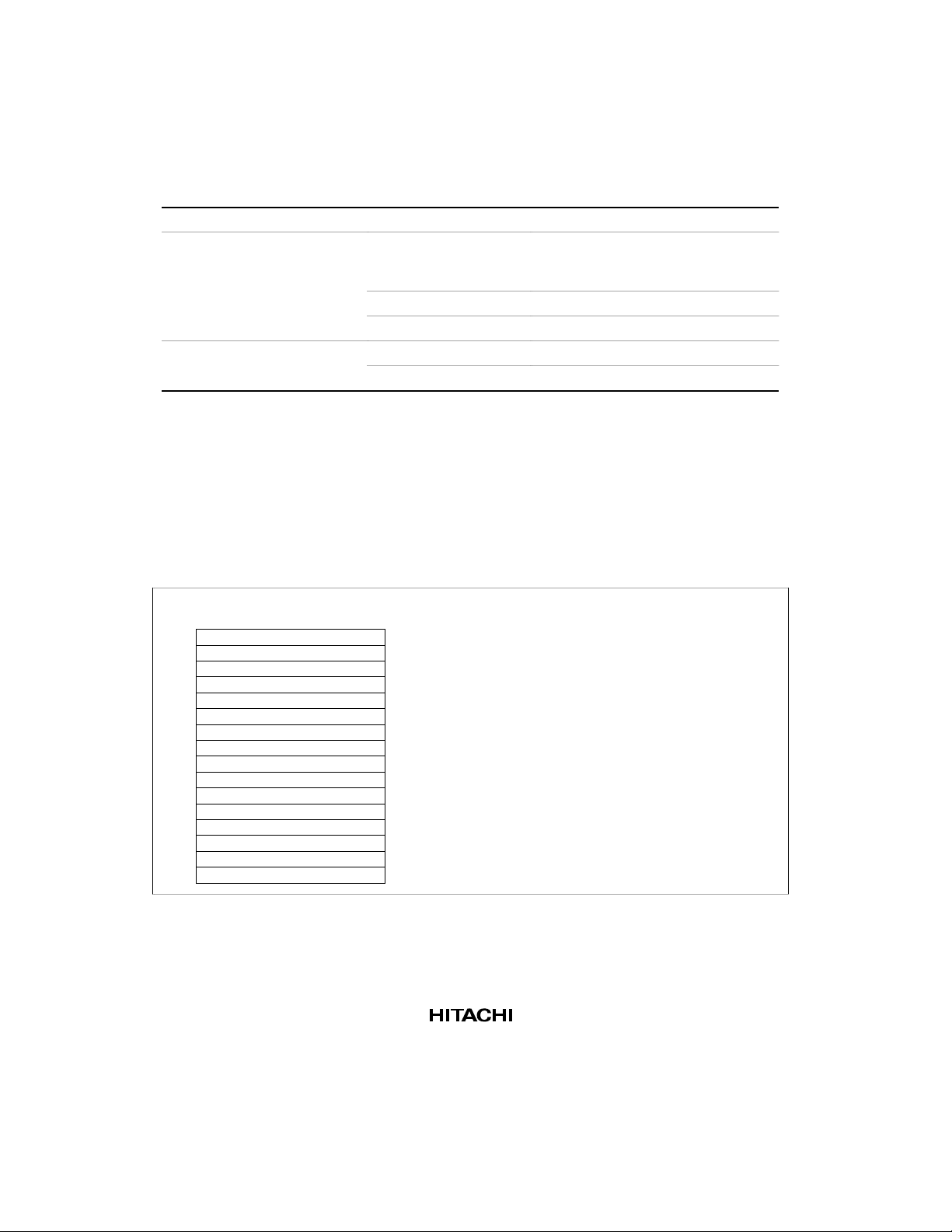

Register values after a reset are shown in table 2.1.

Table 2.1 Initial Register Values

Type Registers Initial Value

General registers R0 to R15 Undefined

Control registers SR MD bit = 1, RB bit = 1, BL bit = 1, I3–

I0 = 1111 (H'F), reserved bits = 0,

others undefined

GBR, SSR, SPC Undefined

VBR H'00000000

System registers MACH, MACL, PR Undefined

PC H'A0000000

Note: Initialized by a power-on reset or manual reset.

2.1.2 General Registers

There are 16 general registers, designated R0 to R15 (figure 2.3). General registers R0 to R7 are

banked registers, with a different R0–R7 register bank (R0_BANK0–R7_BANK0 or R0_BANK1–

R7_BANK1) being accessed according to the processor mode. For details, see section 2.1.1,

Privileged Mode and Banks.

31 0

1, *2

R0*

2

R1*

2

R2*

2

R3*

2

R4*

2

R5*

2

R6*

2

R7*

R8

R9

R10

R11

R12

R13

R14

R15

16

General Registers

Notes:

1.

R0 functions as an index register in the indexed

register-indirect addressing mode and indexed

GBR-indirect addressing mode. In some instructions,

only R0 can be used as the source register or

destination register.

2.

R0–R7 are banked registers.

In privileged mode, SR.RB specifies which banked

registers are accessed as general registers

(R0_BANK0–R7_BANK0 or R0_BANK1–R7_BANK1).

Figure 2.3 General Registers

Loading...

Loading...