HB28C048C6/HB28C032C6

HB28C016C6

CompactFlash™

48 MByte/32 MByte/16 MByte

ADE-203-1189A (Z)

Rev. 1.0

Dec. 1, 2000

Description

HB28C048C6, HB28C032C6, HB28C016C6 are CompactFlash™. This card complies with CompactFlash™

specification, and is suitable for the usage of data storage memory medium for PC or any other electric

equipment and digital still camera. This card is equipped with Hitachi 128 Mega bit Flash memory. This

card is suitable for ISA (Industry Standard Architecture) bus interface standard, and read/write unit is 1 sector

(512 bytes) sequential access. By using this card it is possible to operate good performance for the system

which have CompactFlashTM slots.

Note: CompactFlash™ is a trademark of SanDisk Corporation and is licensed royalty-free to the CFA which

in turn will license it royalty-free to CFA members.

*CFA: CompactFlash™ Association.

Features

• CompactFlash™ specification standard

50 pin two pieces connector and Type I (3.3 mm)

• 3.3V / 5V single power supply operation

• Card density is 48 Mega bytes maximum

This card is equipped with Hitachi 128 Mega bit Flash memory

• 3 variations of mode access

Memory card mode

I/O card mode

True IDE mode

• Internal self-diagnostic program operates at VCC power on

• High reliability based on internal ECC (Error Correcting Code) function

• Data reliability is 1 error in 1014 bits read

• Auto sleep mode

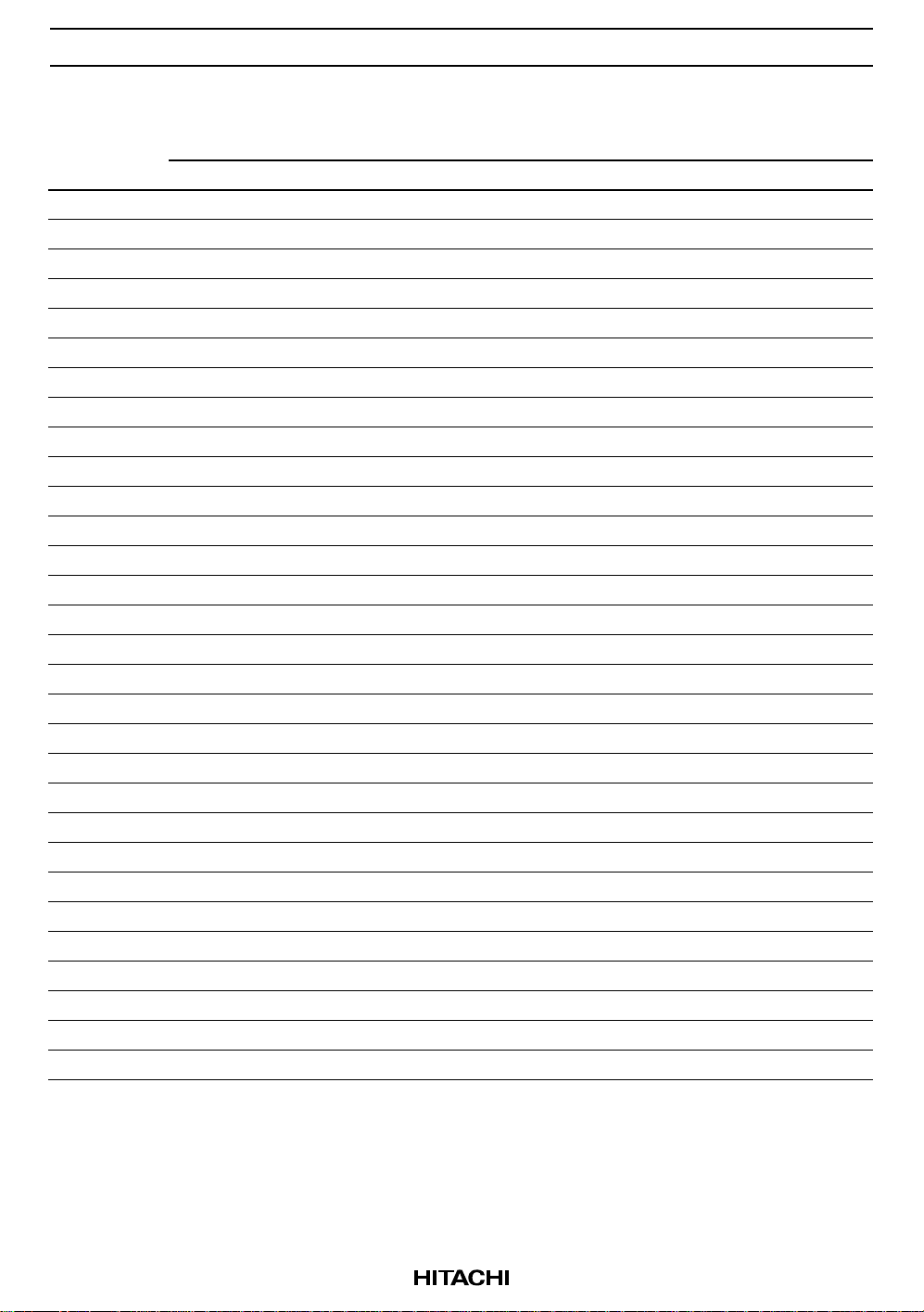

HB28C048/032/016C6

Card Line Up*

Type No. Card density Capacity*

1

4

Total sectors/

3

card*

Sectors/

2

track*

Number of

head

Number of

cylinder

HB28C048C6 48 MB 48,365,568 byte 94,464 32 4 738

HB28C032C6 32 MB 32,243,712 byte 62,976 32 4 492

HB28C016C6 16 MB 16,121,856 byte 31,488 32 2 246

Notes: 1. These data are written in ID.

2. Total tracks = number of head × number of cylinder.

3. Total sectors/card = sectors/track × number of head × number of cylinder.

4. It is the logical address capacity including the area which is used for file system.

2

HB28C048/032/016C6

Card Pin Assignment

Memory card mode I/O card mode True IDE mode

Pin No. Signal name I/O Signal name I/O Signal name I/O

1 GND — GND — GND —

2 D3 I/O D3 I/O D3 I/O

3 D4 I/O D4 I/O D4 I/O

4 D5 I/O D5 I/O D5 I/O

5 D6 I/O D6 I/O D6 I/O

6 D7 I/O D7 I/O D7 I/O

7 -CE1 I -CE1 I -CE1 I

8 A10 I A10 I A10 I

9 -OE I -OE I -ATASEL I

10 A9 I A9 I A9 I

11 A8 I A8 I A8 I

12 A7 I A7 I A7 I

13 VCC — VCC — VCC —

14 A6 I A6 I A6 I

15 A5 I A5 I A5 I

16 A4 I A4 I A4 I

17 A3 I A3 I A3 I

18 A2 I A2 I A2 I

19 A1 I A1 I A1 I

20 A0 I A0 I A0 I

21 D0 I/O D0 I/O D0 I/O

22 D1 I/O D1 I/O D1 I/O

23 D2 I/O D2 I/O D2 I/O

24 WP O -IOIS16 O -IOIS16 O

25 -CD2 O -CD2 O -CD2 O

26 -CD1 O -CD1 O -CD1 O

27 D11 I/O D11 I/O D11 I/O

28 D12 I/O D12 I/O D12 I/O

29 D13 I/O D13 I/O D13 I/O

30 D14 I/O D14 I/O D14 I/O

3

HB28C048/032/016C6

Memory card mode I/O card mode True IDE mode

Pin No. Signal name I/O Signal name I/O Signal name I/O

31 D15 I/O D15 I/O D15 I/O

32 -CE2 I -CE2 I -CE2 I

33 -VS1 O -VS1 O -VS1 O

34 -IORD I -IORD I -IORD I

35 -IOWR I -IOWR I -IOWR I

36 -WE I -WE I -WE I

37 RDY/-BSY O -IREQ O INTRQ O

38 VCC — VCC — VCC —

39 -CSEL I -CSEL I -CSEL I

40 -VS2 O -VS2 O -VS2 O

41 RESET I RESET I -RESET I

42 -WAIT O -WAIT O IORDY O

43 -INPACK O -INPACK O -INPACK O

44 -REG I -REG I -REG I

45 BVD2 I/O -SPKR I/O -DASP I/O

46 BVD1 I/O -STSCHG I/O -PDIAG I/O

47 D8 I/O D8 I/O D8 I/O

48 D9 I/O D9 I/O D9 I/O

49 D10 I/O D10 I/O D10 I/O

50 GND — GND — GND —

4

Card Pin Explanation

Signal name Direction Pin No. Description

A10 to A0

(PC Card Memory mode)

A10 to A0

(PC Card I/O mode)

A2 to A0

(True IDE mode)

BVD1

(PC Card Memory mode)

-STSCHG

(PC Card I/O mode)

-PDIAG

(True IDE mode)

BVD2

(PC Card Memory mode)

-SPKR

(PC Card I/O mode)

-DASP

(True IDE mode)

-CD1, -CD2

(PC Card Memory mode)

-CD1, -CD2

(PC Card I/O mode)

-CD1, -CD2

(True IDE mode)

-CE1, -CE2

(PC Card Memory mode)

Card Enable

-CE1, -CE2

(PC Card I/O mode)

Card Enable

-CE1, -CE2

(True IDE mode)

I 8, 10, 11, 12, 14,

15, 16, 17, 18,

19, 20

18, 19, 20 Address bus is A10 to A0. Only A2 to A0 are used,

I/O 46 BVD1 outputs the battery voltage status in the card.

I/O 45 BVD2 outputs the battery voltage status in the card.

O 26, 25 -CD1 and -CD2 are the card detection signals. -CD1

I 7, 32 -CE1 and -CE2 are low active card select signals.

Address bus is A10 to A0. A10 is MSB and A0 is

LSB.

A10 to A3 should be grounded by the host.

This output line is constantly driven to a high state

since a battery is not required for this product.

-STSCHG is used for changing the status of

Configuration and status register in attribute area.

-PDIAG is the Pass Diagnostic signal in Master/Slave

handshake protocol.

This output line is constantly driven to a high state

since a battery is not required for this product.

-SPKR outputs speaker signals. This output line is

constantly driven to a high state since this product

does not support the audio function.

-DASP is the Disk Active/Slave Present signal in the

Master/Slave handshake protocol.

and -CD2 are connected to ground in this card, so

host can detect that the card is inserted or not.

Byte/Word/Odd byte mode are defined by combination

of -CE1, -CE2 and A0.

-CE2 is used for select the Alternate Status Register

and the Device Control Register while -CE1 is the chip

select for the other task file registers.

HB28C048/032/016C6

5

HB28C048/032/016C6

Signal name Direction Pin No. Description

-CSEL

(PC Card Memory mode)

-CSEL

(PC Card I/O mode)

-CSEL

(True IDE mode)

D15 to D0

(PC Card Memory mode)

D15 to D0

(PC Card I/O mode)

D15 to D0

(True IDE mode)

GND

(PC Card Memory mode)

GND

(PC Card I/O mode)

GND

(True IDE mode)

-INPACK

(PC Card Memory mode)

-INPACK

(PC Card I/O mode)

Input Acknowledge

-INPACK

(True IDE mode)

-IORD

(PC Card Memory mode)

-IORD

(PC Card I/O mode)

-IORD

(True IDE mode)

I 39 This signal is not used.

This signal is used to configure this device as a

Master or a Slave when configured in the True IDE

mode. When this pin is grounded, this device is

configured as a Master. When the pin is open, this

device is configured as a Slave.

I/O 31, 30, 29, 28,

27, 49, 48, 47, 6,

5, 4, 3, 2, 23, 22,

21

— 1, 50 Ground

O 43 This signal is not used and should not be connected

I 34 This signal is not used.

Data bus is D15 to D0. D0 is the LSB of the even byte

of the word. D8 is the LSB of the odd byte of the

word.

at the host.

This signal is asserted low by this card when the card

is selected and responding to an I/O read cycle at the

address that is on the address bus during -CE and

-IORD are low. This signal is used for the input data

buffer control.

This signal is not used and should not be connected

at the host.

-IORD is used for control of read data in I/O task file

area. This card does not respond to -IORD until I/O

card interface setting up.

-IORD is used for control of read data in I/O task file

area. This card does not respond to -IORD until True

IDE interface setting up.

6

Signal name Direction Pin No. Description

-IOWR

(PC Card Memory mode)

-IOWR

(PC Card I/O mode)

-IOWR

(True IDE mode)

-OE

(PC Card Memory mode)

-OE

(PC Card I/O mode)

-ATASEL

(True IDE mode)

RDY/-BSY

(PC Card Memory mode)

-IREQ

(PC Card I/O mode)

INTRQ

(True IDE mode)

-REG

(PC Card Memory mode)

Attribute memory select

-REG

(PC Card I/O mode)

-REG

(True IDE mode)

I 35 This signal is not used.

-IOWR is used for control of data write in I/O task file

area. This card does not respond to -IOWR until I/O

card interface setting up.

-IOWR is used for control of data write in I/O task file

area. This card does not respond to -IOWR until True

IDE interface setting up.

I 9 -OE is used for the control of reading register’s data in

attribute area or task file area.

-OE is used for the control of reading register’s data in

attribute area.

To enable True IDE mode this input should be

grounded by the host.

O 37 The signal is RDY/-BSY pin. RDY/-BSY pin turns low

level during the card internal initialization operation at

VCC applied or reset applied, so next access to the

card should be after the signal turned high level.

This signal is active low -IREQ pin. The signal of low

level indicates that the card is requesting software

service to host, and high level indicates that the card

is not requesting.

This signal is the active high Interrupt Request to the

host.

I 44 -REG is used during memory cycles to distinguish

between task file and attribute memory accesses.

High for task file, Low for attribute memory is

accessed.

-REG is constantly low when task file or attribute

memory is accessed.

This input signal is not used and should be connected

to VCC.

HB28C048/032/016C6

7

HB28C048/032/016C6

Signal name Direction Pin No. Description

RESET

(PC Card Memory mode)

RESET

(PC Card I/O mode)

-RESET

(True IDE mode)

VCC

(PC Card Memory mode)

VCC

(PC Card I/O mode)

VCC

(True IDE mode)

-VS1, -VS2

(PC Card Memory mode)

-VS1, -VS2

(PC Card I/O mode)

-VS1, -VS2

(True IDE mode)

-WAIT

(PC Card Memory mode)

-WAIT

(PC Card I/O mode)

IORDY

(True IDE mode)

-WE

(PC Card Memory mode)

-WE

(PC Card I/O mode)

-WE

(True IDE mode)

I 41 This signal is active high RESET pin. If this signal is

asserted high, the card internal initialization begins to

operate. During the card internal initialization

RDY/-BSY is low. After the card internal initialization

RDY/-BSY is high.

This signal is active high RESET pin. If this signal is

asserted high, the card internal initialization begins to

operate. In this mode, RDY/-BSY signal can not be

used, so using Status Register the Ready/Busy status

can be confirmed.

This signal is active low -RESET pin. If this signal is

asserted low, all the register’s in this card are reset.

In this mode, RDY/-BSY signal can not be used, so

using status register the Ready/Busy status can be

confirmed.

— 13, 38 +5 V, +3.3 V power.

O 33, 40 These signals are intended to notify VCC requirement

to host. -VS1 is held grounded and -VS2 is

nonconnected in this card.

O 42 This signal is active low -WAIT pin. In this card this

signal is constantly high level.

This output signal may be used as IORDY. In this

card this signal is constantly high impedance.

I 36 -WE is used for the control of writing register’s data in

attribute memory area or task file area.

-WE is used for the control of writing register’s data in

attribute memory area.

This input signal is not used and should be connected

to VCC by the host.

8

Signal name Direction Pin No. Description

WP

(PC Card Memory mode)

Write Protect

-IOIS16

(PC Card I/O mode)

-IOIS16

(True IDE mode)

O 24 WP is held low because this card does not have write

protect switch.

-IOIS16 is asserted when task file registers are

accessed in 16-bit mode.

This output signal is asserted low when this device is

expecting a word data transfer cycle. Initial mode is

16-bit. If the user issues a Set Feature Command to

put the device in Byte access mode, the card permits

8-bit accesses.

HB28C048/032/016C6

9

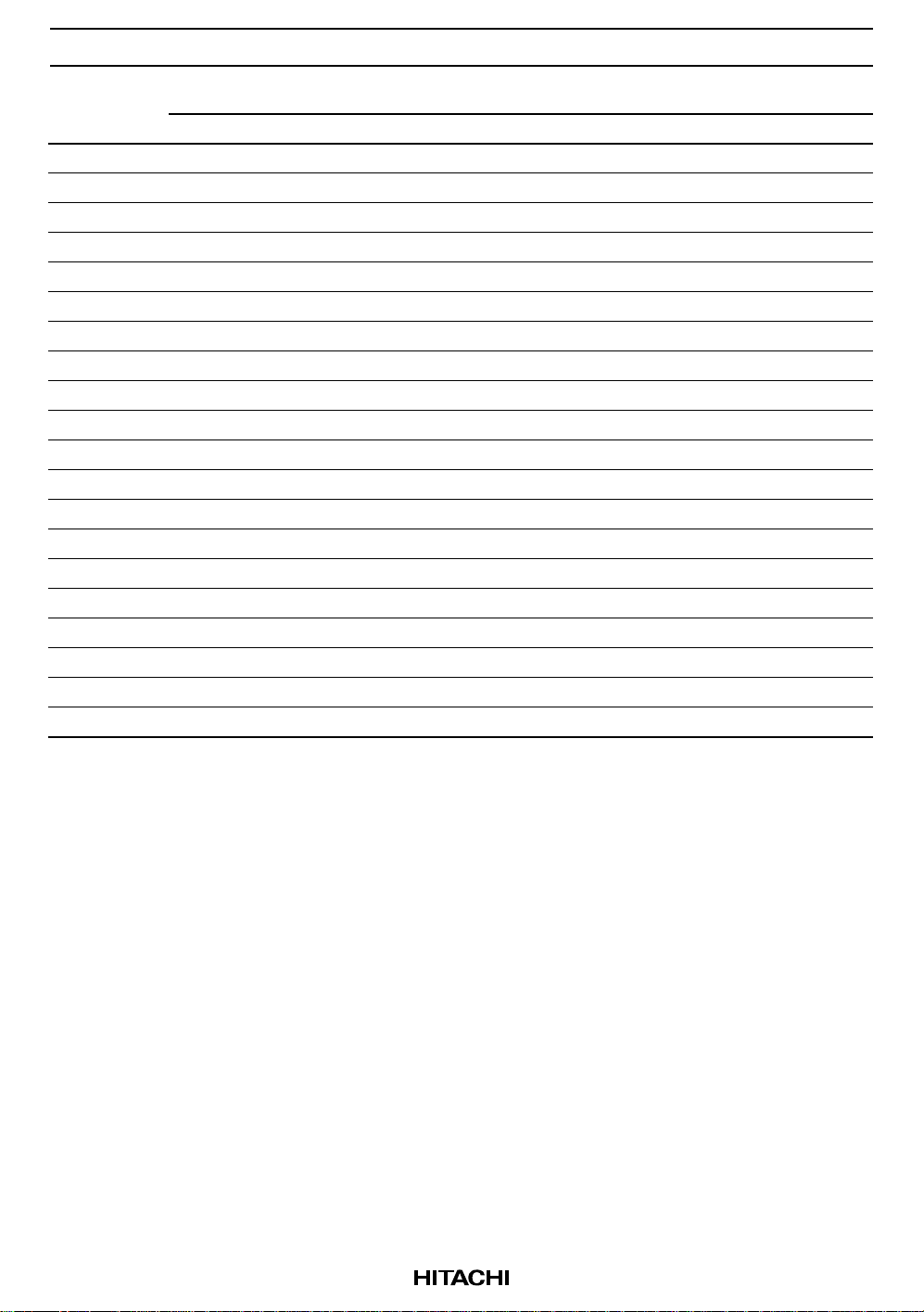

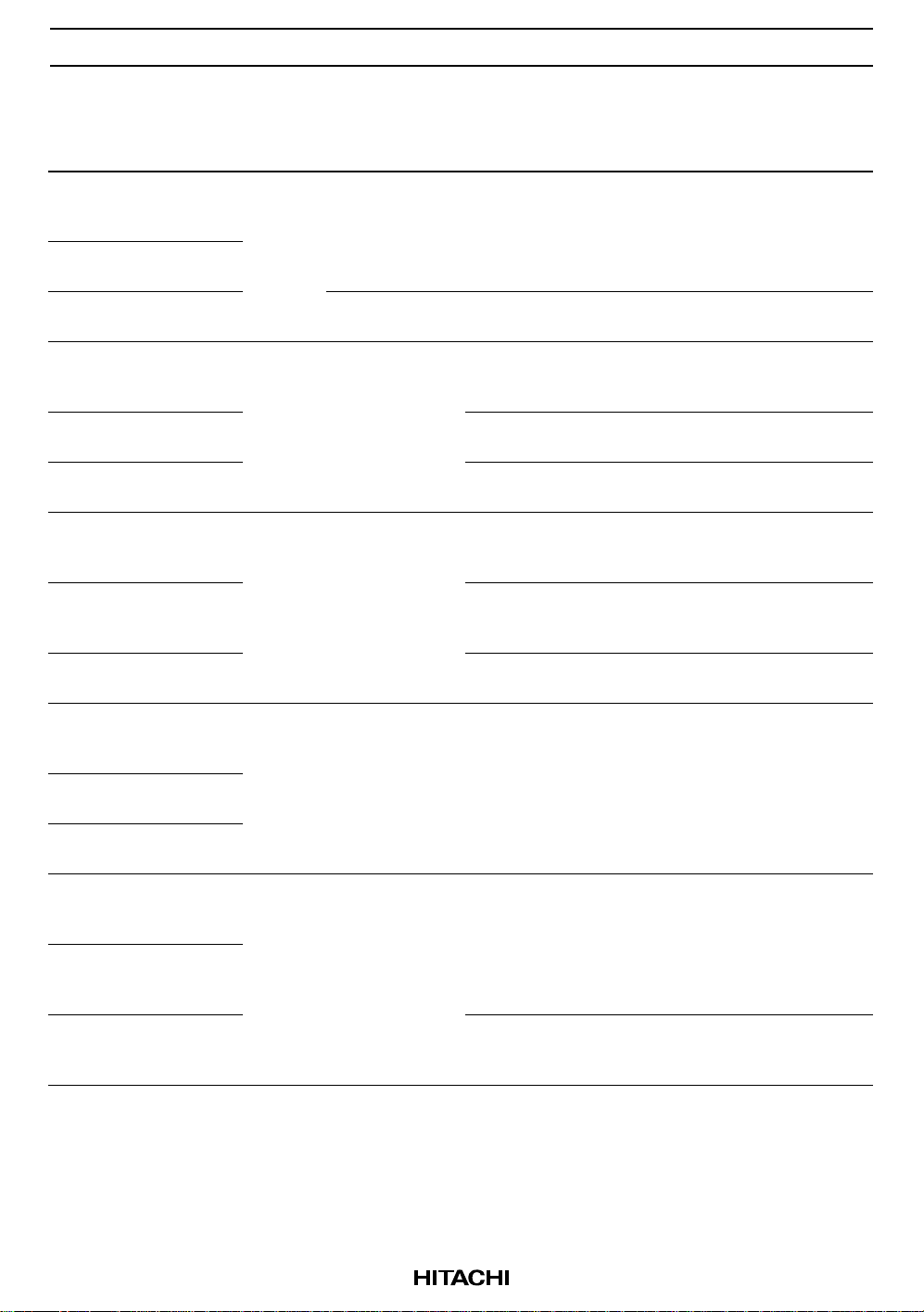

HB28C048/032/016C6

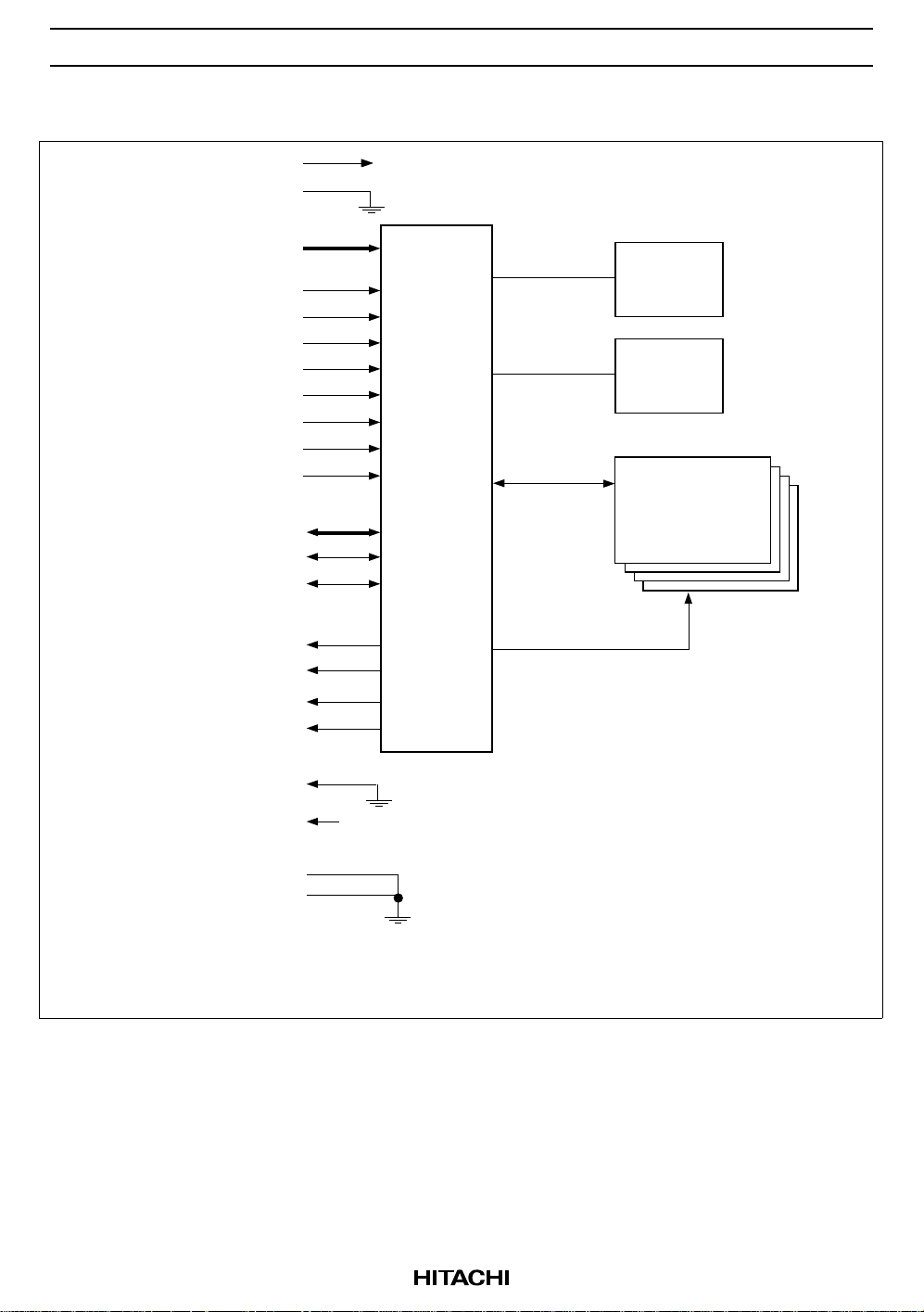

Card Block Diagram

VCC

GND

A0 to A10

-CE1,-CE2

-OE/-ATASEL

-WE

-IORD

-IOWR

-REG

RESET/-RESET

-CSEL

D0 to D15

BVD1/-STSCHG/-PDIAG

BVD2/-SPKR/-DASP

RDY/-BSY/-IREQ/INTRQ

WP/-IOIS16

internal V

Controller

CC

Reset IC

X'tal

Flash

memory

bus

Flash memory

Control signal

-INPACK

-WAIT/IORDY

-VS1

-VS2

-CD1

-CD2

Note: -CE1, -CE2, -OE, -WE, -IORD, -IOWR, -REG, RESET, -CSEL, -PDIAG, -DASP pins are

pulled up in card.

-CE1, -CE2, -OE, -WE, -IORD, -IOWR, -REG pins are schmitt trigger type input buffer.

OPEN

10

Card Function Explanation

Register construction

• Attribute region

Configuration register

• Configuration Option register

• Configuration and Status register

• Pin Replacement register

• Socket and Copy register

CIS ( C ard I nformation S tructure)

• Task File region

Data register

Error register

Feature register

Sector Count register

Sector Number register

Cylinder Low register

Cylinder High register

Drive Head register

Status register

Alternate Status register

Command register

Device Control register

Drive Address register

HB28C048/032/016C6

11

HB28C048/032/016C6

Host access specifications

1. Attribute access specifications

When CIS-ROM region or Configuration register region is accessed, read and write operations are executed

under the condition of -REG = "L" as follows. That region can be accessed by Byte/Word/Odd-byte modes

which are defined by PC card standard specifications.

Attribute Read Access Mode

Mode -REG -CE2 -CE1 A0 -OE -WE D8 to D15 D0 to D7

Standby mode × HH×××High-Z High-Z

Byte access (8-bit) L H LLLHHigh-Z even byte

L H L H L H High-Z invalid

Word access (16-bit) L L L × L H invalid even byte

Odd byte access (8-bit) L L H × L H invalid High-Z

Note: ×: L or H

Attribute Write Access Mode

Mode -REG -CE2 -CE1 A0 -OE -WE D8 to D15 D0 to D7

Standby mode × HH×××Don’t care Don’t care

Byte access (8-bit) L H L L H L Don’t care even byte

L H L H H L Don’t care Don’t care

Word access (16-bit) L L L × H L Don’t care even byte

Odd byte access (8-bit) L L H × H L Don’t care Don’t care

Note: ×: L or H

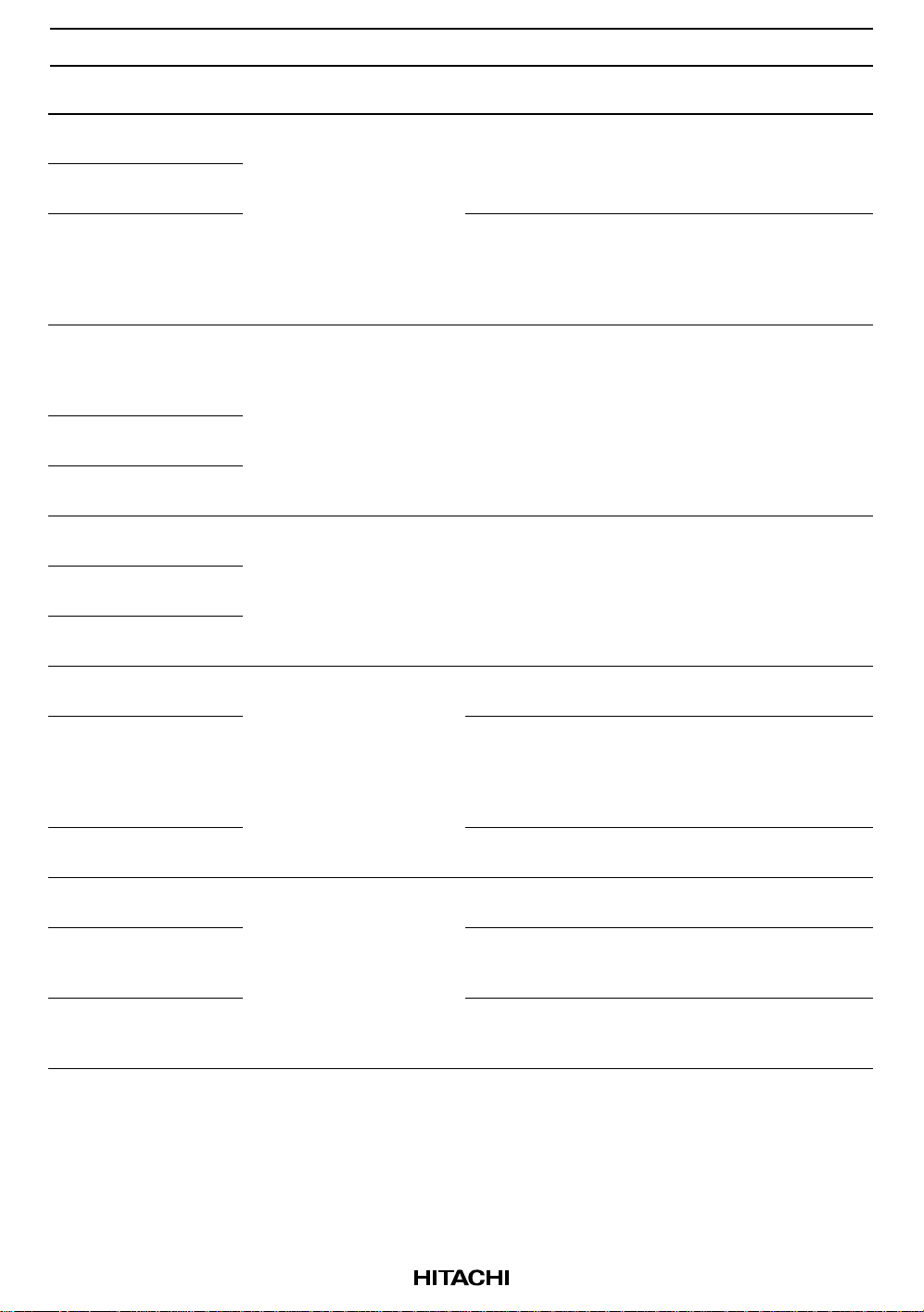

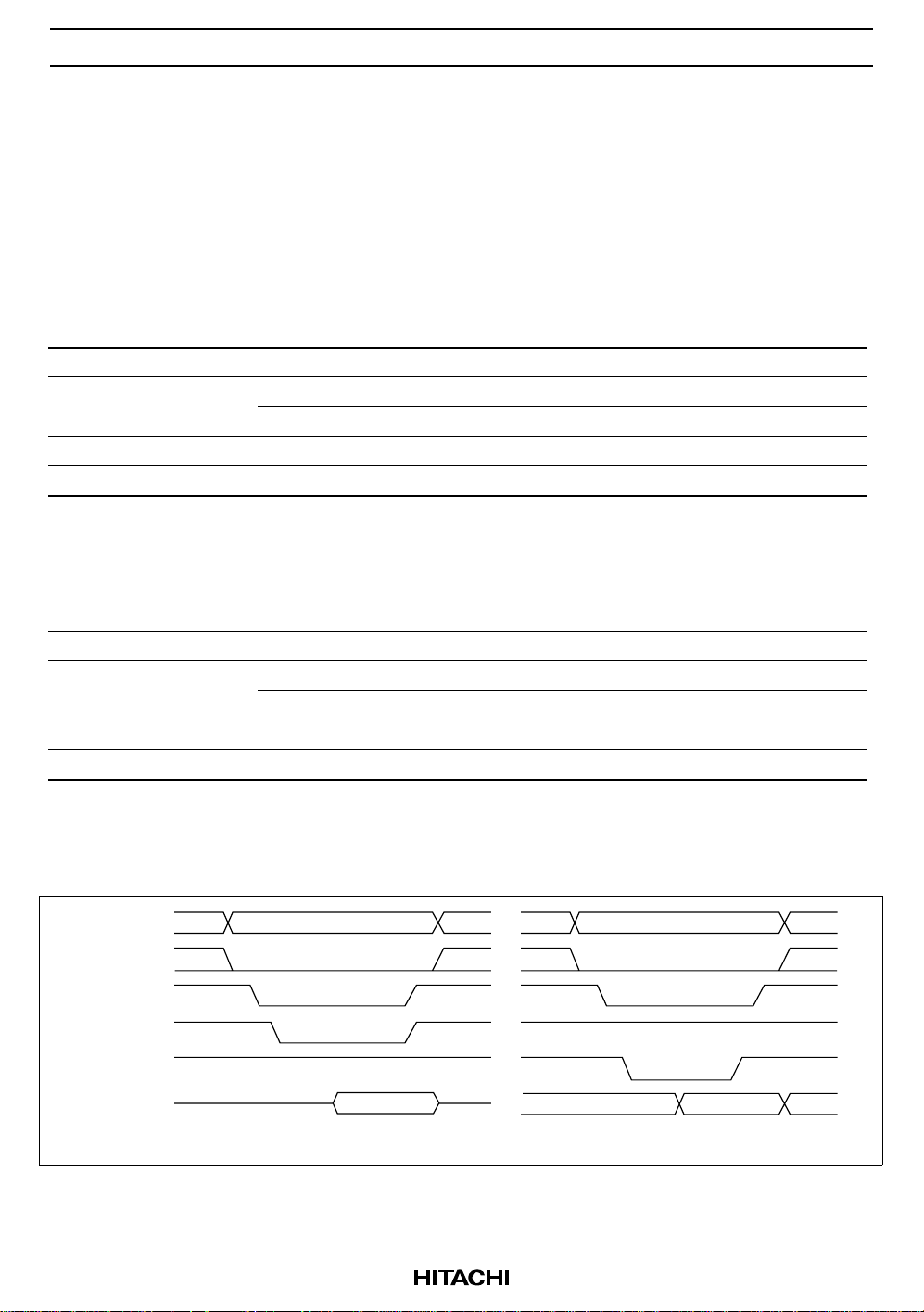

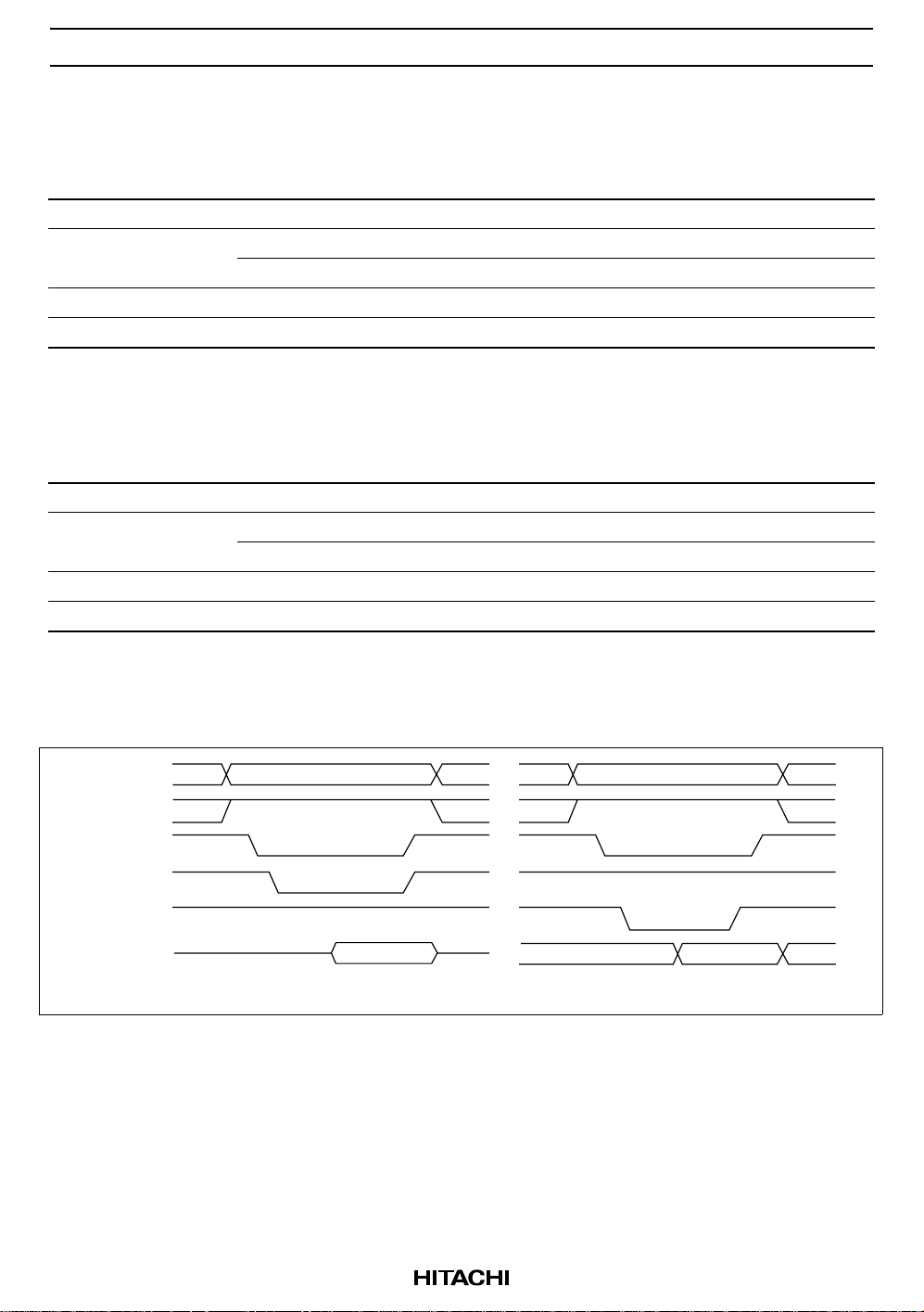

Attribute Access Timing Example

A0 to A10

-REG

-CE2/-CE1

-OE

-WE

D0 to D15

read cycle write cycle

Dout

Din

12

HB28C048/032/016C6

2. Task File register access specifications

There are two cases of Task File register mapping, one is mapped I/O address area, the other is mapped Memory address

area. Each case of Task File register read and write operations are executed under the condition as follows. That area can

be accessed by Byte/Word/Odd Byte mode which are defined by PC card standard specifications.

(1) I/O address map

Task File Register Read Access Mode (1)

Mode -REG -CE2 -CE1 A0 -IORD -IOWR -OE -WE D8 to D15 D0 to D7

Standby mode × HHЧЧЧЧЧHigh-Z High-Z

Byte access (8-bit) L H L L L H H H High-Z even byte

L H L H L H H H High-Z odd byte

Word access (16-bit) L L L × L H H H odd byte even byte

Odd byte access (8-bit) L L H × L H H H odd byte High-Z

Note: ×: L or H

Task File Register Write Access Mode (1)

Mode -REG -CE2 -CE1 A0 -IORD -IOWR -OE -WE D8 to D15 D0 to D7

Standby mode × HHЧЧЧЧЧDon’t care Don’t care

Byte access (8-bit) L H L L H L H H Don’t care even byte

L H L H H L H H Don’t care odd byte

Word access (16-bit) L L L × H L H H odd byte even byte

Odd byte access (8-bit) L L H × H L H H odd byte Don’t care

Note: ×: L or H

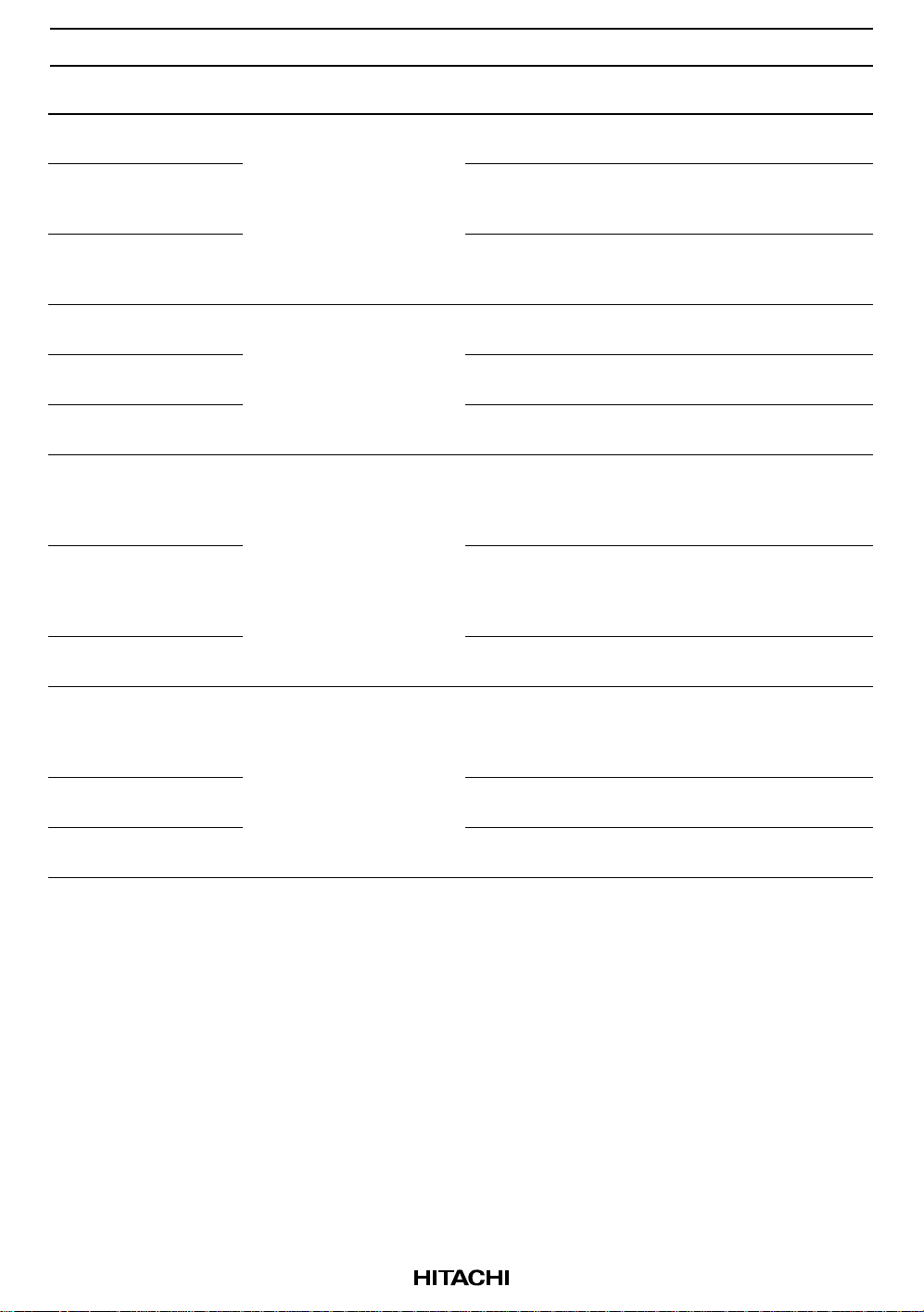

Task File Register Access Timing Example (1)

A0 to A10

-REG

-CE2/-CE1

-IORD

- IOWR

D0 to D15

Dout

read cycle write cycle

Din

13

HB28C048/032/016C6

(2) Memory address map

Task File Register Read Access Mode (2)

Mode -REG -CE2 -CE1 A0 -OE -WE -IORD -IOWR D8 to D15 D0 to D7

Standby mode × HHЧЧЧЧЧHigh-Z High-Z

Byte access (8-bit) H H L L L H H H High-Z even byte

H H L H L H H H High-Z odd byte

Word access (16-bit) H L L × L H H H odd byte even byte

Odd byte access (8-bit) H L H × L H H H odd byte High-Z

Note: ×: L or H

Task File Register Write Access Mode (2)

Mode -REG -CE2 -CE1 A0 -OE -WE -IORD -IOWR D8 to D15 D0 to D7

Standby mode × HHЧЧЧЧЧDon’t care Don’t care

Byte access (8-bit) H H L L H L H H Don’t care even byte

H H L H H L H H Don’t care odd byte

Word access (16-bit) H L L × H L H H odd byte even byte

Odd byte access (8-bit) H L H × H L H H odd byte Don’t care

Note: ×: L or H

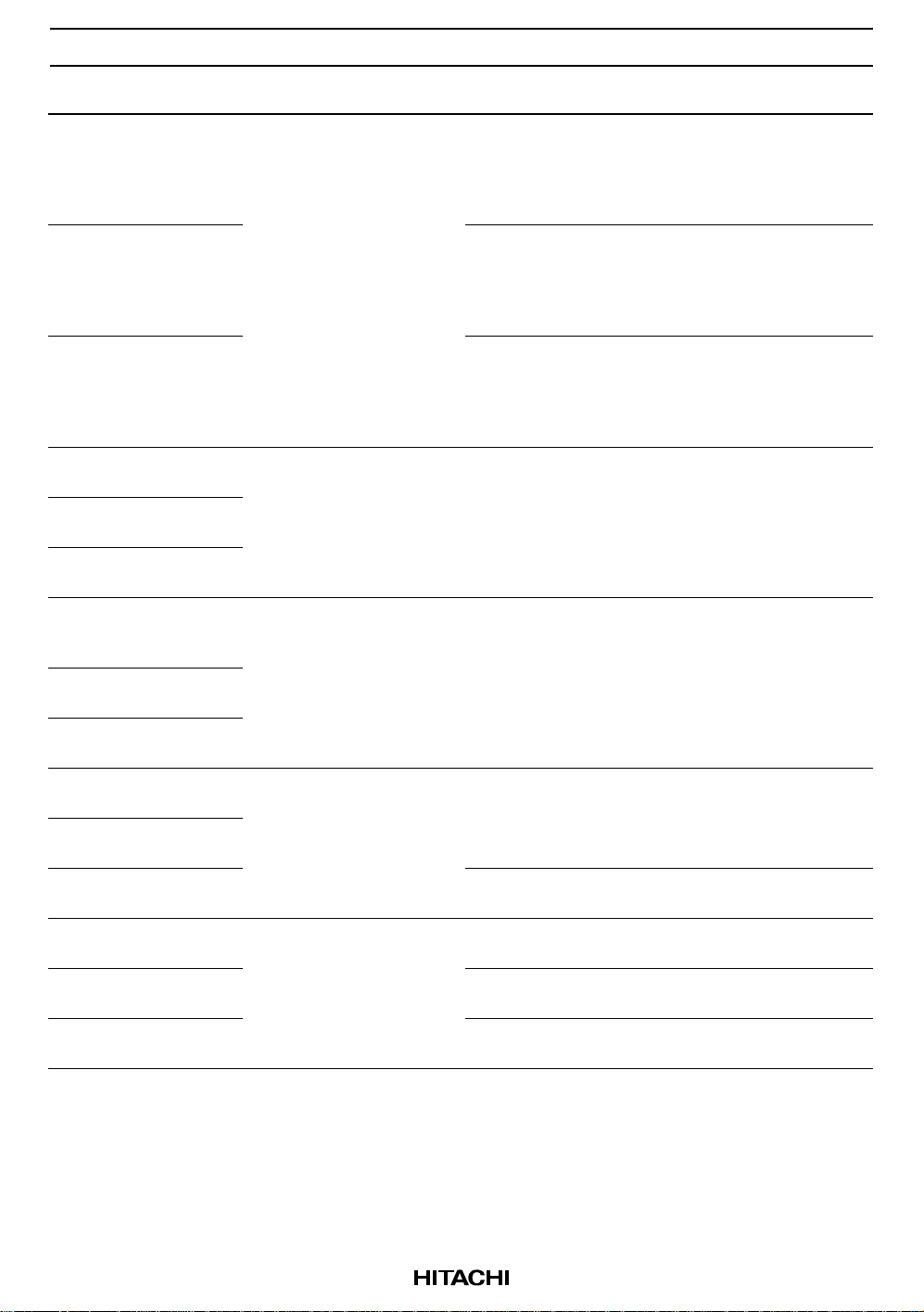

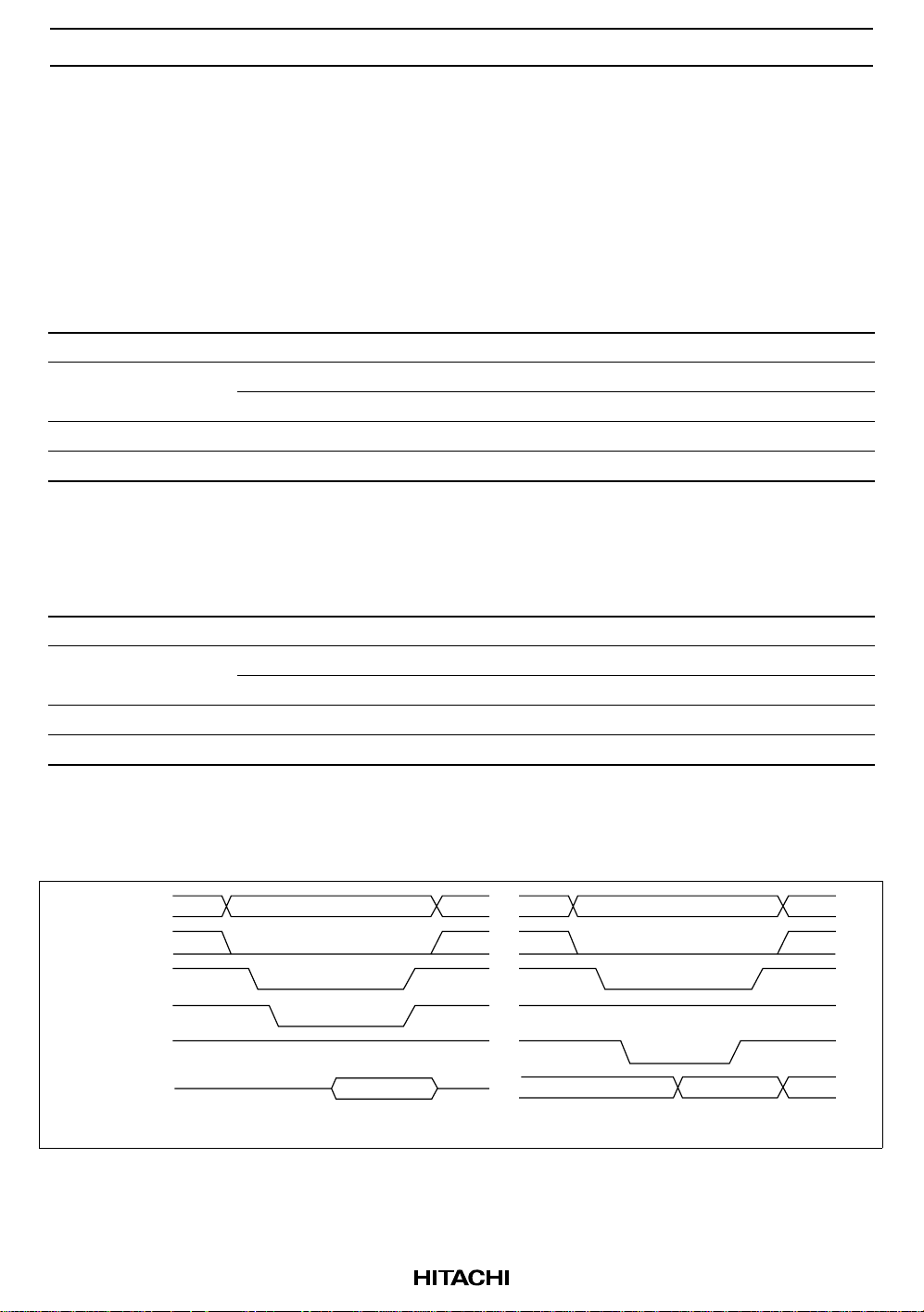

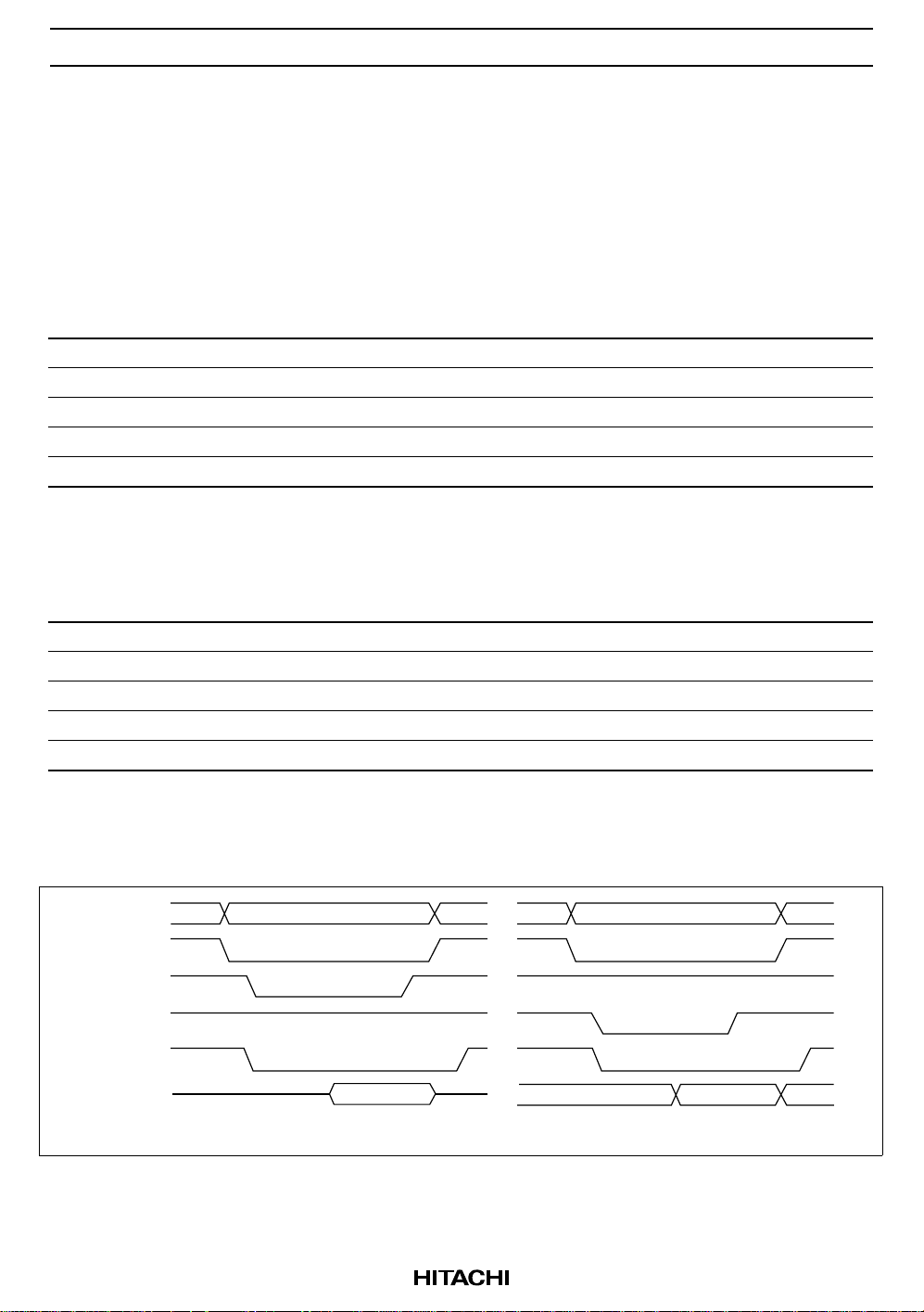

Task File Register Access Timing Example (2)

A0 to A10

-REG

-CE2/-CE1

-OE

-WE

D0 to D15

read cycle write cycle

Dout

Din

14

HB28C048/032/016C6

3. True IDE Mode

The card can be configured in a True IDE mode of operation. This card is configured in this mode only when the -OE

input signal is asserted GND by the host. In this True IDE mode Attribute Registers are not accessible from the host.

Only I/O operation to the task file and data register are allowed. If this card is configured during power on

sequence, data register are accessed in word (16-bit). The card permits 8-bit accesses if the user issues a Set Feature

Command to put the device in 8-bit mode.

True IDE Mode Read I/O Function

Mode -CE2 -CE1 A0 to A2 -IORD -IOWR D8 to D15 D0 to D7

Invalid mode L L ×××High-Z High-Z

Standby mode H H ×××High-Z High-Z

Data register access H L0LHodd byte even byte

Alternate status access L H 6H L H High-Z status out

Other task file access H L 1-7H L H High-Z data

Note: ×: L or H

True IDE Mode Write I/O Function

Mode -CE2 -CE1 A0 to A2 -IORD -IOWR D8 to D15 D0 to D7

Invalid mode L L ×××don’t care don’t care

Standby mode H H ×××don’t care don’t care

Data register access H L 0 H L odd byte even byte

Control register access L H 6H H L don’t care control in

Other task file access H L 1-7H H L don’t care data

Note: ×: L or H

True IDE Mode I/O Access Timing Example

A0 to A2

-CE

-IORD

-IOWR

-IOIS16

D0 to D15

read cycle write cycle

Dout

Din

15

HB28C048/032/016C6

Configuration register specifications

This card supports four Configuration registers for the purpose of the configuration and observation of this

card. These registers can be used in memory card mode and I/O card mode. In True IDE mode, these

registers can not be used.

1. Configuration Option register (Address 200H)

This register is used for the configuration of the card configuration status and for the issuing soft reset to the

card.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

SRESET LevlREQ INDEX

Note: initial value: 00H

Name R/W Function

SRESET

(HOST->)

LevlREQ

(HOST->)

INDEX

(HOST->)

R/W Setting this bit to "1", places the card in the reset state (Card Hard Reset). This

operation is equal to Hard Reset, except this bit is not cleared. Then this bit set to "0",

places the card in the reset state of Hard Reset (This bit is set to "0" by Hard Reset) .

Card configuration status is reset and the card internal initialized operation starts when

Card Hard Reset is executed, so next access to the card should be the same sequence

as the power on sequence.

R/W This bit sets to "0" when pulse mode interrupt is selected, and "1" when level mode

interrupt is selected.

R/W This bits is used for select operation mode of the card as follows.

When Power on, Card Hard Reset and Soft Reset, this data is "000000" for the purpose

of Memory card interface recognition.

INDEX bit assignment

INDEX bit

5 4 3 2 1 0 Card mode Task File register address Mapping mode

0 0 0 0 0 0 Memory card 0H to FH, 400H to 7FFH memory mapped

0 0 0 0 0 1 I/O card xx0H to xxFH contiguous I/O mapped

0 0 0 0 1 0 I/O card 1F0H to 1F7H, 3F6H to 3F7H primary I/O mapped

0 0 0 0 1 1 I/O card 170H to 177H, 376H to 377H secondary I/O mapped

16

HB28C048/032/016C6

2. Configuration and Status register (Address 202H)

This register is used for observing the card state.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

CHGED SIGCHG IOIS8 0 0 PWD INTR 0

Note: initial value: 00H

Name R/W Function

CHGED

(CARD->)

SIGCHG

(HOST->)

IOIS8

(HOST->)

PWD

(HOST->)

INTR

(CARD->)

R This bit indicates that CRDY/-BSY bit on Pin Replacement register is set to "1". When

CHGED bit is set to "1", -STSCHG pin is held "L" at the condition of SIGCHG bit set to

"1" and the card configured for the I/O interface.

R/W This bit is set or reset by the host for enabling and disabling the status-change signal (-

STSCHG pin). When the card is configured I/O card interface and this bit is set to "1", STSCHG pin is controlled by CHGED bit. If this bit is set to "0", -STSCHG pin is kept

"H".

R/W The host sets this field to "1" when it can provide I/O cycles only with on 8-bit data bus

(D7 to D0).

R/W When this bit is set to "1", the card enters sleep state (Power Down mode). When this

bit is reset to "0", the card transfers to idle state (active mode). RRDY/-BSY bit on Pin

Replacement Register becomes BUSY when this bit is changed. RRDY/-BSY will not

become Ready until the power state requested has been entered. This card

automatically powers down when it is idle, and powers back up when it receives a

command.

R This bit indicates the internal state of the interrupt request. This bit state is available

whether I/O card interface has been configured or not. This signal remains true until the

condition which caused the interrupt request has been serviced. If interrupts are

disabled by the -IEN bit in the Device Control Register, this bit is a zero.

17

HB28C048/032/016C6

3. Pin Replacement register (Address 204H)

This register is used for providing the signal state of -IREQ signal when the card configured I/O card interface.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0 0 CRDY/-BSY 0 1 1 RRDY/-BSY 0

Note: initial value: 0CH

Name R/W Function

CRDY/-BSY

(HOST->)

RRDY/-BSY

(HOST->)

4. Socket and Copy register (Address 206H)

This register is used for identification of the card from the other cards. Host can read and write this register.

This register should be set by host before this card's Configuration Option register set.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0 0 0 DRV# 0 0 0 0

Note: initial value: 00H

R/W This bit is set to "1" when the RRDY/-BSY bit changes state. This bit may also be

written by the host.

R/W When read, this bit indicates +READY pin states. When written, this bit is used for

CRDY/-BSY bit masking.

Name R/W Function

DRV#

(HOST->)

R/W This fields are used for the configuration of the plural cards. When host configures the

plural cards, written the card’s copy number in this field. In this way, host can perform

the card’s master/slave organization.

18

HB28C048/032/016C6

CIS informations

CIS informations are defined as follows. By reading attribute address from "0000 H", card CIS informations

can be confirmed.

Address Data 7 6 5 43210 Description of contents CIS function

000H 01H CISTPL_DEVICE Device info tuple Tuple code

002H 04H TPL_LINK Link length is 4 byte Link to next tuple

004H DFH Device type W

006H 4AH EXT Speed

mantissa

008H 01H 1x 2k units 2k byte of address space Device size

00AH FFH List end marker End of device END marker

00CH 1CH CISTPL_DEVICE_OC Other conditions device info

00EH 04H TPL_LINK Link length is 4 bytes Link to next tuple

010H 02H EXT Reserved V

012H D9H Device type W

014H 01H 1x 2k units 2k byte of address space Device size

016H FFH List end marker End of device END marker

018H 18H CISTPL_JEDEC_C JEDEC ID common memory Tuple code

01AH 02H TPL_LINK Link length is 2 bytes Link to next tuple

01CH DFH PCMCIA’s manufacturer’s JEDEC

ID code

01EH 01H PCMCIA JEDEC device code 2nd byte of JEDEC ID

020H 20H CISTPL_MANFID Manufacturer’s ID code Tuple code

022H 04H TPL_LINK Link length is 4 bytes Link to next tuple

024H 07H Low byte of PCMCIA

manufacturer’s code

026H 00H High byte of PCMCIA

manufacturer’s code

028H 00H Low byte of product code HITACHI code for PC CARD

02AH 00H High byte of product code High byte of product code

Device speed Device type = DH: I/O device

P

S

Speed

exponent

MWAIT 3 V, wait is not used Other conditions info field

CC

Device speed Device type = DH: I/O device

P

S

WPS = 1: No WP

Device speed = 7: ext speed

400 ns if no wait Extended speed

tuple

WPS = 1: No WP

Device speed = 1: 250 ns

Manufacturer’s ID code JEDEC ID of PC Card ATA

HITACHI JEDEC

manufacturer’s ID

Code of 0 because other byte

is JEDEC 1 byte

manufacture’s ID

ATA

Device type, WPS, speed

Tuple code

Device type, WPS, speed

Low byte of manufacturer’s

ID code

High byte of manufacturer’s

ID code

Low byte of product code

19

HB28C048/032/016C6

Address Data 7 6 5 43210 Description of contents CIS function

02CH 15H CISTPL_VERS_1 Level 1 version/product info Tuple code

02EH 15H TPL_LINK Link length is 15h bytes Link to next tuple

030H 04H TPPLV1_MAJOR PCMCIA2.0/JEIDA4.1 Major version

032H 01H TPPLV1_MINOR PCMCIA2.0/JEIDA4.1 Minor version

034H 48H ‘ H ’ Info string 1

036H 49H ‘ I ’

038H 54H ‘ T ’

03AH 41H ‘ A ’

03CH 43H ‘ C ’

03EH 48H ‘ H ’

040H 49H ‘ I ’

042H 00H Null terminator

044H 46H ‘ F ’ Info string 2

046H 4CH ‘ L ’

048H 41H ‘ A ’

04AH 53H ‘ S ’

04CH 48H ‘ H ’

04EH 00H Null terminator

050H 35H ‘ 5 ’ Vender specific strings

052H 2EH ‘ . ’

054H 30H ‘ 0 ’

056H 00H Null terminator

058H FFH List end marker End of device END marker

05AH 21H CISTPL_FUNCID Function ID tuple Tuple code

05CH 02H TPL_LINK Link length is 2 bytes Link to next tuple

05EH 04H TPLFID_FUNCTION = 04H Disk function, may be silicon,

may be removable

060H 01H Reserved R P R = 0: No BIOS ROM

P = 1: Configure card at

power on

PC card function code

System initialization byte

20

Loading...

Loading...