HIT HB288064MM1 Datasheet

HB288064MM1

MultiMediaCard

64 MByte

ADE-203-1191 (Z)

Preliminary

Rev. 0.0

Jul. 25, 2000

Description

The Hitachi MultiMediaCard HB288064MM1 is a highly integrated flash memory with serial and

random access capability. It is accessible via a dedicated serial interface optimized for fast and reliable

data transmission. This interface allows several cards to be stacked by through connecting their peripheral

contacts. The HB288064MM1 is fully compatible to a new consumer standard, called the MultiMediaCard

system standard defined in the MultiMediaCard system specification [1]. The MultiMediaCard system is a

new mass-storage system based on innovations in semiconductor technology. It has been developed to

provide an inexpensive, mechanically robust storage medium in card form for multimedia consumer

applications. MultiMediaCard allows the design of inexpensive players and drives without moving parts.

A low power consumption and a wide supply voltage range favors mobile, battery-powered applications

such as audio players, organizers, palmtops, electronic books, encyclopedia and dictionaries. Using very

effective data compression schemes such as MPEG, the MultiMediaCard will deliver enough capacity for

all kinds of multimedia data: software/programs, text, music, speech, images, video etc.

Note: MultiMediaCard is a trademark of Siemens AG.

Features

• 64 MByte memory capacity

• On card error correction

Preliminary: The specifications of this device are subject to change without notice. Please contact your

nearest Hitachi’s Sales Dept. regarding specifications.

HB288064MM1

• MultiMediaCard system standard compatibility

System specification version 2.11 compliant

SPI interface supported

Block and partial block read supported (Command classes 0 and 2)

Stream read supported (Command class 1)

Block write and erase supported (Command classes 4 and 5)

Group write protection (Command classes 6)

Stream write supported (Command classes 3)

Password data access protection

Small erase block size of 512 bytes, tagged erase supported

Read block size programmable between 1 and 2048 bytes

VCC = 2.7 V to 3.6 V operation voltage range (VCC = 2.0 V to 3.6 V for the interface)

No external programming voltage required

Damage free powered card insertion and removal

4kV ESD protection

• High speed serial interface with random access

Read speed: sustained: 13.7 Mbits/s (multi-block read)

burst (one block): 20 Mbit/s

Write speed: sustained: 2.8 Mbit/s (multi-block write to pre-erased sectors)

burst (one block): 20 Mbit/s

Up to 10 stacked card (at 20 MHz, VCC = 2.7 to 3.6V)

Access time: 300 µs (max) (at 20 MHz, VCC = 2.7 to 3.6V, random byte access (Typical case))

• Low power dissipation

High speed: 95 mW (max) (at 20 MHz, VCC = 2.7 V)

2

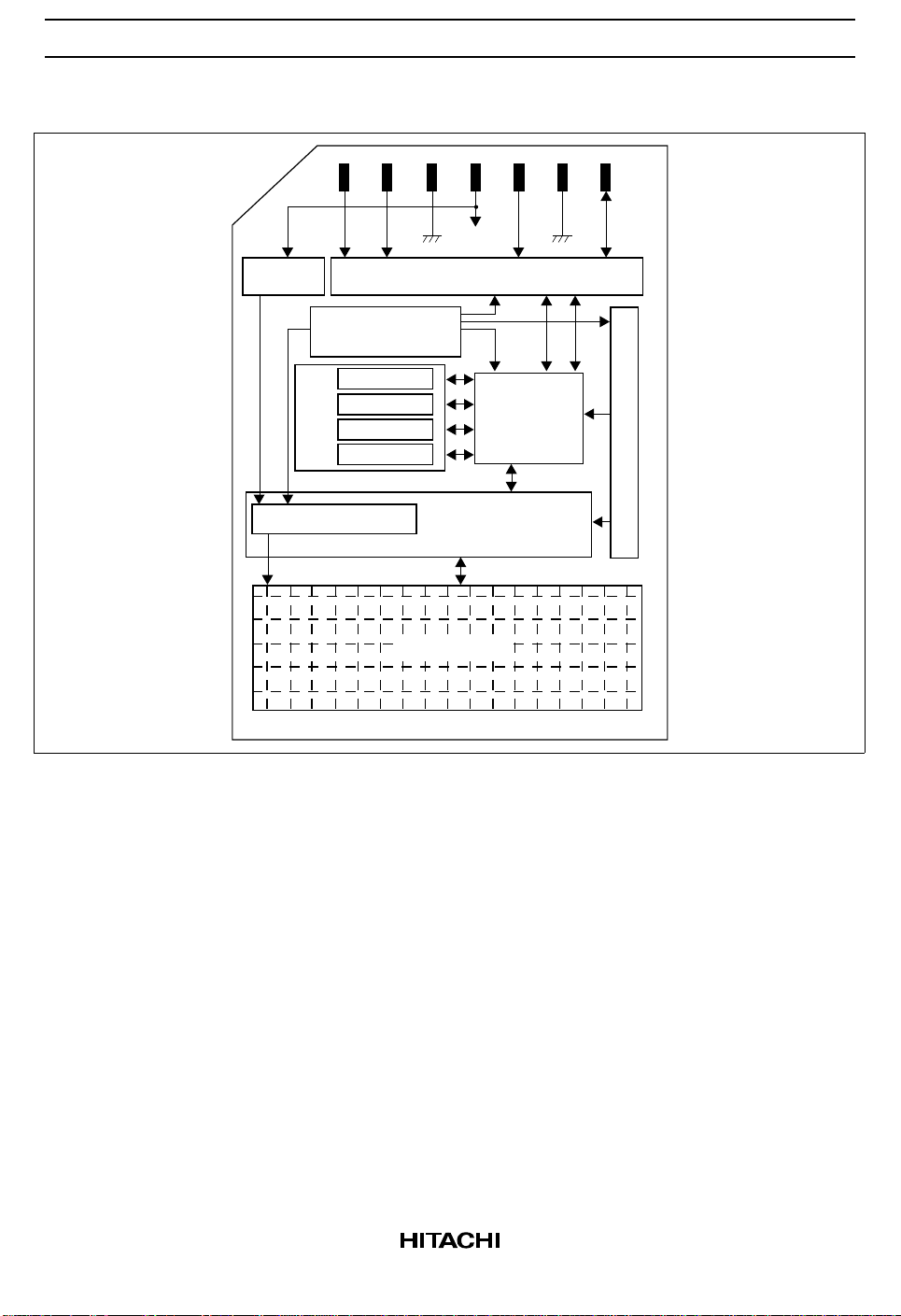

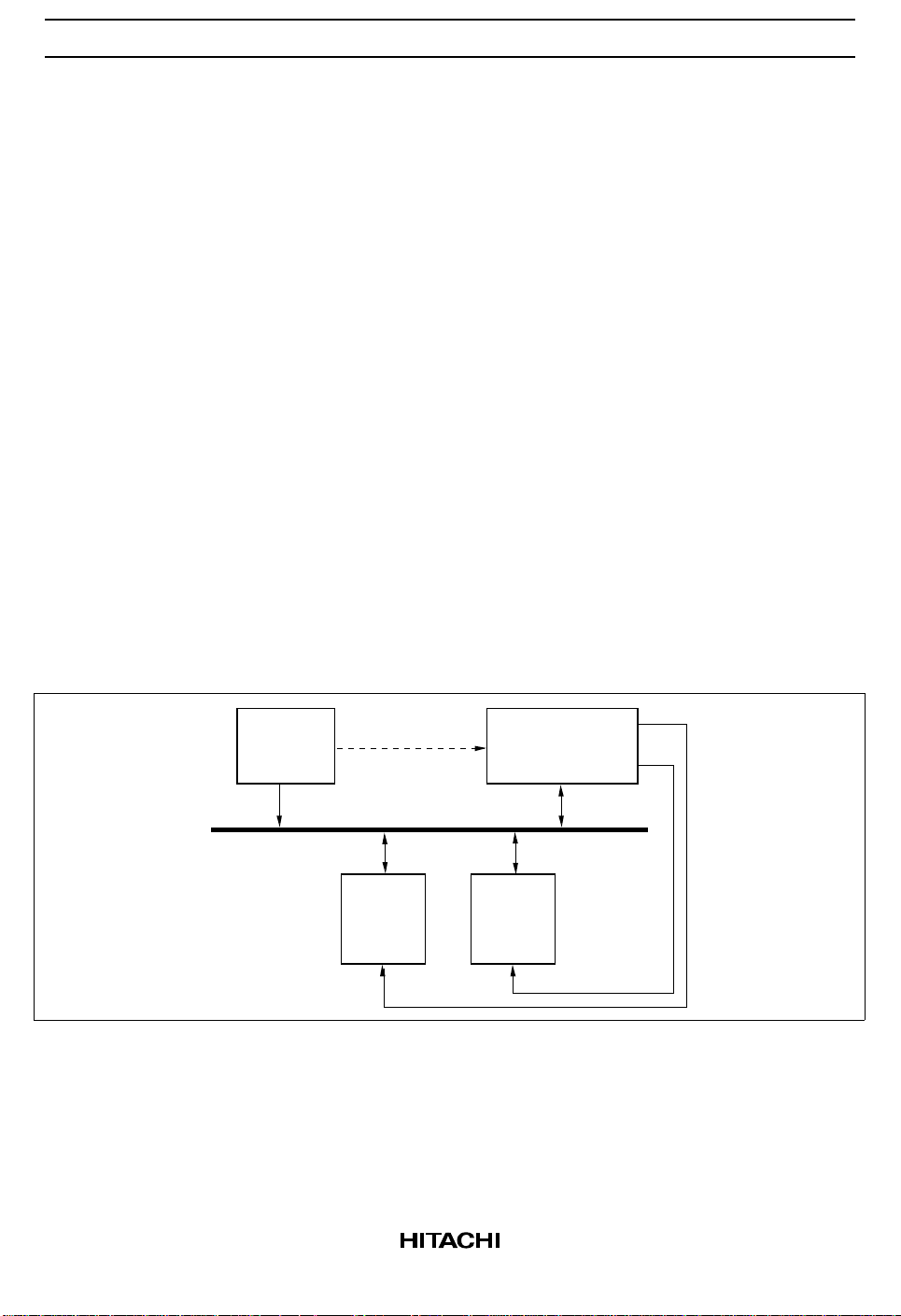

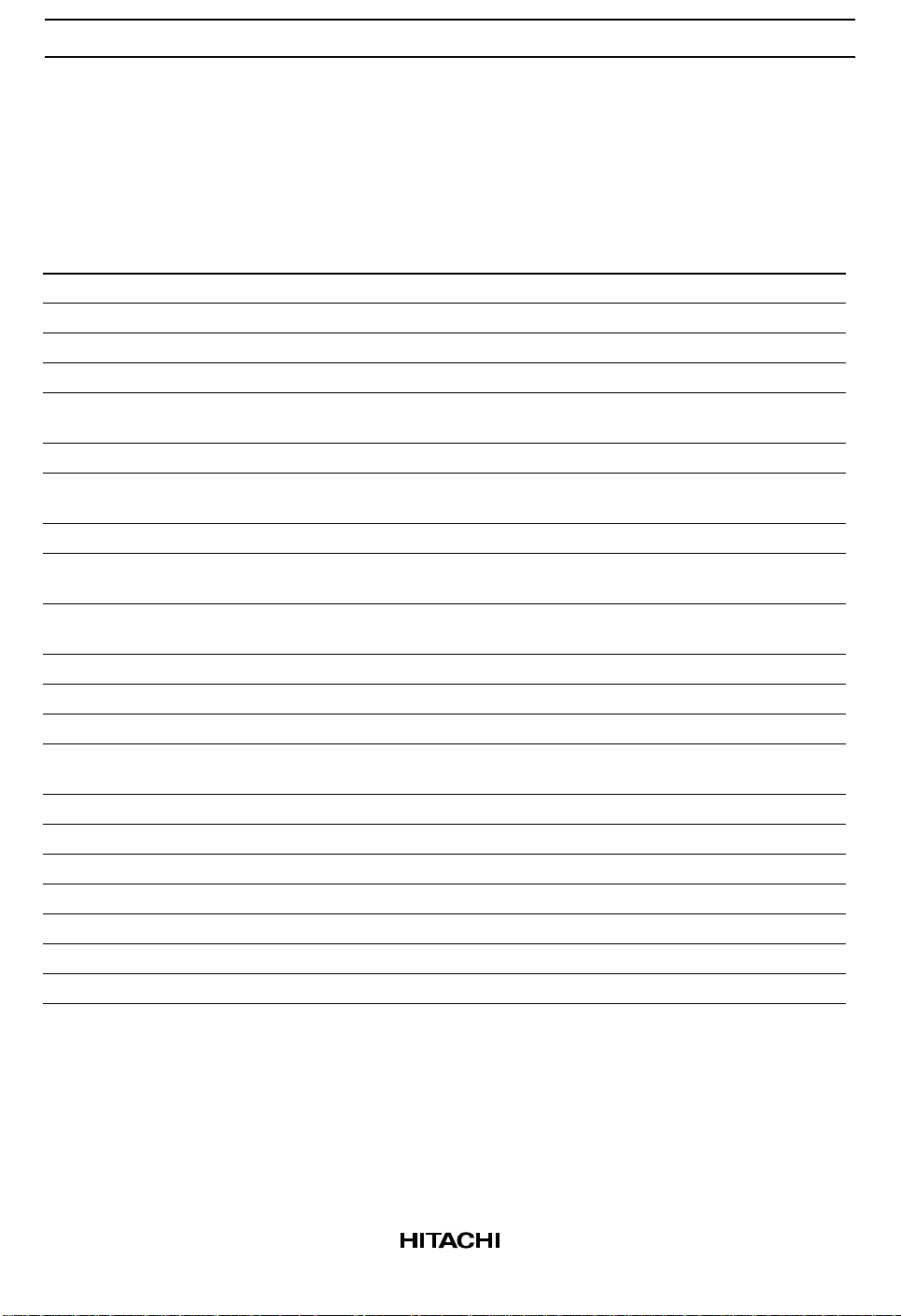

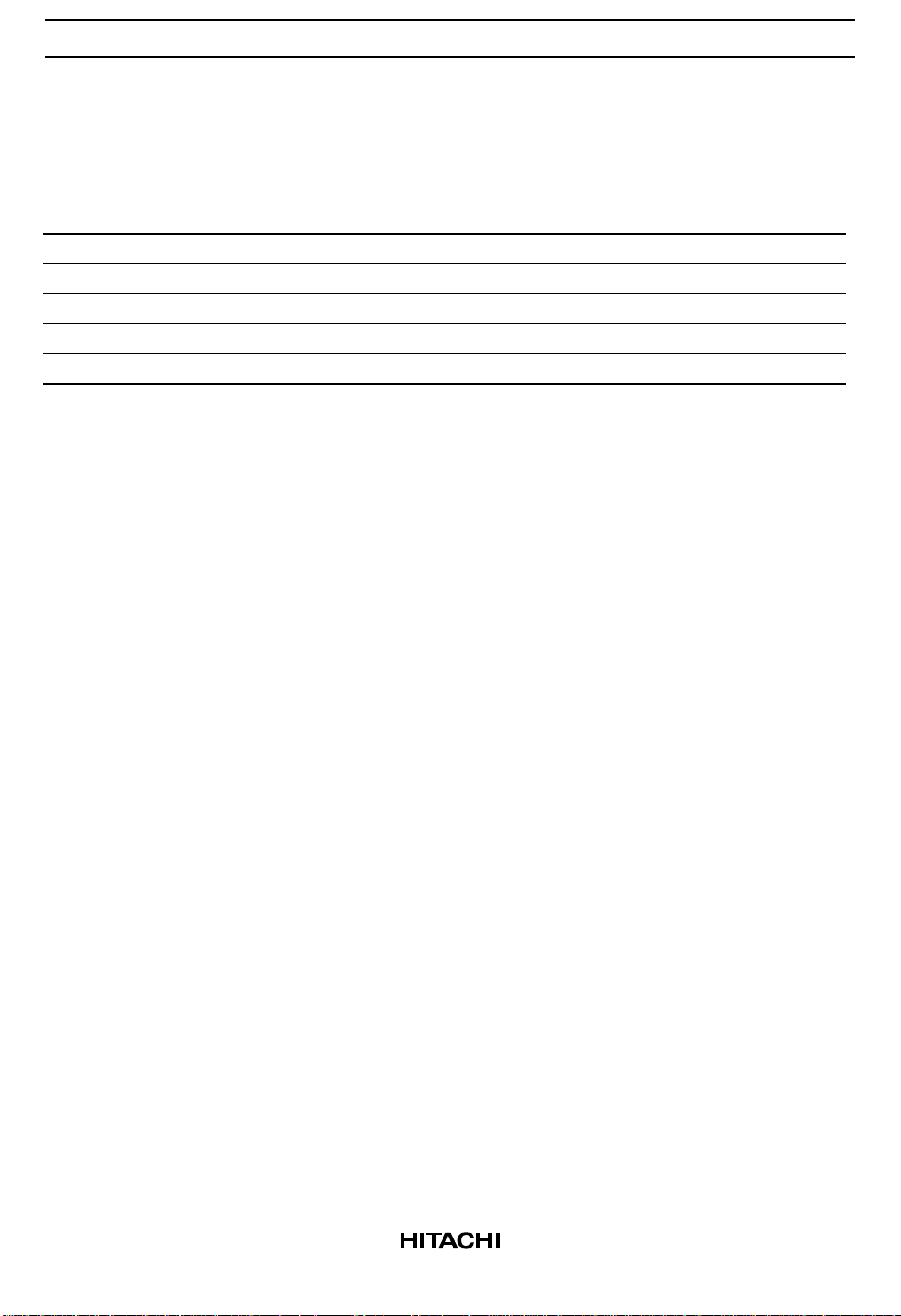

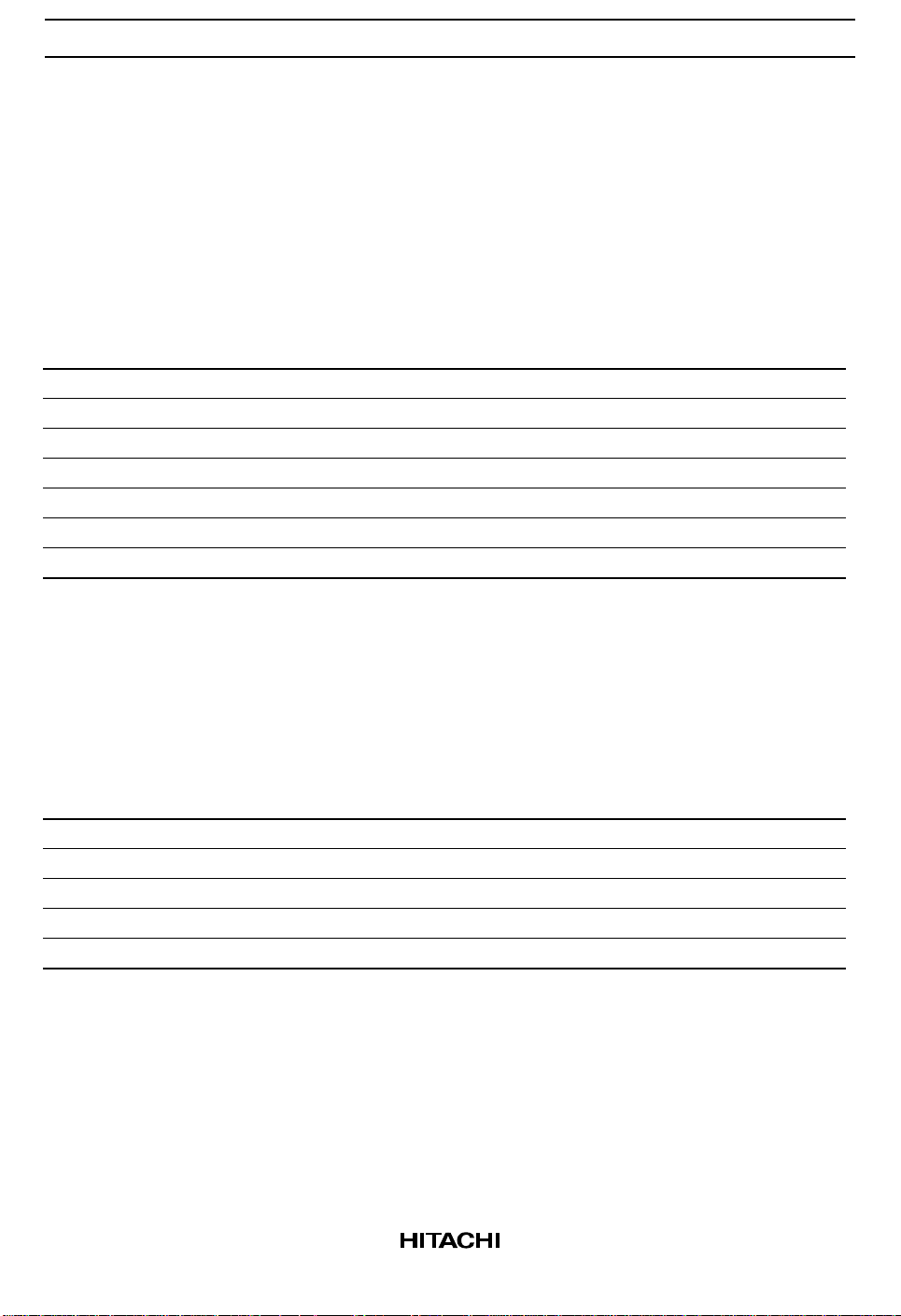

Block Diagram

HB288064MM1

V

PP

Generator

Flash control

1234

V

CC

CS CMD/DI DAT/DOCLK/SCLK

Internal clock

OCR[31:0]

CID[127:0]

set

CSD[127:0]

Register

RCA[15:0]

Interface driver

Interface

Core control

Memory core

567

DA T

CMD

Power on reset unit

All units in the HB288064MM1 are clocked by an internal clock generator. The Interface driver unit

synchronizes the DAT and CMD signals from external CLK to the internal used clock signal. The card is

controlled by the three line MultiMediaCard interface containing the signals: CMD, CLK, DAT (refer to

Chapter “Interfaces”). For the identification of the HB288064MM1 in a stack of MultiMediaCards a card

identification register (CID) and a relative card address register (RCA) is foreseen. An additional register

contains different types of operation parameters. This register is called card specific data register (CSD).

The communication using the MultiMediaCard lines to access either the memory field or the registers is

defined by the MultiMediaCard standard (refer to Chapter “Communication”). The card has its own power

on detection unit. No additional master reset signal is required to setup the card after power on. It is

protected against short circuit during insertion and removal while the MultiMediaCard system is powered

up (refer to Chapter “Power Supply”). No external programming voltage supply is required. The

programming voltage is generated on card. HB288064MM1 supports a second interface operation mode

the SPI interface mode. The SPI mode is activated if the CS signal is asserted (negative) during the

reception of the reset command (CMD0) (refer to Chapter “SPI Communication”).

3

HB288064MM1

Interface

The HB288064MM1 interface can operate in two different modes:

• MultiMediaCard mode

• SPI mode

Both modes are using the same pins. The default mode is the MultiMediaCard mode. The SPI mode is

selected by activating (= 0) the CS signal (Pin1) and sending the CMD0.

MultiMediaCard Mode

In the HB288064MM1, all data is transferred over a minimal number of lines:

• CLK: with each cycle of this signal an one bit transfer on the command and data lines is done. The

frequency may vary between zero and the maximum clock frequency. The MultiMediaCard bus master

is free to generate these cycles without restrictions in the range of 0 to 20 MHz.

• CMD: is a bidirectional command channel used for card initialization and data transfer commands.

The CMD signal has two operation modes: open drain for initialization mode and push pull for fast

command transfer. Commands are sent from the MultiMediaCard bus master to the HB288064MM1

and responses vice versa.

• DAT: is a bidirectional data channel with a width of one line. The DAT signal of the HB288064MM1

operates in push pull mode.

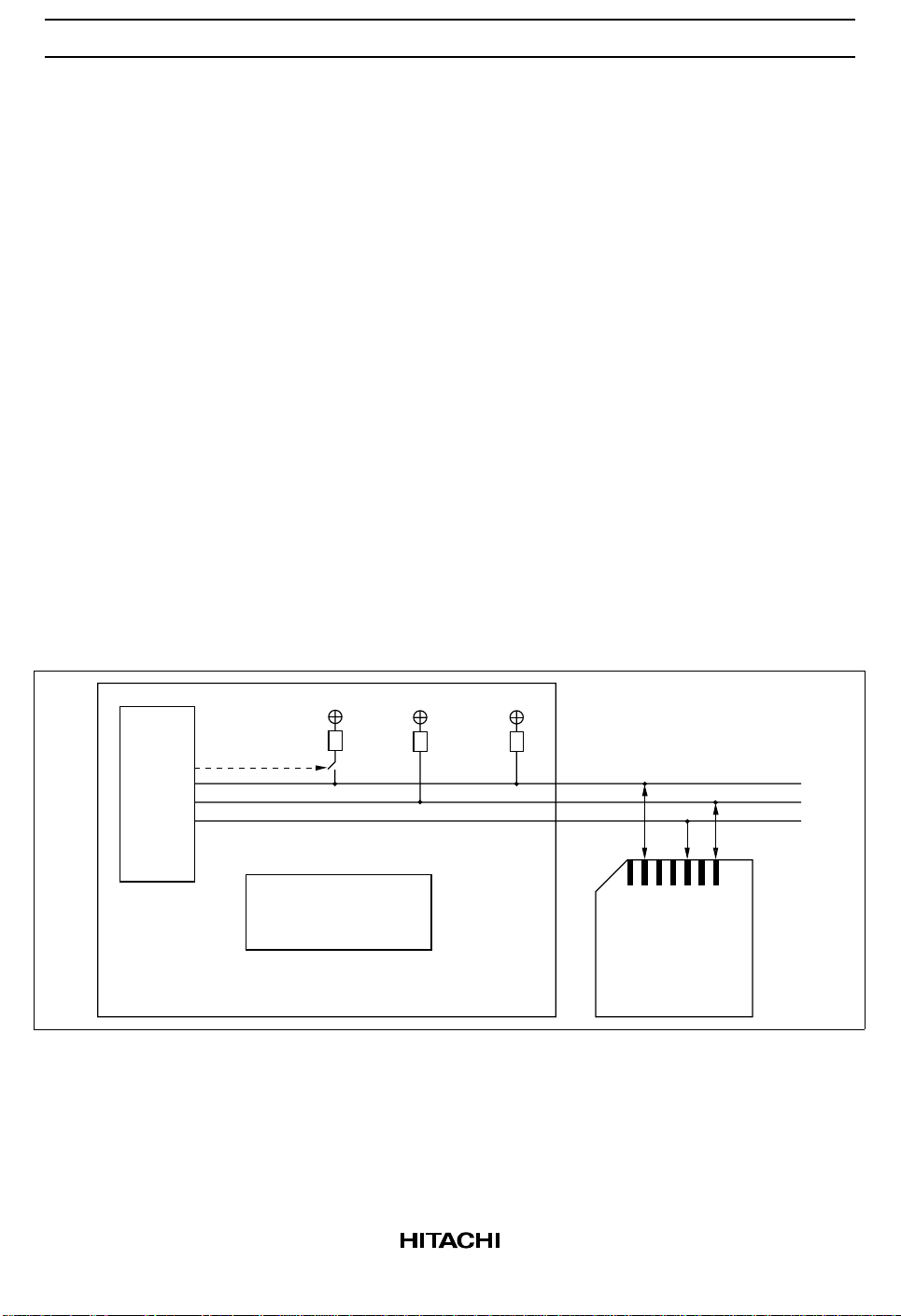

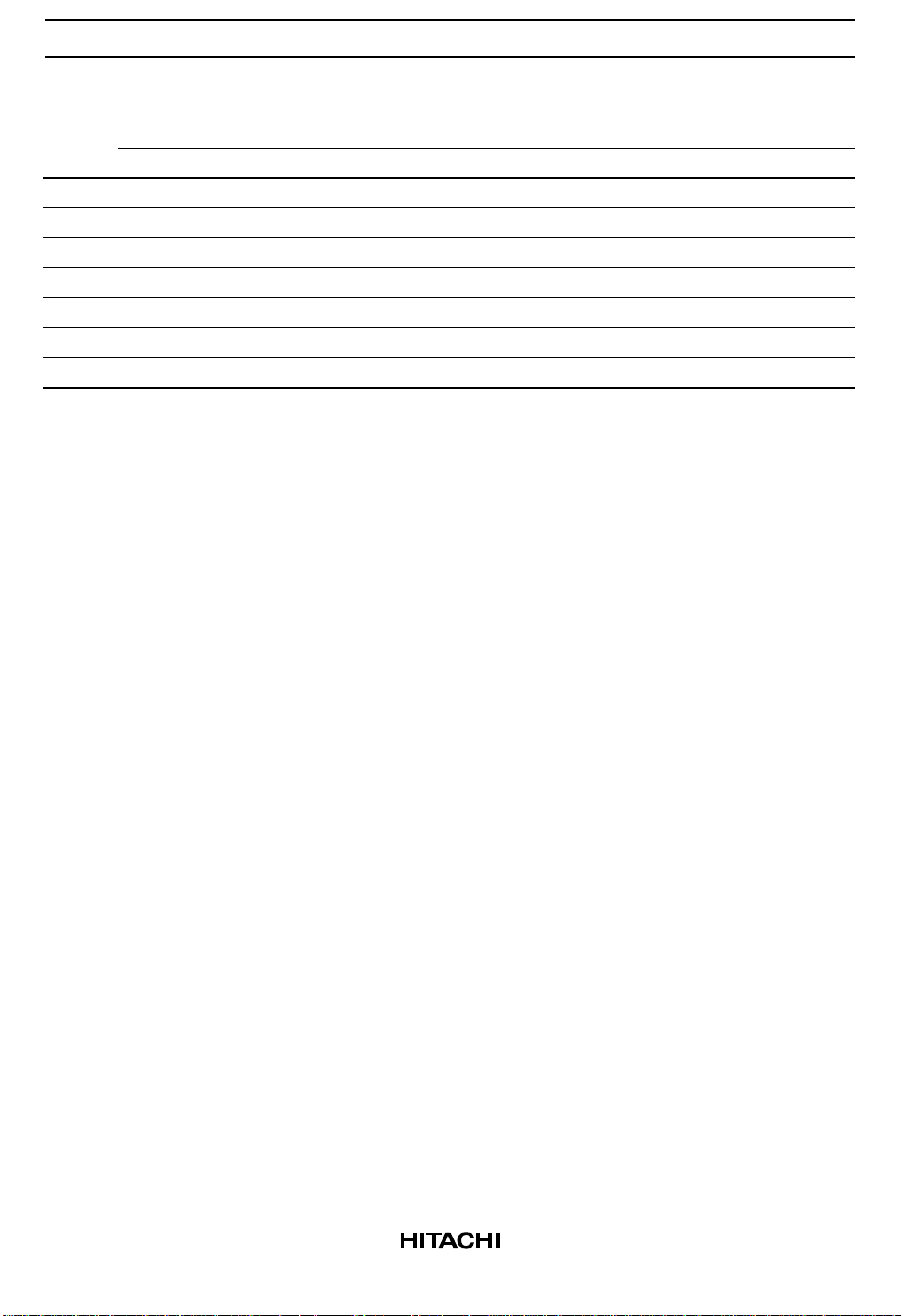

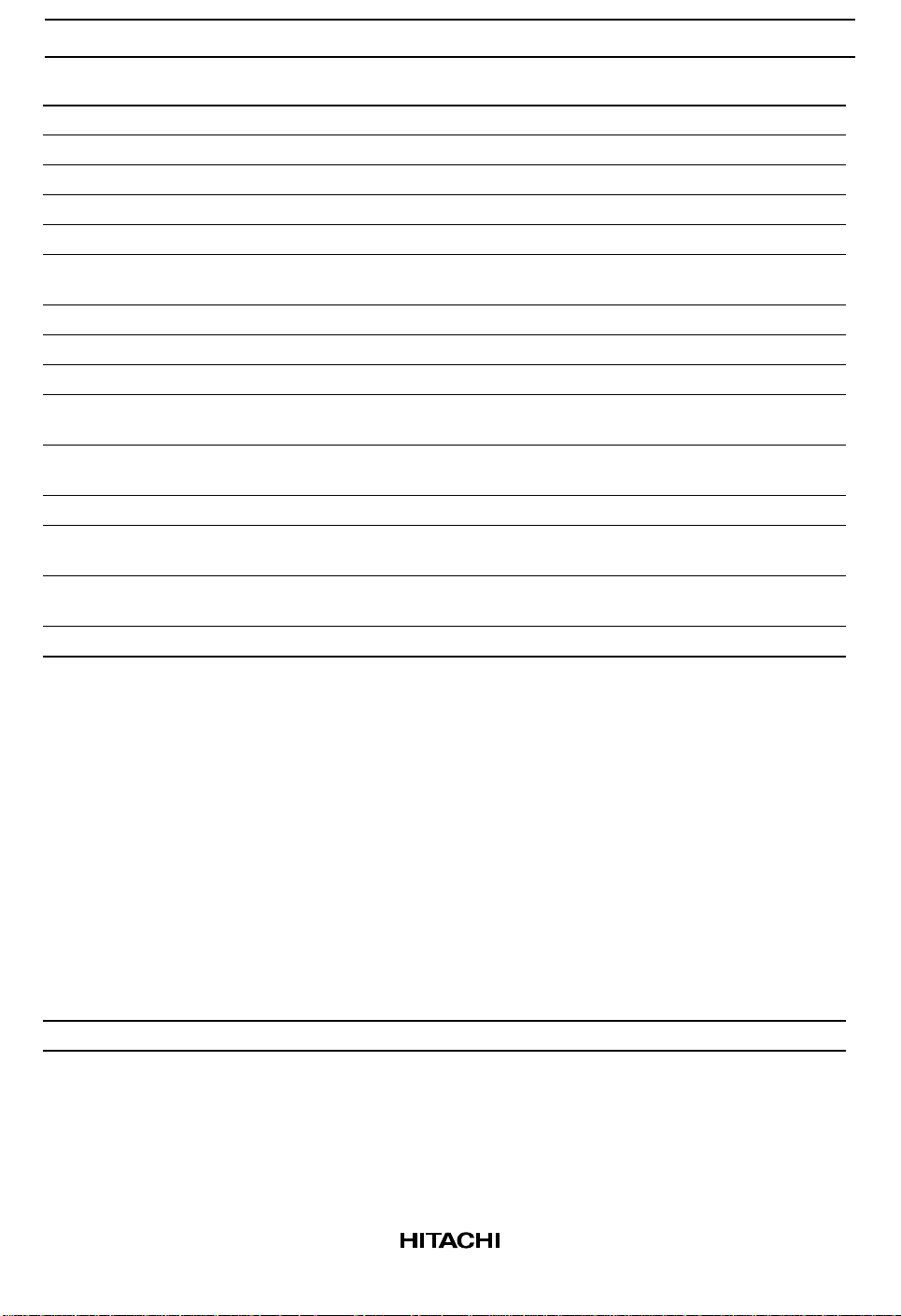

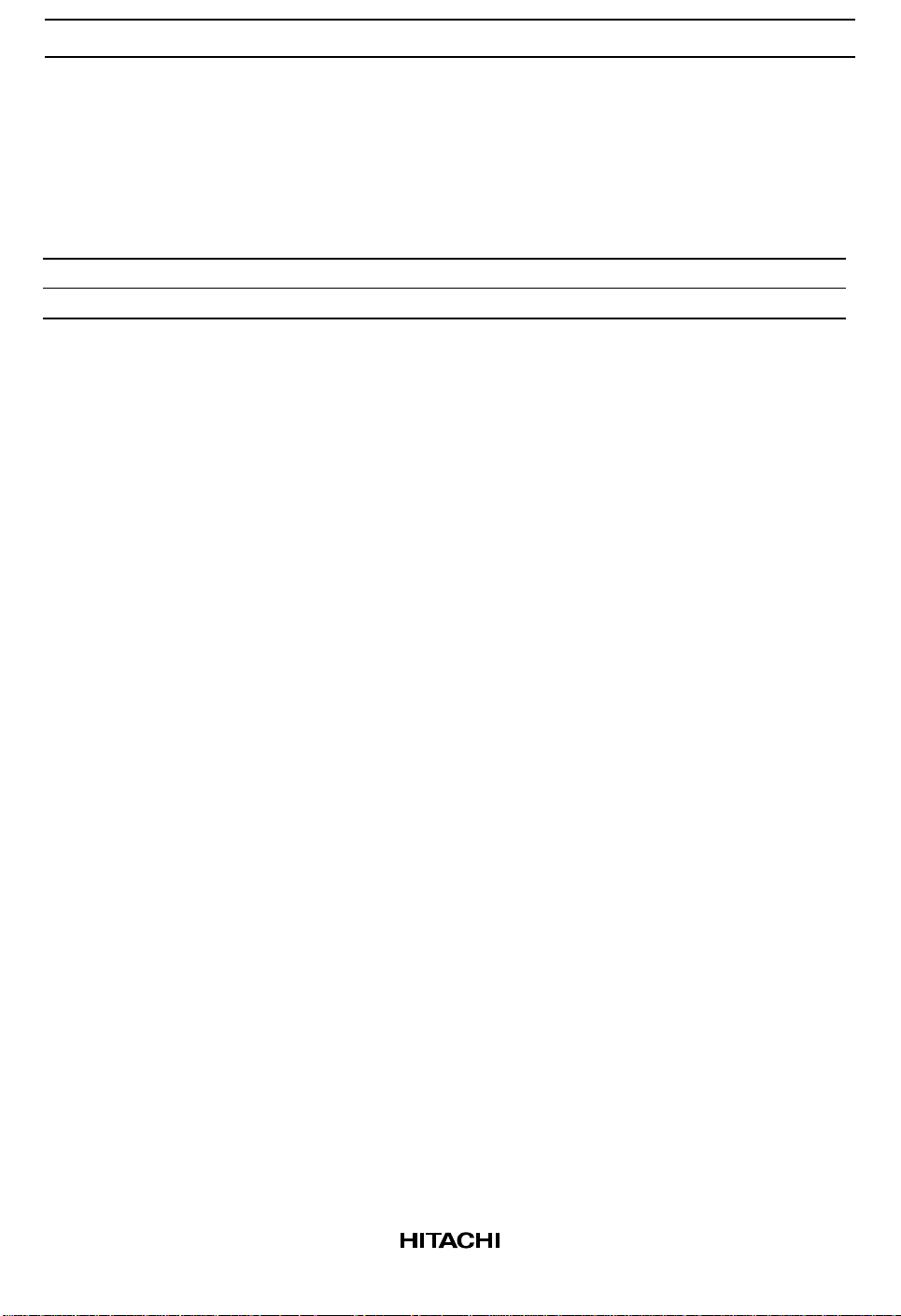

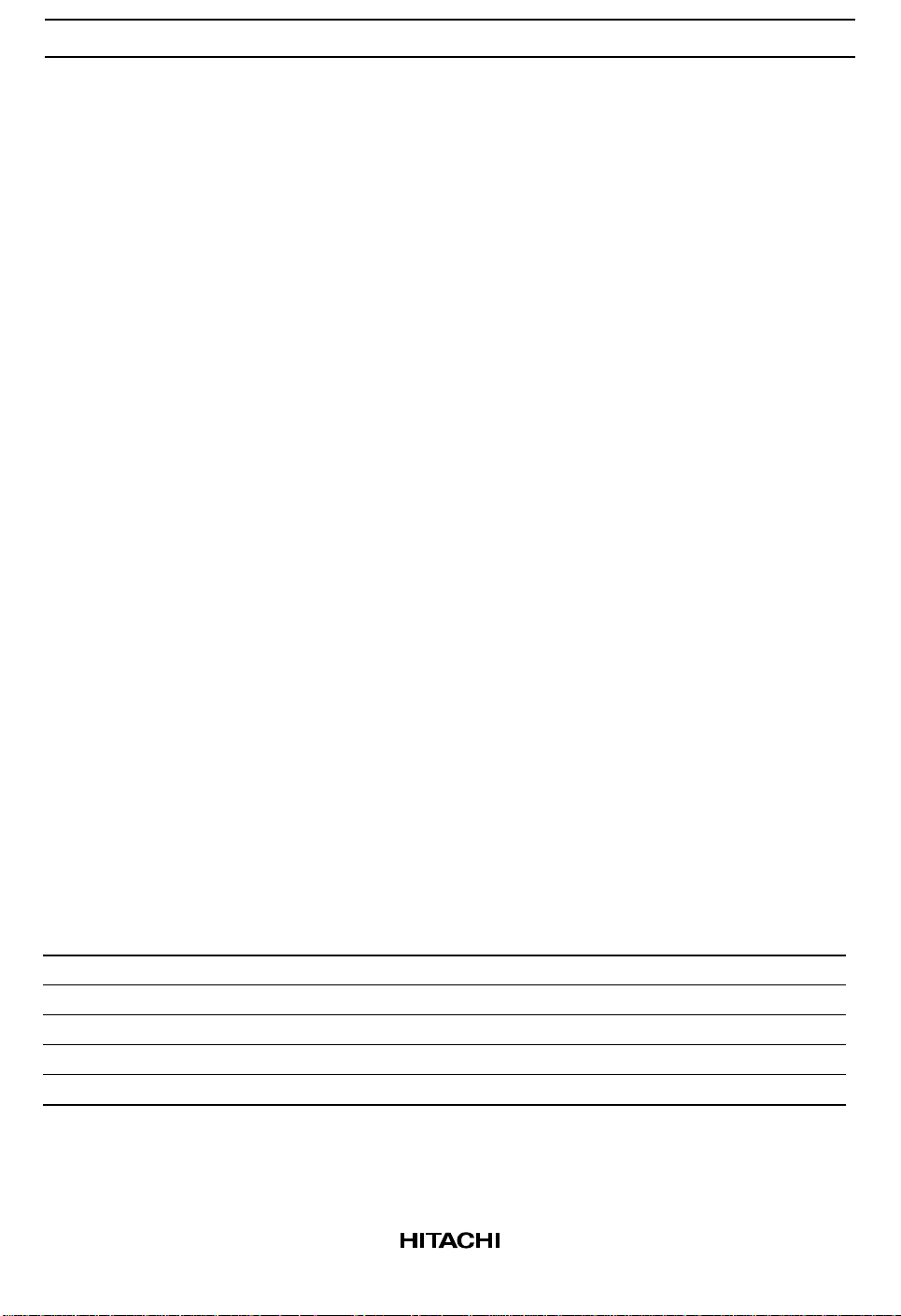

Interface driver

R

OD

MultiMediaCard Host

R

DA T

R

CMD

CMD

DA T

CLK

1 2 3 4 5 6 7

HB288064MM1

MultiMediaCard Mode Interface

All MultiMediaCards are connected directly to the lines of the MultiMediaCard bus. The following table

defines the card contacts.

4

MultiMediaCard Mode Pad Definition

HB288064MM1

Pin No. Name Type*

1

Description

1 RSV NC No connection

2 CMD I/O/PP/OD Command/Response

3V

SS1

S Ground

4VCCS Power supply

5 CLK I Clock

6V

SS2

S Ground

7 DAT I/O/PP Data

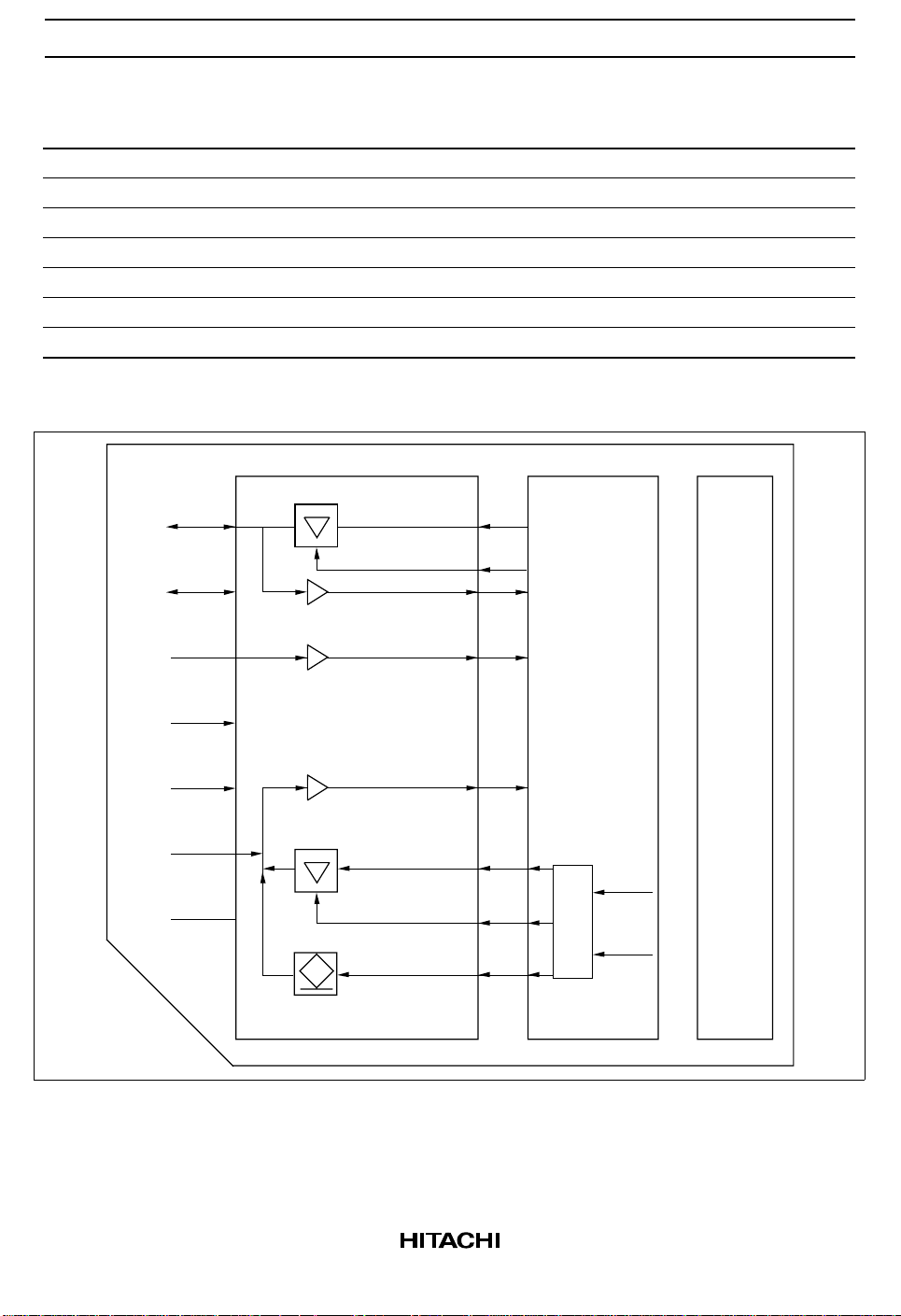

Note: 1. S: power supply; I: input; O: output; PP: push-pull; OD: open-drain; NC: No connection or V

DAT

enable

V

SS2

CLK

IH

V

CC

V

SS1

CMD

1 2 3 4 5 6 7

enable

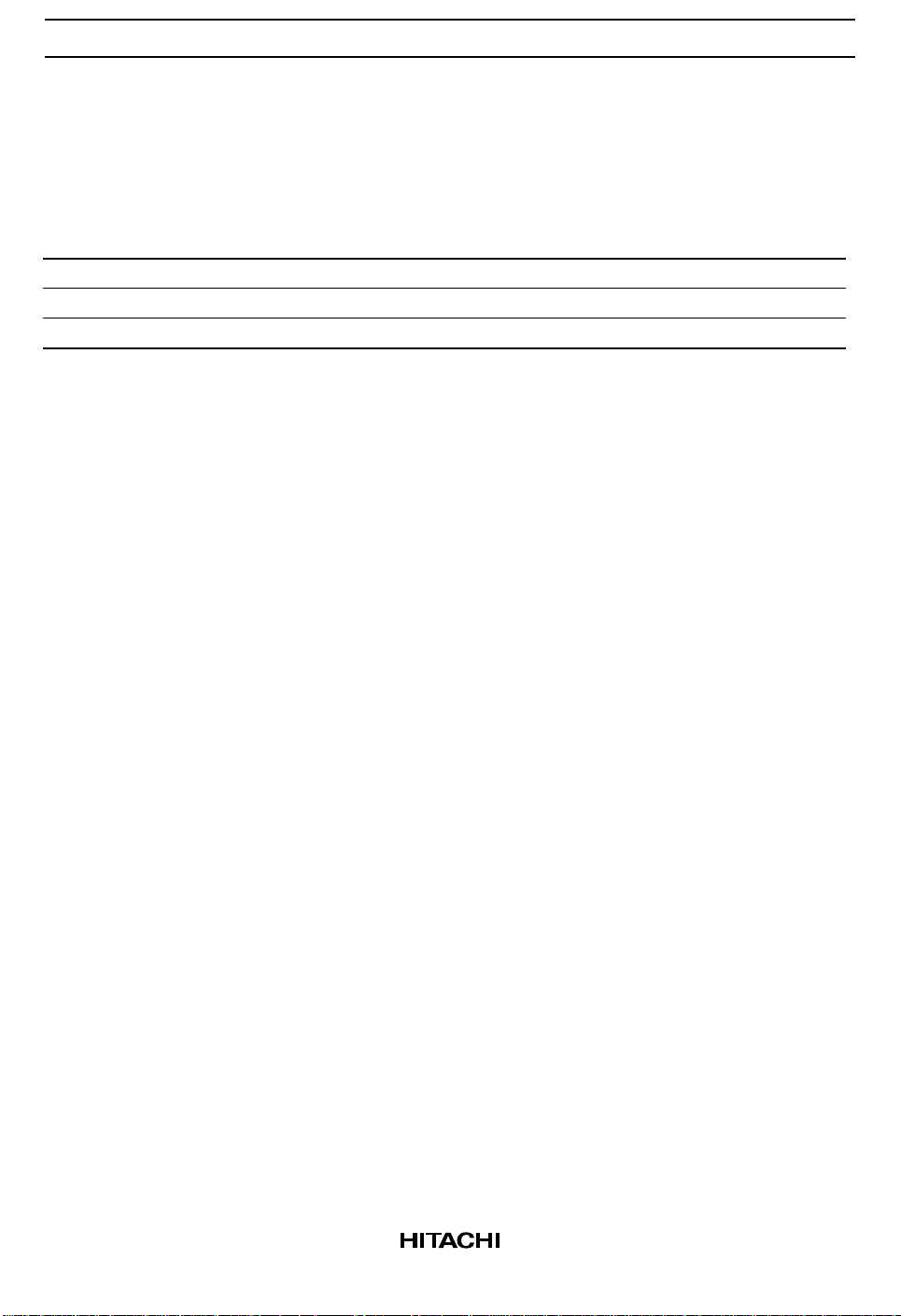

Interface driver

MultiMediaCard Mode I/O-drivers

MultiMediaCard interface controller

Memory core interface

OD/PP

5

HB288064MM1

SPI Mode

The Serial Peripheral Interface (SPI) is a general-purpose synchronous serial interface originally found on

certain Motorola microcontrollers. The MultiMediaCard SPI interface is compatible with SPI hosts

available on the market. As any other SPI device the MultiMediaCard SPI interface consists of the

following four signals:

CS: Host to card Chip Select signal.

CLK: Host to card clock signal

Data in: Host to card data signal.

Data out: Card to host data signal.

The MultiMediaCard card identification and addressing methods are replaced by a hardware Chip Select

(CS) signal. There are no broadcast commands. For every command, a card (slave) is selected by asserting

(active low) the CS signal (refer to Figure “SPI Bus System”). The CS signal must be continuously active

for the duration of the SPI transaction (command, response and data). The only exception occurs during

card programming, when the host can de-assert the CS signal without affecting the programming process.

The bidirectional CMD and DAT lines are replaced by unidirectional data in and data out signals. This

eliminates the ability of executing commands while data is being read or written and, therefore, makes the

sequential and multi block read/write operations obsolete. Only single block read/write commands are

supported by the SPI channel. The SPI interface uses the same seven signals of the standard

MultiMediaCard bus (refer to Table “SPI Interface Pin Configuration”).

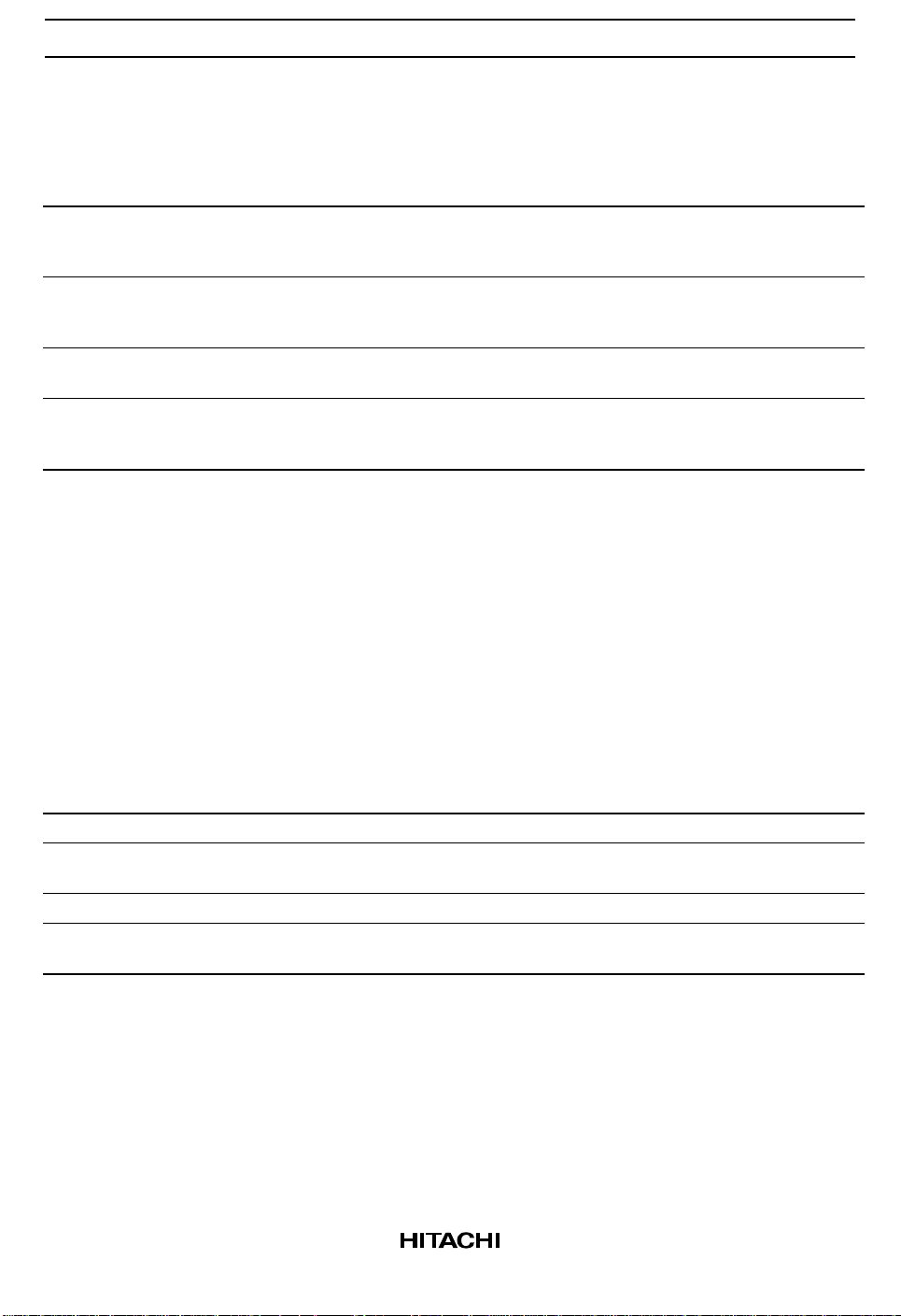

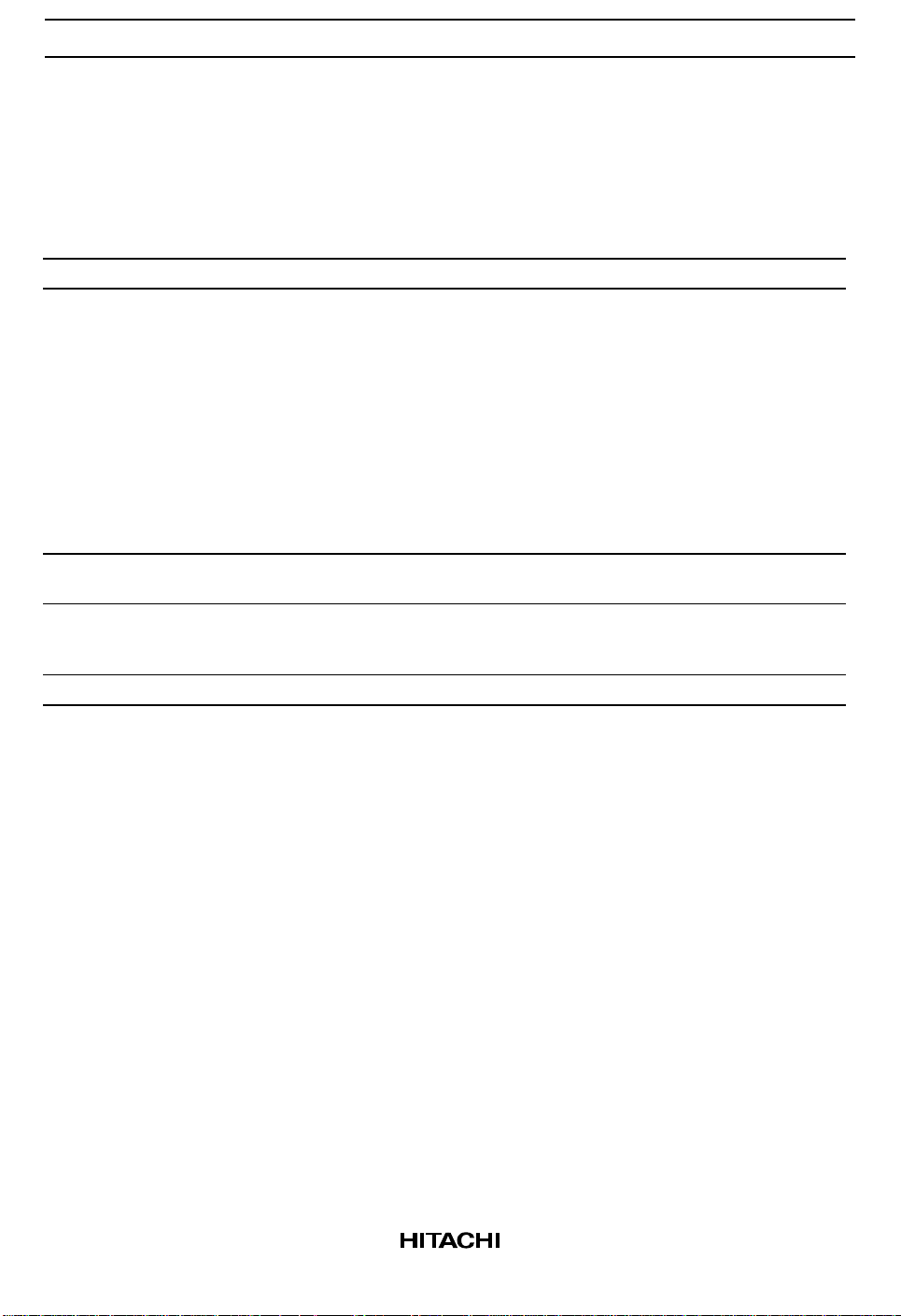

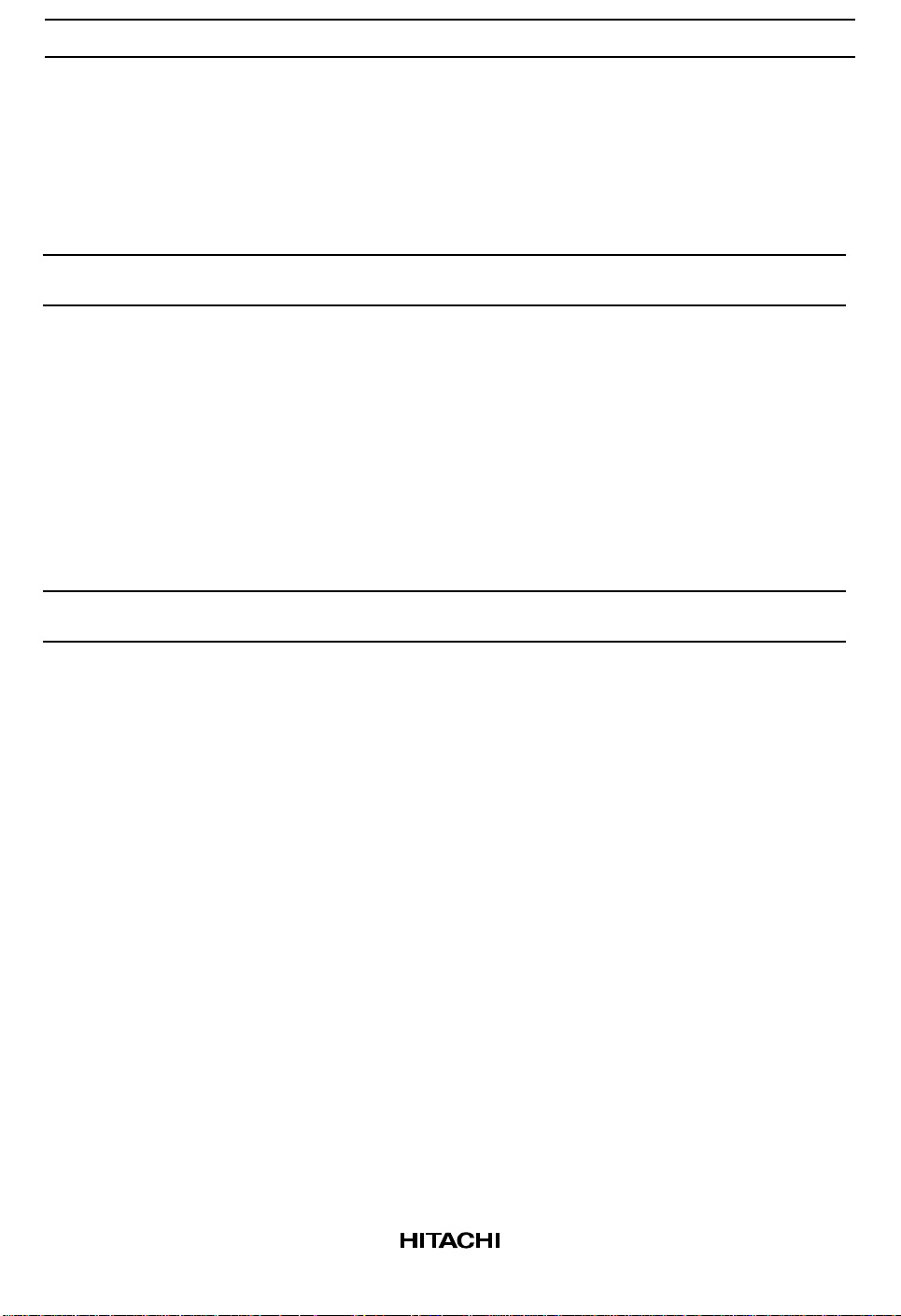

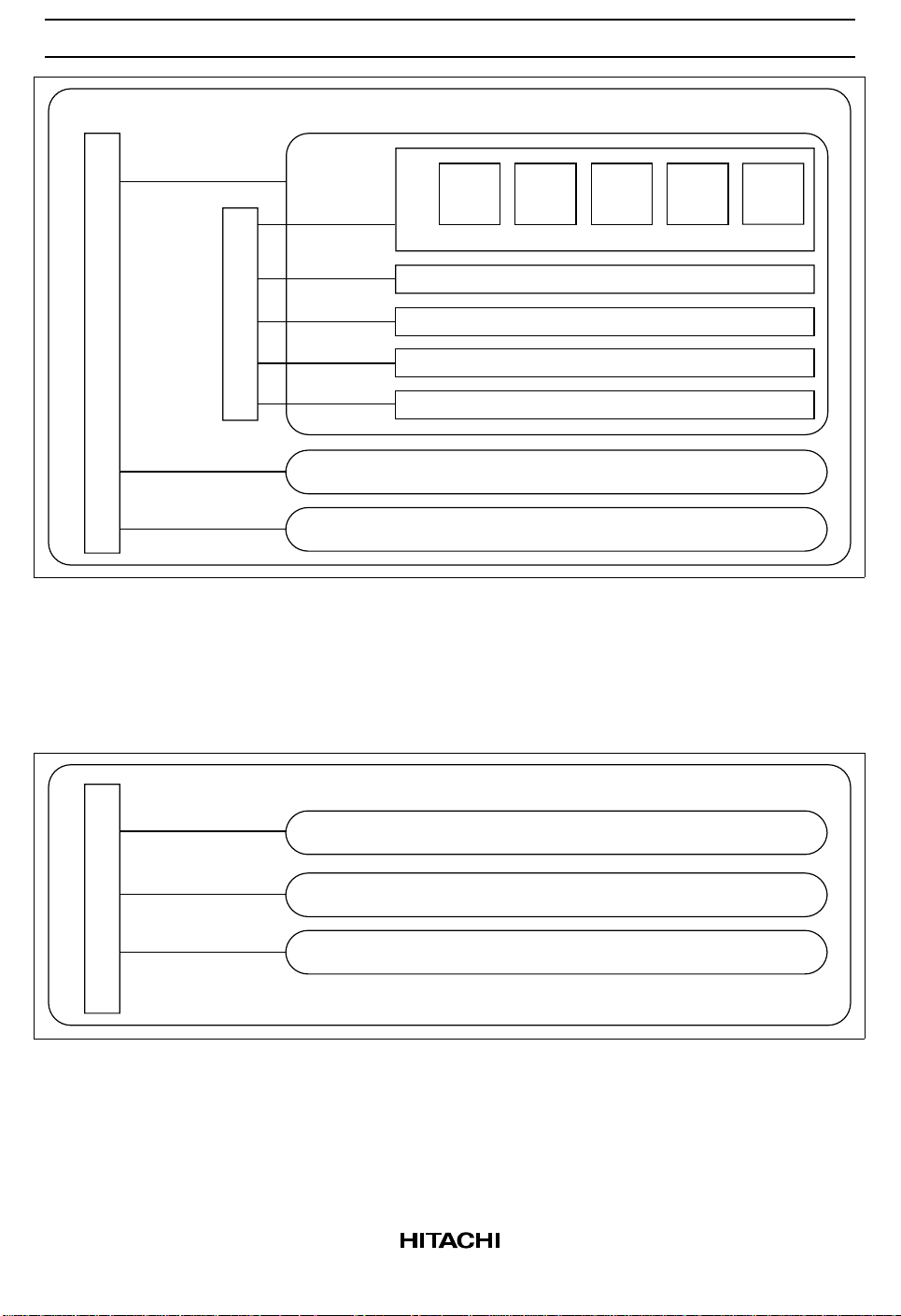

Power

supply

SPI bus (CLK, Datain, Dataout)

SPI Bus System

SPI bus master

SPI cardSPI card

CS

CS

6

HB288064MM1

SPI Interface Pin Configuration

MuitiMediaCard SPI

Pin No. Name Type*

1

1 RSV NC Reserved for future use CS I Chip select (neg true)

2 CMD I/O/PP/OD Command/Response DI I Data in

3V

SS1

S Ground V

4VCCS Power supply V

5 CLK I Clock SCLK I Clock

6V

SS2

S Ground V

7 DAT I/O/PP Data DO O/PP Data out

Note: 1. S: power supply; I: input; O: output; PP: push-pull; OD: open-drain; NC: No connection or V

Description Name Type Description

SS

CC

SS2

S Ground

S Power supply

S Ground

IH

7

HB288064MM1

Registers

The HB288064MM1 contains the following information registers:

Name Width Type Description

OCR 32 Programmed by the

manufacturer.

Read only for user

CID 128 Programmed by the

manufacturer.

Read only for user

RCA 16 Programmed during

initialization, not readable

CSD 128 Programmed by the

manufacturer. Partially

programmable by the user.

CID and RCA are used for identifying and addressing the HB288064MM1. The third register contains the

card specific data record. This record is a set of information fields to define the operation conditions of the

HB288064MM1.

Supported voltage range, card power up status bit

Card identification number, card individual number for

identification.

Relative card address, local system address of a card,

dynamically assigned by the host during initialization.

Card specific data, information about the card operation

conditions.

For the user the CID and the CSD are read only registers. They are read out by special commands (refer to

Chapter “Commands”). The RCA registers are write only registers. Unlike CID and CSD, RCA looses its

contents after powering down the card. Its value is reassigned in each initialization cycle. The

MultiMediaCard registers usage in SPI mode is summarized in Table “MultiMediaCard Registers in SPI

Mode”:

MultiMediaCard Registers in SPI Mode

Name Available in SPI mode Width (Bytes) Description

OCR Yes 32 Operation condition register.

CID Yes 16 Card identification data (serial number, manufacturer ID

etc.)

RCA No

CSD Yes 16 Card specific data, information about the card operation

conditions.

8

HB288064MM1

Card Identification (CID)

This register contains the card identification information used during the card identification procedure. It is

a 128 bit wide register, one-time programmable by the provider. The CID is divided into eight slices:

CID Fields

Name Field Width CID-slice

Manufacturer ID MID 8 [127:120]

OEM/Application ID OID 16 [119:104]

Product name PNM 48 [103:56]

Product revision PRV 8 [55:48]

Product serial number PSN 32 [47:16]

Manufacturing date MDT 8 [15:8]

CRC checksum CRC 7 [7:1]

not used, always 1 — 1 [0:0]

The CID has to be error free. To ensure the correctness of the CID a CRC checksum is added to the end of

the CID. The CRC checksum is computed by the following formula:

CRC Calculation: G(x) = x7 + x3 + 1

M(x) = CID[127]∗x

CRC[6...0] = Remainder [(M(x)∗x7)/G(x)]

119

+...+ CID[8]∗x

0

Relative Card Address (RCA)

The 16-bit relative card address register carries the card address assigned by the host during the card

identification. This address is used for the addressed host to card communication after the card

identification procedure. The default value of the RCA register is 0x0001. The value 0x0000 is reserved to

set all cards in Standby State with the command SELECT_DESELECT_CARD (CMD7). The RCA is

programmed with the command SET_RELATIVE_ADDRESS (CMD3) during the initialization procedure.

The content of this register is lost after power down. The default value is assigned when an internal reset is

applied by the power up detection unit of the HB288064MM1.

9

HB288064MM1

Card Specific Data (CSD)

The card specific data register describes how to access the card content. The CSD defines card operating

parameters like maximum data access time, data transfer speed.

The CSD Fields

Name Field Width CSD-slice Value Type

CSD structure CSD_STRUCTURE 2 [127:126] 1 read only

Spec version SPEC_VERS 4 [125:122] 2 read only

Reserved — 2 [121:120] 0 read only

Data read access-time-1 TAAC 8 [119:112] 0x0E (1 ms) read only

Data read access-time-2 in

CLK cycles (NAC*100)

Max. data transfer rate TRAN_SPEED 8 [103:96] 0x2A (20 Mbit/s) read only

Card command classes CCC 12 [95:84] 0x0FF (class 0, 1,

Max. read data block length READ_BLK_LEN 4 [83:80] 0x9 (512 bytes) read only

Partial blocks for read

allowed

Write block misalignment WRITE_BLK_MISALIGN1 [78:78] ‘0’ (Disabled) read only

NSAC 8 [111:104] 0x01 (100 cycles) read only

read only

2, 3, 4, 5, 6, 7)

READ_BLK_PARTIAL 1 [79:79] ‘1’*1 (Enabled) read only

Read block misalignment READ_BLK_MISALIGN 1 [77:77] ‘0’ (Disabled) read only

DSR implemented DSR_IMP 1 [76:76] ‘0’ (Disabled) read only

Reserved — 2 [75:74] 0 read only

Device size C_SIZE 12 [73:62] 0x7A7

(64 MByte)*

2

read only

Max. read current at VDD min VDD_R_CURR_MIN 3 [61:59] 0x5 (35 mA) read only

Max. read current at VDD max VDD_R_CURR_MAX 3 [58:56] 0x5 (45 mA) read only

Max. write current at V

Max. write current at V

Device size multiplier C_SIZE_MULT 3 [49:47] 4 (64 MByte)*

min VDD_W_CURR_MIN 3 [55:53] 0x5 (35 mA) read only

DD

max VDD_W_CURR_MAX 3 [52:50] 0x5 (45 mA) read only

DD

3

read only

Erase sector size SECTOR_SIZE 5 [46:42] 0 (512 Bytes) read only

Erase group size ERASE_GRP_SIZE 5 [41:37] 0x0F (8 kByte) read only

10

HB288064MM1

Name Field Width CSD-slice Value Type

Write protect group size WP_GRP_SIZE 5 [36:32] 0x01 (16 kByte) read only

Write protect group enable WP_GRP_ENABLE 1 [31:31] ‘1’ read only

Manufacturer default ECC DEFAULT_ECC 2 [30:29] 0 read only

Write speed factor R2W_FACTOR 3 [28:26] 2 (4) read only

Max. write data block length WRITE_BLK_LEN 4 [25:22] 9 (512 Bytes) read only

Partial blocks for write

allowed

Reserved — 5 [20:16] 0 read only

File format group FILE_FORMAT_GRP 1 [15:15] × read/write

Copy flag (OTP) COPY 1 [14:14] ×*

Permanent write protection PERM_WRITE_PROTECT1 [13:13] × read/write

Temporary write protection TMP_WRITE_PROTECT1 [12:12] × read/write/

File format FILE_FORMAT 2 [11:10] × read/write

ECC code ECC 2 [9:8] × read/write/

CRC CRC 7 [7:1] × read/write/

Not used, always 1 — 0 [0:0] 1 read only

Notes: 1. Access time from block to block within sector is 1 µs. For blocks smaller than 256 Byte, it is 62

µs.

2. This field is depended on the model. Refer to also C_SIZE_MULT

3. This field is depended on the model. Refer to also C_SIZE

4. × means user programmable

WRITE_BLK_PARTIAL 1 [21:21] ‘0’ read only

4

read/write

erase

erase

erase

Some of the CSD fields are one-time or multiple programmable by the customer or provider. All other

field values are fixed. The following section describes the CSD fields and their values for the

HB288064MM1:

• CSD_STRUCTURE

CSD Register Structure

CSD_STRUCTURE CSD register structure

‘01’ CSD version No. 1.1

The CSD version of the HB288064MM1 is related to the “MultiMediaCard system specification, Version

2.11”. The parameter CSD_STRUCTURE has permanently the value 1.

11

HB288064MM1

• SPEC_VERS

Defines the Spec version supported by the card. It includes the commands set definition and the definition

of the card responses. The card identification procedure is compatible for all spec versions!

SPEC Version

SPEC_VERS System specification version number

‘0010’ System specification version 2.11

The Spec version of the HB288064MM1 is related to the “MultiMediaCard system specification, Version

2.11”. The parameter SPEC_VERS has permanently the value 2.

• TAAC

Defines the asynchronous data access time:

TAAC Access Time Definition

TAAC bit Description Values

2:0 time exponent 0 = 1 ns, 1 = 10 ns, 2 = 100 ns, 3 = 1 µs, 4 = 10 µs,

5 = 100 µs, 6 = 1 ms, 7 = 10 ms

6:3 time mantissa 0 = reserved, 1 = 1.0, 2 = 1.2, 3 = 1.3, 4 = 1.5,

5 = 2.0, 6 = 2.5, 7 = 3.0, 8 = 3.5, 9 = 4.0, A = 4.5,

B = 5.0, C = 5.5, D = 6.0, E = 7.0, F = 8.0

7 reserved always ‘0’

The value for the asynchronous delay for the HB288064MM1 is 1 ms. The coded TAAC value is 0x0E (=

1 ms). For more details refer to Chapter “Operating Characteristics”.

• NSAC

Defines the worst case for the synchronous data access time. NAC is defined as 100*NSAC clock cycles,

where NSAC presents a binary value. Max. value for the data access time NAC is 25.6k clock cycles. The

total access time is the sum of both TAAC and NAC*clock period. The value of NSAC for the

HB288064MM1 is 0x01 (100 cycles). For more details refer to Chapter “Operating Characteristics”.

12

HB288064MM1

• TRAN_SPEED

The following table defines the maximum data transfer rate TRAN_SPEED:

Maximum Data Transfer Rate Definition

TRAN_SPEED bit Description

2:0 transfer rate exponent 0 = 100 kbit/s, 1 = 1 Mbit/s, 2 = 10 Mbit/s, 3 = 100

Mbit/s, 4...7 = reserved

6:3 time mantissa 0x0 = reserved, 0x1 = 1.0, 0x2 = 1.2, 0x3 = 1.3, 0x4 = 1.5,

0x5 = 2.0, 0x6 = 2.5, 0x7 = 3.0, 0x8 = 3.5, 0x9 = 4.0, 0xA = 4.5, 0xB = 5.0,

0xC = 5.5, 0xD = 6.0, 0xE = 7.0, 0xF = 8.0

7 reserved = ’0’

The HB288064MM1 supports a transfer rate between 0 and 20 Mbit/s. The parameter TRAN_SPEED is

0x2A.

• CCC

The MultiMediaCard command set is divided into subsets (command classes). The card command class

register CCC defines which command classes are supported by this card. A set CCC bit means that the

corresponding command class is supported. For command class definition refer to Table “HB288064MM1

Command Classes”.

Supported Card Command Classes

CCC bit Supported card command classes

0 class0

1 class1

...... ......

11 class11

The HB288064MM1 supports the command classes 0, 1, 2, 3, 4, 5, 6 and 7. The parameter CCC is

permanently assigned to the value 0x0FF.

13

HB288064MM1

• READ_BLK_LEN

The data block length is computed as 2

READ_BLK_LEN

.

Data Block Length

READ_BLK_LEN Block length Remark

0

02

12

...... ......

11 211 = 2048 bytes

12–15 reserved

= 1 byte

1

= 2 bytes

The block length might therefore be in the range 1, 2, 4...2048 bytes. This parameter defines the block

length if READ_BLK_PARTIAL is not set. If READ_BLK_PARTIAL is set this parameter contains the

maximum allowed value of the block length in bytes. All block lengths between one and this value are

permitted. The actual block size is programmed by the command SET_BLOCKLEN (CMD16). The

HB288064MM1 supports block lengths from 1 byte up to 2048 bytes. The parameter READ_BLK_LEN is

permanently assigned to the value 0x9.

• READ_BLK_PARTIAL

READ_BLK_PARTIAL defines whether partial block sizes can be used in block read and block write

commands. READ_BLK_PARTIAL = 0 means that only the block size defined by READ_BLK_LEN can

be used for block-oriented data transfers. READ_BLK_PARTIAL = 1 means that smaller blocks can be

used as well. The minimum block size will be equal to minimum addressable unit (one byte). The

HB288064MM1 supports partial block read. The parameter READ_BLK_PARTIAL is permanently

assigned to the value ‘1’.

• WRITE_BLK_MISALIGN

Defines if the data block to be written by one command can be spread over more than one physical blocks

of the memory device. The size of the memory block is defined in WRITE_BLK_LEN.

WRITE_BLK_MISALIGN is permanently assigned to the value ‘0’, signalling that crossing physical block

boundaries is not allowed.

• READ_BLK_MISALIGN

Defines if the data block to be read by one command can be spread over more than one physical block of

the memory device. The size of the data block is defined in READ_BLK_LEN. READ_BLK_MISALIGN

= 0 signals that crossing physical block boundaries is not allowed. READ_BLK_MISALIGN = 1 signals

that crossing physical block boundaries is allowed. The HB288064MM1 does not support read block

operations with boundary crossing. The parameter READ_BLK_MISALIGN is permanently assigned to

the value ‘0’.

14

HB288064MM1

• DSR_IMP

Defines if the configurable driver stage option is integrated on the card or not. If implemented a driver

stage register (DSR) must be implemented also.

DSR Implementation

DSR_IMP DSR type

0 no DSR implemented

1 DSR implemented

The HB288064MM1 output drivers are not configurable. The parameter DSR_IMP is permanently

assigned to the value ‘0’.

• C_SIZE

This parameter is used to compute the card capacity. The memory capacity of the card is computed from

the entries C_SIZE, C_SIZE_MULT and READ_BLK_LEN as follows:

memory capacity = BLOCKNR*BLOCK_LEN

Where

BLOCKNR = (C_SIZE+1)*MULT

MULT = 2

BLOCK_LEN = 2

C_SIZE_MULT+2

READ_BLK_LEN

(C_SIZE_MULT < 8)

, (READ_BLK_LEN < 12)

Therefore, the maximal capacity which can be coded is 4096*512*512 = 1 GBytes.

Example: A 64 MBytes card with BLOCK_LEN = 512 can be coded with C_SIZE_MULT = 4 and

C_SIZE = 1959.

The card capacity is 64 MBytes.

The value of the parameter C_SIZE used in the formula above for the HB288064MM1 is 0x7A7.

15

HB288064MM1

• VDD_R_CURR_MIN, VDD_W_CURR_MIN

The maximum supply current at the minimum supply voltage V

Maximum Supply Current Consumption at V

VDD_R_CURR_MIN

VDD_W_CURR_MIN Code for current consumption at 2.7 V

2:0 0 = 0.5 mA; 1 = 1 mA; 2 = 5 mA; 3 = 10 mA; 4 = 25 mA; 5 = 35 mA; 6

= 60 mA; 7 = 100 mA

= 2.7 V

CC

(2.7 V) is coded as follows:

CC

The parameter VDD_R_CURR_MIN and VDD_W_CURR_MIN are permanently assigned to the value 5

(35 mA).

• VDD_R_CURR_MAX, VDD_W_CURR_MAX

The maximum supply current at the maximum supply voltage VCC (3.6 V) is coded as follows:

Maximum Supply Current Consumption at V

VDD_R_CURR_MAX

VDD_W_CURR_MAX Code for current consumption at 3.6 V

2:0 0 = 1 mA; 1 = 5 mA; 2 = 10 mA; 3 = 25 mA; 4 = 35 mA; 5 = 45 mA; 6 =

80 mA; 7 = 200 mA

= 3.6 V

CC

The parameter VDD_R_CURR_MAX and VDD_W_CURR_MAX are permanently assigned to the value 5

(45 mA). For more details refer to Chapter “Characteristics”.

16

• C_SIZE_MULT

HB288064MM1

This parameter is used for coding a factor MULT for computing the total device size (refer to “C_SIZE”).

The factor MULT is defined as 2

C_SIZE_MULT+2

.

Multiply Factor for the Device Size

C_SIZE_MULT MULT Remark

2

02

12

22

32

42

52

62

72

= 4

3

= 8

4

= 16

5

= 32

6

= 64

7

= 128

8

= 256

9

= 512

The card capacity is 64 MBytes. The value of the parameter C_SIZE_MULT used in the formula to

calculate the card capacity (refer to parameter “C_SIZE”) for the HB288064MM1 is 4 (multiplier = 64).

• SECTOR_SIZE

The size of an erasable or write protection sector. The content of this register is a binary coded value

defining the number of write blocks (refer to “WRITE_BLK_LEN”) of a sector. The sector size of the

HB288064MM1 is set to 0 (= one write block = 512 bytes).

• ERASE_GROUP_SIZE

The size of an erasable group. The content of this register is a binary coded value defining the number of

sectors (refer to “SECTOR_SIZE”) of a group. This parameters value is 15 which means a group size of

(15+1)*512 bytes = 8 kByte.

• WP_GRP_SIZE

The size of a write protection group. The content of this register is a binary coded value defining the

number of sectors (refer to “SECTOR_SIZE”) of a group. This parameters value is 1 which means a group

size of (1+1)*(ERASE_GROUP_SIZE) = 16 kByte.

• WP_GRP_ENABLE

The value is set to ‘1’, meaning group write protection is enabled.

17

HB288064MM1

• DEFAULT_ECC

Set by the card manufacturer and defines the ECC code which is recommended to use (e.g. the device is

tested for). The value is set to ‘0’, indicating that no designated ECC is recommended.

• R2W_FACTOR

Defines the typical block program time as a multiple of the read access time. The following table defines

the field format.

R2W_FACTOR

R2W_FACTOR Multiples of read access time

01

1 2 (write half as fast as read)

24

38

416

532

6, 7 reserved

This parameter value is 2 for the HB288064MM1.

• WRITE_BLK_LEN

The data block length is computed as 2

WRITE_BLK_LEN

.

Data Block Length

WRITE_BLK_LEN Block length Remark

0

02

12

...... ......

11 211 = 2048 bytes

12–15 reserved

= 1 byte

1

= 2 bytes

The block length might therefore be in the range 1, 2, 4...2048 bytes. This parameter defines the block

length if WRITE_BLK_PARTIAL is not set. If WRITE_BLK_PARTIAL is set this parameter contains the

maximum allowed value of the block length in bytes. All block lengths between one and this value are

permitted. The actual block size is programmed by the command SET_BLOCKLEN (CMD16). The

HB288064MM1 supports blocks with the length 512 bytes. The parameter WRITE_BLK_LEN is

permanently assigned to the value 0x9.

18

HB288064MM1

• WRITE_BLK_PARTIAL

WRITE_BLK_PARTIAL defines whether partial block sizes can be used in block read and block write

commands. WRITE_BLK_PARTIAL = 0 means that only the block size defined by WRITE_BLK_LEN

can be used for block-oriented data transfers. WRITE_BLK_PARTIAL = 1 means that smaller blocks can

be used as well. The minimum block size will be equal to minimum addressable unit (one byte). The

HB288064MM1 supports no partial block write. The parameter WRITE_BLK_PARTIAL is permanently

assigned to the value ‘0’.

• FILE_FORMAT_GRP

Indicates the selected group of file formats. This field is read-only for ROM. The usage of this field is

shown in table “File_Formats”.

• COPY

Defines if the contents are an original (COPY = “0”) or a copy (= “1”). The COPY bit for OTP and MTP

devices, sold to end consumers, is set to “1” which identifies the card content as a copy. The COPY bit is a

one time programmable bit, being set by the customer

• PERM_WRITE_PROTECT

Permanently protects the whole card content against overwriting or erasing (all write and erase commands

for this card is permanently disabled). This parameter is one-time programmable by the customer. The

default value is ‘0’ (not protected).

• TMP_WRITE_PROTECT

Temporarily protects the whole card content from being overwritten or erased (all write and erase

commands for this card are temporarily disabled). This parameter is programmable by the customer. The

default value is ‘0’ (not protected).

• FILE_FORMAT

Indicates the file format on the card. This field is read-only for ROM. The following formats are defined:

File_Formats

FILE_FORMAT_GRP FILE_FORMAT Type

0 0 Hard disk-like file system with partition table

0 1 DOS FAT (floppy-like) with boot sector only (no partition table)

0 2 Universal File Format

0 3 Others/Unknown

1 0, 1, 2, 3 Reserved

19

HB288064MM1

• ECC

Defines the ECC code that was used for storing data on the card. This field is used by the host (or

application) to decode the user data. The following table defines the field format.

ECC Type

ECC ECC type Maximum number of correctable bits

0 none (default) none

1 BCH (542,512) 3

2–15 reserved —

The content provider or customer defines which kind of error correction may be used to protect the contents

of the HB288064MM1. This value is programmable.

• CRC

The CRC register contains the check sum for the CSD content. The check sum is computed by the

following formulas: Generator polynomial:

G(x) = x7 + x3 + 1

119

M(x) = CSD[127]∗x

+...+ CSD[8]∗x0 CRC[6...0] = Remainder [(M(x)∗x7)/G(x)]

The user has to recalculate a new CRC after defining a new CSD.

20

HB288064MM1

MultiMediaCard Communication

All communication between host and cards is controlled by the host (master). The host sends commands

and, depending on the command, receives a corresponding response from the selected card. In this chapter

the commands to control the HB288064MM1, the card responses and the contents of the status and error

field included in the responses, are defined.

Memory Array Partitioning

The basic unit of data transfer to/from the MultiMediaCard is one byte. All data transfer operations which

require a block size always define block lengths as integer multiples of bytes. Some special functions need

other partition granularity. For block-oriented commands, the following definition is used:

• Block: is the unit which is related to the block-oriented read and write commands. Its size is the

number of bytes which will be transferred when one block command is sent by the host. The size of a

block is either programmable or fixed. The information about allowed block sizes and the

programmability is stored in the CSD.

For devices which have erasable memory cells, special erase commands are defined. The granularity of the

erasable units is in general not the same as for the block-oriented commands:

• Sector: is the unit which is related to the erase commands. Its size is the number of blocks which will

be erased in one portion. The size of a sector is fixed for each device. The information about the sector

size (in blocks) is stored in the CSD.

• Group: is a number of sectors. Its size is the number of consecutive sectors which will be erased at

once. The size of a group is fixed for each device. The information about the size is stored in the CSD.

For devices which include a write protection:

• WP-Group: is the minimal unit which may have individual write protection. Its size is the number of

sectors which will be write protected by one bit. The size of a WP-group is fixed for each device. The

information about the size is stored in the CSD.

Each erasable unit (group and sector) has a special “tag” bit. This bit may be set or cleared by special

commands to tag the unit. All tagged units will be erased in parallel by one erase command following a

number of tag commands. All tag bits are cleared by each command except a tag or untag command.

Therefore, immediately after a sequence of tag commands an erase command has to be sent by the host.

Commands others than tagging or erasing abort a tag-erase cycle irregularly.

21

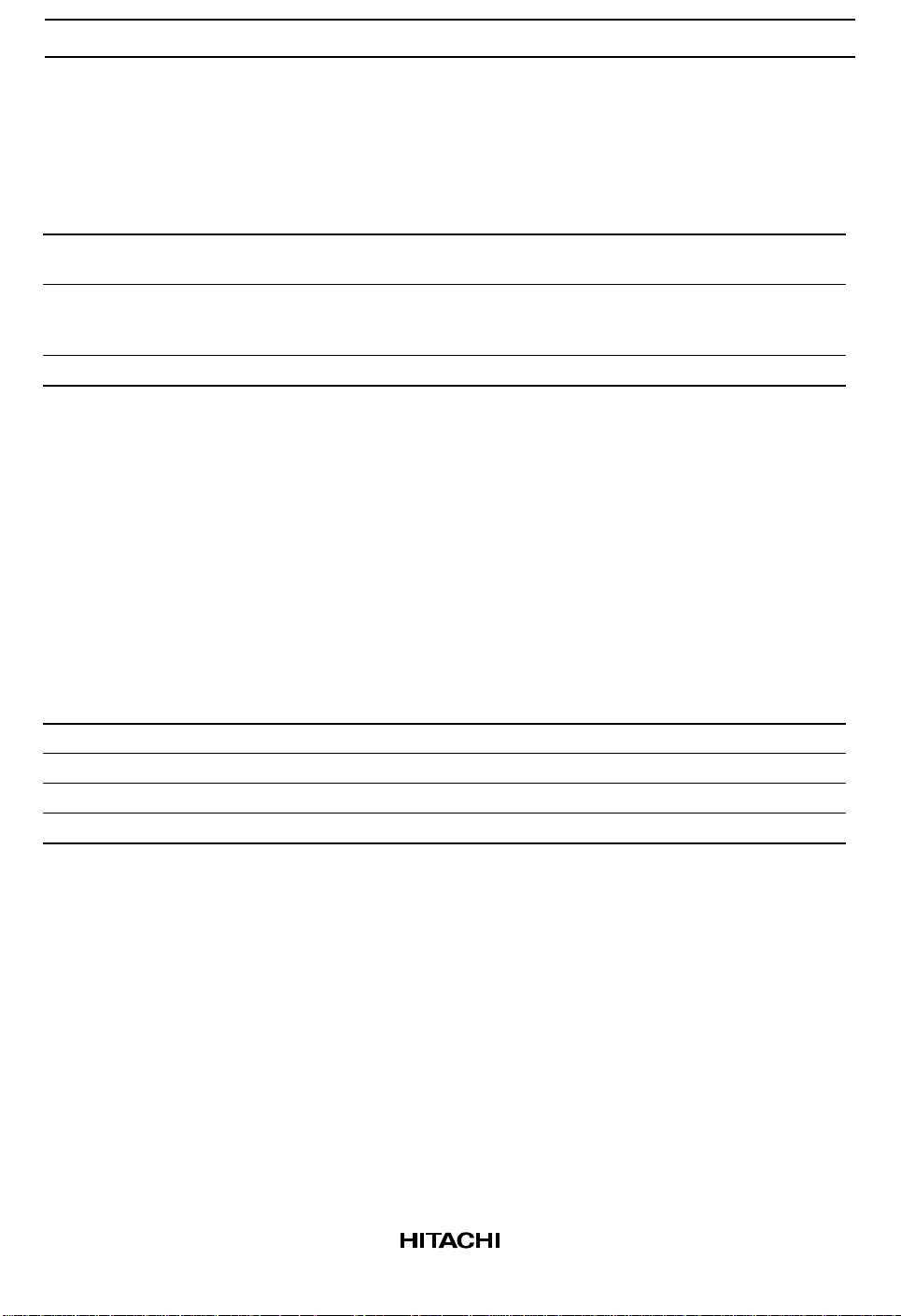

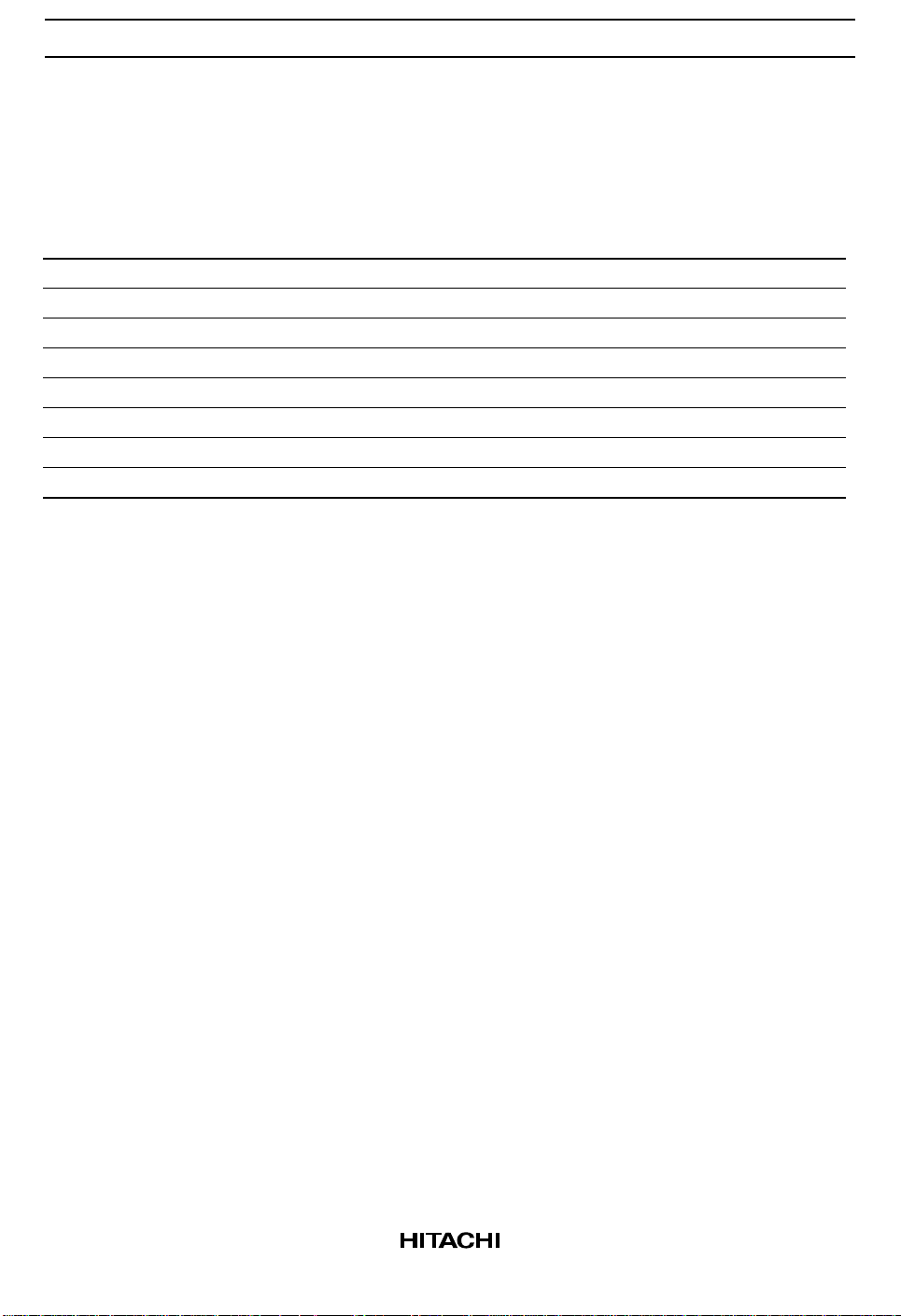

HB288064MM1

MultiMediaCard

GROUP 0

Block 0 Block 1 Block 2 Block 3 Block n

Sector 0.0

Sector 0.1

Sector 0.2

Sector tagging

Group tagging

GROUP 1

GROUP n

Sector 0.3

Sector 0.n

Erase Tagging Hierarchy

Each WP-group may have an additional write protection bit. The write protection bits are programmable

via special commands (refer to Chapter “Commands”). Both functions are optional and only useful for

writable/erasable devices. The write protection may also be useful for multi type MultiMediaCards (e.g. a

ROM - Flash combination). The information about the availability is stored in the CSD.

WP-GROUP 0

WP-GROUP 1

22

WP-GROUP n

Group write protection

Write Protection

HB288064MM1

Commands

The command set of the MultiMediaCard system is divided into classes corresponding to the type of card

(see also [1]). The HB288064MM1 supports the following command classes:

HB288064MM1 Command Classes (Class 0 to Class 2)

Supported commands

Card command

class (CCC) Class description

Class 0 basic ++++++++ +++

Class 1 stream read +

Class 2 block read + + +

HB288064MM1 Command Classes (Class 3 to Class 8)

Card command

class (CCC) Class description

Class 3 stream write +

Class 4 block write ++++

Class 5 erase +++++++

Class 6 write protection + + +

Class 7 lock card +

01234791011121315161718

Supported commands

20 24 25 26 27 28 29 30 32 33 34 35 36 37 38 42

Class 0 is mandatory and supported by all cards. It represents the card identification and initialization

commands, which are intended to handle different cards and card types on the same bus lines. The Card

Command Class (CCC) is coded in the card specific data register of each card, so that the host knows how

to access the card. There are four kinds of commands defined on the MultiMediaCard bus:

• broadcast commands (bc) sent on CMD line, no response

• broadcast commands with response (bcr) sent on CMD line, response (all cards simultaneously) on

CMD line

• addressed (point-to-point) commands (ac) sent on CMD line, response on CMD line

• addressed (point-to-point) data transfer commands (adtc) sent on CMD line, response on CMD line,

data transfer on DAT line

23

HB288064MM1

The command transmission always starts with the MSB. Each command starts with a start bit and ends with

a CRC command protection field followed by an end bit. The length of each command frame is fixed to 48

bits (2.4 µs at 20 MHz):

0

start bit1host

Note: 1. (Cyclic Redundancy Check)

bit5...bit0

command

bit31...bit0

argument

bit6...bit0

CRC*

1

1

end bit

The start bit is always ‘0’ in command frames (sent from host to MultiMediaCard). The host bit is always

‘1’ for commands. The command field contains the binary coded command number. The argument

depends on the command (refer to Table “Basic Commands (class 0) and Table “Block-Oriented Read

Commands (class 2)”). The CRC field is defined in Chapter “Cyclic Redundancy Check (CRC)”. The

HB288064MM1 supports the following MultiMediaCard commands:

24

Loading...

Loading...