Page 1

5

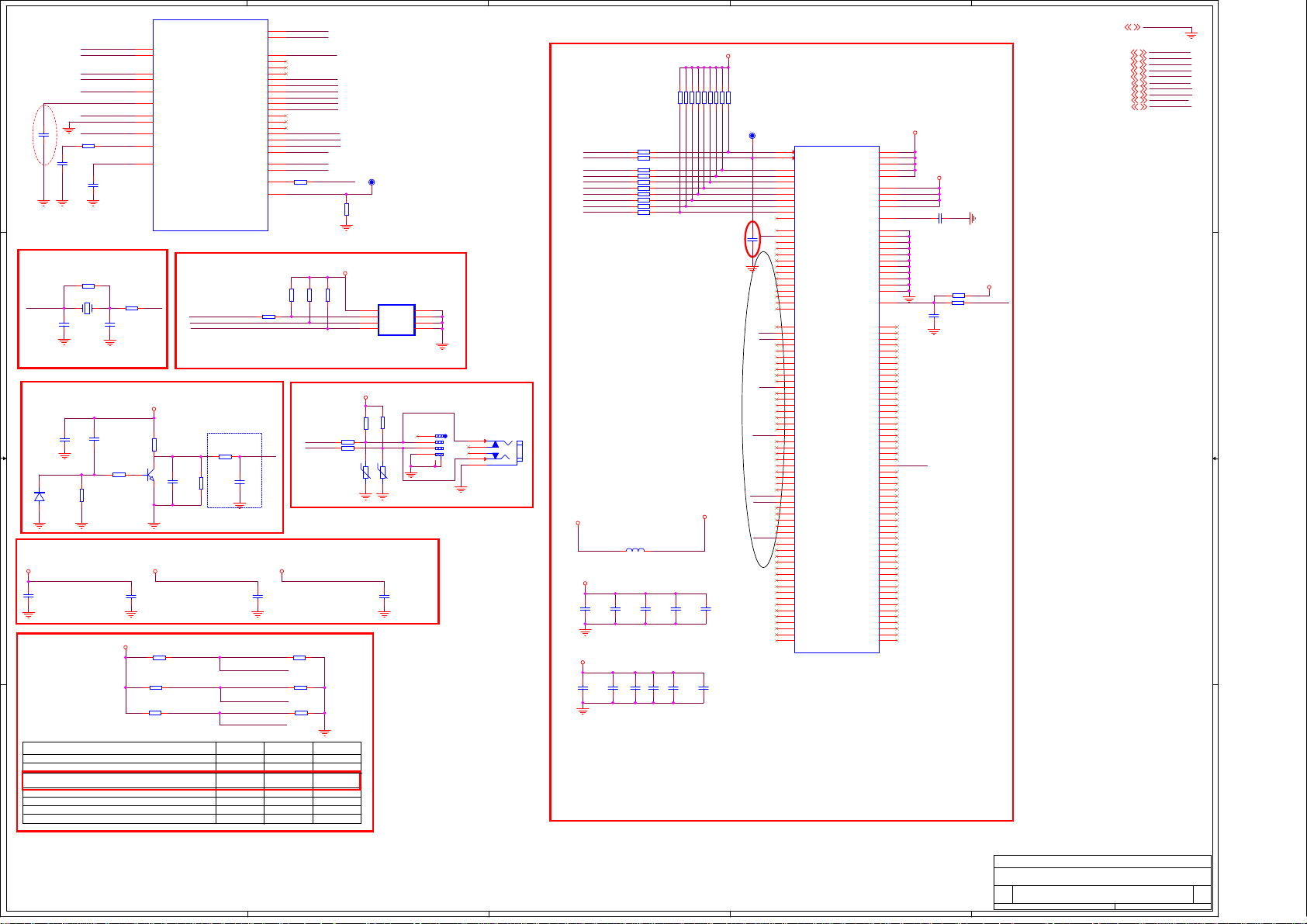

MB circuit:6484

4

3

2

1

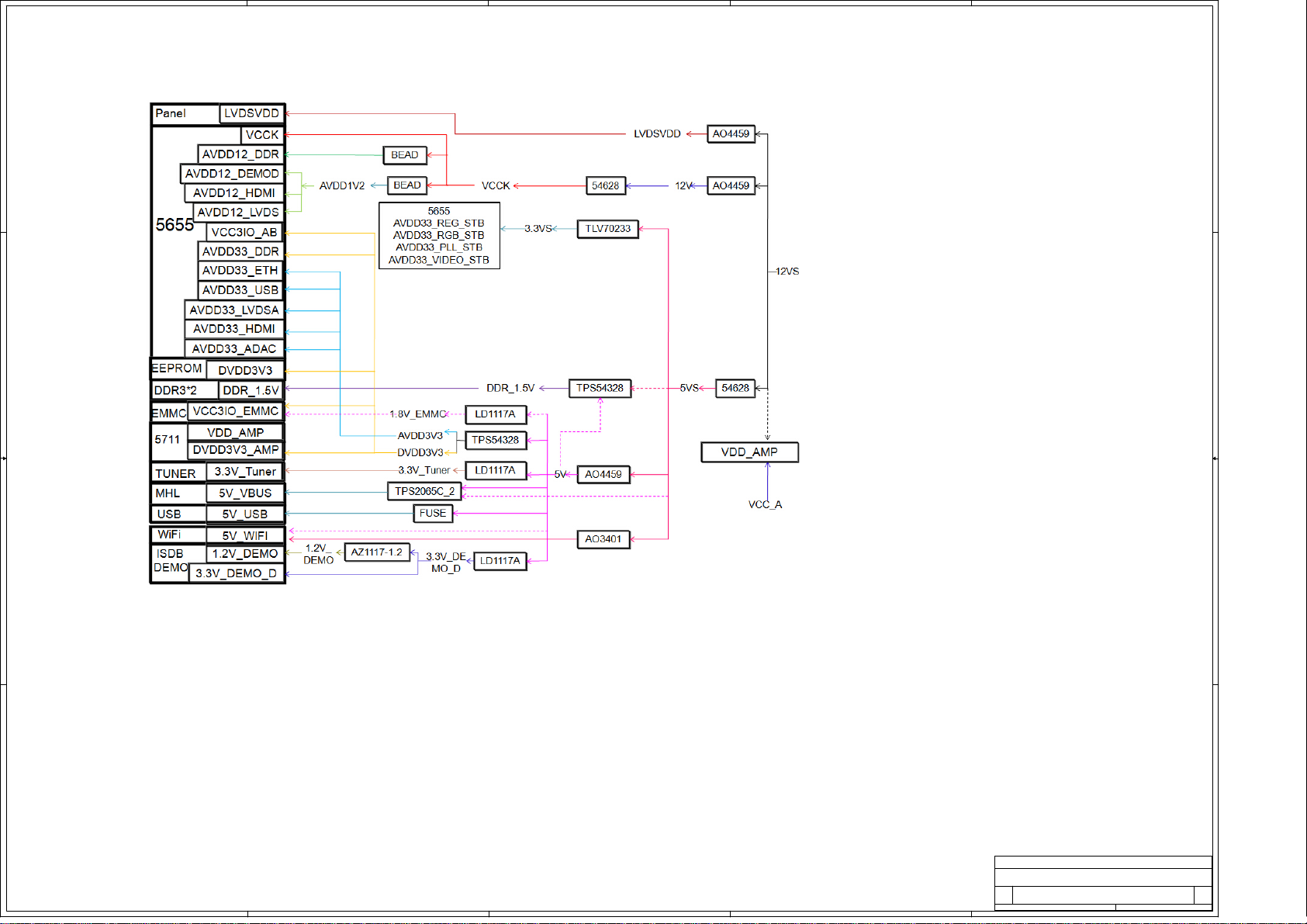

POWER TREE

D D

C C

B B

A A

Hisense Electric Co.,LTD

Title

Title

5

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

113Friday, April 10, 2015

113Friday, April 10, 2015

113Friday, April 10, 2015

1.0

of

of

of

Page 2

5

MB circuit:6484

4

3

2

1

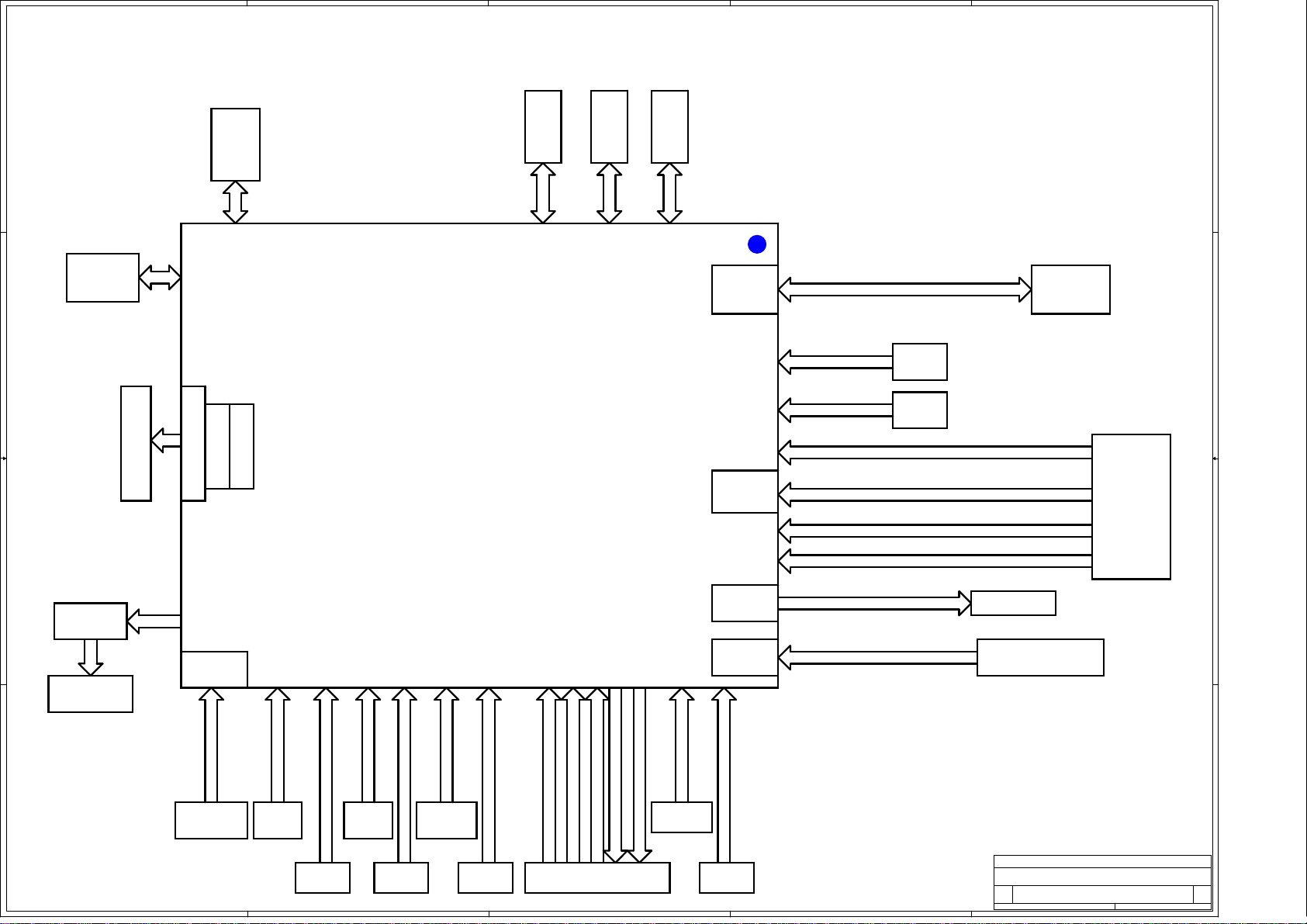

Block Diagram

NAND FLASH

UM3 or U1

EMMC

D D

UD1

DDR3

Flash

SPISerial

UM2.UM4

SDIOx1

UD2

DDR3

C C

JL1

LVDS Port

V By One

LVDS Port

mini_LVDS A Port

MT5655

UM1

CI

Embedded

DEMOD

USB_P0_P1_P2

HDMI_P0_P1

Serial TS

Tuner IF+/IF-

USBx3

HDMIx2

Tuner CVBS1

B B

Audio DAC

UA4

SPEAKER AMP

TPS5711

JA1.JA2

SPEAKER OUT

I2S

Embedded

RMII PHY

MII/RMII

USB_P3

CVBS2 IN

RGB IN

LINE OUT

LINE IN

SCART1 AV OUT

x 3

Audio ADC

x4

CVBS3

MPXP share with CVBS0

LINE IN

PA2,PA11,PV7

PV7,PA6,PA7,PA8

PC1

CAM Card

TUNER&

External

Demod

JT1,JT2

LINE IN

HDMI_P2

A A

UW2

Ethernet

5

PU4

USBx1

HDMI X1

PH3

IRM1

IR

4

J2

I2C1

J3

UART0

PV5

VGA

PV7

SCART2

3

PV3

YPbPr0

PV8

AV1

Hisense Electric Co.,LTD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

2

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

213Friday, April 10, 2015

213Friday, April 10, 2015

213Friday, April 10, 2015

1.0

of

of

of

Page 3

5

MB circuit:6484

4

3

2

1

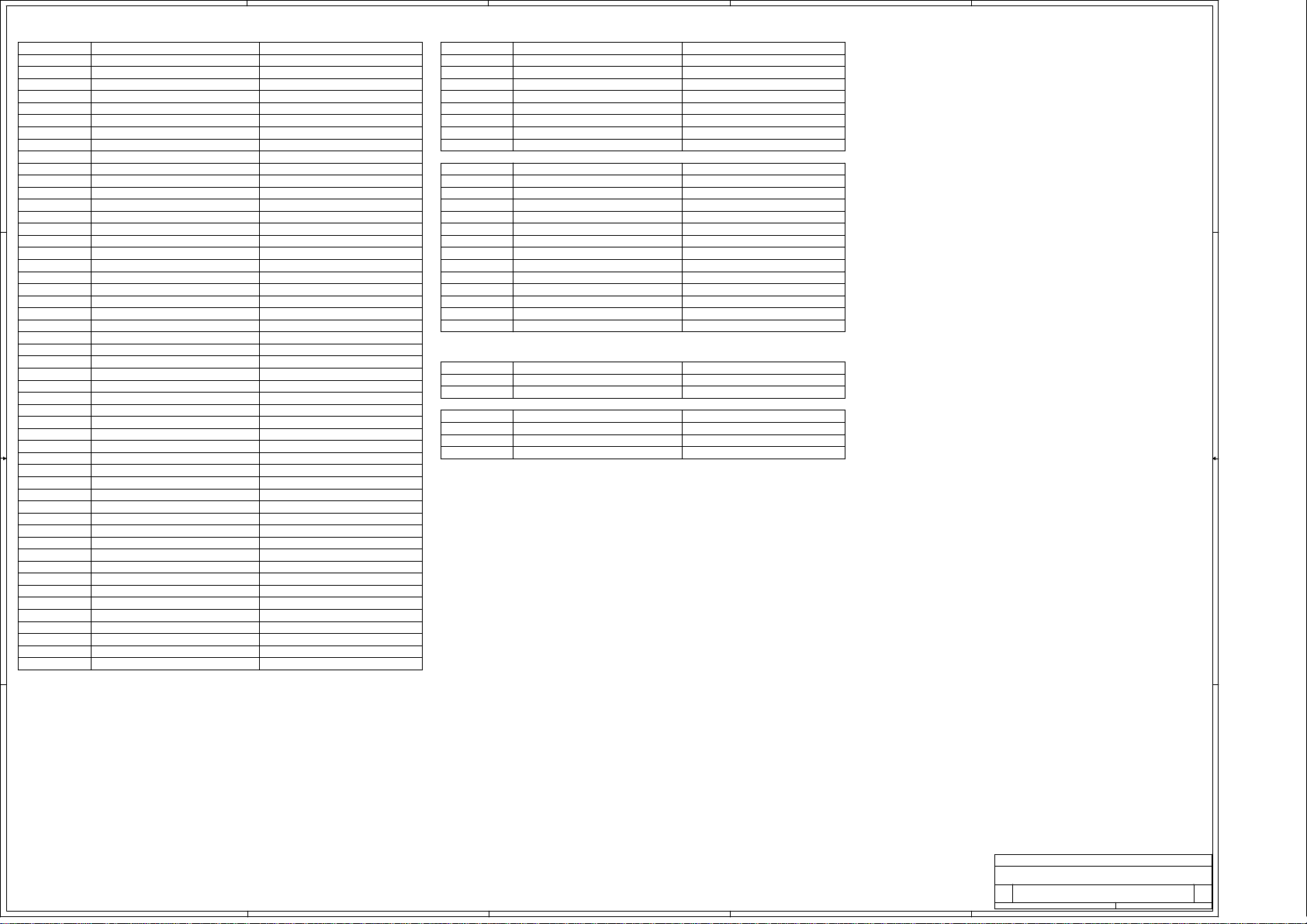

GPIO LIST

PIN NAME

CI_A0

CI_A1

CI_A2

CI_A3

CI_A4

D D

CI_A5

CI_A6

CI_A7

CI_A8

CI_A9

CI_A10

CI_A11

CI_A12

CI_A13

CI_A14

CI_MCLKI

CI_MIVAL

CI_MISTRT

CI_MDI0

CI_MDI1

CI_MDI2

CI_MDI3

CI_MDI4

CI_MDI5

C C

CI_MDI6

CI_MDI7

CI_D0

CI_D1

CI_D2

CI_D3

CI_D4

CI_D5

CI_D6

CI_D7

CI_MDO0

CI_MDO1

CI_MDO2

CI_MDO3

CI_MDO4

CI_MDO5

CI_MDO6

CI_MDO7

GPIO_42

B B

GPIO_43

GPIO_44

GPIO_45

GPIO_46

GPIO_47

Function define

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

CI Interface

3D ENABLE PANEL_3D_EN

BACKLIGHT OPWM

3D SYNC OUT

3D SYNC IN

PANEL_3D_LR_SYNC IN

GPIO Function

CI_A0

CI_A1

CI_A2

CI_A3

CI_A4

CI_A5

CI_A6

CI_A7

CI_A8

CI_A9

CI_A10

CI_A11

CI_A12

CI_A13

CI_A14

CI_MCLKI

CI_MIVAL

CI_MISTRT

CI_MDI0

CI_MDI1

CI_MDI2

CI_MDI3

CI_MDI4

CI_MDI5

CI_MDI6

CI_MDI7

CI_D0

CI_D1

CI_D2

CI_D3

CI_D4

CI_D5

CI_D6

CI_D7

CI_MDO0

CI_MDO1

CI_MDO2

CI_MDO3

CI_MDO4

CI_MDO5

CI_MDO6

CI_MDO7

3D_blink1BACKLIGHT OPWM

3D_blink2

GPIO45

GPIO46

PANEL_IN_3D_LR_SYNC

(GPIO_0)

(GPIO_1)

(GPIO_2)

(GPIO_3)

(GPIO_4)

(GPIO_5)

(GPIO_6)

(GPIO_7)

(GPIO_8)

(GPIO_9)

(GPIO_10)

(GPIO_11)

(GPIO_12)

(GPIO_13)

(GPIO_14)

(GPIO_15)

(GPIO_16)

(GPIO_17)

(GPIO_18)

(GPIO_19)

(GPIO_20)

(GPIO_21)

(GPIO_22)

(GPIO_23)

(GPIO_24)

(GPIO_25)

(GPIO_26)

(GPIO_27)

(GPIO_28)

(GPIO_29)

(GPIO_30)

(GPIO_31)

(GPIO_32)

(GPIO_33)

(GPIO_34)

(GPIO_35)

(GPIO_36)

(GPIO_37)

(GPIO_38)

(GPIO_39)

(GPIO_40)

(GPIO_41)

PIN NAME

ADIN0_SRV

ADIN1_SRV

ADIN2_SRV

ADIN3_SRV

ADIN4_SRV

ADIN5_SRV

ADIN6_SRV

ADIN7_SRV

PIN NAME

OPCTRL0

OPCTRL1

OPCTRL2

OPCTRL3

OPCTRL4

OPCTRL5

OPCTRL6

OPCTRL7

OPCTRL8

OPCTRL9

OPCTRL10

OPCTRL11

OPCTRL12

PIN NAME GPIO FunctionFunction define

LED_PWM0

LED_PWM1

PIN NAME

OPWM0

OPWM1

OPWM2

Function define

KEY_PAD

Headphone Detect

MHL Over Current Protect MHL_OC

KEY_PAD

Enable AMP_MUTE AMP_MUTE

Function define

Wifi Reset

Wifi detect WIFI_DEV_wake

Reset TUNER

Strapping Strap[3]

LED PWM

LED PWM

RESET AMP

Wifi Power Enable

LVDS Power Control

Audio Mute

Backlight Control

MHL_PWR_EN MHL_PWR_EN

Strapping

Strapping

Function define

SYSTEM EEPROM write protect

Backlight DIMMING

TUNER SWITCH

GPIO Function

KEY_PAD0

HP_DET

KEY_PAD1

PANEL_I2C_WPEnable panel I2C

GPIO Function

REG_ON

TUNER-RST

LED_0

LED_1

AMP_RESET

WAKEUP_PWR_EN

LVDS_PWR_EN

MUTE_CTL

BL_ON/OFF

FB_PWR_ENDRAM Standby Power Control

Strap[1]

Strap[2]

GPIO Function

SYS_EEPROM_WP

BL_DIMMING

SW_TUNER

A A

Hisense Electric Co.,LTD

Title

Title

5

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

313Friday, April 10, 2015

313Friday, April 10, 2015

313Friday, April 10, 2015

1.0

of

of

of

Page 4

5

MB circuit:6484

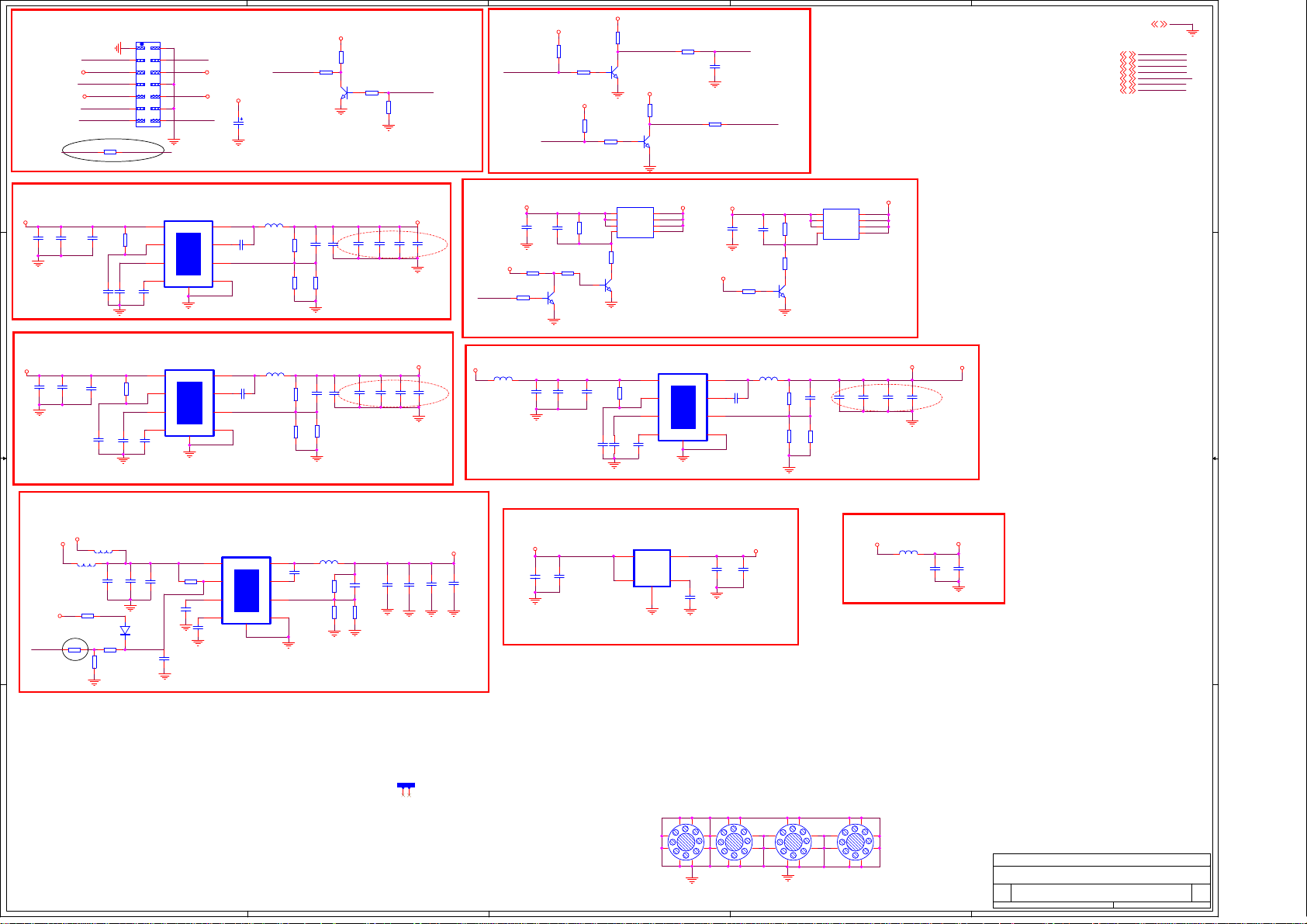

MAIN POWER

XP1

1 2

3

4

BL_ENDIMMING

6

12VS

8

10

12

14

12VS

C1

100u/16V/NC

POWER ON/OFF

12V-->5V需使用TPS54628

8

1

3

C14

N30

VIN

EN

VRG5

SS4GND

TPS54628

9

EPAD

VBST

6

SW

7

2

VFB

5

C5

100n/16V

L1

2.2 uH

3D_SG/PWM2

R538

0R/NC

5

7

9

11

13

12VS

POWER ON/OFF

VCC_A VCC_A

D D

PANEL_3D_EN 3D_LR/PWM1

DIMMING 3D_SG/PWM2

预留blinking接口电路,默认NC

12V-->5V

R13

C4

C3

C2

10u/16V

10u/16V/NC

100n/16V

C12

100n/16V

C13

1u/25V

10k

8.2n/50V

MMBT3904LT1

R14

130k

22p/50V

R15

27k

R9

1k

C6

R16

140k

4

5VS

R11

1k

3

R10

1

V3

4.7k

2

R12

47k

5A

C7

C8

C9

22u/6.3V

22u/6.3V

22u/6.3V

closed to L

Vout=0.765*(1+R14/R15//R16)=5.15V

LO = > POWER_ON

HI = > POWER_OFF

OPWRSB

5VS12VS

C10

C11

22u/6.3V

100n/16V

BL_ON/OFF

POWER SWITCH

12VS

C47

100n/16V

5VS

R509

4.7k

R33

OPWRSB

LO = > POWER_ON

HI = > POWER_OFF

1

4.7k

3.3VS

R3

10k

BL_DIMMING

C48

1u/16V

R510

4.7k

3

V6

MMBT3904LT1

2

R1

4.7k

3.3VS

3

5V

R2

1k

1

V1

MMBT3904LT1

2 3

R7

10k

R5

1

4.7k

N40

1

S1

2

S2

3

R31

S3

4

20k

G

AO4459

R32

20k

3

V46

1

MMBT3904LT1

2

5V

R6

4.7k

V2

MMBT3904LT1

2 3

8

D1

7

D1

6

D2

5

D2

R4

1k

12V

R8

1k

C501

2.2u/10V

VCCK

BL_EN

5VS

100n/16V

C50

DIMMING

R36

4.7k

C51

1u/16V

1

R34

20k

R35

10k

3

V5

MMBT3904LT1

2

1

2

3

4

N42

S1

S2

S3

G

AO4459

2

5V

8

D1

7

D1

6

D2

5

D2

8

8,12

12

12

12

1

OPWRSB5

3D_SG/PWM28

3D_LR/PWM1

PANEL_3D_EN

FB_PWR_EN

BL_DIMMING

BL_ON/OFF

GND5,6,7,8,9,10,11,12,13

OPWRSB

3D_SG/PWM2

3D_LR/PWM1

PANEL_3D_EN

FB_PWR_EN

BL_DIMMING

BL_ON/OFF

Core Power 1.0V

C C

12V

C17

C16

10u/16V

10u/16V/NC

C18

100n/16V

C19

100n/16V

Buck Converter 6A Solution

N33

8

VIN

1

EN

3

VRG5

SS4GND

VBST

VFB

EPAD

TPS54628

9

SW

R17

10k

C20

1u/25V

C21

8.2n/50V

DIGITAL POWER DVDD3V3

5V

L112

BLM18PG121SN1

C30

10u/16V

C31

10u/16V/NC

100n/16V

C33

100n/16V

C32

C34

1u/25V

N35

8

VIN

R25

1

10k

EN

3

VRG5

SS4GND

C35

8.2n/50V

VBST

EPAD

TPS54328

9

6

SW

7

2

VFB

5

C36

100n/16V

2.2 uH

L3

R28

73.2k

R27

22k

C39

C49

22u/6.3V

22p/50V

closed to L

R29

140k/NC

Vout=0.765*(1+R28/R7//R29)=3.31V

3A

C40

22u/6.3V

DVDD3V3 AVDD3V3

C41

C42

22u/6.3V

100n/16V

C27

22u/6.3V

C28

22u/6.3V

VCCK

C29

100n/16V

5A

C24

C25

22u/6.3V

22p/50V/NC

R21

27k

Vout=0.765*(1+R19/R20//R21)=1.23V

C26

22u/6.3V

closed to L

C22

100n/16V

L2

2.2 uH

R19

8.2k

R20

27k

6

7

2

5

DRAM Power

1、需要快速开关机时,L7上件;DDR-PWREN网络上件;

5V

5VS

L6

BLM18PG121SN1/NC

L7 BLM18PG121SN1

B B

5V

FB_PWR_EN

靠近IC端

A A

100R

R548

C52

10u/16V

R37

12

10k

R38

1k

R39

47k

2、不需要快速开关机,L6、R40上件;DDR-PWREN网络断开;

N36

C53

10u/16V

VD11

1N4148W

DDR_PWREN

C54

100n/16V

C56

100n/16V

R40

10k/NC

C55

1u/25V

C57

8.2n/50V

8

VIN

1

EN

3

VRG5

SS4GND

VBST

EPAD

9

TPS54228

6

SW

7

2

VFB

5

L5

2.2 uH

C58

100n/25V

R41

C59

36k

22p/50V/NC

R42

R43

140k/NC

37.4k

VOUT = 0.765 (1+R41/R42//R43)=1.50V

C60

22u/6.3V

E1

C61

22u/6.3V

NC11NC2

RSAG7.308.0219

2

C62

22u/6.3V

DDR_1.5V

C63

100n/16V

STANDBY POWER 3V3SB

5VS

2.2u/10V

C44

C43

100n/16V

N12

1

VIN

3

EN

TLV70233DBVR

预留C504,兼容其他IC使用,使用70233时需NC

2

VOUT

GND

AVDD1V2

VCCK

BLM18PG121SN1

S4

C45

10u/16V

S2

3.3VS

C46

100n/16V

S3

5

4

NC

C504

100n/16V/NC

S1

AVDD1V2

L48

C499

C500

10u/10V

100n/16V

5

D4

4

3

D4

D4

D4

2

Hisense Electric Co.,LTD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

MT5655

MT5655

MT5655

1

422Friday, April 10, 2015

422Friday, April 10, 2015

422Friday, April 10, 2015

of

of

of

1.0

1.0

1.0

Page 5

5

MB circuit:6484

N3-6

OSDA0

OSCL0

XTALI

XTALO

AVDD33_REG_STB

VCC3IO_EMMC

AVDD33_RGB_STB

D D

C70

1u/16V

AVSS33_RGB

AVDD33_PLL_STB

R52

0R

C71

4.7u/10V

AE26

OSDA0

AH26

OSCL0

B28

XTALI

B27

XTALO

J22

AVDD33_REG_STB

J1

VCC3IO_EMMC

H24

AVDD33_RGB_STB

K21

AVSS33_RGB

J23

AVDD33_PLL_STB

U25

AVDD10_LDO EMMC_CLK

AVDD10_ELDO

C66

4.7u/10V

Y26

AVDD10_LDO

AVDD10_ELDO

close to main chip

MT5655

24MHz CRYSTAL

R50

1M

Z1

R51

HC-49SM24MHZ

C67

33p/50V

晶体频偏需要小于

C525

100n/16V

R58

82k/NC

12

0R

C68

33p/50V

30PPM

R60、R61、R62、C73、C516上件,其他NC

C72

10u/10V/NC

R59

82k/NC

MMBT3904LT1 /NC

XTALI XTALO

C C

NOTE:

RESET Circuit

VD1

1N4148W/NC

1 2

3.3VS

R60

16k

3

1

V7

2

100n/16V

SYSTEM EEPROM

I2C ADDRESS "A0"

LO = > WP

HI = > WRITE

SYS_EEPROM_WP

OSCL0

OSDA0

close to main chip

R61

1k

R62

C73

22k

U0TX

U0RX

POWE#

POOE#

POCE1#

POCE0#

PDD7

PDD6

PDD5

PDD4

PDD3

PDD2

PDD1

PDD0

PARB#

PACLE

PAALE

EMMC_CLK

EMMC_RST

OPWRSB

ORESET#

FSRC_WR

R54 0R

ORESETB

C516

100n/16V

T25

U0TX

T24

U0RX

J2

POWE_B

N7

M7

L7

P3

PDD7

N1

PDD6

N2

PDD5

N4

PDD4

M3

PDD3

L1

PDD2

N6

P6

N5

L3

PACLE

K3

PAALE

P4

P7

EMMC_RST

R26

OPWRSB

L25

ORESETB

R533

L26

OIRI

100R

AH27

FSRC_WR

E-Fuse

R55

R56

2.2k

4.7k

UART0

U0RX

U0TX

Analog Power

3.3VS 3.3VS 3.3VS

B B

C74

10u/16V

STRAPPING

ICE mode + 24M + serial boot

ICE moce + 24M + ROM to 60bit ECC Nand boot

ICE moce + 24M + ROM to eMMC boot from

eMMC pins(share pins w/s NAND)

Boundary scan mode

A A

OLT mode

scan mode

cpu model mode

3.3VS

C75

100n/16V

AVDD33_RGB_STBAVDD33_REG_STB AVDD33_PLL_STB

C76

100n/16V

R70

10k/NC

R71

10k/NC

R72

10k/NC

LED_PWM0

LED_PWM1

OPCTRL3

LED_PWM0 LED_PWM1 OPCTRL3STRAPPING

001

0

0

1

1

1

R73

10k

R74

10k

R75

10k

1

0

00

0

1

11

OIRI

R53

4.7k

DVDD3V3

R57

2.2k

For ESD

R65

100R

R66

100R

RV88

AVLC18S02015

0

0

11

0

4

TP1

1

8

7

6

5

3.3VS

R67

4.7k

AVLC18S02015

VCC

WP

SCL

24LC128

R68

4.7k

RV89

N50

C77

100n/16V

3

VCC3IO_EMMC

R99 10k/NC

R98 10k/NC

R97 10k/NC

R96 10k/NC

R95 10k/NC

R94 10k/NC

R93 10k/NC

R92 10k/NC

R91 10k/NC

EMMC

R799

C84

100n/16V/NC

C89

100n/16V

TP2

1

C78

15p/50V/NC

DAT3

VDDI_C2

DAT5

DAT5

DAT6

DAT7

DAT0

DAT1

DAT2

DAT3

DAT4

DAT5

DAT6

DAT7

DAT4

DAT7

E10

F10

G10

K10

P10

A10

A11

A12

A13

A14

B10

B11

B12

B13

B14

C10

C11

C12

C13

C14

D12

D13

D14

E12

E13

E14

F12

F13

F14

G12

G13

G14

N87 H26M31001HPR

M5

CMD

M6

CLK

A3

DAT0

A4

DAT1

A5

DAT2

B2

DAT3

B3

DAT4

B4

DAT5

B5

DAT6

B6

DAT7

H5

Data Strobe

A7

RFU_0

C5

RFU_1

E5

RFU_2

E8

RFU_3

E9

RFU_4

RFU_5

RFU_6

G3

RFU_7

RFU_8

K6

RFU_9

K7

RFU_10

RFU_11

P7

RFU_12

RFU_13

A1

NC_0

A2

NC_1

A8

NC_2

A9

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

B1

NC_9

B7

NC_10

B8

NC_11

B9

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

C1

NC_18

C3

NC_19

C7

NC_20

C8

NC_21

C9

NC_22

NC_23

NC_24

NC_25

NC_26

NC_27

D1

NC_28

D2

NC_29

D3

NC_30

D4

NC_31

NC_32

NC_33

NC_34

E1

NC_35

E2

NC_36

E3

NC_37

NC_38

NC_39

NC_40

F1

NC_41

F2

NC_42

F3

NC_43

NC_44

NC_45

NC_46

G1

NC_47

G2

NC_48

NC_49

NC_50

NC_51

H1

NC_52

保证

CLK

走线包地且均匀打孔

POWE_B

R80 47R

EMMC_CLK

R81 47R

PAALE

R82 47R

PACLE

R83 47R

PDD2

R84 47R

PDD3

R85 47R

PDD4

R86 47R

PDD5

R87 47R

PDD6

R88 47R

PDD7

R89 47R

三星的

eMMC在HS400

模式下需要增加

1

A0

2

A1

3

A2

Vss4SDA

1

2

3

4

XP3

6

5

CKX-3.5-111

3

R

4

WR

2

WL

1

L

5

GND

XS13

立式回流端子

此部分网络只是为PCB出线预留

无实际意义

EMMC VCC/VCCQ Power

BLM18PG121SN1

C82

C83

100n/16V

100n/16V

引脚放置

C522

C88

1u/10V

100n/16V

引脚放置

VCC3IO_EMMC

DVDD3V3

DVDD3V3

C80

10u/10V

VCC3IO_EMMC

C85

10u/10V

靠近

靠近

eMMC Flash

L40

C81

1u/10V

eMMC Flash

C86

C87

1u/10V

1u/10V

2

VDD_0

VDD_1

VDD_2

VDD_3

VDD_4

VDDF_0

VDDF_1

VDDF_2

VDDF_3

VDDI

VSS_0

VSS_1

VSS_2

VSS_3

VSS_4

VSSQ_0

VSSQ_1

VSSQ_2

VSSQ_0

VSSQ_3

VSSQ_5

Rest_n

NC_53

NC_54

NC_55

NC_56

NC_57

NC_58

NC_59

NC_60

NC_61

NC_62

NC_63

NC_64

NC_65

NC_66

NC_67

NC_68

NC_69

NC_70

NC_71

NC_72

NC_73

NC_74

NC_75

NC_76

NC_77

NC_78

NC_79

NC_80

NC_81

NC_82

NC_83

NC_84

NC_85

NC_86

NC_87

NC_88

NC_89

NC_90

NC_91

NC_92

NC_93

NC_94

NC_95

NC_96

NC_97

NC_98

NC_99

NC_100

NC_101

NC_102

NC_103

NC_104

NC_105

C6

M4

N4

P3

P5

E6

F5

J10

K9

C2

E7

G5

H10

J5

K8

A6

C4

N2

N5

P4

P6

K5

H2

H3

H12

H13

H14

J1

J2

J3

J12

J13

J14

K1

K2

K3

K12

K13

K14

L1

L2

L3

L12

L13

L14

M1

M2

M3

M7

M8

M9

M10

M11

M12

M13

M14

N1

N3

N6

N7

N8

N9

N10

N11

N12

N13

N14

P1

P2

P8

P9

P11

P12

P13

P14

VCC3IO_EMMC

VDDI_C2

GND

DVDD3V3

C79 100n/16V

R104

R105 22R

C90

1u/10V/NC

VCC3IO_EMMC

4.7k

EMMC_RST

4,6,7,8,9,10,11,12,13

4

7,8,10,13

12

12

12

12

13

1

GND

OPWRSB

U0RX6

U0TX6

OSCL0

OSDA07,8,10,13

OPCTRL3

LED_PWM1

LED_PWM0

SYS_EEPROM_WP

OIRI

OPWRSB

U0RX

U0TX

OSCL0

OSDA0

OPCTRL3

LED_PWM1

LED_PWM0

SYS_EEPROM_WP

OIRI

5

Hisense Electric Co.,LTD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

513Wednesday, December 23, 2015

513Wednesday, December 23, 2015

513Wednesday, December 23, 2015

1.0

of

of

of

Page 6

5

MB circuit:6484

N3-4

IF_AGC

OSCL1

OSDA1

D27

D28

E27

F15

E14

E15

D15

H27

H28

J25

G28

G26

G25

ADCINP_DEMOD

ADCINN_DEMOD

AVDD12_DEMOD

IF_AGC

RF_AGC

OSCL1

OSDA1

CVBS_COM

CVBS3P

CVBS2P

CVBS1P

CVBS0P

SIF_COM

MT5655

AVDD33_VIDEO_STB

AVSS33_DEMOD

ADCINP_DEMOD

ADCINN_DEMOD

AVDD12_DEMOD

DVDD3V3

R130

R131

2.2k

D D

2.2k

CVBS_COM

CVBS3P

CVBS2P

HSYNC

VSYNC

COM

SOG

VGA_SDA

VGA_SCL

COM1

PB1P

PR1P

SOY1

COM0

PB0P

PR0P

SOY0

VDACX_OUT

AVSS33_XTAL

Y1P

Y0P

RP

GP

BP

R27

R28

N26

N28

P28

N27

P27

T28

T27

M25

L28

L27

M26

N25

K26

K25

J26

K27

K28

G27

H23

J20

K20

COM0

PB0P

PR0P

Y0P

SOY0

R529 75R

AVDD33_VIDEO_STB

AVSS33_XTAL

AVSS33_DEMOD

4

Analog Power 1V2

AVDD1V2

AVDD12_DEMOD

L30

BLM18PG121SN1

C509

100n/16V

Analog Power 3V3

C105

100n/16V

3.3VS

3

AVDD33_VIDEO_STB

C505

10u/16V

C106

100n/16V

2

7

7

8

8

10

10

10

AIN_R3

AIN_L3

OSCL1

OSDA1

TU_FAT_IN+

TU_FAT_IN-

IF_AGC

1

GND4,5,6,7,8,9,10,11,12,13

AIN_R3

AIN_L3

OSCL1

OSDA1

TU_FAT_IN+

TU_FAT_INIF_AGC

TUNER INPUT

Close to Main Chip

TU_FAT_IN+

TU_FAT_IN-

C107

47p/50V/NC

C108

47p/50V/NC

R153

R154

51R

51R

ADCINP_DEMOD

ADCINN_DEMOD

Close to CONNECTOR

R521

0R/NC

C C

COMP INPUT

XS4

左

1

GND1

GND2

GND3

Y_IN_0

2

3

PB_IN_0

4

5

PR_IN_0

6

SIGNAL1

绿

中

SIGNAL2

蓝

右

SIGNAL3

红

AV3-RGB-RC3718N-L008\Reflow

立式回流端子

B B

0R

RV8

AVLC18S02015

RV11

AVLC18S02015

RV82

AVLC18S02015

R132

10R

R133

R142

0R

R138

0R

CVBS_2 CVBS2P

C506

47p/50V/NC

R134

C92

75R

10p/50V

R136

0R

R140

C93

75R

10p/50V

R141

C94

75R

10p/50V

AV & AUDIO INPUT

RV17

RV1

RV18

AVLC18S02015

R147

R149

R144

0R

0R

0R

R151

10k/NC

AV_IN_0

XS5

左

SIGNAL1

黄

GND1

中

SIGNAL2

白

GND2

右

SIGNAL3

红

GND3

AV3-YWR-RC3720N\Reflow

A A

立式回流端子

AVLC18S02015

1

2

3

4

5

6

AVLC18S02015

CVBS_3 CVBS3P

R145

C100

75R

47p/50V

C101

1u/16V

C102

1u/16V

R152

10k/NC

C506 NC,

Close to Main Chip

R522

C507

100R/NC

47n/16V/NC

防止干扰输入信号

C508

1u/10V/NC

C95 1.5n/50V

R135

100R

R137

100R

R139

100R

R143

100R

Close to Main ChipClose to CONNECTOR

C103

R146

100R

47n/16V

C104

1u/10V

R148

33k

R150

33k

C96

10n/50V

C97

10n/50V

C98

10n/50V

C99

10n/50V

CVBS_COM

SOY0

Y0P

COM0

PB0P

PR0P

CVBS_COM

AIN_L3

AIN_R3

R552 0R

R553 0R

R554 0R

R556 0R

5

Hisense Electric Co.,LTD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

613Friday, April 10, 2015

613Friday, April 10, 2015

613Friday, April 10, 2015

1.0

of

of

of

Page 7

5

MB circuit:6484

N3-3

A25

C25

B26

A27

B25

A26

F21

AG27

AH28

AF27

AD26

AG28

AE27

AF28

AR0_ADAC

AL0_ADAC

AVDD33_ADAC

ASPDIFO1

ASPDIFO0

R514 33R

R513 33R

R512 33R

R511

close to main chip

33R

C22

AIN_R0

C24

AIN_L0

B23

AIN_R1

E23

AIN_L1

D23

AIN_R2

A22

AIN_L2

B22

AIN_R3

AIN_L3

D D

AVDD33_AADC

VMID_AADC

C125

100n/16V

C126

1u/16V

AVSS33_CLN

C23

E21

D22

K19

AIN_R3

AIN_L3

AVDD33_AADC

VMID_AADC

AVSS33_CLN

MT5655

AR0_ADAC

AL0_ADAC

AR1_ADAC

AL1_ADAC

AR2_ADAC

AL2_ADAC

AVDD33_ADAC

ASPDIFI

ASPDIFO0

AOBCK

AOLRCK

AOMCLK

AOSDATA1

AOSDATA0

AOBCK

AOLRCK

AOMCLK

AOSDATA0

4

3

Analog Power

AVDD3V3

SPDIF OUT

5V

C135

33p/50V

L41

BLM18PG181SN1

AVDD33_ADAC

C130

100n/16V

R112

100R

R113

10k

C133

10u/10V

100n/16V

C136

C131

10u/16V

AVDD3V3

C134

100n/16V

SPDIFOUTASPDIFO0

1

2

3

GQ-103\Reflow

AVDD33_AADC

SPDIF

VCC

GND

NC14NC2

2

C132

100n/16V

6

6

XS1

5

11

4,5,6,7,8,9,10,11,12,13

OSCL05,8,10,13

OSDA05,8,10,13

AIN_R3

AIN_L3

ASPDIFO1

HP_DET12

MUTE_CTL12

AMP_RESET12

AMP_MUTE12

1

GND

OSCL0

OSDA0

AIN_R3

AIN_L3

ASPDIFO1

HP_DET

MUTE_CTL

AMP_RESET

AMP_MUTE

供电选择

C168

470n/50V

C169

470n/50V

C177

470n/50V

C178

470n/50V

VDD_AMP

STPB2012-121PT

STPB2012-121PT

STPB2012-121PT/NC

STPB2012-121PT/NC

DVDD3V3 DVDD3V3_AMP

DVDD3V3

R547

HP_DET

100R

靠近IC端

BLM18PG121SN1

AMP-Lout+

AMP-Lout-

AMP-Rout-

AMP-Rout+

L44

BLM18PG121SN1

L45

L10

15.0 uH

L11

15.0 uH

L12

15.0 uH

L13

15.0 uH

AMP

DVDD3V3_AMP

DVDD3V3_AMP

SPEAKER Amplifier

I2C Address

HI 0X36

LO 0X34

C C

B B

DVDD3V3_AMP

DVDD3V3_AMP

R196 18k

此处工作频率辐射超标时,增加

MUTE_AMP

DVDD3V3_AMP

R191 10k/NC

R192 10k

R197 15k

C149

100n/25V/NC

AMP_RESET

C140 33p/50V/NC

C141

C142 33p/50V/NC

C143

AOSDATA0

C144 4.7u/10V

C140/C141/C142/C143

33p/50V/NC

33p/50V/NC

AOMCLK

AOBCK

AOLRCK

OSCL0

OSDA0

R195 470R

R198 470R

R199 200R

R202 15k/NC

R203 15k

R205 100R

R204 10k

R515

10k/NC

R185

10k

R193 22R

R194 22R

C145 4.7n/50V

C146 47n/16V

C147 4.7n/50V

C148 47n/16V

R200 18k

C150 4.7u/10V

C151 100n/16V

C152 2.2n/50V/NC

R201 22k

C153

10n/50V

100u/25V

C155

10u/25V

C156

100n/25V

C157

Close to 5711

N80

15

MCLK

21

SCLK

20

LRCLK

22

SDIN

24

SCL

23

SDA

19

PDN

8

PBTL

11

PLL_FLTP

12

VR_ANA

10

PLL_FLTM

16

OSC_RES

18

VR_DIG

6

SSTIMER

7

OC_ADJ

14

A_SEL

25

RESET_24

VDD_AMP

C158

3

PVDD_A12PVDD_A2

10u/25V

C159 100n/25V

41

45

PVDD_B144PVDD_B2

PVDD_C140PVDD_C2

TAS5711

PGND_CD137PGND_CD2

PGND_AB147PGND_AB2

17

38

48

35

PVDD_D134PVDD_D2

AVSS

DVSSO

9

DVSS28GND29AGND

30

13

AVDD

26

27

GVDD_OUT1

GVDD_OUT2

STEST

EPAD

49

DVDD

OUT_A

BST_A

BST_B

OUT_B

OUT_C

BST_C

BST_D

OUT_D

VREG

C160

2.2u/10V

C162

2.2u/10V

1

4

C165

C166

43

46

C172 1u/16V

5

C173

32

39

42

C175

C176 33n/50V

33

36

31

100n/16V

C181

100n/16V

100n/16V

33n/50V

33n/50V

1u/16V

33n/50V

C161

C163

BLM18PG121SN1

HeadPhone Output

C189

15p/50V

C195

1u/10V

N86

+INR1+INL

2

-INR

3

OUTR

4

GND

5

Mute

6

VSS

7

CN

DRV632\BBY

C196

1u/10V

OUTL

-INL

UVP

GND

VDD

CP

C190

R210

AR0_ADAC AL0_ADAC

15k

10u/10V

LO1R_PA

RV86

AVLC18S02015

A A

C193

47n/16V

C191

220p/50V

R213

5.1R

R211

R212

30.1k

MUTE_HP

43k

C192

47p/50V

C194

1u/10V

C199

15p/50V

14

13

12

11

3.3V_HP

10

9

8

100n/16V

C197

C200

47p/50V

BLM18PG121SN1

C198

2.2u/10V

R214

43k

R215

30.1k

L42

220p/50V

DVDD3V3

C202

C201

10u/10V

R217

5.1R

R216

15k

C203

47n/16V

LO1L_PA

RV85

AVLC18S02015

L110

L46

L47

L111

L43

R218

10k

R219

100R

C204

100n/16V

VCC_A

12VS

C185

1u/16V

1

2

3

4

6

5

LO1R_PA

LO1L_PA

RV87

AVLC18S02015

Power off mute

5V

12

VD2

R223

1N4148W

R224

0R/NC

VD6

47u/25V/NC

C206

1k

312

V9

MMBT3906LT1

R228

100k/NC

1 2

R226

47k

VD8

1N4148W /NC

MUTE_CTL

AMP_MUTE

R222

1k

12

VD28

1N4148W

R225

C205

1 2

100k

47u/25V

XP5

2

R

1

L

4

SW

3

GND

1N4148W

R227

12V

1k/NC

Power on mute

XS2

3.3VS

3.3VS

1

2

1

2

R537

10k/NC

VD3

R232

10k

1 2

VD27 1N4148W

VD7 BAT54C /NC

VD9

1 2

Headphone mute

BAT54C

3

AMP mute

3

1N4148W/NC

R229

10k

R231

100k

R234 10k/NC

R236

100k/NC

DVDD3V3

1

12V

1

R230

4.7k

3

V8

MMBT3904LT1

2

R233

10k/NC

3

V10

MMBT3904LT1/NC

2

MUTE_HP

MUTE_AMP

R235

4.02k/NC

5

Hisense Electric Co.,LTD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

713Friday, April 10, 2015

713Friday, April 10, 2015

713Friday, April 10, 2015

1.0

of

of

of

Page 8

5

MB circuit:6484

N3-2

AE18

TCON0

AF18

TCON1

AD17

TCON2

AE15

TCON3

AD15

TCON4

AC19

TCON5

AD18

TCON6

AD19

TCON7

AC17

TCON8

AD16

TCON9

AC15

TCON10

TX_AE4NH

TX_AE3NH

TX_AECKNH

TX_AE2NH

TX_AE1NH

TX_AE0NH

TX_AO4NH

TX_AO3NH

TX_AOCKNH

TX_AO2NH

TX_AO1NH

TX_AO0NH

BIT_SEL

PANEL_3D_EN

SDA_PANEL

AC18

TCON11

AB17

TCON12

AG14

AVDD12_LVDS

G22

AVDD33_LVDSA

AF14

REXT_VPLL

MT5655

XP11

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42 41

44 43

12

PANEL_OUT_3D_LR_SYNC

3

5

TX_AE4PH

7

TX_AE3PH

9

TX_AECKPH

11

TX_AE2PH

13

TX_AE1PH

15

TX_AE0PH

17

19

TX_AO4PH

21

TX_AO3PH

23

TX_AOCKPH

25

TX_AO2PH

27

TX_AO1PH

29

TX_AO0PH

31

33

35

SCL_PANEL

37

39

D D

AVDD12_LVDS

AVDD33_LVDSA

REXT_VPLL

R250

24k

PANEL_IN_3D_LR_SYNC

C C

B B

LVDSVDD LVDSVDD

AF19

AE19

AH19

AG19

AH18

AG18

AF17

AE17

AF16

AE16

AH16

AG16

AG15

AH15

AF24

AE24

AF23

AE23

AH23

AG23

AF22

AE22

AF21

AE21

AH21

AG21

AF20

AE20

AE0P

AE0N

AE1P

AE1N

AE2P

AE2N

AECKP

AECKN

AE3P

AE3N

AE4P

AE4N

AO0P

AO0N

AO1P

AO1N

AO2P

AO2N

AOCKP

AOCKN

AO3P

AO3N

AO4P

AO4N

AE0P

AE0N

AE1P

AE1N

AE2P

AE2N

AECKP

AECKN

AE3P

AE3N

AE4P

AE4N

AE5P

AE5N

AO0P

AO0N

AO1P

AO1N

AO2P

AO2N

AOCKP

AOCKN

AO3P

AO3N

AO4P

AO4N

AO5P

AO5N

SEL

LVDS PORT A

4

AVDD1V2_LVDS

AVDD1V2

10u/10V/NC

C290

C291

1u/16V/NC

AVDD12_LVDS

C292

100n/16V

LVDS POWER CONTROL

12VS

HI = > LVDS POWER ON

LO = > LVDS POWER OFF

PANEL_IN_3D_LR_SYNC PANEL_OUT_3D_LR_SYNC

TX_AE4NH

TX_AE3NH

TX_AECKNH

TX_AE2NH

TX_AE1NH

TX_AE0NH

TX_AO4NH

TX_AO3NH

TX_AOCKNH

TX_AO2NH

TX_AO1NH TX_AO1PH

TX_AO0NH

BIT_SEL

PANEL_3D_EN

L56

BLM18PG121SN1

L60

BLM18PG121SN1

XP12

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

45 46

47 48

49 50

兼容120HZ输出

R268

20k

LVDS_PWR_EN

LVDS PORT B

TX_AE4PH

TX_AE3PH

TX_AECKPH

TX_AE2PH

TX_AE1PH

TX_AE0PH

TX_AO4PH

TX_AO3PH

TX_AOCKPH

TX_AO2PH

TX_AO0PH

SCL_PANELSDA_PANEL

SEL

C236

1u/10V

12V

LVDSVDDLVDSVDD

C293

1u/16V

当供电为

调节

1

R266/R267/C235

AVDD33_LVDSA

AVDD3V3

+5V

C240

100n/16V

V30

MMBT3904LT1

2 3

AVDD33_LVDSA

时,注意

R266/R267

的值来调整开关导通时间,以调整

C235

R266

56k

2.2u/10V

R267

56k

C234

100n/16V/NC

的比值,作用于

1

2

3

4

C237

100n/16V/NC

3

N102

S1

S2

S3

G

AO4459

MOS

管的压差要大于

D1

D1

D2

D2

LVDS_VDD

8

7

6

5

3.3V

的斜率。

C238

10u/16V

。

LVDSVDD

C239

100n/16V

2

Common RC Filter for EMC

AO0N

AO0P

AO1N

AO1P

RP16

AO2N

AO2P

AOCKN

AOCKP

AO3N

RP17

AO3P

AO4N

AO4P

RP18

AE0N

AE0P

AE1N

AE1P

AE2N

RP19

AE2P

AECKN

AECKP

AE3N

RP20

AE3P

AE4N

AE4P

RP21

XP14

61

60

59

58

57

56

55

54

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

22R

22R

22R

22R

22R

22R

TX_AE4PH

TX_AE4NH

TX_AE3PH

TX_AE3NH

TX_AECKPH

TX_AECKNH

TX_AE2PH

TX_AE2NH

TX_AE1PH

TX_AE1NH

TX_AE0PH

TX_AE0NH

TX_AO4PH

TX_AO4NH

TX_AO3PH

TX_AO3NH

TX_AOCKPH

TX_AOCKNH

TX_AO2PH

TX_AO2NH

TX_AO1PH

TX_AO1NH

TX_AO0PH

TX_AO0NH

TX_AO0NH

TX_AO0PH

TX_AO1NH

TX_AO1PH

TX_AO2NH

TX_AO2PH

TX_AOCKNH

TX_AOCKPH

TX_AO3NH

TX_AO3PH

TX_AO4NH

TX_AO4PH

TX_AE0NH

TX_AE0PH

TX_AE1NH

TX_AE1PH

TX_AE2NH

TX_AE2PH

TX_AECKNH

TX_AECKPH

TX_AE3NH

TX_AE3PH

TX_AE4NH

TX_AE4PH

C210 10p/50V

C211 10p/50V

C212 10p/50V

C213 10p/50V

C214 10p/50V

C215 10p/50V

C216 10p/50V

C217 10p/50V

C218 10p/50V

C219 10p/50V

C220 10p/50V

C221 10p/50V

C222 10p/50V

C223 10p/50V

C224 10p/50V

C225 10p/50V

C226 10p/50V

C227 10p/50V

C228 10p/50V

C229 10p/50V

C230 10p/50V

C231 10p/50V

C232 10p/50V

C233 10p/50V

LVDSVDD

TX_AO4PH

TX_AE4PH

TX_AO4NH

TX_AE4NH

SAM屏预留8bit

R1002

R1003

R1004

R1005

4,12

5,7,10,13

5,7,10,13

6

6

13

1.5k/NC

1.5k/NC

1.5k/NC

1.5k/NC

4

4

12

12

12

12

12

PANEL_IN_3D_LR_SYNC12

3D_SG/PWM2

3D_LR/PWM1

PANEL_3D_EN

OSCL0

OSDA0

OSCL1

OSDA1

GPIO45

GPIO46

3D_blink1

3D_blink2

LVDS_PWR_EN12

PANEL_I2C_WP

3D_GLASS_SYNC

AVDD3V3

1

GND4,5,6,7,8,9,10,11,12,13

3D_SG/PWM2

3D_LR/PWM1

PANEL_3D_EN

OSCL0

OSDA0

OSCL1

OSDA1

GPIO45

GPIO46

3D_blink1

3D_blink2

LVDS_PWR_EN

PANEL_I2C_WP

PANEL_IN_3D_LR_SYNC

3D_GLASS_SYNC

PANEL I2C

R278

10k

27k/NC

SCL_PANEL

SDA_PANEL

LVDSVDD

PANEL_I2C_WP

R270 0R/NC

3

OSCL1

OSDA1

A A

V27

2N7002

R271

3

V26

2N7002

1

0R/NC

1

C247

100n/16V/NC

2

2

R276

R277 0R

5

SEL/BIT

DVDD3V3

R262

4.7k

R263

0R/NC

DVDD3V3

BIT_SELSEL

R264

4.7k/NC

R265

0R/NC

3D发射部分

3D_LR/PWM1连接电源

输入插座(2*7)第14pin

4

3D_GLASS_SYNC信号为3D眼镜

同步信号,连接到发射板

如果不需要MCU调整时序,

可以上此电阻直接bapass

同步信号到发射板

TO TCON

FROM TCON

3D_GLASS_SYNC

PANEL_IN_3D_LR_SYNC

PANEL_OUT_3D_LR_SYNC

3D_LR/PWM1

R280 0R/NC

R281 0R/NC

R282 0R/NC

R283 0R/NC

R289 0R/NC

R290 0R/NC

R291

0R/NC

R292

10k/NC

FROM MT5655

MT5655输出调制后同步信号给眼镜

GPIO45

3D_SG/PWM2

PANEL_3D_EN

R286 0R/NC

3D_SYNC

R288 0R/NC

3D_blink1

FROM MT5655

MT5655输出给背光驱动板PWM1信号

R284 0R/NC

R285

R287 0R/NC

3

C241

22u/6.3V/NC

100n/16V/NC

N99

1

DVCC

2

SENSOR1

3

SENSOR2

4

SENSOR3

5

0R/NC

I/O_SECT.0

6

I/O_SECT.1

7

LED_CON

8

SENSOR4

9

SENSOR5

10

SENSOR6

MSP430G2203IPW20/NC

R293

GPIO46

0R/NC

TO MT5655

调制前同步信号3D_SYNC输入给MT5655

BLM18PG121SN1/NC

C242

C243

22u/6.3V/NC

DVSS

I/O_ALL.1

I/O_ALL.0

TEST

RST

I/O_MODE.1

I/O_MODE.0

PWM1

PWM2

SENSOR7

FROM MT5655

MT5655输出给背光驱动板PWM2信号

L99

20

19

18

17

16

15

14

13

12

11

DVDD3V3

R295

R296

3D_blink2

TEST

RST

100R/NC

100R/NC

R297

100R/NC

R298

0R/NC

DVDD3V3

R294

4.7k/NC

1n/50V/NC

OSDA0

OSCL0

3D_SG/PWM2

R299

10k/NC

C244

3D_SG/PWM2连接电源

输入插座(2*7)第11pin

2

TEST

RST

DVDD3V3

XP16

1

2

3

4

6

5

Hisense Electric Co.,LTD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

813Wednesday, December 23, 2015

813Wednesday, December 23, 2015

813Wednesday, December 23, 2015

1.0

of

of

of

Page 9

5

MB circuit:6484

N3-1

AB4

RA0

RA0

AC9

RA1

RA1

AE3

RA2

RA2

AE6

RA3

RA3

AD9

RA4

RA4

AE4

RA5

RA5

AC11

RA6

RA6

AD5

RA7

RA7

AE9

RA8

RA8

AE5

RA9

RA9

AE7

RA10

RA10

AD11

RA11

RA11

AE12

RA12

RA12

AC5

RA13

RA13

AE10

RA14

RA14

AE11

RA15

RA15

AD7

RBA0

RBA0

AE8

RBA1

RBA1

AC7

RBA2

RBA2

V4

RCS

RCS#

W4

RCSD

D D

R310 120R

ARTN

R311

48.7R

DDR_1.5V

C C

RCSD#

AA5

RRAS

RRAS#

AA6

RCAS

RCAS#

AC4

RWE

RWE#

W5

RODT

RODT

W6

RCKE

RCKE

U6

RRESET

RRESET

AA4

RCLK0

RCLK0

Y4

RCLK0B

RCLK0#

U5

DDRVREF_A1

DDRVREF_A1

AE13

DDRVREF_A2

DDRVREF_A2

W9

ARTP

ARTP

W8

ARTN

Y8

MEMTP

Y9

MEMTN

AC20

TP_HPCPLL

AD20

TN_HPCPLL

R4

DDRV_1

T4

DDRV_2

R5

DDRV_3

T5

DDRV_4

R6

DDRV_5

T6

DDRV_6

R7

DDRV_7

T7

DDRV_8

R8

DDRV_9

V8

DDRV_10

R9

DDRV_11

T9

DDRV_12

U9

DDRV_13

V9

DDRV_14

AB12

DDRV_15

T8

DDRVA

DDRVA

MT5655

ANALOG POWER

DVDD3V3

AVDD33_DDR

VCCK

AVSS12_DDR

AVDD12_DDR

AVDD33_DDR

AVDD12_DDR

AVSS12_DDR

AVDD33_DDR

AVDD12_DDR

RDQM0

RDQS0

RDQS0#

RDQM1

RDQS1

RDQS1#

RDQ10

RDQ11

RDQ12

RDQ13

RDQ14

RDQ15

RDQM2

RDQS2

RDQS2#

RDQ16

RDQ17

RDQ18

RDQ19

RDQ20

RDQ21

RDQ22

RDQ23

RDQM3

RDQS3

RDQS3#

RDQ24

RDQ25

RDQ26

RDQ27

RDQ28

RDQ29

RDQ30

RDQ31

C250

1u/10V

AA3

RDQM0RDQM0

Y2

RDQS0RDQS0

Y1

RDQS0B

U3

RDQ0RDQ0

RDQ0

AE2

RDQ1RDQ1

RDQ1

T3

RDQ2

RDQ2

AE1

RDQ3

RDQ3

R2

RDQ4RDQ4

RDQ4

AF2

RDQ5RDQ5

RDQ5

R1

RDQ6

RDQ6

AF1

RDQ7

RDQ7

W2

RDQM1RDQM1

AB3

RDQS1

AB2

RDQS1B

AD2

RDQ8

RDQ8

U1

RDQ9

RDQ9

AD3

RDQ10

U2

RDQ11RDQ11

AC3

RDQ12RDQ12

V1

RDQ13

AC1

RDQ14RDQ14

V2

RDQ15RDQ15

AF8

RDQM2RDQM2

AG7

RDQS2RDQS2

AH7

RDQS2B

AG3

RDQ16

AG12

RDQ17

AF3

RDQ18

AH12

RDQ19

AG2

RDQ20

AG13

RDQ21

AH2

RDQ22

AH13

RDQ23

AG6

RDQM3

AF9

RDQS3

AG9

RDQS3B

AF12

RDQ24

AH4

RDQ25

AF11

RDQ26

AG4

RDQ27

AG10

RDQ28

AF5

RDQ29

AH10

RDQ30

AF6

RDQ31

U4

AVDD33_DDR

Y15

AVDD12_DDR

W15

AVSS12_DDR

C251

100n/16V

4

AD/CM Damping

2_WE#

RODT RODT

2_CAS#

2_RAS#

2_A7

2_A2

2_A5

2_A0

2_A3

2_A9

2_A13

2_BA1

2_A10

2_BA0

2_BA2

2_A8

2_A14

2_A4

2_A1

2_A15

2_A12

2_A11

2_A6

TP3

1

Support asymmetry /symmetry DRAM

DDR_1.5V

RWE

RCAS

RRAS

22R

RP1

22R

RP2

RRESETRRESET

22R

RP3

22R

RP4

22R

RP5

22R

RP6

1_RCS RCSD 2_RCSDRCS

R313

47R

Differential Clock

NEAR Main Chip

RCLK0

RCLK0B

R325 49.9k

RRESET

R326 0R

RODT RODT

1_CAS#

1_RAS#

RP7 22R

RA7

RA2

RA5

RA0

RA3

RA9

RA13

RBA1

RA10

RBA0

RBA2

RA8

RA14

RA4

RA1

RA15

RA12

RA11

RA6

1_A7

1_A2

1_A5

1_A0

RP8

22R

1_A3

1_A9

1_A13

RRESET RRESET

RP9

22R

1_BA1

1_A10

1_BA0

1_BA2

22R

RP10

1_A8

1_A14

1_A4

1_A1

RP11 22R

1_A15

1_A12

1_A11

1_A6

RP12 22R

DDR_1.5V DDR_1.5V

R314

100R/NC

R315

100R/NC

C320

R316

NEAR DRAM

100n/16V

47R

RCLK0

R319

100R

RCLK0B

3

DDR3#1 DDR3#2

N60

E3

RDQ0

DQ0

F7

RDQ1

RWE1_WE#

RCAS

RRAS

RA7

RA2

RA5

RA0

RA3

RA9

RA13

RBA1

RA10

RBA0

RBA2

RA8

RA14

RA4

RA1

RA15

RA12

RA11

RA6

R317

100R/NC

R318

100R/NC

RCKE

C321

100n/16V

DDR_1.5V

R321

240R

R327

100R/NC

R328

100R/NC

DQ1

F2

RDQ2

DQ2

F8

RDQ3

DQ3

H3

RDQ4

DQ4

H8

RDQ5

DQ5

G2

RDQ6

DQ6

H7

RDQ7

DQ7

D7

RDQ8

DQ8

C3

RDQ9

DQ9

C8

RDQ10

DQ10

C2

RDQ11

DQ11

A7

RDQ12

DQ12

A2

RDQ13

DQ13

B8

RDQ14

DQ14

A3

RDQ15

DQ15

C7

RDQS1

UDQS

B7

RDQS1B

UDQS#

F3

RDQS0

LDQS

G3

RDQS0B

LDQS#

D3

RDQM1

UDM

E7

RDQM0

LDM

H1

DDRVREF_A1 DDRVREF_A2

VREFDQ

M8

A_VREFCA1

VREFCA

L8

A_ZQ1

ZQ

T2

RRESET

RESET#

A1

VDDQ_0

A8

VDDQ_1

C1

VDDQ_2

C9

VDDQ_3

D2

VDDQ_4

E9

VDDQ_5

F1

VDDQ_6

H2

VDDQ_7

H9

VDDQ_8

B2

VDD_0

D9

VDD_1

G7

VDD_2

VDD_3K2VSS_3

K8

VDD_4

N1

VDD_5

N9

VDD_6

R9

VDD_8

R1

VDD_7

H5TQ4G63AFR-RDC

DDR_1.5V

R329

100R/NC

RODT

R330

100R/NC

2

N3

1_A0

A0

P7

1_A1

A1

P3

1_A2

A2

N2

1_A3

A3

P8

1_A4

A4

P2

1_A5

A5

R8

1_A6

A6

R2

1_A7

A7

T8

1_A8

A8

R3

1_A9

A9

L7

1_A10

A10/AP

R7

1_A11

A11

N7

1_A12

A12/BC#

J1

NC_0

J9

NC_1

L1

NC_2

L9

NC_3

M7

1_A15

NC_4

T3

1_A13

NC_5

T7

1_A14

NC_6

M2

1_BA0

BA0

N8

1_BA1

BA1

M3

1_BA2

BA2

J7

RCLK0

CK

K7

RCLK0B

CK#

L2

1_RCS

CS#

K3

1_CAS#

CAS#

K1

RODT

ODT

J3

1_RAS#

RAS#

L3

1_WE#

WE#

K9

RCKE

CKE

B1

VSSQ_0

B9

VSSQ_1

D1

VSSQ_2

D8

VSSQ_3

E2

VSSQ_4

E8

VSSQ_5

F9

VSSQ_6

G1

VSSQ_7

G9

VSSQ_8

A9

VSS_0

B3

VSS_1

E1

VSS_2

G8

J2

VSS_4

J8

VSS_5

M1

VSS_6

M9

VSS_7

P1

VSS_8

P9

VSS_9

T1

VSS_10

T9

VSS_11

DDR3#1 Ref Volt.

R331

1k

A_VREFCA1 A_VREFCA2

R332

1k

Near DRAM

DDR_1.5V

C323

100n/16V

C324

100n/16V

1

GND4,5,6,7,8,9,10,11,12,13

N61

E3

RDQ16

F7

RDQ17

F2

RDQ18

F8

RDQ19

H3

RDQ20

H8

RDQ21

G2

RDQ22

H7

RDQ23

D7

RDQ24

C3

RDQ25

C8

RDQ26

C2

RDQ27

A7

RDQ28

A2

RDQ29

B8

RDQ30

A3

RDQ31

C7

RDQS3

B7

RDQS3B

F3

RDQS2

G3

RDQS2B

D3

RDQM3

E7

R534

R535

RDQM2

1k/NC

1k/NC

C322

100n/16V

H1

M8

A_VREFCA2

L8

A_ZQ2

T2

RRESET

R322

DDR_1.5VDDR_1.5V

240R

A1

A8

C1

C9

D2

E9

F1

H2

H9

B2

D9

G7

K8

N1

N9

R9

R1

DDR3#2 Ref Volt.

DDR_1.5VDDR_1.5V

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

A10/AP

DQ11

DQ12

A12/BC#

DQ13

DQ14

DQ15

UDQS

UDQS#

LDQS

LDQS#

UDM

LDM

VREFDQ

VREFCA

ZQ

RESET#

VSSQ_0

VDDQ_0

VSSQ_1

VDDQ_1

VSSQ_2

VDDQ_2

VDDQ_3

VSSQ_3

VDDQ_4

VSSQ_4

VSSQ_5

VDDQ_5

VSSQ_6

VDDQ_6

VSSQ_7

VDDQ_7

VDDQ_8

VSSQ_8

VDD_0

VSS_0

VDD_1

VSS_1

VSS_2

VDD_2

VDD_3K2VSS_3

VSS_4

VDD_4

VDD_5

VSS_5

VSS_6

VDD_6

VSS_7

VDD_8

VSS_8

VDD_7

VSS_9

VSS_10

VSS_11

H5TQ2G63FFR-RDC

R333

1k

R334

1k

N3

2_A0

A0

P7

2_A1

A1

P3

2_A2

A2

N2

2_A3

A3

P8

2_A4

A4

P2

2_A5

A5

R8

2_A6

A6

R2

2_A7

A7

T8

2_A8

A8

R3

2_A9

A9

L7

2_A10

R7

2_A11

A11

N7

2_A12

J1

NC_0

J9

NC_1

L1

NC_2

L9

NC_3

M7

2_A15

NC_4

T3

2_A13

NC_5

T7

2_A14

NC_6

M2

2_BA0

BA0

N8

2_BA1

BA1

M3

2_BA2

BA2

J7

RCLK0

CK

K7

RCLK0B

CK#

L2

2_RCSD

CS#

K3

2_CAS#

CAS#

K1

RODT

ODT

J3

2_RAS#

RAS#

L3

2_WE#

WE#

K9

RCKE

CKE

B1

B9

D1

D8

E2

E8

F9

G1

G9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

C325

100n/16V

C326

100n/16V

Near DRAM

DDR_1.5V

C272

10u/10V

C264

100n/16V

C302

10u/10V

C258

100n/16V

C273

1u/10V

C259

100n/16V

100n/16V

100n/16V

C260

C261

100n/16V

10n/50V

Main Chip Bottom Side

C265

C266

100n/16V

C267

1u/10V

C268

100n/16V

C269

10u/10V

bottom side

C274

100n/16V

C275

100n/16V

C276

100n/16V

C277

22u/6.3V

C278

4.7u/10V

C279

100n/16V

C280

100n/16V

C281

100n/16V

C282

100n/16V/NC

C283

100n/16V

C284

100n/16V

C285

100n/16V

C286

1u/10V

C287

100n/16V

bottom side

C305

C303

C304

100n/16V

1u/10V

4

C306

100n/16V

C307

100n/16V

C308

100n/16V

C309

100n/16V

3

100n/16V

100n/16V

C311

C310

C312

100n/16V

C313

1u/10V

C314

22u/6.3V/NC

Hisense Electric Co.,LTD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

1.0

of

of

of

913Friday, April 10, 2015

913Friday, April 10, 2015

913Friday, April 10, 2015

C255

C256

C257

22u/6.3V

100u/16V/NC

B B

DDR_1.5V

C262

10u/10V

DDR_1.5V

C270

100u/16V/NC

DDR_1.5V

A A

C300

100u/16V/NC

4.7u/10V

Close to Main Chip

C263

1u/10V

CAPs for DRAM IO Power ( DDR#1 )

TOP SIDE

C271

22u/6.3V

CAPs for DRAM IO Power ( DDR#2 )

TOP SIDE

C301

22u/6.3V

5

Page 10

5

MB circuit:6484

ATSC/T+C/T2/ISDB TUNER

SHARP-VA4N1BC1201/NC

D D

C C

NC1

RF_SW

B1_3.3V

NC2

IF AGC

IF-

IF+

NC3

NC4

SCL

SDA

GND112GND213GND314GND4

15

U2

1

2

3

4

5

6

7

8

9

10

11

TUNER-SW

POW_TUNER

IF_AGC_T

IF_P_TU

IF_N_TU

C529

100n/16V

U1

BM

IFAGC

SCL

SDA

DIFP

DIFN

GND7GND8GND9GND

10

HFT-96S3/NC

U3

SCT-89S1-13FJ4H-FJ4\Reflo

1

2

3

4

5

6

ISDB DEMO

IF_AGC_ISDB

DEMO_SCL

DEMO_SDA

1.2V_DEMO

L53

BLM18PG121SN1

3.3V_DEMO_D

R357

1.2V_DEMO

BLM18PG121SN1

BLM18PG121SN1

L51

4.7k/NC

R358

0R

L52

B B

A A

C340

1u/10V

1u/10V

IF_N_TU

IF_P_TU

33p/50V

33p/50V

C342

100n/16V

C343

100n/16V

C344

1u/10V

R354 0R

R355 0R

C338

C339

C341

100n/16V

1.2V_DEMO

1.2V_DEMO

100n/16V

C346

12

25.4MHz

Z2

JAS25D\TP

C345

C347

100n/16V

C348 100n/16V

C349 100n/16V

C350 100n/16V

C351 100n/16V

DEMOD_RST

XOUT

R356

1M

XIN

24

23

XI

25

PLLVDD_25

26

PLLVSS_26

27

VDDC_27

28

CKI

29

SLADRS1

30

TSMD

31

VSS_31

32

VDDC_32

33

ADCVDD_33

34

ADCVSS_34

35

VREFL_35

36

VREFH_36

AINPI37AINNI38AINPQ39AINNQ40VPGM41SYRSTN42STSFLG143SRSFLG044SCL45SDA46VSS_4747VDDS_48

IF_IN

IF_IP

IF_QP

IF_QN

R364

100R

RF/SW

+BM

IF-AGC

SCL

SDA

DIF1

DIF2

Rest

XOUT

GND10GND11GND12GND

13

Close to IC

C337

100n/16V

TP50

CLOCK_OUT#

22

XO

XCKO

3.3V_DEMO_D

R365

4.7k

100n/16V

1

2

3

4

5

6

7

8

9

R353 20k

21

20

TNSCL

TNSDA

C352

POW_TUNER

C330

100n/16V

TUNER-SW

3.3V_Tuner

R347

100k

C334

1u/10V

靠近

Tuner

19

18

AGCCNTI

AGCCNTR

C331

10u/10V

IF_AGC_T

端

3.3V_DEMO_D

R359

4.7k/NC

R360

0R

16

17

SBYTE

SLADRS0

4

3.3V_Tuner

L65

BLM18PG121SN1

Close to Tuner

R340 10k

C335

10n/50V

R343 0R/NC

R344 0R/NC

R345 100R

R346 100R

C332

C333

22p/50V

22p/50V

R348

TUNER-RST

100R/NC

靠近IC端

Demodulator:TC90537

Slave Address:

"0011"+SLADRS[1:0]+"0" =18(0011000)

3.3V_DEMO_D

C353

100n/16V

14

VDDS_14

13

VSS_13

SRCK

PBVAL

SRDT

SLOCK

RLOCK

RERR

SLPEN

GPIO2

GPIO1

GPIO0

VSS_2

VDDC_1

48

3.3V_DEMO_D

0R

N91

TC90537FG

12

11

10

9

8

7

6

5

4

3

2

1

C355

100n/16V

TUNER_SDA

TUNER_SCL

1.2V_DEMO

15

RSEORF

R367

R368 0R

IF_AGC_5655

IF_AGC_ISDB

3.3V_Tuner

R342

R341

2.2k

2.2k

Tuner switch

0: Cable

1: Air

TUNER-SW

V15

MMBT3904LT1

R361

R362

R363

R516

C354

100n/16V

R349

10k

3

2

TUNER_SCL

TUNER_SDA

DEMO_SCL

DEMO_SDA

IF_P_TU

IF_N_TU

R350

100R/NC

1

R352

22k/NC

22R

22R

22R

22R

R340:DVBT2 change to 1K

C335 ATSC 10nF 1053142

DVBT2/T/C 100nF 1052674

3.3V_Tuner

C336

1u/10V/NC

R351

SW_TUNER

22k

DEMOD_TSSYNC

DEMOD_TSCLK

DEMOD_TSVAL

DEMOD_TSDATA0

100n/16V

C528

3

MT5655 AGC

IF_AGCIF_AGC_5655

R369 10k

C356

47n/16V

Close to TunerTuner

C359

47p/50V

IF_P_TU

IF_N_TU

Differential Pair

ATSC/DVB-T/C/ISDB_Tuner_ POWER

5V

C365

C366

10u/10V

100n/16V

C361

1u/10V

C362

1u/10V

C360

47p/50V

N19

3

VOUT_1

VIN

VOUT_2

ADJ

SPX1117M3-ADJLD1117A-ADJ

1

Vout=1.25 x (1+R2/R1)= 3.3V

Power of Demodulator

5V

10u/10V

3.3V_DEMO

1u/16V

C369

C375

100n/16V

C376

100n/16V

C370

N21

3

VOUT

VIN

VOUT

ADJ

1

LD1117A-3.3AZ1117H-3.3

N22

3

VOUT

VIN

VOUT

ADJ

1

AZ1117-1.2

4

2

R372 100R

R373 100R

4

2

150mA(Max)

4

2

100n/16V

100n/16V

TUNER I2C

C367

10n/50V

R336

110R

R339

180R

3.3V_DEMO

C371

10u/10V

1.2V_DEMO

C377

10u/10V

TUNER_SDA

TUNER_SCL

R374

330R

3.3V_Tuner

C368

10u/10V

L55

BLM18PG121SN1

C372

C378

R518

0R

R517

0R

C357

33p/50V

100n/16V

2

R370 100R

R371 100R

C358

33p/50V

C363

47p/50V/NC

R377

680R/NC

C364

47p/50V/NC

3.3V_DEMO_D

C373

1u/16V

C374

R375

0R

R376

0R

OSDA0

OSCL0

TU_FAT_IN+

TU_FAT_IN-

5,7,8,13

6

6

6

12

12

12

12

IF_AGC

TU_FAT_IN+

TU_FAT_IN-

OSCL05,7,8,13

OSDA0

SW_TUNER

TUNER-RST

DEMOD_RST

DEMOD_TSSYNC12

DEMOD_TSVAL12

DEMOD_TSCLK

DEMOD_TSDATA012

1

GND4,5,6,7,8,9,10,11,12,13

IF_AGC

TU_FAT_IN+

TU_FAT_INOSCL0

OSDA0

SW_TUNER

TUNER-RST

DEMOD_RST

DEMOD_TSSYNC

DEMOD_TSVAL

DEMOD_TSCLK

DEMOD_TSDATA0

5

Hisense Electric Co.,LTD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

10 13Tuesday, November 10, 2015

10 13Tuesday, November 10, 2015

10 13Tuesday, November 10, 2015

1.0

of

of

of

Page 11

5

MB circuit:6484

N3-5

HDMI_CEC CEC

R380

HDMI_0_SCL

R541 49.9R

HDMI_1_SCL

R542

HDMI_2_SCL

D D

C C

HDMI Power

5V AVDD3V3

HDMI_0_SDA

HDMI_1_SDA

HDMI_2_SDA

R381

1k

C390

10n/10V

R543

R544

R545

R546 49.9R

HDMI_0_PWR5V

HDMI_0_HPD_CBUS

HDMI_1_HPD

HDMI_2_HPD

MHL_SENSE

AVDD12_HDMI1

AVDD12_HDMI2

AVDD33_HDMI

V16

2

AO3400A

1

R382

100k

C19

100R

C16

D19

49.9R

U23

49.9R

D16

49.9R

G19

49.9R

U24

E18

E17

F19

T22

E16

A14

U26

G20

3

AVDD33_HDMI

C391

100n/16V

防止HDMI3V3倒灌

HDMI_CEC

HDMI_0_SCL

HDMI_1_SCL

HDMI_2_SCL

HDMI_0_SDA

HDMI_1_SDA

HDMI_2_SDA

HDMI_0_PWR5V

HDMI_0_HPD_CBUS

HDMI_1_HPD

HDMI_2_HPD

MHL_SENSE

AVDD12_HDMI1

AVDD12_HDMI2

AVDD33_HDMI

MT5655

AVDD1V2

AVDD12_HDMI1

HDMI_0_RX_0

HDMI_0_RX_0B

HDMI_0_RX_1

HDMI_0_RX_1B

HDMI_0_RX_2

HDMI_0_RX_2B

HDMI_0_RX_C

HDMI_0_RX_CB

HDMI_1_RX_0

HDMI_1_RX_0B

HDMI_1_RX_1

HDMI_1_RX_1B

HDMI_1_RX_2

HDMI_1_RX_2B

HDMI_1_RX_C

HDMI_1_RX_CB

HDMI_2_RX_0

HDMI_2_RX_0B

HDMI_2_RX_1

HDMI_2_RX_1B

HDMI_2_RX_2

HDMI_2_RX_2B

HDMI_2_RX_C

HDMI_2_RX_CB

C392

100n/16V

C393

1u/16V

A17

B17

A16

B16

A15

B15

C17

D17

A20

B20

A19

B19

C18

D18

C21

B21

W26

W25

V26

V25

V28

V27

Y28

Y27

AVDD1V2

4

RX_0_0

RX_0_0B

RX_0_1

RX_0_1B

RX_0_2

RX_0_2B

RX_0_C

RX_0_CB

RX_1_0

RX_1_0B

RX_1_1

RX_1_1B

RX_1_2

RX_1_2B

RX_1_C

RX_1_CB

RX_2_0

RX_2_0B

RX_2_1

RX_2_1B

RX_2_2

RX_2_2B

RX_2_C

RX_2_CB

AVDD12_HDMI2

C394

100n/16V

HDMI Port0 (MHL)

HDMI_0_PWR5V

C397

47n/16V

R411

300k

R410

47k

MHL_SENSE

1

3.3VS

R412

20k

3

V19

2

MMBT3904LT1

3

R405

1k

HDMI_0_SCL

HDMI_0_SDA

R413

10k

100R

3

1

2

HDMI_0_HPD_CBUS

HDMI0_5V

R414

V18

MMBT3904LT1

2

5,6,7,8,9,10,11,12,13,14,15,17,18,19,20,21

5VS

1

2

1

3

R540

R406

47k

0R

VD30

BAT54C

R407

47k

2

V17

AO3401L

3

need fine tune

12

VD18

1N4148W

R415

820R

RX_0_2

MHL_SENSE

RX_0_2B

RX_0_1

RX_0_1B

RX_0_0

RX_0_0B

RX_0_C

RX_0_CB

HDMI_CEC

R408 49.9R

R409 49.9R

R416

33R

HDMI0_5V

R440

R441

R442

R443

R444

R445

R446

R447

R448

RV23

MHL_PWR_EN

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

RV25

RV24

RV26

ASES12U020R2

ASES12U020R2

ASES12U020R2

R525

300k

RX-0_2

RX-0_2B

RX-0_1

RX-0_1B

RX-0_0

RX-0_0B

RX-0_C

RX-0_CB

RV27

ASES12U020R2

ASES12U020R2

5VS

MHL_SENSE

H : ON

L : OFF

1

DATA2+

2

DATA2S

3

DATA2-

4

DATA1+

5

DATA1S

6

DATA1-

7

DATA0+

8

DATA0S

9

DATA0-

10

CLK+

11

CLKS

12

CLK-

13

CEC

14

NC

15

SCL

16

SDA

17

CEC/GND

18

+5V

19

HPDET

XS9

161311192\TP

卧式贴片端子

L103

BLM18PG121SN1

1k

R417

1k/NC

R418

23

5V_MHL

C400

1u/10V

RV90 ASES12U020R2

TPS2065C_2

5

IN

4

EN

N100

RX-0_2

RX-0_2B

RX-0_1

RX-0_1B

RX-0_0

RX-0_0B

RX-0_C

RX-0_CB

OUT

GND

FLT

RV91 ASES12U020R2

RV92 ASES12U020R2

RV93 ASES12U020R2

RV94 ASES12U020R2

RV95 ASES12U020R2

RV96 ASES12U020R2

RV97 ASES12U020R2

22u/6.3V

1

2

3

R524

R419

GND120GND322GND221GND4

C398

12

12

5V_VBUS

100R

47k

ASPDIFO17

MHL_PWR_EN

MHL_OC

C399

100n/16V

1

HDMI0_5V

MHL_OC

3.3VS

R523

10k

GND

ASPDIFO1

MHL_PWR_EN

MHL_OC

HDMI Port1 (ARC)

RX_1_2

R383

RX_1_2B

R384

RX_1_1

R385

R392

47k

R396

0R

3

V42

2

RX_1_1B

RX_1_0

RX_1_0B

RX_1_C

RX_1_CB

HDMI_CEC

R393 49.9R

R394 49.9R

R397

1k

R400

100k

ARC

C395

100n/16V

R386

R387

R388

R389

R390

RV29

RV28

ASES12U020R2

HDMI1_5V

R395

47k

HDMI_1_HPD

R391

47k

HDMI1_5V

100n/16V

R398

47R

1

C402

MMBT3904LT1

B B

HDMI_1_SCL

HDMI_1_SDA

3.3VS

R399

47k

1

MMBT3904LT1

3

V43

2

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

RV31

RV30

ASES12U020R2

ASES12U020R2

ASES12U020R2

RX-1_2

RX-1_2B

RX-1_1

RX-1_1B

RX-1_0

RX-1_0B

RX-1_C

RX-1_CB

RV32

ASES12U020R2

23

1

DATA2+

2

DATA2S

3

DATA2-

4

DATA1+

5

DATA1S

6

DATA1-

7

DATA0+

8

DATA0S

9

DATA0-

10

CLK+

11

CLKS

12

CLK-

13

CEC

14

NC

15

SCL

16

SDA

17

CEC/GND

18

+5V

19

HPDET

XS10

161311192\TP

卧式贴片端子

GND120GND322GND221GND4

5V

VD17

4

RX-1_1

RX-1_1B RX-1_2B

RX-1_C

RX-1_CB

R401

47k

C396

1u/10V

R402

47k

IC1

5

VCC

6

IC2

ESDA6V8UE

VD19

4

IC1

5

VCC

6

IC2

ESDA6V8UE

I/O3

GND

I/O1

GND

R404

180R/NC

3

RX-1_2

2

1

3

RX-1_0

I/O3

2

1

RX-1_0B

I/O1

R403

ASPDIFO1ARC

330R

HDMI Port2

HDMI_2_SCL

HDMI_2_SDA

3.3VS

R434

3

1

V45

47k

2

MMBT3904LT1

R432

47k

HDMI_2_HPD

HDMI2_5V

R430

47k

HDMI2_5V

R435

47R

R431

47k

C401

100n/16V

1

MMBT3904LT1

R433

0R

3

V44

2

RX_2_2

RX_2_2B

RX_2_1

RX_2_1B

RX_2_0

RX_2_0B

RX_2_C

RX_2_CB

HDMI_CEC

R428 49.9R

R429 49.9R

R436

1k

R437

100k

C403

100n/16V

R420

R421

R422

R423

R424

R425

R426

R427

RV38

RV39

ASES12U020R2

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

4.7R

RV41

RV40

ASES12U020R2

ASES12U020R2

ASES12U020R2

RX-2_2

RX-2_2B

RX-2_1

RX-2_1B

RX-2_0

RX-2_0B

RX-2_C

RX-2_CB

RV42

ASES12U020R2

BSE-4

20

GND2

21

GND1

1

DATA2+

2

DATA2S

3

DATA2-

4

DATA1+

5

DATA1S

6

DATA1-

7

DATA0+

8

DATA0S

9

DATA0-

10

CLK+

11

CLKS

12

CLK-

13

CEC

14

NC

15

SCL

16

SDA

17

CEC/GND

18

+5V

19

HPDET

立式贴片端子

22

24

GND3

GND423GND5

RX-2_1

RX-2_1B RX-2_2B

RX-2_C

RX-2_CB

XS11

VD20

4

IC1

5

VCC

6

IC2

ESDA6V8UE

VD21

4

5

6

ESDA6V8UE

3

RX-2_2

I/O3

2

GND

1

I/O1

3

IC1

VCC

IC2

RX-2_0

I/O3

2

GND

1

RX-2_0B

I/O1

R404用来调整SPDIF输出幅度

A A

5

R1007 0R

R1008 0R

R1009 0R

R1006 0R

层侧出两路

Top

Bottom

add 20150420

HDMI,端子GND

层每个端子预留两个0R电阻

4

同信号

GND

相连

Hisense Electric Co.,LTD

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

3

2

Date: Sheet

MT5655

MT5655

MT5655

1

1.0

1.0

11 13Thursday, April 23, 2015

11 13Thursday, April 23, 2015

11 13Thursday, April 23, 2015

1.0

of

of

of

Page 12

5

MB circuit:6484

4

3

2

1

N3-7

D2

D1

C3

C1

C2