Page 1

CDMA/GSM Mobile Phone

EG59

Technical Manual

Apr, 2010

Page 1 of 13

Page 2

1. Introduction

EG59 mobile phone is designed and developed for CDMA/GSM network.

Its main features are:

The QUALCOMM single chip QSC6085 and MediaTek MT6223D

chipset are used, which feature Zero-IF and CMOS technology,

resulting high integration and great RF performance

Memory chips are 256MByte NAND/128MByte DDR and 64M bit

NOR/32M bit PSram MCP

65k colors, 320*240 TFT color LCD display

MIDI,MMF,AAC,MP3 ringtone

Camera

T-Flash memory card

Bluetooth

Touch panel

USB storage

2. Key Design Technology

2.1. Hardware:

CDMA/GSM/Bluetooth antenna design

technology Transmit link design technology

Receive link design technology

Frequency synthesize technology

RF control software compensation technology

Integrated system control technology

LCD implementation technology Interface

circuit design technology

Low power consumption design technology

High intensity PCB design technology

Ringtone quality improve technology

Components cost control

EMC/EMI design technology

Page 2 of 13

Page 3

Reliability design technology

2.2. Software:

Reliable control of Flash & RAM

User-friendly UI design

Localized system capture optimization technology

Power consumption reducing software optimization technology

Systematic reliability design

3. Technical Specifications and Performance Parameters

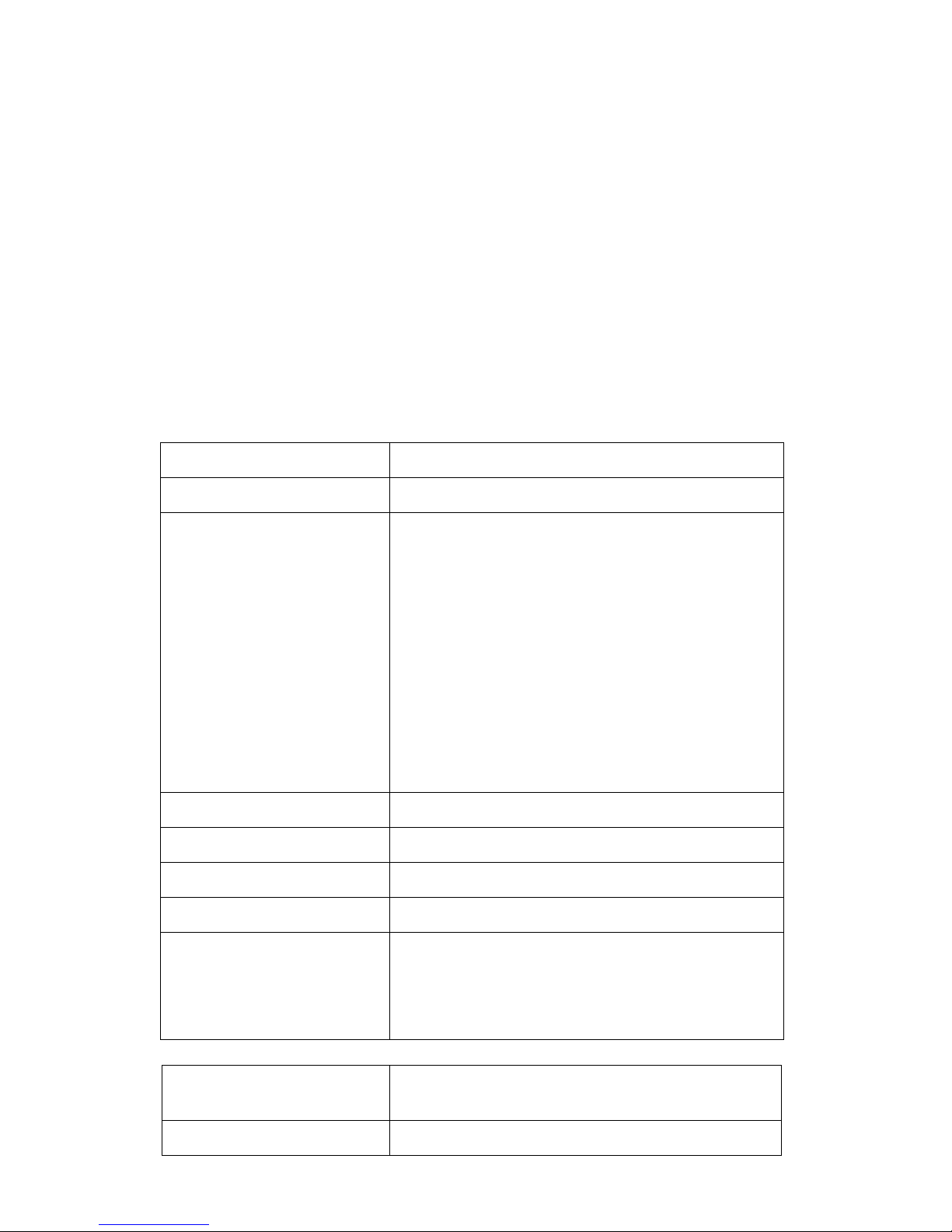

3.1. General specifications

Item Content

Mode CDMA/GSM

Frequency Band CDMA 800MHz

Tx: 824 ~ 849MHz

Rx: 869 ~ 894MHz

GSM 900 MHz: (Used in European only)

Tx: 880 ~ 915MHz

Rx: 925 ~ 960MHz

DCS 1800 MHz: (Used in European only)

Tx: 1710-1785MHz

Rx: 1805-1880MHz

BLUETOOTH:

2402MHz to 2480MHz

Dimensions (L*W*D) 116mm×51mm×13.5mm

Working temperature -20 ~ +55°C

Storage temperature -30 ~ +60°C

Relative humidity 5% ~ 95%

Tx Output Power

Channel bandwidth 1.23MHz(CDMA)

Battery capacity 1100mAh

23±2dBm Max (CDMA)

33±2dBm Max(GSM)

29±2dBm Max(DCS)

-6~+4dBm(BT)

200kHz(GSM)

Page 3 of 13

Page 4

Page 4 of 13

Page 5

3.2. Electronic specifications

Tx unit

GSM:

Item Description Marks

Frequency band GSM: 880~ 915MHz

Output power

Channel bandwidth 200kHz

Modulation GMSK/QPSK

CDMA:

Item Description Marks

Frequency band Tx:824 ~ 849MHz

Output power

Channel bandwidth 1.23MHz

Modulation OQPSK

Rx unit

GSM:

Item Description Marks

DCS: 1710-1785MHz

GSM: 33±2dBm

DCS: 29±2dBm

23±2dBm Max

Frequency band GSM: 925~ 960MHz

DCS: 1805-1880MHz

Receiver sensitivity

Phase Error Peak

Phase Error RMS

Frequency Error

–102dBm (Class II

FER<2.44%)

-20°-- +20°

≤5°

GSM: ±90Hz

DCS: ±180Hz

Page 5 of 13

Page 6

CDMA:

Item Content Comment

Frequency band

CELL:869~ 894MHz

Channel bandwidth 1.23MHz

Receiver sensitivity < –104dBm (FER:0.5%)

Single Frequency

< –101dBm (FER: 1.0%) Frequency

Interference Resist

Inter-modulation

spurious response

attenuation

Frequency offset: ±0.9MHz/±1.7MHz, Power: ① -

43dBm

Frequency offset: ±0.9MHz/±1.7MHz, Power: ② -

32dBm

Frequency offset: ±0.9MHz/±1.7MHz, Power: ③ -

21dBm

<① –81dBm Conductibility

spurious emission

<② –61dBm

3.3. Other Electronic Specifications

SIM / UIM interface, Support either 3V or 1.8V

4. Phone Work Principles

offset: 900KHz

Power: -30dBm

4.1 RF circuit

4.1.1 RF circuit of CDMA

4.1.1.1Main functions of RF circuit:

The baseband CDMA signal is modulated by transmitting circuit, and

then is transmitted by antenna on the bandwidth: 824MHz~849MHz;

When the receiver circuit receives the signal on 869MHz~894MHz, it is

demodulated and becomes to the forward channel baseband CDMA

signal; and at the same time, provides the constant controllable

19.2MHz frequency source.

4.1.1.2 Structure of RF circuit:

We could divide it to 4 units according to the functions: Antenna unit,

Page 6 of 13

Page 7

frequency synthesized unit, receiving unit, transmitting unit.

4.1.1.2.1 Antenna unit

This unit is composed by antenna groupware, antenna switch, diplexer

and duplexer.

This antenna groupware is the transceiver of the wireless signal that is

composed by intside antenna, and could fetch up the disadvantages

such as the low efficiency and the poor radiancy direction by the high

performance match. This phone has the antenna switch, diplexer and

duplexer. The antenna switch is used as the auto-test mechanical

switch, which is located at the RF channel and parallel connected to

the antenna to reduce the 0.47dB loss during using. When producing

and testing, it is connected to the test cable. Duplexer is used to

isolate the received and transmitted signals, which can reduce the

interference.

4.1.1.2.2 Frequency-synthesized unit

QSC6085 platform has a high integration on the frequency-synthesizing

and a flexible design project, which is composed of the following circuits:

crystal oscillator (XO) 19.2MHz, Loop filter and QSC6085 power

management. Crystal oscillator (XO) is provided to TX and RX as the

fiducially source, and also is provided to QSC6085 as the clock source

buffered and filtered by inside power management.

4.1.1.2.3 Transmitting unit

Mainly the following circuits compose this unit: Tx SAW filter, Power

amplifier, burst mode/PA-ON control circuit and high power detect

circuit. CDMA 1X signal is output from QSC6085. For transmitting the

power control correctly, QSC6085 outputs TX_AGC_ADJ PDM signal to

control the output power. PDM pulse wave can realize the plus control

beyond 85dB by RC filter circuit. The frequency of the output signal is

conversed up from analog base band signal to 824MHz-849MHz mixed

by UHF_LO. Output signal go through TX SAW filter (836.5MHz+/-

12.5MHz) to power amplifier, and then output to duplexer. The duplexer

has 55dB isolation to the receiver unit.

4.1.1.2.4Receiving unit

The duplexer gets the 869MHz-894MHz signals received from the

antenna. To the transmitting loop, the duplexer has 56dB isolation, and

the insertion loss of the duplexer is 2.2dB. After entering the integrated

low noise amplifier embedded in QSC6085 chip, the low noise amplifier

has gain switch function, when there are stronger interfering signals

coming in the received band, the gain will be reduced, which will

Page 7 of 13

Page 8

weaken distortion generated by inferior processes. When the received

signal is lower than -85dBm, LNA processes the high gain control, at

the same time, QSC6085 controls LNA current offset and gain

compensation of QSC chip. LNA outputs to RX SAW filter and restrains

the 40dB transmitted signal and out-of-band signal. The bandwidth of

the filter is 25MHz, and the frequency range is 881.5+/-12.5MHz, then

output to QSC6085. QSC6085 supports zero intermediate frequency

technology, which can converse the frequency down to base band

signal directly, and then generates two analog signals ( I and Q) to enter

QSC6085 chip for advanced demodulation.

4.1.2 RF circuit of GSM

4.1.2.1 Main functions of RF circuit:

The baseband modulate the uplink baseband GSM signal, and then

transmit it on 885MHz--915MHz carrier by the antenna; Demodulate the

received wireless signal transmitted by the base station on 925MHz925MHz carriers by the receiving circuit and get the forward

channel GSM signal; at the same time, provide the steady en-control

13MHz frequency source.

4.1.2.2 Structure of RF circuit:

We can divide it to 4 units according to the functions: Antenna unit,

frequency synthesized unit, receiving unit, transmitting unit.

4.1.2.2.1 Antenna unit

Composed by antenna groupware, antenna switch and diplexer. This

antenna groupware is the transceiver of the wireless signal that is

composed by inside antenna, and could fetch up the disadvantages

such as the low efficiency and the poor radiance direction by the high

performance match. This phone has the antenna switch and diplexer.

The antenna switch is used as the auto-test mechanical switch, which is

located at the RF channel and parallel connected to the antenna. When

producing and testing, it is connected to the test cable. Diplexer is used

to isolate the received and transmitted signals, which can reduce the

interference.

4.1.2.2.2 Frequency-synthesized unit

Page 8 of 13

Page 9

EG59 uses MT6139 as RF transceiver. MT6139 is a highly-integrated

RF transceiver IC for GSM850/GSM900/DCS1800 bands. It includes 4

LNAs, 2 RF quadrature mixers, a channel filter, a programmable-gain

amplifier for the receiver, a high-precision I/Q modulator for the

transmitter, a 26MHz VCXO reference, a fractional-N frequency

synthesizer with a fully-integrated LC-tank VCO and 3 built-in LDO

regulators for VCO, VCXO and SDM. Its functional block diagram is

shown as below.

The MT6139 includes a Phase-Locked Loop (PLL)-based fractional-N

frequency synthesizer with a fully-integrated LC-tank VCO. It provides

the Local Oscillator (LO) signals for both receiver and transmitter. In

order to reduce the inherent spurs caused by the fractional-N

synthesizer, a 3rd-order sigma-delta modulator with a dithering function

is used to generate the division number N for the prescaler. The

prescaler is composed of a high-frequency divided-by-2 circuit and a

multi-modulus frequency divider with the programmable division number

ranging from 32 to 127. A conventional digital-type Phase-Frequency

Detector (PFD) with a charge pump is used for phase comparison.

4.1.2.2.3. Transmitting unit

MT6139 transmitter adopts the direct-conversion architecture with

higher integration level and simpler frequency plan. It consists of

BaseBand (BB) I/Q filters, I/Q modulators, frequency dividers, output

buffers and a bias-core circuit. BB I/Q differential signals from the BB

chip are fed into the one-pole RC low-pass filter first for better out-ofthe-band noise performance. The 3-dB frequency corner is allocated at

700kHz. Two double balanced mixers (modulators), one for I+/I- and

another for Q+/A- signals, are responsible for translating the filtered BB

I/Q signals to the transmitting frequencies. LO signals are provided by

the divided-by-2 (DCS1800) and divided-by-4 (GSM850/GSM900)

dividers. The output buffers amplify the modulator output signals to an

adequate level to fulfill P-in requirement of Power Amplifier (PA). At last,

the on-chip balun is used to convert the differential signals to singleended output signal.

4.1.2.2.4. Receiving unit

The receiver section includes Quad-Band Low-Noise Amplifiers (LNAs),

RF quadrature mixers, channel filters, Programmable-Gain Amplifiers

(PGAs), and on-chip automatic DC-offset correction loops. The

differential inputs are matched to SAW filters using LC networks and the

H/L gain step is 36dB. Following the LNAs are two quadrature RF

mixers that down-convert the RF signal to IF I/Q signals. The LO signals

Page 9 of 13

Page 10

for mixers are generated by VCO divided-by-2 (DCS1800) and dividedby-4 (GSM850/GSM900). The IF I/Q signals are then filtered and

amplified through a low-pass filter and a PGA. The overall channenl

response composes of an anti-blocking low-pass filter with f3dB =

1.5MHz at mixer differential load and a 5th-order Butterworth low-pass

filter with f3dB = 135kHz. The multi-stage PGA is implemented between

filtering staged to control the gain of the receiver. With a 2dB gain step,

a 60dB dynamic range of the PGA ensures a proper signal level for

baseband setting requirement. Two DC-Offset Corretion (DCOC) loops

ensure that the residual static DC-offset voltage held digitally is less

than 200mV at maxium gain case. DC-offset correction is performed

every time the receiver gain is programmed even in the multislot mode.

4.2. Digital base band circuit principle

4.2.1 General

The digital base band circuit is composed by central control and data

processing unit, power management unit, voice processing unit, display

unit and outside interface unit.

4.2.2 The circuit and principle of each unit

4.2.2.1 Central control and data processing unit

QSC6085 is a single chip integrated multiple processors on-chip. The

baseband circuits and system software incorporates a low-power, highperformance reduced instruction set chip (RISC) microprocessor core

featuring the ARM926EJ-S™ CPU and Jazelle™ accelerator circuit

from ARM® Limited. There are two low-power, high-performance

QDSP4000™ digital signal processor (DSP) cores, one for the modem

and one for applications.

The QSC6085 is High tier device (153.6kbps data, dual memory bus)

within the family of QUALCOMM single chips. It support all the usual

digital signal processing and software functions, eg : processors,

memory support, video, audio, BREW, security, JTAG. At the same time,

The keypad (and its backlighting), USB, UARTs, RUIM, speakers,

microphones, LCD (and its backlighting), vibration motor are also

supported.

Page 10 of 13

Page 11

The baseband function reduces part costs by using two external bus

interfaces to support next-generation memory architectures, such as

NAND FLASH, SRAM and pseudo SRAM (PSRAM), page and burst

mode NOR or MLC NOR FLASH, and low-power SDRAM (LP-SDRAM).

The EBI2 also serves as an enhanced LCD interface.

Audio support supplements the analog/RF function’s CODEC, including

MP3 decoding,AAC and AAC+ devices, a Compact Media

Extension™ (CMX™)/MIDI synthesizer, and QCELP®.

The CDMA air interfaces are implemented on the baseband CDMA

processor. All necessary interfaces to the RF functions are provided,

some using a portion of the 57 GPIOs. Many of the AMSS-configurable

GPIOs are available for alternate uses as desired by the wireless

product designers.

Support circuitry and baseband internal functions include security, clock

generation and distribution, JTAG/embedded trace macrocell (ETM) test

interfaces, mode and reset controls, and the Q-fuse.

QCT provides a complete software suite — Advanced Mobile

Subscriber Software™(AMSS™) — for building handsets around the

QSC6085 device.

The GSM platform is MT6223D.It performed as the Modem.QSC6085

communicate with MT6223D by UART.

4.2.2.2 External Memory

CDMA: 256M Byte NAND FLASH + 128M Byte DDR

GSM: 64M bit NOR FLASH + 32M bit pSRAM

4.2.2.3 Power circuit

The input power management portion of its block accepts power from

common sources —the main battery or an external charger — and

generates all the regulated voltages needed to power the appropriate

handset electronics. It monitors and controls the power sources

detecting which sources are applied, verifying that they are within

acceptable operational limits, and coordinates battery and coin cell

recharging while maintaining the handset electronics supply voltages.

On-chip voltage regulators generate ten programmable output voltages

using one switched-mode power supply and nine low dropout voltage

regulators, all derived from a common trimmed voltage reference.

Page 11 of 13

Page 12

The PM general housekeeping functions include an analog multiplexer

that has several internal and external connections. The internal

connections are used to monitor on-chip functions, such as the

temperature sensor and reference voltage. Six external connections are

hardwired to access input power nodes, such as VCHG, VBAT, etc.

And finally, two multipurpose pins can be configured as analog inputs

and routed to the multiplexer through a switch matrix. These are

available to monitor system parameters such as temperatures, battery

ID, or transmit power level. The multiplexer output signal's offset and

gain is adjusted, then buffered and routed to the analog/RF circuits for

analog-to-digital conversion.

Various oscillator, clock, and counter circuits are provided to initialize

and maintain valid pulse waveforms and measure time intervals for

higher-level handset functions. A dedicated controller manages the

TCXO warm-up and signal buffering, and key parameters are monitored

to protect against detrimental conditions. A new and improved search

and acquisition algorithm eliminates the need for a VCTCXO (typically

±2.5 ppm) allowing a less expensive 19.2 MHz crystal (typically ±12

ppm, max load capacitance, 7 pF) to be used.

Handset-level user interfaces are also supported. The PM block

includes two backlight or LED drivers with brightness (current) control

that are intended for keypad and LCD lighting. A vibration motor driver

alerts handset users of incoming calls, and a speaker driver with volume

control can be used for audio alerts or speakerphone and melody ringer

applications.

PM circuit interfaces include a bus used by the baseband circuits to

control and status the PM functions. This bus is supplemented by an

interrupt manager for time-critical information. Another dedicated

interface circuit monitors multiple trigger events and controls the powe

on/poweroff sequences. A universal serial bus (USB) transceiver is

included for interfacing the baseband circuits to computers as a USB

1.1 peripheral.

4.2.2.4 LCD

We use 320*240 dot matrix 262k color TFT LCD display module, with

touch panel support.

4.2.2.5 Camera Module

We use 2.0 mega camera module with OV CMOS sensor.

Page 12 of 13

Page 13

4.2.2.6 Bluetooth

We use Qualcomm BTS4025 as main Bluetooth transceiver IC which

supporting voice and data communication function. Its working mode

or state is controlled by QSC6085 via UART inferface. The PCM voice

siganal interfacing with BTS4025 is processed by QSC6085 directly.The

MT6223D analogy signal was transferred via the CODEC of QSC6085 .

And BTS4025 needs a external 32MHz crystal as clock source and use

the QSC6085’S LDO as power source.

Page 13 of 13

Loading...

Loading...