HEI HV7121B Datasheet

HV7121B

CMOS IMAGE SENSOR

With 8-bit ADC

Electronics Industries Co., Ltd.

System IC Division

DESCRIPTION

HV7121B is a highly integrated single chip CMOS color image sensor using Hyundai 0.5um CMOS process

developed for image application to realize high efficiency R/G/B photo sensor. The sensor has 414X314 pixels

total, and 400X300 pixels effective. Each pixel is high photo sensitive, small size active pixel element that

converts photons to analog voltage signal. The sensor has three on-chip 8 bit Digital to Analog Convert (DAC)

and 414 comparators to digitize the pixel output. The three on-chip 8 bit DAC can be used for independent

R/G/B gain control. Hyundai proprietary on-chip CDS circuit can reduce Fixed Pattern Noise (FPN)

dramatically. The whole 8 bit digital color raw data is directly available on the package pins and just few

control signals are needed for whole chip control, so it is very ease to configure a system using the sensor.

FEATURES

l 400 x 300 pixels resolution l Full function control through standard I2C bus

l 8um x 8um square pixels l Built-in AGC

l High efficiency R/G/B color photo sensors l 48Pin CLCC / 20Pin CDIP

l Integrated 8-bit ADC for direct digital output l Bayer RGB color pattern

l Low power 3.3V operation (5V tolerant I/O) l Anti-blooming circuit

l Integrated pan control and window sizing l Flexible exposure time control

l Clock speed up to 15MHz l Integrated on-chip timing and drive control

l Programmable frame rate and synchronous

l 1/4" optical format

format

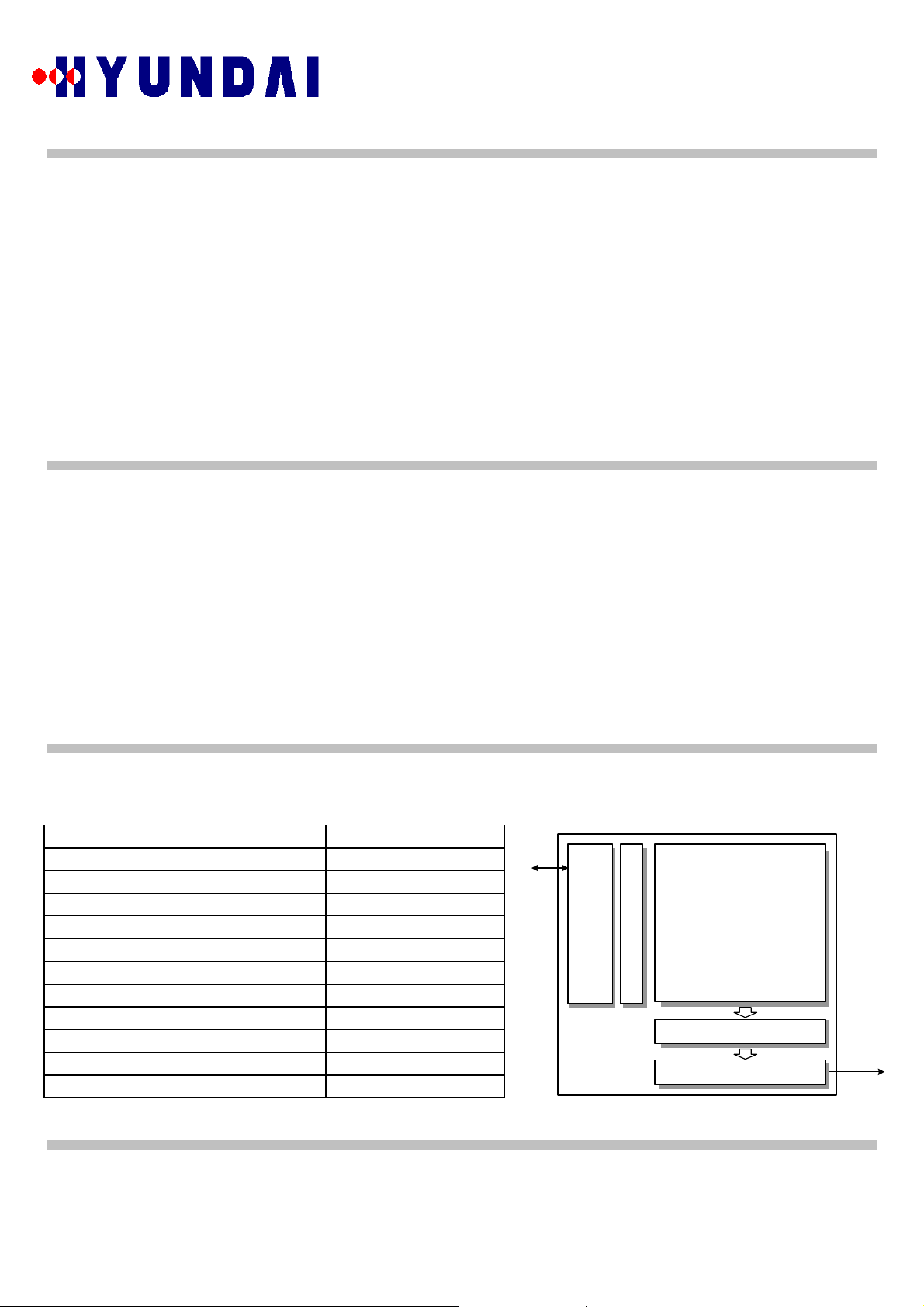

TECHNICAL SPECIFICATION FUNCTIONAL BLOCK DIAGRAM

Pixel resolution 402x302

Pixel size 8x8um

2

Fill factor 30%

Format CIF

Sensitivity TBD

S/R TBD

Supply voltage for analog 3.3V

Supply voltage for digital 3.3V

Supply voltage for 5V tolerant input 5.0V

Supply current

Operating temperature 0~40 C

Technology 0.5um 3metal CMOS

I2C

Control

Register

& Logic

Pixel

Array

Decoder/Pixel Driver

ADC Block

Line Buffer

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. NO patent licenses are implied.

DA41990615R_1.0 1 1999 Hyundai System IC Division

HV7121B

CMOS IMAGE SENSOR

With 8-bit ADC

Electronics Industries Co., Ltd.

System IC Division

ELECTRICAL CHARACTERISTIC

Absolute Maximum Ratings

l Supply voltage(Analog, Digital) : 3.0 V ~ 3.6 V

l Voltage on any input pins : 0 V ~ 5.0 V

l Operating Temperature : 0¡É ~ 40¡É

Note : Input pins are 5V tolerant. Stresses exceeding the absolute maximum ratings may induce failure.

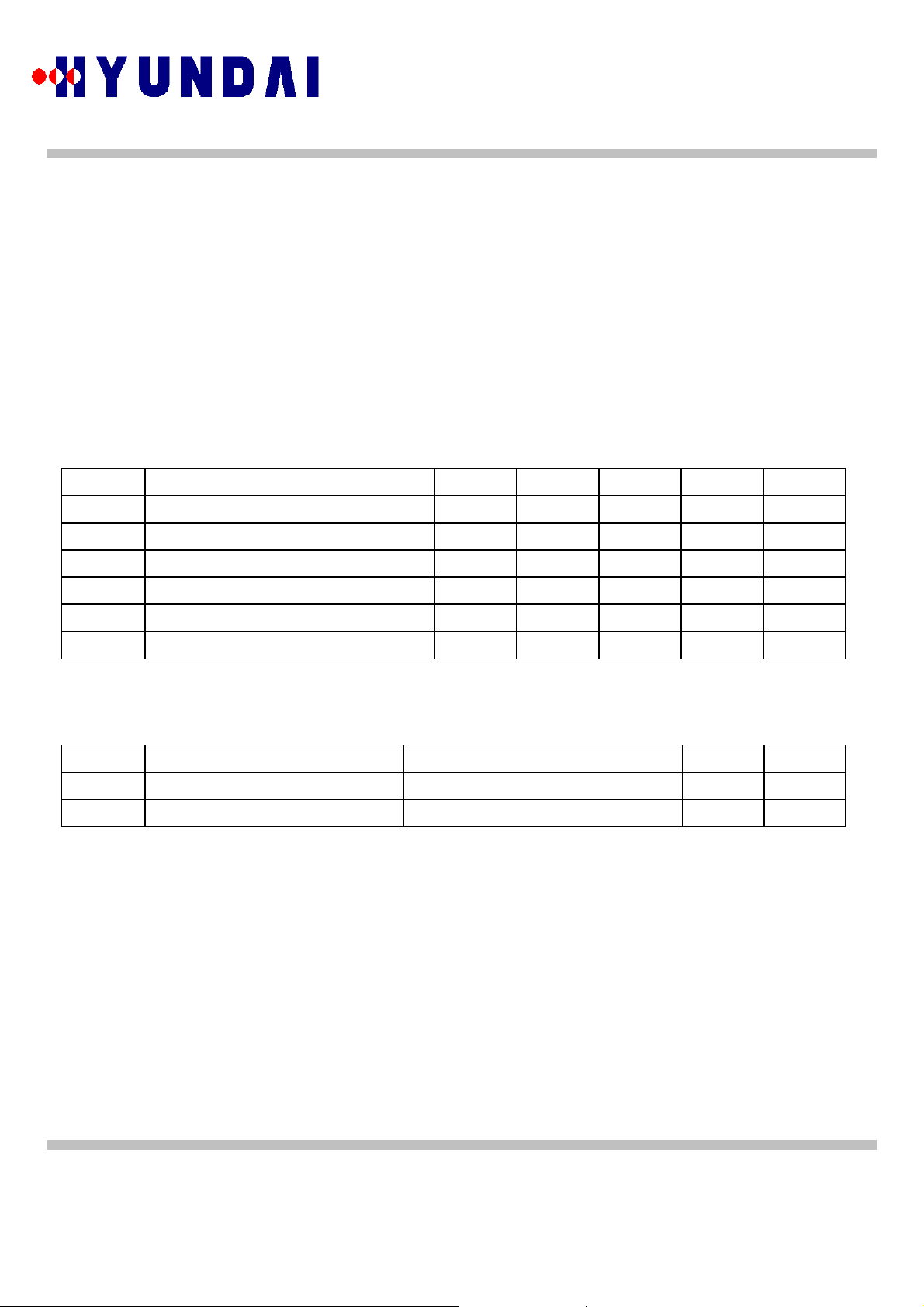

DC Operating Conditions

Symbol Parameter Units Min. Max. Load[pF] Notes

V

dd

V

ih

V

il

V

oh

V

ol

T

a

Internal operation supply voltage Volt 3.0 3.6

Input voltage logic "1" Volt 2.0 5 6.5

Input voltage logic "0" Volt 0 0.8 6.5

Output voltage logic "1" Volt 2.15 3.6 60

Output voltage logic "0" Volt 0.4 0.4 60

Ambient operating temperature Celsius 0 40

AC Operating Conditions

Symbol Parameter Max Operation Frequency Units Notes

MCLK Main clock frequency 20 MHz 1

SCK I2C clock frequency 400 kHz 2

1. MCLK can be divided according to Clock Divide Register for internal clock.

2. SCK is driven by host processor. For the detail serial bus timing, refer to I

2

C Spec.

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. NO patent licenses are implied.

DA41990615R_1.0 2 1999 Hyundai System IC Division

Electronics Industries Co., Ltd.

CMOS IMAGE SENSOR

With 8-bit ADC

System IC Division

ELECTRO-OPTICAL CHARACTERISTICS

Parameter Units Min. Typical Max. Note

Sensitivity mV / lux sec TBD TBD TBD 1)

HV7121B

Dark Signal mV TBD

Output Saturation Signal mV TBD TBD TBD 3)

Blooming % TBD

Dynamic Range dB TBD TBD 4)

Shading TBD 5)

Fixed Pattern Noise % TBD 6)

Note:

1) Measured at 26 [1ux] illumination for exposure time 10 [msec]

2) Measured at zero illumination for exposure time 48 [msec] (Ta = 25 C)

3) Measured at Vdd =3.3V

4) 48dB is limited by 8-bit ADC

5) Variation in individual pixel response over entire sensor area

6) Measured at zero [lux] and 70 [lux] illumination for exposure time 10 [msec] Variation of average

pixel response from column(i) to column(i+2) and from row(i) to raw(i+2) due to Bayer Pattern RGB

sampling.

TBD

2)

Remarks : Master Clock = 15MHz

*All values are measured by raw image data from image sensor.

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. NO patent licenses are implied.

DA41990615R_1.0 3 1999 Hyundai System IC Division

HV7121B

CMOS IMAGE SENSOR

With 8-bit ADC

MCLK

Electronics Industries Co., Ltd.

System IC Division

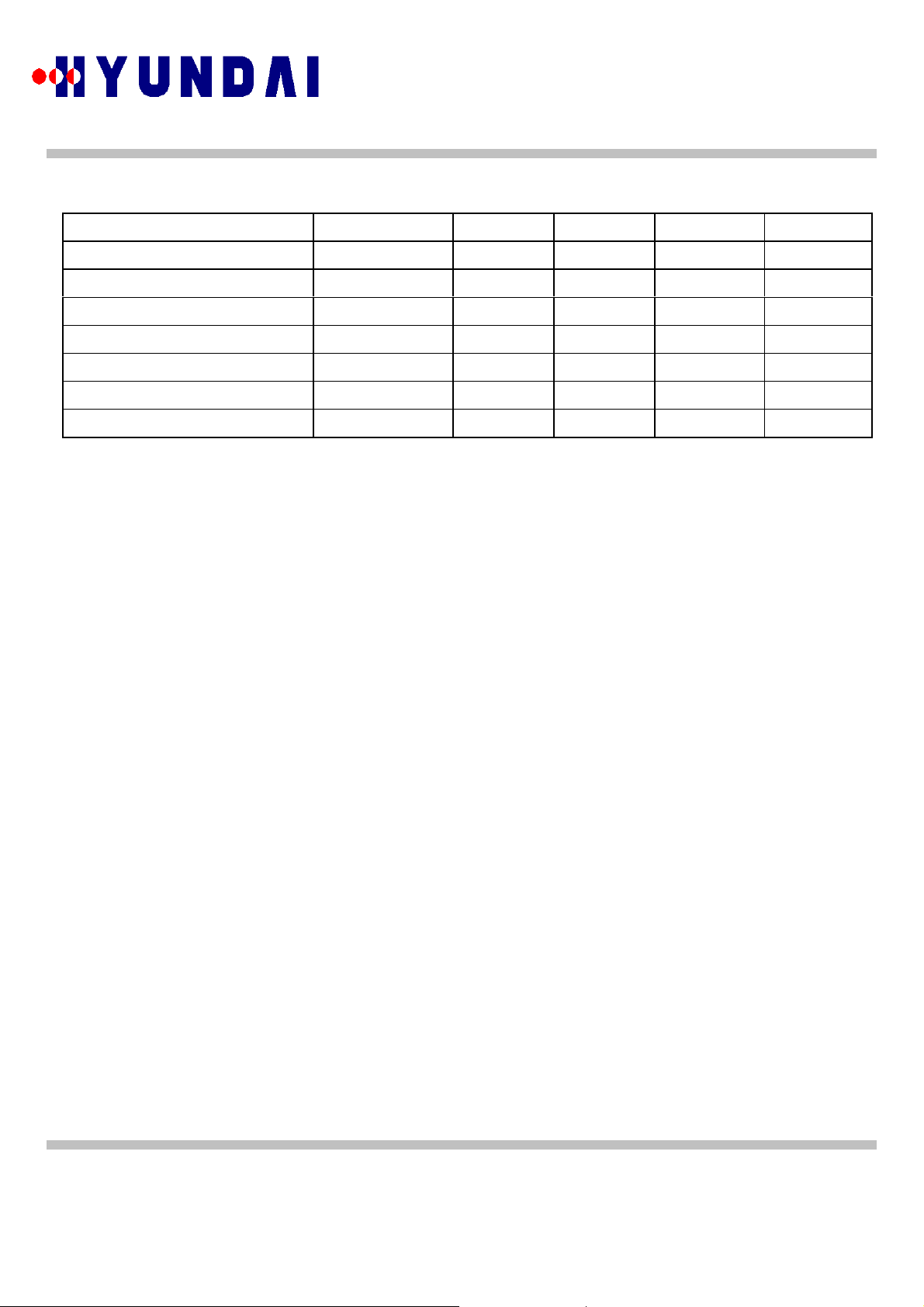

INPUT / OUTPUT AC CHARACTERISTICS

l All output timing delays are measured with output load 60[pF].

l Output delay include the internal clock path delay[6ns] and output driving delay that changes in

respect to the output load, the operating environment, and a board design.

l Due to the variable valid time delay of the output, output signals may be latched in the negative

edge of MCLK for the stable data transfer between the image sensor and a host for less than

15MHz operation.

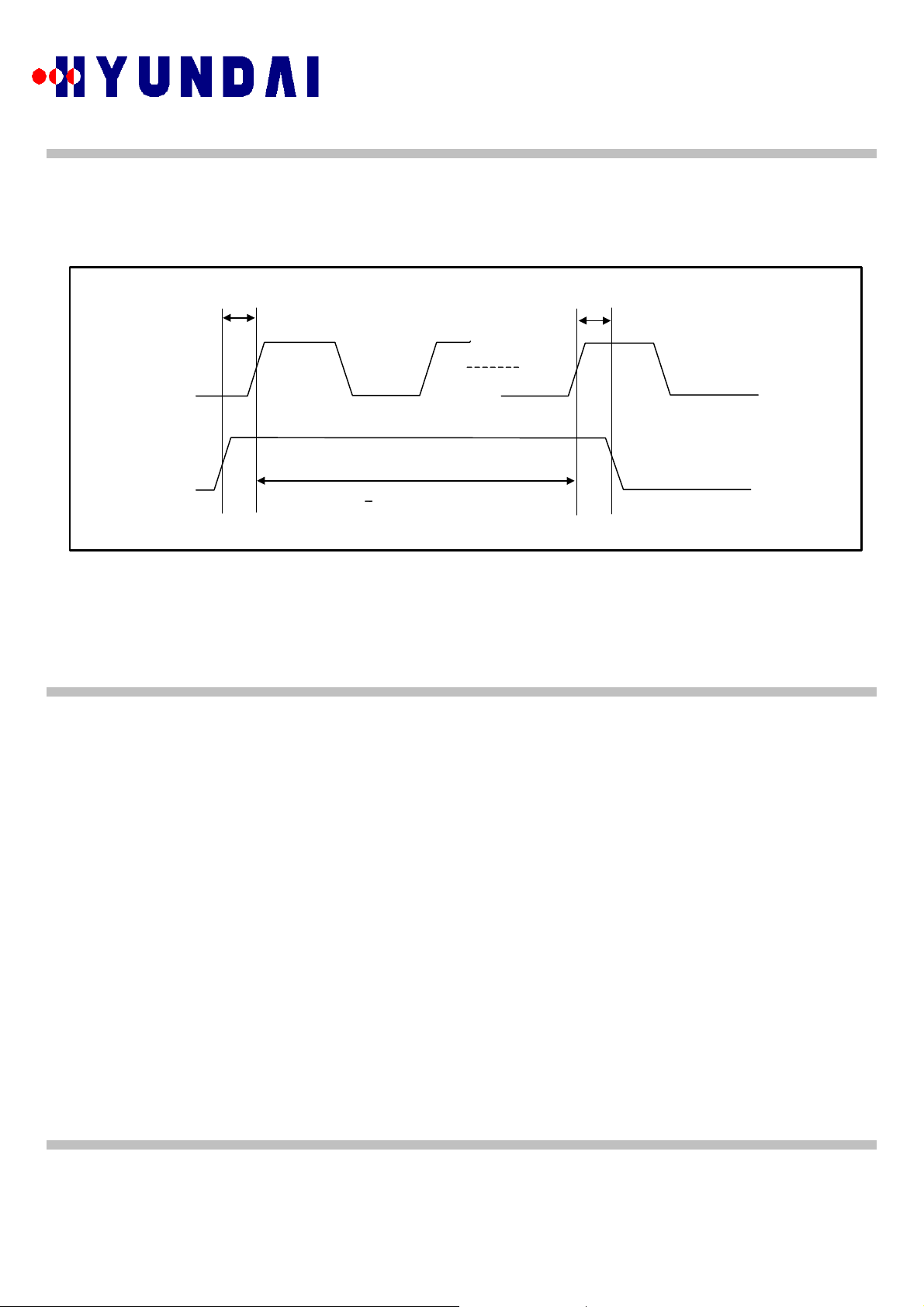

MCLK to HSYNC/VSYNC Timing

T1

MCLK

HSYNC/VSYNC

T2

T1

T1 : MCLK rising to HSYNC/VSYNC Valid maximum Time : 18ns [output load: 60pF]

T2 : HSYNC/VSYNC Valid Time : minimum 1Clock(subject to T1, T2 timing rule)

MCLK to DATA Timing

T3

DATA[7:0]

Valid DATA

T3

T3 : MCLK rising to DATA Valid maximum Time : 18ns [output load: 60pF]

Note) HSYNC signal is high when valid data is on the DATA bus.

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. NO patent licenses are implied.

DA41990615R_1.0 4 1999 Hyundai System IC Division

Electronics Industries Co., Ltd.

CMOS IMAGE SENSOR

With 8-bit ADC

System IC Division

INPUT / OUTPUT AC CHARACTERISTICS (Continue)

ENB Timing

MCLK

ENB

HV7121B

T5T4

T4 : ENB Setup Time : 5ns

T5 : ENB Hold Time : 5ns

T6 : ENB Valid Time : minimum 2 Clock

RESET Timing

Must in Valid (active LOW) state at least 8MCLK periods

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. NO patent licenses are implied.

DA41990615R_1.0 5 1999 Hyundai System IC Division

Electronics Industries Co., Ltd.

CMOS IMAGE SENSOR

With 8-bit ADC

System IC Division

INPUT / OUTPUT AC CHARACTERISTICS CONTINUE

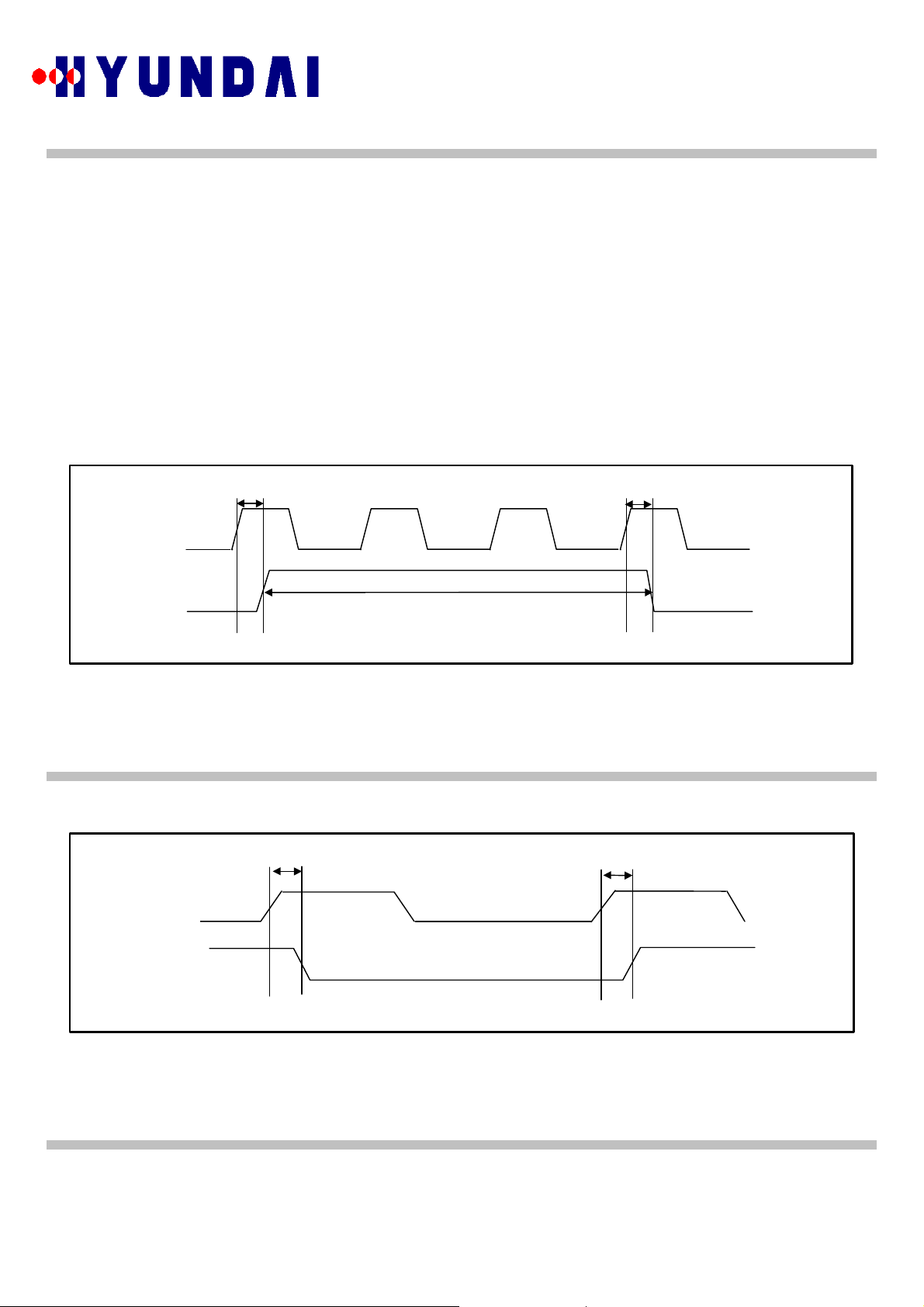

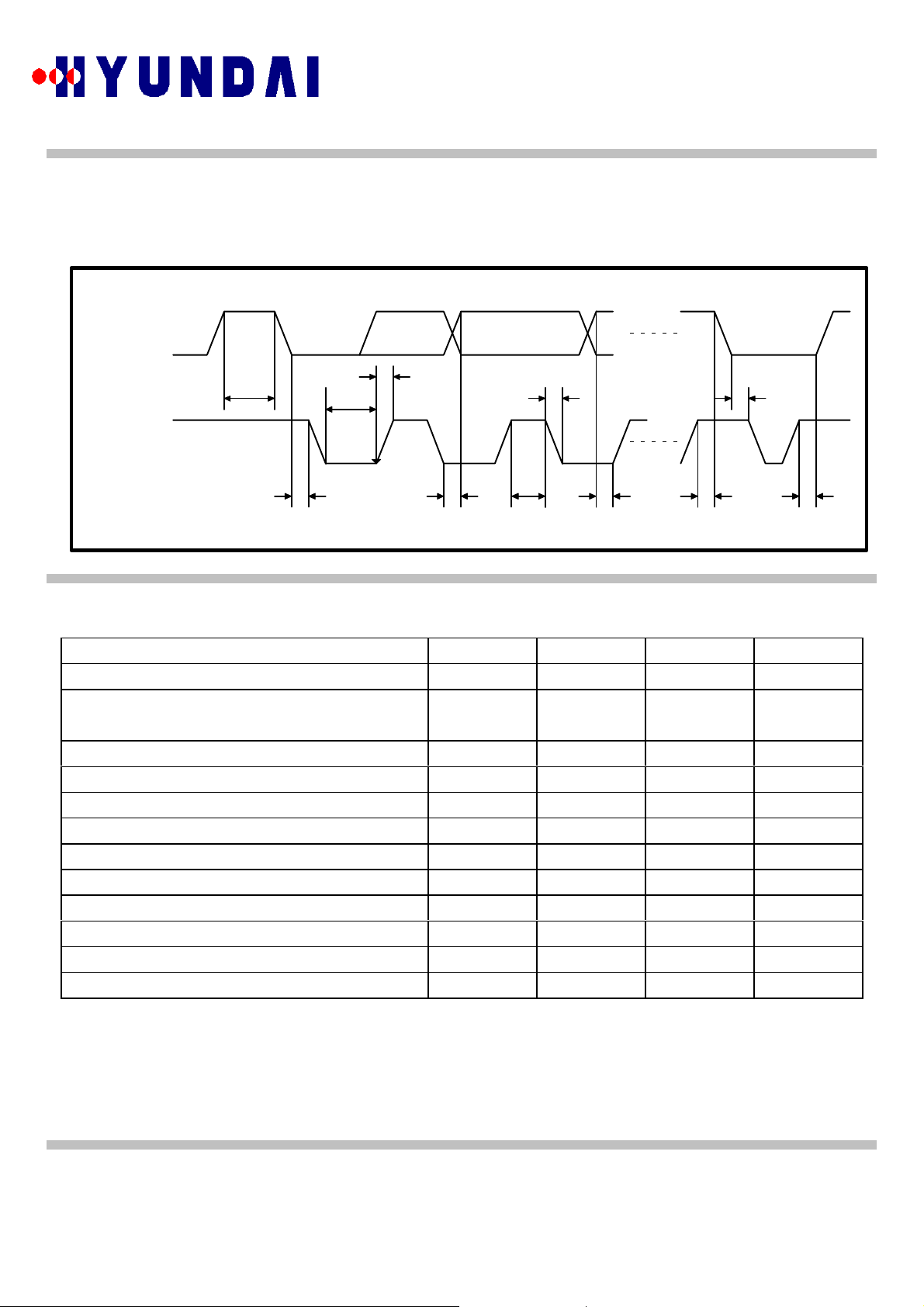

I2C Bus (Programming Serial Bus) Timing

HV7121B

stop start

SDA

tbuf

SCK

thd;sta

tlow

I2C Bus Interface Timing

Parameter Symbol Min. Max. Unit

SCK clock frequency f

Time that I2C bus must be free before a new

transmission can start

tr

tf

thd;dat thigh tsu;dat tsu;sta tsu;sto

0 400 KHz

1.2 us

t

sck

buf

thd;sta

stopstart

Hold time for a START thd;s

LOW period of SCK t

HIGH period of SCK t

Setup time for START tsu;s

Data hold time thd;d

Data setup time tsu;d

Rise time of both SDA and SCK t

Fall time of both SDA and SCK t

Setup time for STOP tsu;s

Capacitive load of each bus lines(SDA,SCK) C

ta

low

high

ta

at

at

r

f

to

b

1.0 us

1.2 us

1.0 us

1.2 us

1.3 us

250 ns

250 ns

300 ns

1.2 us

pf

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. NO patent licenses are implied.

DA41990615R_1.0 6 1999 Hyundai System IC Division

Electronics Industries Co., Ltd.

CMOS IMAGE SENSOR

With 8-bit ADC

start point

System IC Division

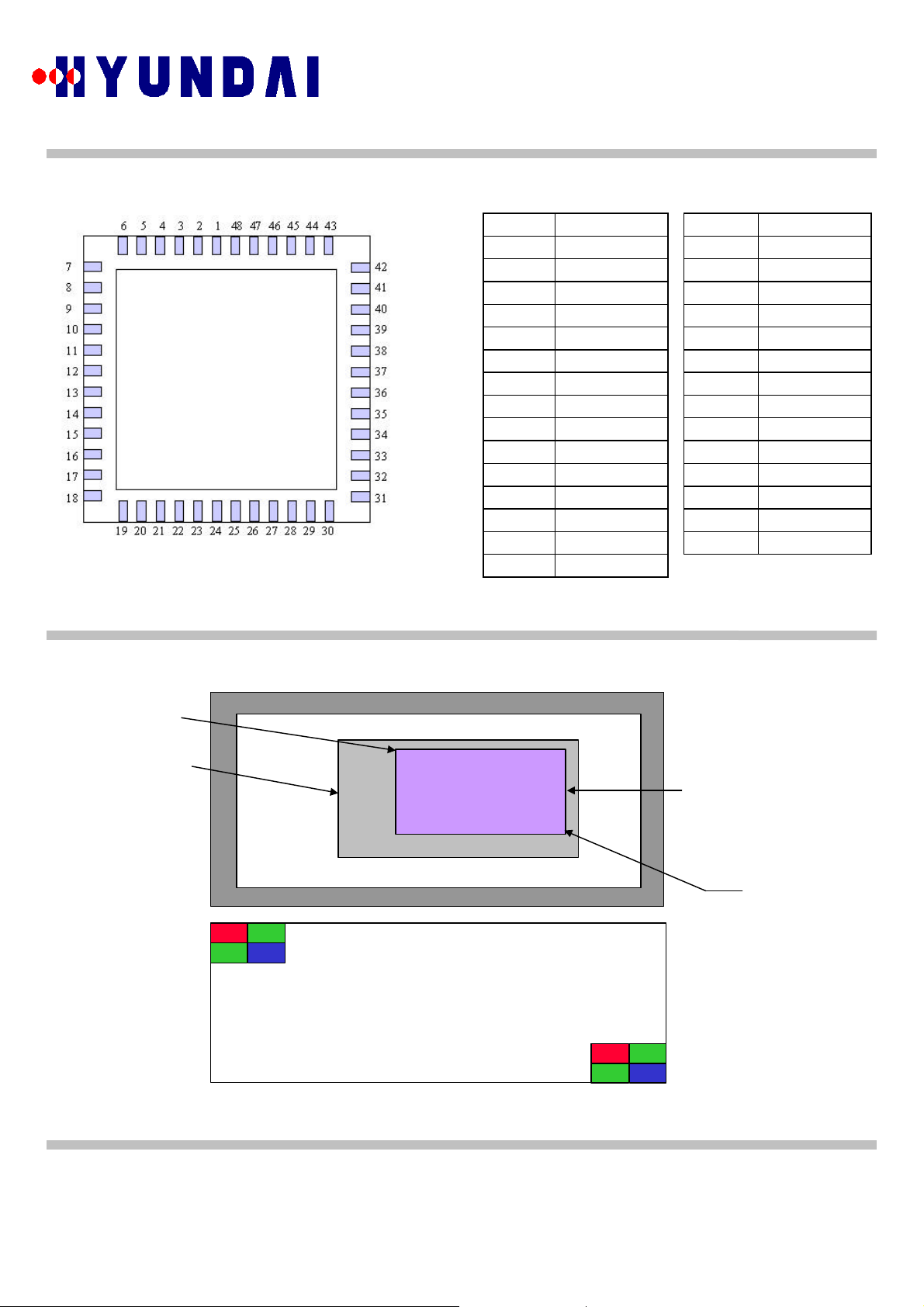

PIN CONFIGURATION (48 pin CLCC)

HV7121B

PIN NO. NAME PIN NO. NAME

1 SCK 26 DGND1

2 DGND 27 DATA3

3 ENB 28 DATA2

4 DGND 29 DATA1

5 MCLK 30 DATA0

6 VDD5 31 DVDD

7 AVDD 32 DGND1

8 AGND 42 DVDD

17 AGND 43 RESET

18 AVDD 44 VSYNC

21 DGND 45 HSYNC

22 DATA7 46 DGND

23 DATA6 47 SDA

24 DATA5 48 DGND

25 DATA4

Pin9~16, Pin19~20, Pin33~41 : No Connection

COLOR PATTERN

(413, 313)

DIE

313

312

pixel array

origin (0,0)

Read out

412

413

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. NO patent licenses are implied.

DA41990615R_1.0 7 1999 Hyundai System IC Division

1 0

Electronics Industries Co., Ltd.

CMOS IMAGE SENSOR

With 8-bit ADC

System IC Division

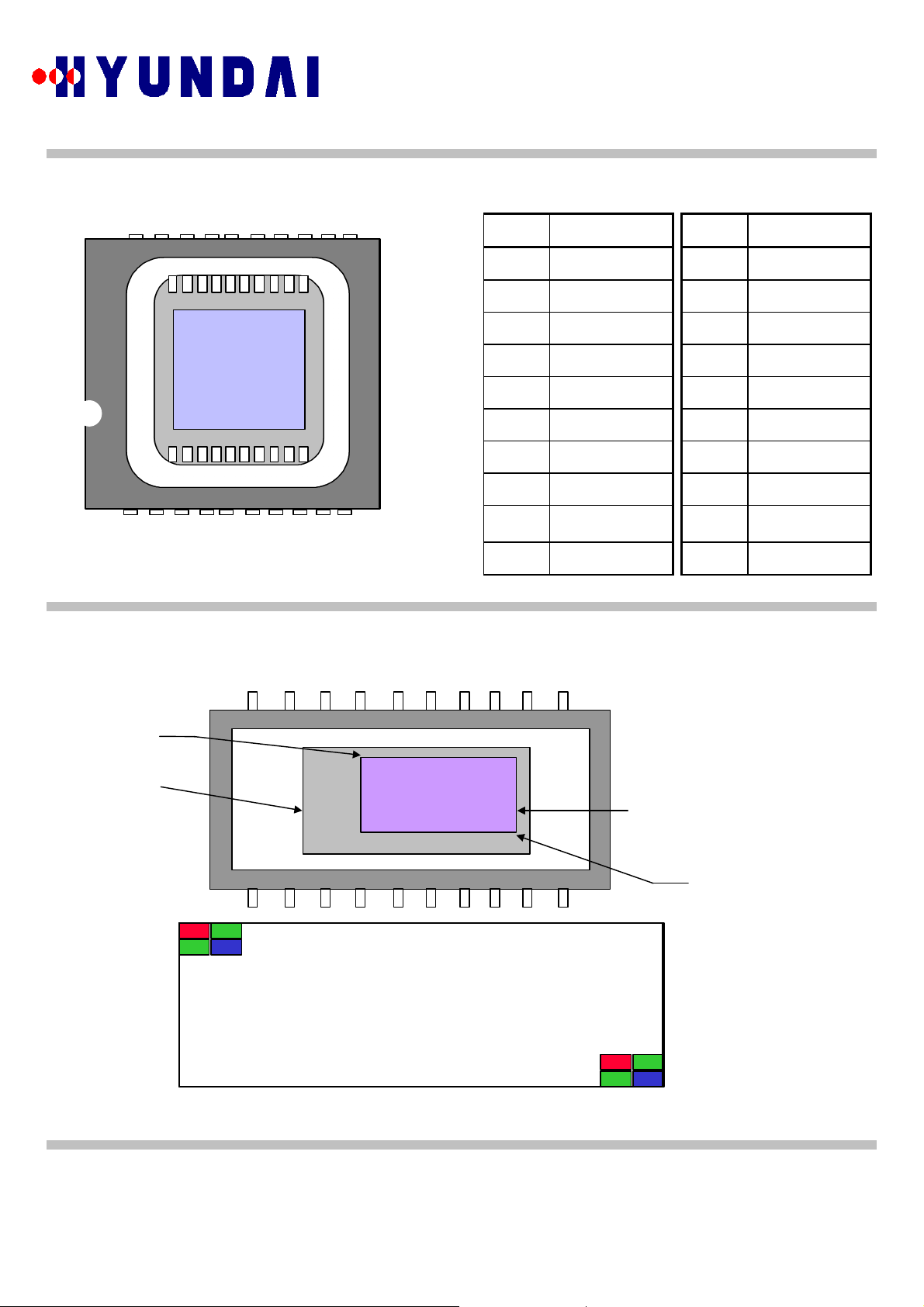

PIN CONFIGURATION (20 pin CDIP)

HV7121B

20 19 18 17 16 15 14 13 12 11

1 2 3 4 5 6 7 8 9 10

COLOR PATTERN

PIN NO. NAME PIN NO. NAME

1 AGND 11 DVDD

2 DATA 7 12 RESET

3 DATA 6 13 VSYNC

4 DATA 5 14 HSYNC/DVALID

5 DATA 4 15 SDA

6 DATA 3 16 SCK

7 DATA 2 17 ENB

8 DATA 1 18 MCLK

9 DATA 0 19

+5V Tolerant

Bias

10 DGND 20 AVDD

(413, 313)

DIE

313

312

413 412

active sensing area

origin (0,0)

Read out

1 0

Start Point

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. NO patent licenses are implied.

DA41990615R_1.0 8 1999 Hyundai System IC Division

Electronics Industries Co., Ltd.

CMOS IMAGE SENSOR

With 8-bit ADC

System IC Division

PIN DESCRIPTION (48 Pin CLCC)

HV7121B

PIN NAME I/O

1 SCK I I2C Clock ; I2C clock control from IIC master

2 DGND I Digital Ground

3 ENB I Sensor Enable Signal ; 'H' enable normal operation

'L' disable sensor by stalling internal clock

4 DGND I Digital Ground

5 MCLK I Master Clock (up to 15MHz)

; Global master clock for image sensor internal timing control

6 VDD5 I I/O bias voltage for 5V tolerant *1)

7 AVDD I Analog Supply Voltage 3.3V

8 AGND I Analog Ground

9 ~ 16 N.C No Connection

17 AGND I Analog Ground

18 AVDD I Analog Supply Voltage 3.3V

19, 20 Reserved Reserved

21 DGND I Digital Ground

22 DATA7 O Image Data bit 7

23 DATA6 O Image Data bit 6

24 DATA5 O Image Data bit 5

25 DATA4 O Image Data bit 4

26 DGND I Digital Ground

27 DATA3 O Image Data bit 3

28 DATA2 O Image Data bit 2

29 DATA1 O Image Data bit 1

30 DATA0 O Image Data bit 0

31 DVDD I Digital Supply Voltage 3.3V

32 DGND I Digital Ground

33 ~ 41 N.C No Connection

42 DVDD I Digital Supply Voltage 3.3V

43 RESET I Hardware Reset Signal, Active Low

44 VSYNC O Vertical synchronization signal / Frame start output

; Signal pulse at start of image data frame with programmable

blanking duration

45 HSYNC O Horizontal synchronization signal / Data valid output

/DVALID ; Data valid when 'H' with programmable blanking duration

46 DGND I Digital Ground

47 SDA I/O I2C Data ; I2C standard data I/O port

48 DGND I Digital Ground

DESCRIPTION

*1) Tie to DVDD for 3.3V operation / Tie to 5V for 5V tolerant operation

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. NO patent licenses are implied.

DA41990615R_1.0 9 1999 Hyundai System IC Division

Loading...

Loading...