HEI HL14203 Datasheet

H L 1 4 2 0 3

LCD Driver IC

HL14203

Preliminary

2Q. 1999

Hyundai Electronics Industries

System IC Division

1

P r e l i m i n a r y

Contents

1. General Description

2. Features

3. Block Diagram

4. Pin Diagram

5. Pin Description

6. Serial I/O Data Format

7. Registers

HL14203

8. Key Scan Function

9. LCD Function

10. Power On Reset

11. Power Down Mode

12. Oscillator Port

13. Electrical Characteristics

14. Application

2

P r e l i m i n a r y

HL14203

1. General Description

The HL14203 is 1/3 duty LCD display driver. It can drive directly maximum

126 segments. Also it has four general purpose output ports and a key scan

function that accepts input from up to 30 keys.

2. Features

• LCD display ..................................... 42 segments x 3 commons

1/3 duty - 1/2 bias

1/3 duty - 1/3 bias

• Key scan ............................................ Maximum 30 keys

Input 5 pins, Output 6 pins

• Power down mode ............................. Sleep mode and all segments off mode

• Port

Output .................................................. 4 pins

( Including the LCD segment port )

• Serial I/O .............................................. Data transfer and receive

• Power on reset ..................................... Supply voltage detection ( SVD )

• RC oscillator

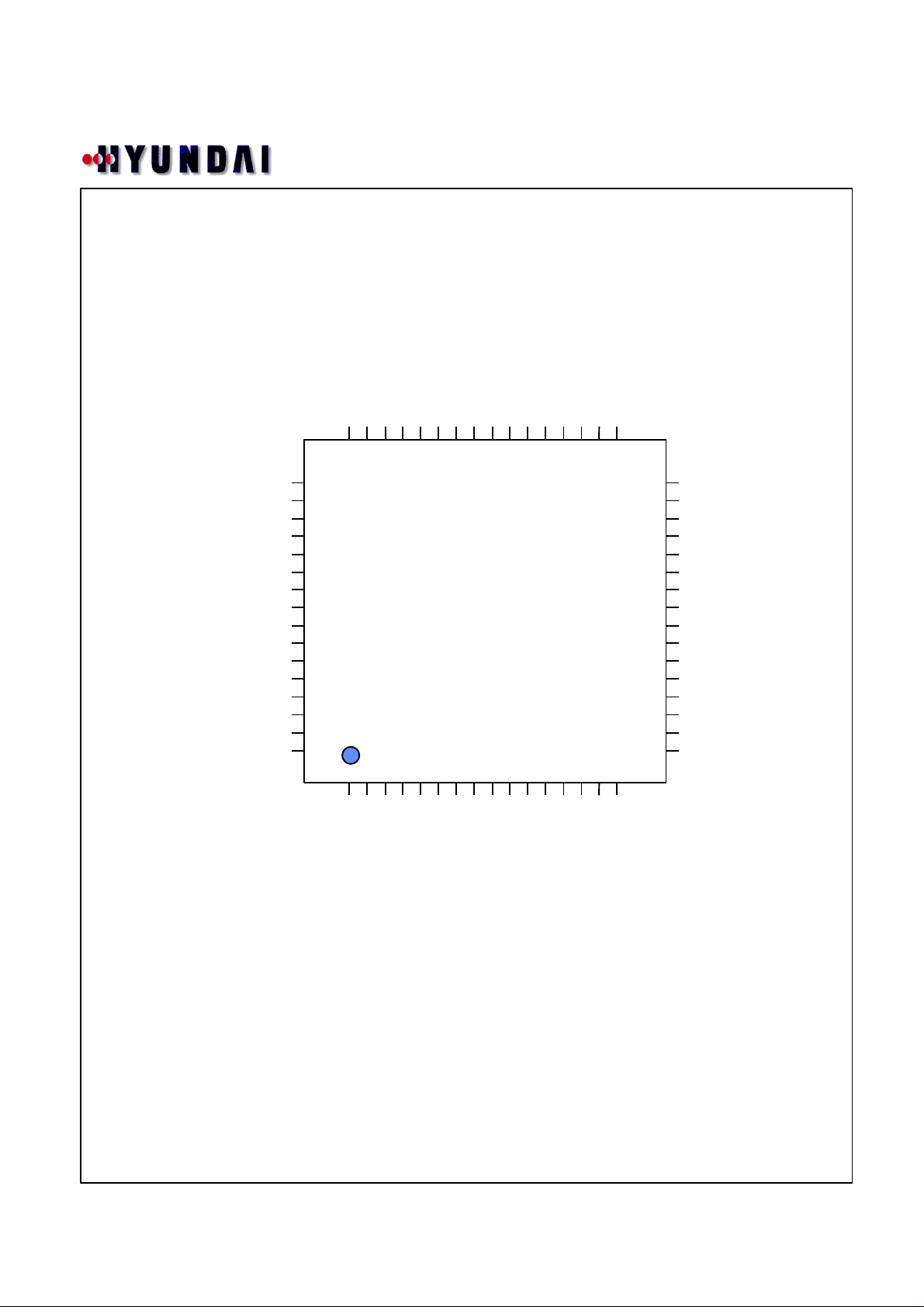

• Package ............................................... 64QFP

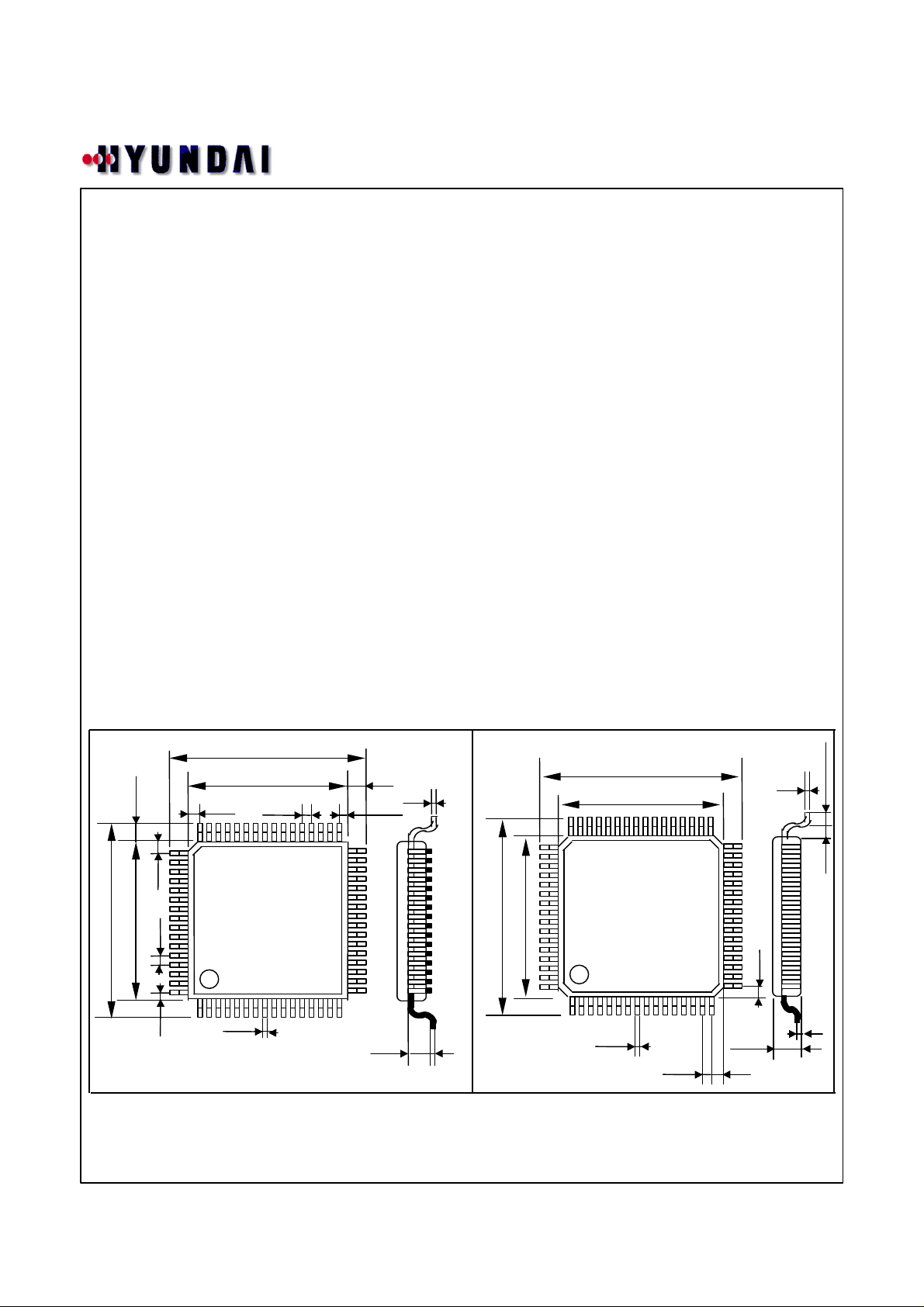

(1.6)

17.2

14.0

Unit : mm

Package Dimensions

64QFP (14×14)

17.2

14.0

1.0

0.8

1.0

48

49

64

1.0

1

0.8

0.35

16

33

32

17

(1.6)

1.0

0.15

64QFP (10×10)

12.0

10.0

48

49

12.0

10.0

64

1

0.12.7

Unit : mm

0.18

0.5

32

33

16

0.15

1.25

17

1.7max

1.25

0.5

0.5

0.1

3

P r e l i m i n a r y

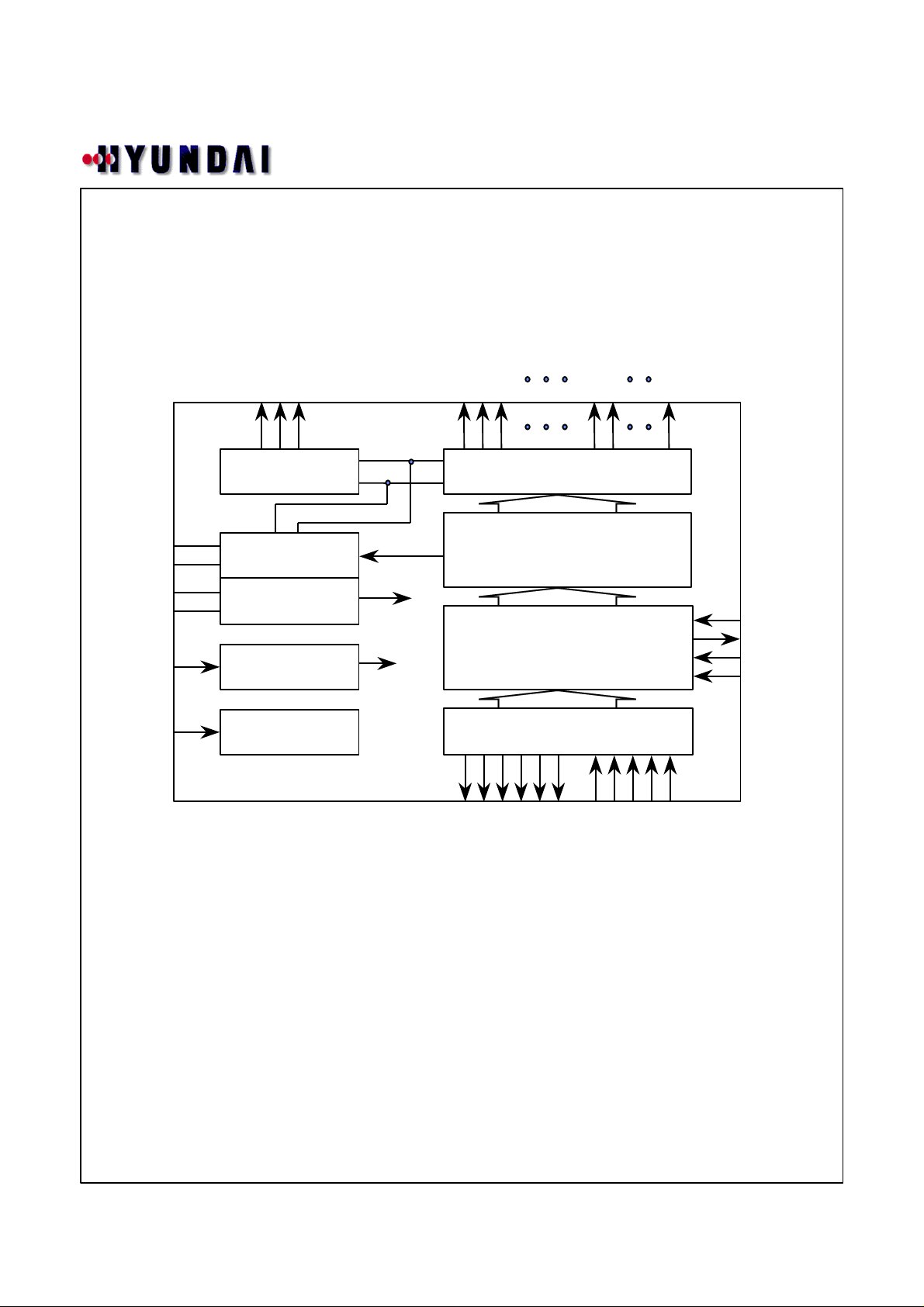

3. Block Diagram

COM3

COM2

COM1

KS2 / SEG42

KS1 / SEG41

SEG40

SEG5

SEG4 / P4

HL14203

SEG1 / P1

VCL1

VCL2

VDD

VSS

OSC

TEST

COMMOM

DRIVER

LCD

BIAS

SVD

CLOCK

GENERATOR

TEST

CONTROL

RESET

CLOCK

SEGMENT

DRIVER

LCD

DISPLAY & CONTROL

REGISTER

SERIAL

I/O

KEY

SCAN

KS6

KS5

KS4

KS3

KS2

KS1

KIN5

KIN4

KIN3

KIN2

SI

SO

SCK

CE

KIN1

4

P r e l i m i n a r y

4. Pin Diagram

KS5

KS4

KS3

KS2 / SEG42

KS1 / SEG41

COM3

COM2

COM1

SEG40

SEG39

SEG38

SEG37

SEG36

SEG35

SEG34

HL14203

SEG33

KS6

KIN1

KIN2

KIN3

KIN4

KIN5

TEST

VDD

VCL1

VCL2

VSS

OSC

SO

CE

SCK

484746454443424140393837363534

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

SI

123456789101112131415

SEG1 / P1

SEG2 / P2

HL14203

SEG5

SEG6

SEG3 / P3

SEG4 / P4

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

SEG16

SEG32

SEG31

SEG30

SEG29

SEG28

SEG27

SEG26

SEG25

SEG24

SEG23

SEG22

SEG21

SEG20

SEG19

SEG18

SEG17

5

P r e l i m i n a r y

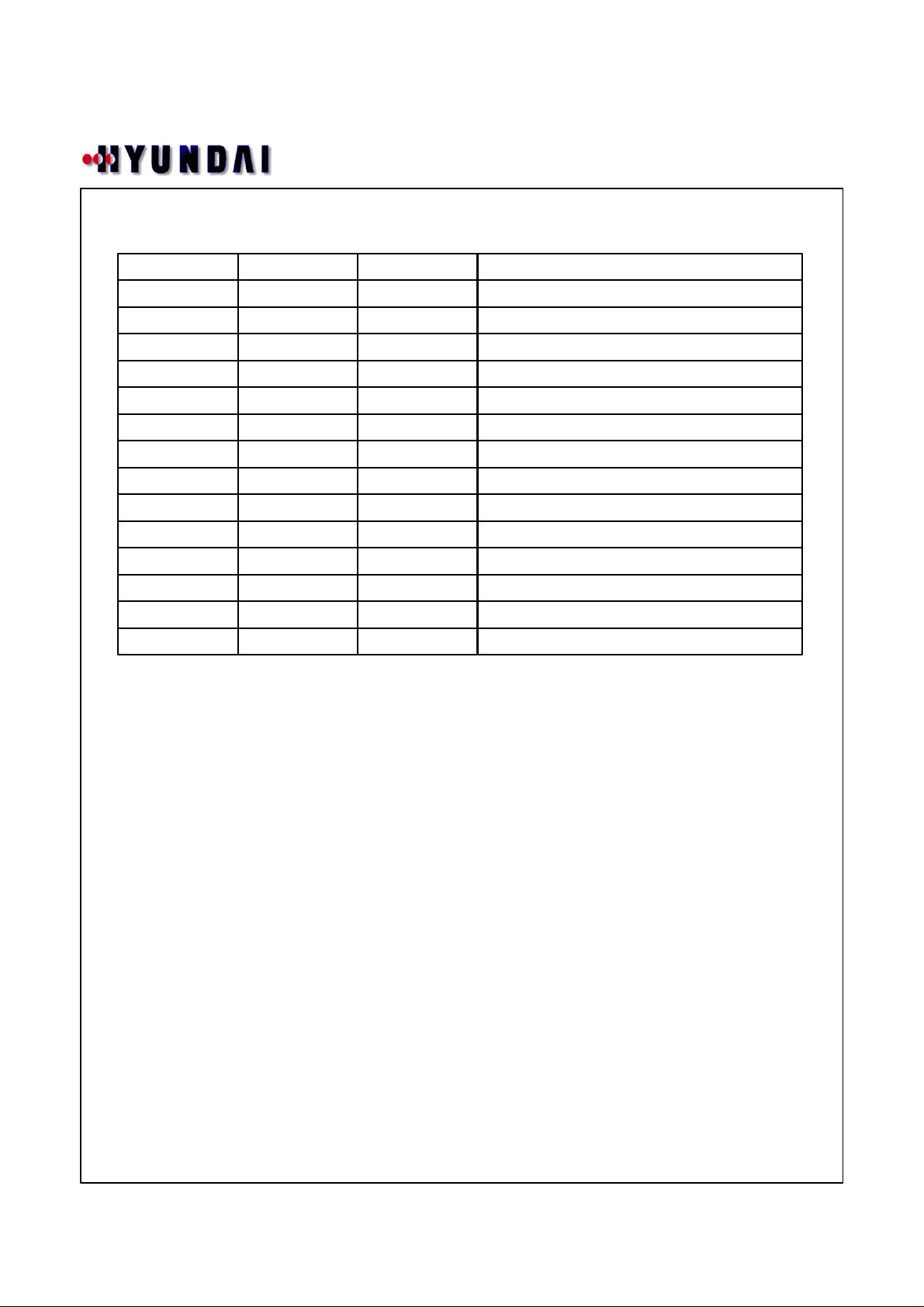

5. Pin Description

PIN Name I/O Pin Number Contents

SEG[42:1] O 42 LCD SEG Pins share P1,P2,P3 and P4

COM [3:1] O 3 LCD Common Pins

VCL[2:1] I 2 LCD Bias Pins

OSC I/O 1 Oscillator Input Pin

KS[6:1] O 6 Key Scan Output Pins

KIN[5:1] I 5 Key Scan Input Pins

CE I 1 Serial I/O Control Pin

SCK I 1 Serial I/O Clock Pin

SO O 1 Serial I/O Data Output Pin

SI I 1 Serial I/O Data Input Pin

TEST I 1 Test Pin. “1” Test mode , “0” Normal Mode

P[4:1] O 4 Output Port share SEG[4:1]

VDD I 1 Power Supply Pin

HL14203

VSS I 1 Ground Pin

6

P r e l i m i n a r y

6. Serial I/O Data Format

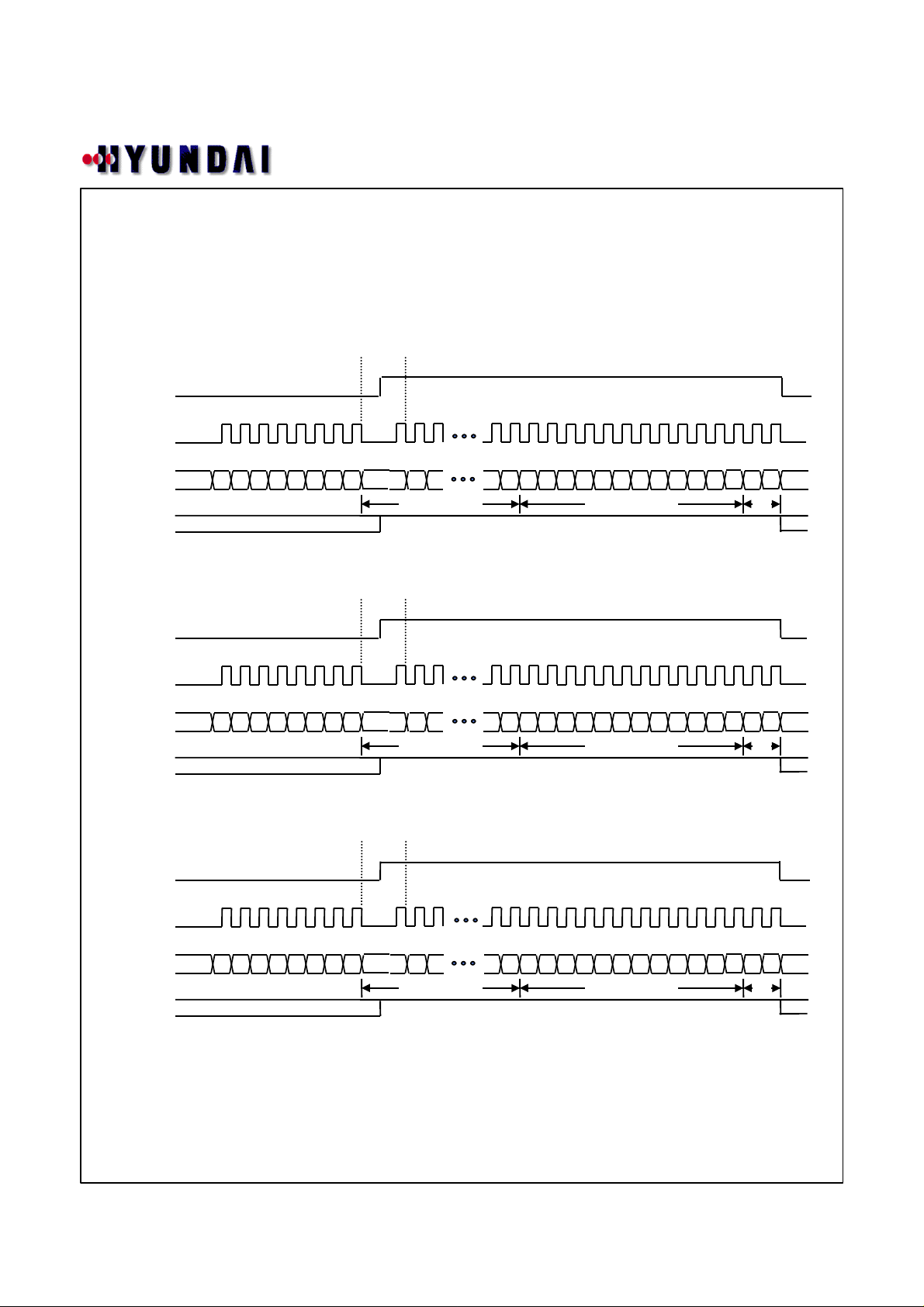

1) Writing Mode

i )SCK is stopped at the low level

CE

SCK

HL14203

SI

SO

CE

SCK

SI

SO

CE

SCK

A0 A1 A2 A3 A4 A5 A6 A7

A0 A1 A2 A3 A4 A5 A6 A7

0 1 0 0 0 0 1 0 D1 D2 D3XX

Display data

D41

D42 0 0 0 0 S0 S1 K0 K1 P0 P1 SC DR 0 0

Control data DD

0 1 0 0 0 0 1 0 D43 D44 D45XX

Display data

D83

D84 0 0 0 0 0 0 0 0 0 0 0 0 0 1

Fixed data DD

SI

SO

A0 A1 A2 A3 A4 A5 A6 A7

D125

0 1 0 0 0 0 1 0 D85 D86 D87XX

Display data

7

D126

0 0 0 0 0 0 0 0 0 0 0 0 1 0

Fixed data DD

P r e l i m i n a r y

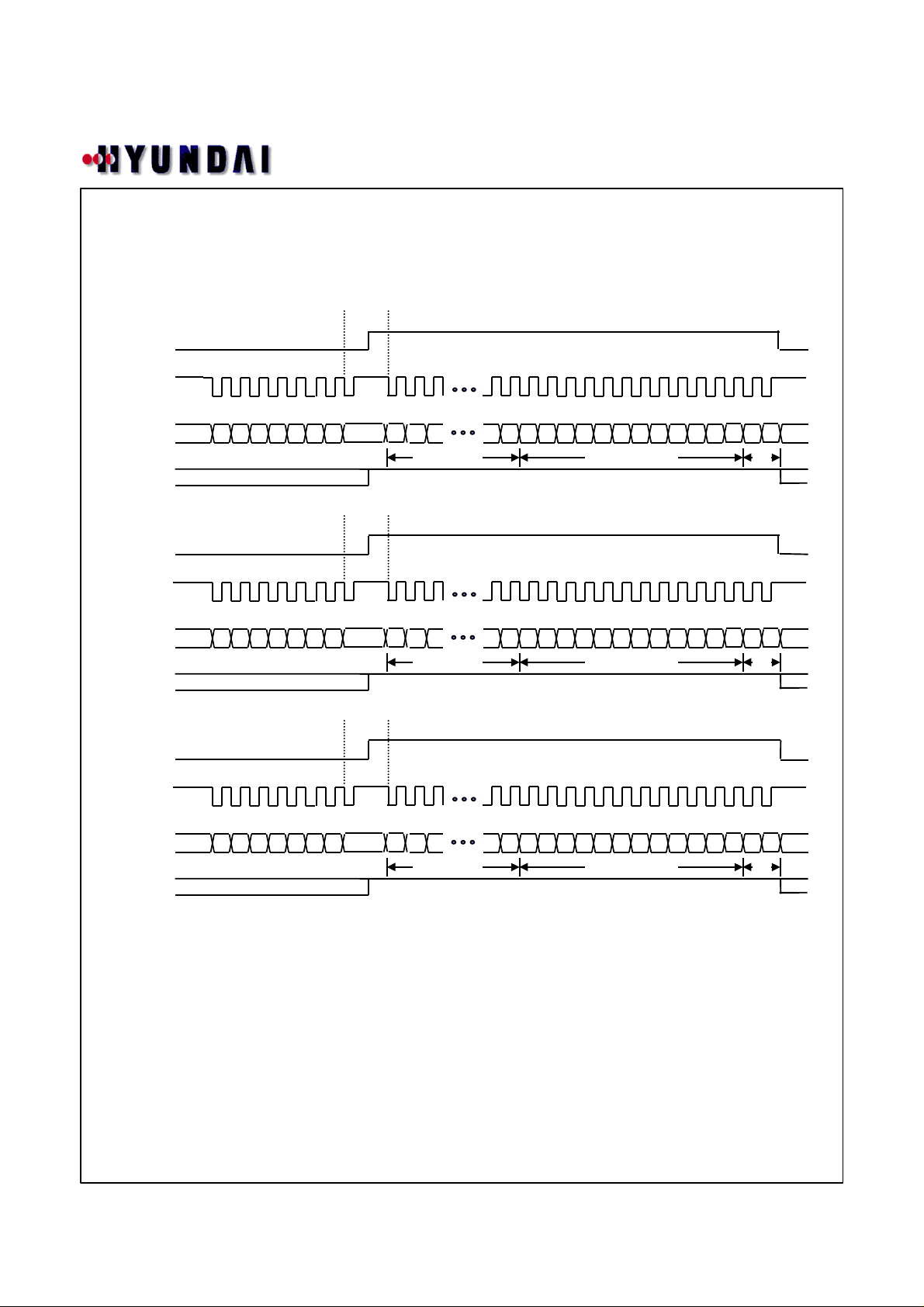

ii )SCK is stopped at the high level

CE

SCK

HL14203

SI

SO

CE

SCK

SI

SO

CE

SCK

SI

SO

1 0 0 0 0 1 0 0 D2 D3XX

A0 A1 A2 A3 A4 A5 A6 A7

1 0 0 0 0 1 0 0 D44 D45XX

A0 A1 A2 A3 A4 A5 A6 A7

1 0 0 0 0 1 0 0 D86 D87XX

A0 A1 A2 A3 A4 A5 A6 A7

D1

D43

D85

Display data

Display data

Display data

D41

D42 0 0 0 0 S0 S1 K0 K1 P0 P1 SC DR 0 0

Control data DD

D83

D84 0 0 0 0 S0 S1 K0 K1 P0 P1 SC DR 0 1

Fixed data DD

D125

D126

0 0 0 0 S0 S1 K0 K1 P0 P1 SC DR 1 0

Fixed data DD

A7~A0 : 42H address

D126~D1 : Data of LCD display registers

S0, S1 : Sleep control data

K0, K1 : Key scan output / Segment output selection data

P0, P1 : Segment output / general-purpose output port selection data

SC : Segment on / off control data

DR : 1/2 bias or 1/3 bias drive selection data

8

P r e l i m i n a r y

Loading...

Loading...