Page 1

RCV56HCF

PCI/CardBus Modem Designer's Guide

(Preliminary)

ROCKWELL PROPRIETARY INFORMATION.

DISSEMINATION OR USE OF THIS INFORMATION IS NOT PERMITTED WITHOUT THE

WRITTEN PERMISSION OF ROCKWELL INTERNATIONAL.

Order No. 1129

Rev. 1, August 19, 1997

Page 2

RCV56HCF PCI/CardBus Modem Designer’s Guide

NOTICE

Information furnished by Rockwell International Corporation is believed to be accurate and reliable. However, no

responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties

which may result from its use. No license is granted by implication or otherwise under any patent rights of Rockwell

International other than for circuitry embodied in Rockwell products. Rockwell International reserves the right to change

circuitry at any time without notice. This document is subject to change without notice.

K56flex is a trademark of Lucent Technologies and Rockwell International.

MNP 10EC and DigiTalk are trademarks of Rockwell International.

MNP is a trademark of Microcom Systems, Inc.

VoiceView is a registered trademark of Radish Communications, Inc.

Hayes is a trademark of Hayes Microcomputer Products, Inc.

ii

ROCKWELL PROPRIETARY INFORMATION

1129

Page 3

RCV56HCF PCI/CardBus Modem Designer’s Guide

Table of Contents

1. INTRODUCTION .............................................................................................................................................1-1

1.1 SUMMARY................................................................................................................................................. 1-1

1.2 FEATURES................................................................................................................................................1-1

1.3 TECHNICAL OVERVIEW ...........................................................................................................................1-7

1.3.1 General Description..........................................................................................................................1-7

1.3.2 Operating Modes..............................................................................................................................1-7

Data/Fax Modes..............................................................................................................................1-7

AudioSpan Modes...........................................................................................................................1-7

Host-Controlled DSVD Mode (ISDN and SP Models) .......................................................................1-7

Voice/Audio Mode (V Models)..........................................................................................................1-7

Speakerphone Mode (ISDN and SP Models)...................................................................................1-8

Synchronous Access Mode (SAM)...................................................................................................1-8

1.3.3 Host-Controlled Modem Software......................................................................................................1-8

1.3.4 Downloadable Modem Data Pump Firmware.....................................................................................1-8

1.3.5 Hardware Interfaces .........................................................................................................................1-8

2. TECHNICAL SPECIFICATIONS......................................................................................................................2-1

2.1 ESTABLISHING DATA MODEM CONNECTIONS.......................................................................................2-1

Dialing............................................................................................................................................. 2-1

Modem Handshaking Protocol.........................................................................................................2-1

Call Progress Tone Detection..........................................................................................................2-1

Answer Tone Detection ...................................................................................................................2-1

Ring Detection............................................................................................................................... ..2-1

Billing Protection.............................................................................................................................. 2-1

Connection Speeds.........................................................................................................................2-1

Automode .......................................................................................................................................2-1

2.2 DATA MODE..............................................................................................................................................2-1

Speed Buffering (Normal Mode) ...................................................................................................... 2-1

DTE-to-Modem Flow Control ...........................................................................................................2-1

Escape Sequence Detection............................................................................................................2-1

GSTN Cleardown (K56flex, V.34, V.32 bis, V.32).............................................................................2-1

Fall Forward/Fallback (K56flex, V.34/V.32 bis/V.32).........................................................................2-2

Retrain............................................................................................................................................2-2

2.3 ERROR CORRECTION AND DATA COMPRESSION.................................................................................2-2

V.42 Error Correction ......................................................................................................................2-2

MNP 2-4 Error Correction................................................................................................................2-2

V.42 bis Data Compression.............................................................................................................2-2

MNP 5 Data Compression...............................................................................................................2-2

2.4 MNP 10EC™ ENHANCED CELLULAR CONNECTION...............................................................................2-2

2.5 FAX CLASS 1 OPERATION .......................................................................................................................2-2

2.6 VOICE/AUDIO MODE ................................................................................................................................2-2

2.6.1 Online Voice Command Mode........................................................................................................... 2-3

2.6.2 Voice Receive Mode.........................................................................................................................2-3

2.6.3 Voice Transmit Mode........................................................................................................................2-3

2.6.4 Tone Detectors................................................................................................................................. 2-3

2.6.5 Speakerphone Modes.......................................................................................................................2-3

SIMULTANEOUS AUDIO/VOICE AND DATA (A

2.7

2.8 HOST-BASED DSVD MODE......................................................................................................................2-3

2.9 FULL-DUPLEX SPEAKERPHONE (FDSP) MODE......................................................................................2-3

2.10 VOICEVIEW.............................................................................................................................................2-3

2.11 CALLER ID...............................................................................................................................................2-4

2.12 WORLD CLASS COUNTRY SUPPORT....................................................................................................2-4

2.12.1 Programmable Parameters.............................................................................................................2-4

2.12.2 Blacklist Parameters.......................................................................................................................2-4

2.13 DIAGNOSTICS.........................................................................................................................................2-4

UDIOSPAN

)..........................................................................2-3

1129

ROCKWELL PROPRIETARY INFORMATION

iii

Page 4

RCV56HCF PCI/CardBus Modem Designer’s Guide

2.13.1 Commanded Tests..........................................................................................................................2-4

2.13.2 Power On Reset Tests....................................................................................................................2-4

2.14 LOW POWER SLEEP MODE...................................................................................................................2-4

3. HARDWARE INTERFACE...............................................................................................................................3-1

3.1 HARDWARE SIGNAL PINS AND DEFINITIONS.........................................................................................3-1

3.2 ELECTRICAL,SWITCHING,AND ENVIRONMENTAL CHARACTERISTICS...............................................3-18

3.2.1 Power and Maximum Ratings..........................................................................................................3-18

3.2.2 PCI Bus..........................................................................................................................................3-19

3.2.3 MDP...............................................................................................................................................3-20

3.3 INTERFACE TIMING AND WAVEFORMS................................................................................................3-22

3.3.1 PCI Bus Timing...............................................................................................................................3-22

3.3.2 Serial EEPROM Timing...................................................................................................................3-22

3.3.3 External Device Bus Timing ............................................................................................................3-23

3.3.4 IOM-2 Interface ..............................................................................................................................3-25

4. DESIGN CONSIDERATIONS .......................................................................................................................... 4-1

4.1 PC BOARD LAYOUT GUIDELINES............................................................................................................4-1

4.1.1 General Principles.............................................................................................................................4-1

4.1.2 Component Placement......................................................................................................................4-1

4.1.3 Signal Routing ..................................................................................................................................4-2

4.1.4 Power...............................................................................................................................................4-3

4.1.5 Ground Planes..................................................................................................................................4-4

4.1.6 Crystal Circuit...................................................................................................................................4-4

4.1.7 VC_L1 and VREF Circuit...................................................................................................................4-4

4.1.8 Telephone and Local Handset Interface............................................................................................4-5

4.1.9 Optional Configurations..................................................................................................................... 4-5

4.1.10 MDP Specific..................................................................................................................................4-5

4.2 CRYSTAL/OSCILLATOR SPECIFICATIONS..............................................................................................4-5

4.3 OTHER CONSIDERATIONS ...................................................................................................................... 4-5

4.4 PACKAGE DIMENSIONS........................................................................................................................... 4-8

5. SOFTWARE INTERFACE................................................................................................................................5-1

5.1 PCI C

5.2 BASE ADDRESS REGISTER.....................................................................................................................5-3

5.3 SERIAL EEPROM INTERFACE..................................................................................................................5-4

6. COMMAND SET..............................................................................................................................................6-1

ONFIGURATION REGISTERS

5.1.1 Vendor ID Field.................................................................................................................................5-1

5.1.2 Device ID Field ................................................................................................................................ .5-1

5.1.3 Command Register...........................................................................................................................5-2

5.1.4 Status Register................................................................................................................................. 5-2

5.1.5 Revision ID Field...............................................................................................................................5-3

5.1.6 Class Code Field...............................................................................................................................5-3

5.1.7 Latency Timer Register.....................................................................................................................5-3

5.1.8 Header Type Field ............................................................................................................................5-3

5.1.9 CIS Pointer Register.........................................................................................................................5-3

5.1.10 Subsystem Vendor ID and Subsystem ID Registers........................................................................5-3

5.1.11 Interrupt Line Register ....................................................................................................................5-3

5.1.12 Interrupt Pin Register......................................................................................................................5-3

5.1.13 Min Grant and Max Latency Registers..................................................................................... ........5-3

....................................................................................................................5-1

iv

ROCKWELL PROPRIETARY INFORMATION

1129

Page 5

RCV56HCF PCI/CardBus Modem Designer’s Guide

List of Figures

Figure 1-1. RCV56HCF System Overview..........................................................................................................................1-4

Figure 1-2. RCV56HCF Hardware Configuration Block Diagram.........................................................................................1-5

Figure 1-3. Typical Audio Signal Interface (U.S.)..............................................................................................................1-10

Figure 3-1. RCV56HCF Interface Signals...........................................................................................................................3-2

Figure 3-2. Bus Interface 176-Pin TQFP Hardware Interface Signals .................................................................................3-3

Figure 3-3. Bus Interface 176-Pin TQFP Pin Signals..........................................................................................................3-4

Figure 3-4. MDP 144-Pin TQFP Hardware Interface Signals............................................................................................3-11

Figure 3-5. MDP 144-Pin TQFP Pin Signals.....................................................................................................................3-12

Figure 3-6. Waveforms - Serial EEPROM Interface..........................................................................................................3-22

Figure 3-7. Waveforms - External Device Bus Interface...................................................................................................3-24

Figure 3-8. Waveforms - IOM-2 Interface.........................................................................................................................3-25

Figure 4-1. Package Dimensions - 144-Pin TQFP.............................................................................................................. 4-8

Figure 4-2. Package Dimensions - 176-Pin TQFP.............................................................................................................. 4-9

1129

ROCKWELL PROPRIETARY INFORMATION

v

Page 6

RCV56HCF PCI/CardBus Modem Designer’s Guide

List of Tables

Table 1-1. Modem Models and Functions ..........................................................................................................................1-3

Table 1-2. Typical Signal Routing - Voice Mode...............................................................................................................1-11

Table 1-3. Relay Positions - VoiceView Mode ..................................................................................................................1-11

Table 3-1. Bus Interface 176-Pin TQFP Pin Signals...........................................................................................................3-5

Table 3-2. Bus Interface Pin Signal Definitions...................................................................................................................3-7

Table 3-3. MDP Pin Signals - 144-Pin TQFP....................................................................................................................3-13

Table 3-4. MDP Pin Signal Definitions..............................................................................................................................3-15

Table 3-5. Current and Power Requirements ...................................................................................................................3-18

Table 3-6. Maximum Ratings........................................................................................................................................... 3-18

Table 3-7. PCI Bus DC Specifications for 3.3V Signaling..................................................................................................3-19

Table 3-8. PCI Bus AC Specifications for 3.3V Signaling..................................................................................................3-19

Table 3-9. MDP Digital Electrical Characteristics..............................................................................................................3-20

Table 3-10. Analog Electrical Characteristics ...................................................................................................................3-21

Table 3-11. Timing - Serial EEPROM Interface................................................................................................................3-22

Table 3-12. Timing - External Device Bus Interface............................................................................. .............................3-23

Table 3-13. Timing - IOM-2 Interface...............................................................................................................................3-25

Table 4-1. Modem Pin Noise Characteristics......................................................................................................................4-3

Table 4-2. Crystal Specifications - Surface Mount..............................................................................................................4-6

Table 4-3. Crystal Specifications - Through Hole................................................................................................................4-7

Table 5-1. PCI Configuration Registers..............................................................................................................................5-1

Table 5-2. Command Register............................................................................................................................... ............5-2

Table 5-3. Status Register.................................................................................................................................................5-2

Table 5-4. BIF Address Map..............................................................................................................................................5-3

Table 5-5. EEPROM Configuration Data............................................................................................................................ 5-4

Table 6-1. Command Set Summary - Functional Use Sort .................................................................................................6-1

Table 6-2. Command Set Summary - Alphanumeric Sort...................................................................................................6-4

vi

ROCKWELL PROPRIETARY INFORMATION

1129

Page 7

RCV56HCF PCI/CardBus Modem Designer’s Guide

1. INTRODUCTION

1.1 SUMMARY

The Rockwell RCV56HCF-PCI Host-Controlled Modem Device Family supports high speed analog data, high speed fax,

ISDN, DSVD, AudioSpan, speakerphone, audio/voice, and VoiceView operation. It operates with PSTN or ISDN telephone

lines in the U.S. and world-wide and is offered in several device models (see Table 1-1).

The modem device set consists of PC PCI bus interface (BIF) and modem data pump (MDP) hardware available in two thin

quad flat packs (TQFPs). Host-controlled modem software is also provided.

Operating with +3.3V power, this device set supports 32-bit host applications in such designs as embedded motherboards,

PCI half cards, and CardBus cards.

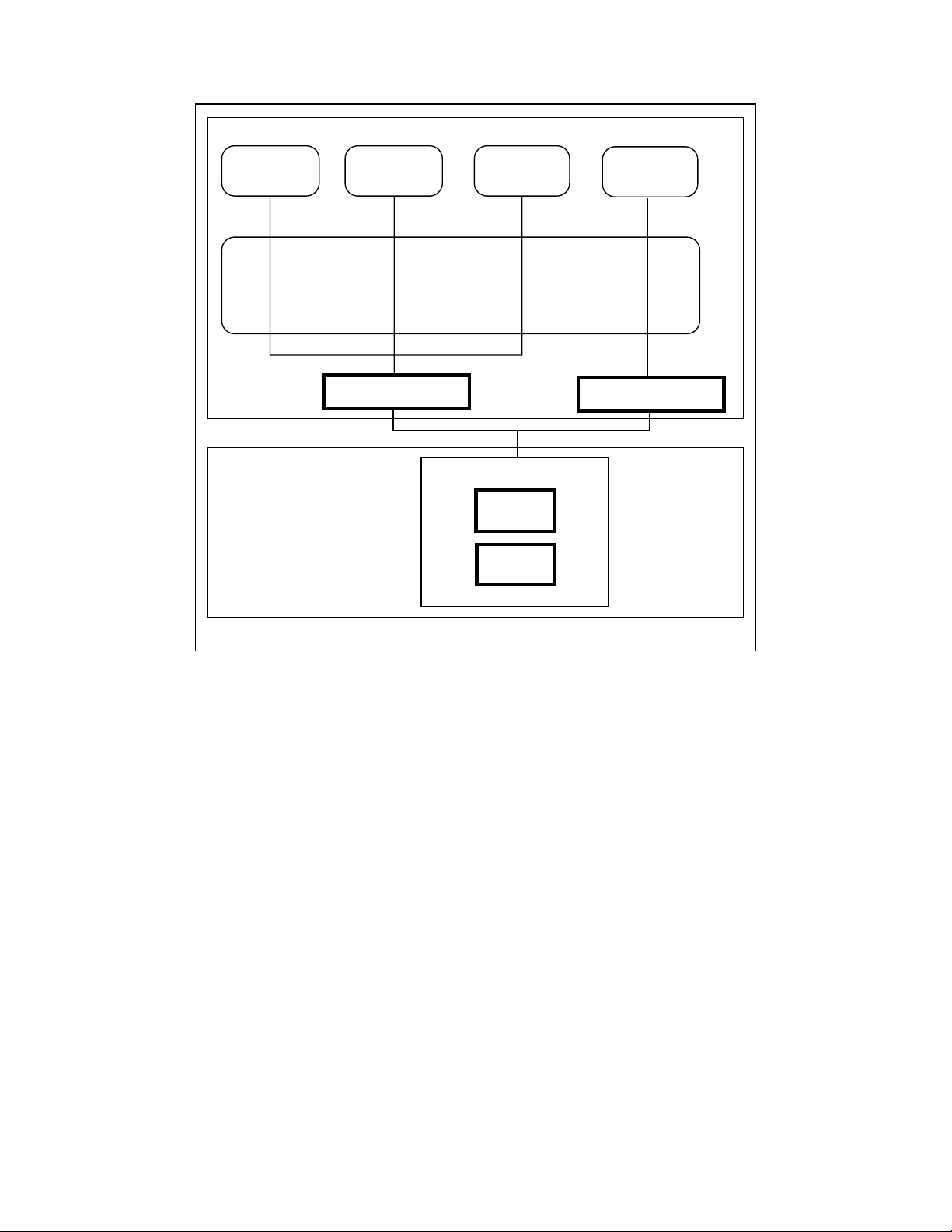

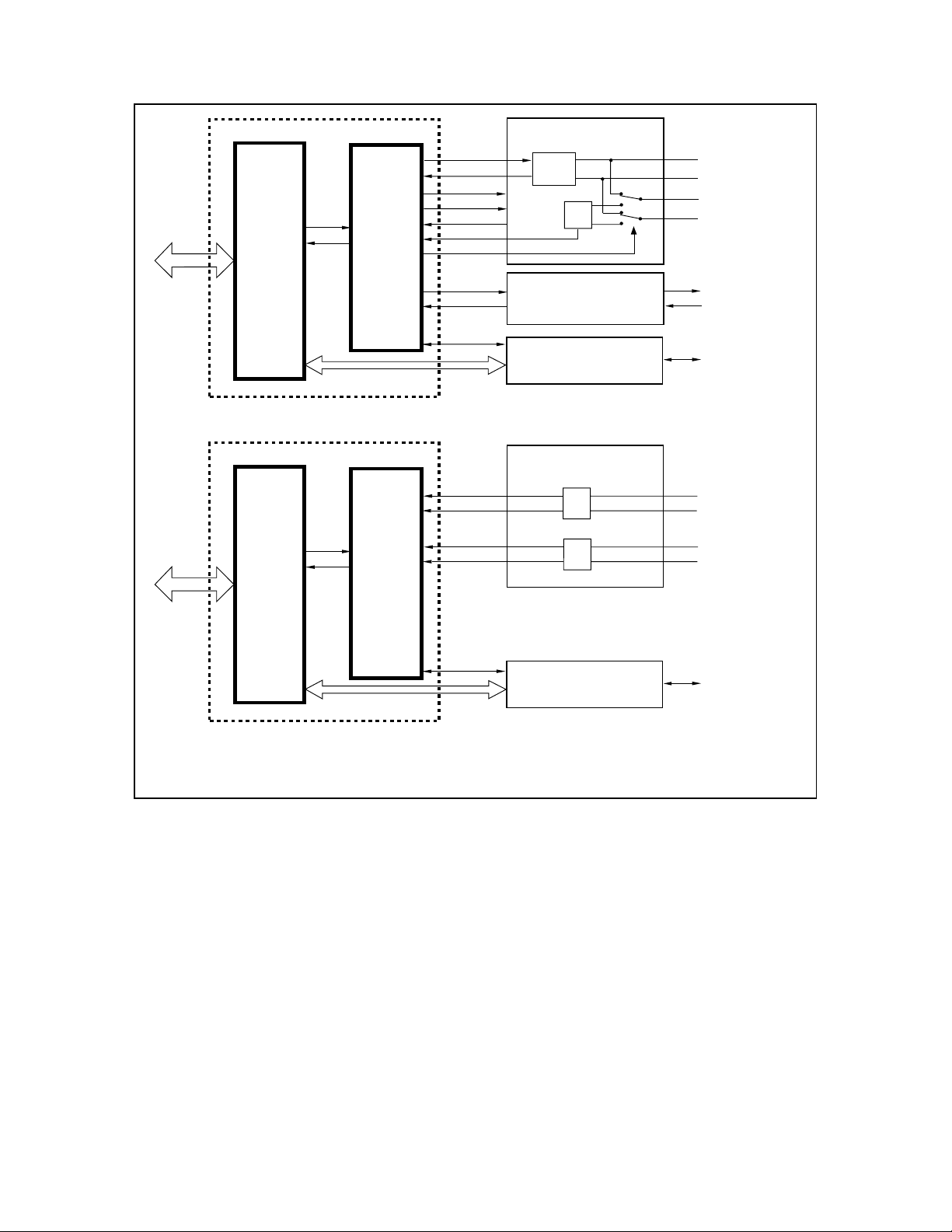

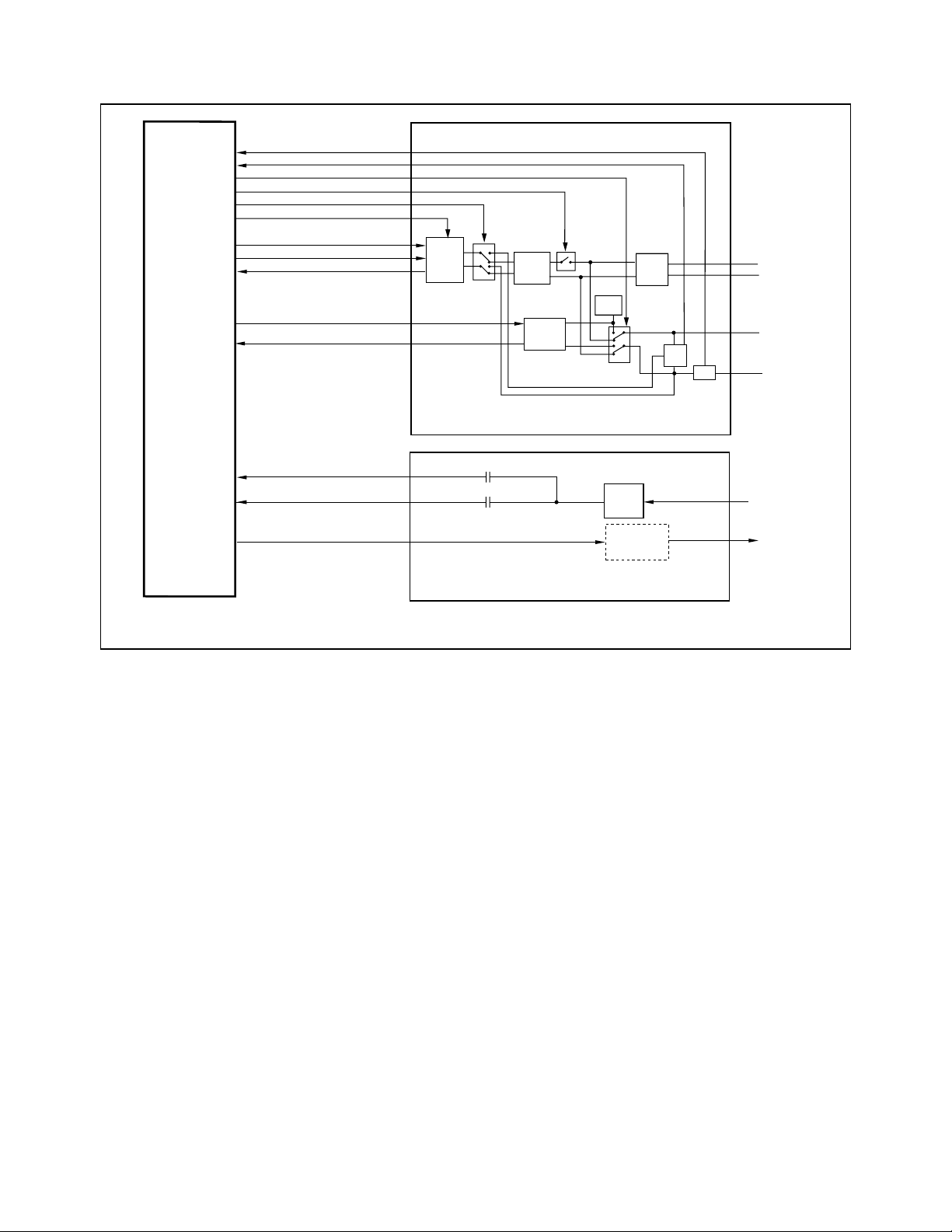

Figure 1-1 illustrates the general structure of the RCV56HCF software and the interface to the RCV56HCF hardware. Figure

1-2 illustrates the major hardware interfaces supported by each model.

The RCV56HCF employs a downloadable architecture so that the user can update MDP executable code.

Using K56flex technology, the RCV56HCF can receive data at speeds up to 56 kbps from a digitally connected K56flex-

compatible central site modem, such as a Rockwell RC56CSM modem. K56flex modems take advantage of the PSTN which

is primarily digital except for the client modem to central office local loop and are ideal for applications such as remote

access to an Internet service provider (ISP), on-line service, or corporate site. The RCV56HCF can send data at speeds up

to V.34 rates.

In V.34 data mode, the modem operates at line speeds up to 33600 bps. Error correction (V.42/MNP 2-4) and data

compression (V.42 bis/MNP 5) maximize data transfer integrity and boost average data throughput. Non-error-correcting

mode is also supported.

AudioSpan (analog simultaneous audio/voice and data) operation supports a data rate with audio of 4.8 kbps.

SP models support position independent, full-duplex speakerphone (FDSP), as well as digital simultaneous voice and data

(DSVD) with speech coding per ITU-T G.729 Annex A with interoperable G.729 Annex B, and SIG DigiTalk DSVD.

The modem supports fax Group 3 send and receive rates up to 28800 bps and T.30 protocol.

V.80 and Rockwell Video Ready compatible synchronous access modes support host-controlled communication protocols, e.

g., H.324 video conferencing.

In voice/audio mode, PCM coding and decoding at 8000 Hz sample rate allows efficient digital storage of voice/audio. This

mode supports digital telephone answering machine, voice annotation, and audio recording/playback applications.

AccelerATor kits and reference designs are available to minimize application design time and costs.

This designer's guide describes the modem hardware capabilities and identifies the supporting commands. Commands and

parameters are defined in the RCVHCF Command Reference Manual (Order No. 1118).

1.2 FEATURES

•

Data modem

−

K56flex, 33.6 kbps, 31.2 kbps, V.34, V.32 bis, V.32, V.22 bis, V.22A/B, V.23, and V.21; Bell 212A and 103

−

V.42 LAPM and MNP 2-4 error correction

−

V.42 bis and MNP 5 data compression

−

V.25 ter (Annex A) and EIA 602 command set

•

Fax modem send and receive rates up to 28800 bps

−

ITU-T V.34 fax*, V.17, V.29, V.27 ter, and V.21 ch 2

−

EIA/TIA 578 Class 1, Class 1.0 (T.31) fax

•

ISDN BRI support (option)*

−

PC Bus support 2B+D channels

−

IOM-2 interface to external U or S/T transceiver

−

Simultaneous transfer of B1, B2, D channels (144 kbps; 64 kbps x 2, 16 kbps)

−

V.34, DSVD, FDSP, audio functions over B channel

1129

ROCKWELL PROPRIETARY INFORMATION

1-1

Page 8

RCV56HCF PCI/CardBus Modem Designer’s Guide

•

AudioSpan (simultaneous audio/voice and data)*

−

ITU-T V.61 modulation (4.8 kbps data plus audio)

−

Handset, headset, or half-duplex speakerphone

•

ITU-T V.70 DSVD (option)

−

ITU-T G.729 Annex A with interoperable G.729 Annex B

−

SIG (special interest group) DigiTalk DSVD

−

Voice/silence detection and handset echo cancellation

−

Handset, headset, or half-duplex speakerphone

•

Full-duplex speakerphone (FDSP) mode

−

Over PSTN or ISDN B channel (option)

−

Switching to/from data, fax, DSVD and VoiceView

−

Microphone gain and muting

−

Speaker volume control and muting

−

Adaptive line and acoustic echo cancellation

−

Loop gain control, transmit and receive path AGC

−

Acoustic echo cancellation concurrent with DSVD

−

Noise suppression

−

Room monitor

•

V.80 and Rockwell Video Ready synchronous access modes support host-controlled communication protocols

−

H.324 interface support

•

V.8/V.8bis and supporting AT commands (V.25 ter with Annex A)

•

Data/Fax/VoiceView/Voice call discrimination

•

Voice, telephony, audio, VoiceView

−

Voice (8-bit µ-Law compression/decompression)

−

TIA-695 command set

−

VoiceView alternating voice and data (option)

−

8-bit linear and 8-bit µ-Law record/playback

−

8.0 kHz, 11.025 kHz, 22.050 kHz and 44.1 kHz (down sampled to 11.025)

−

Handset, acoustic, line echo cancellation

−

Music on hold from host or analog hardware input

−

TAM support with concurrent DTMF detect, ring detect and caller ID

•

World-class operation (option)

−

Call progress, blacklisting, multiple country support

•

Integrated internal hybrid

•

Caller ID and distinctive ring detect

•

Modem and audio paths concurrent across PCI bus

•

Single profile stored in host

•

System compatibilities

−

Windows 95 and Windows NT operating systems

−

Microsoft's PC 97 Design Initiative compliant

−

Unimodem/V compliant

•

32-bit PCI Local Bus interface

−

Conforms to the PCI Local Bus Specification, Production Version, Revision 2.1

−

PCI Bus Mastering interface to the MDP

−

CardBus support with 512-byte RAM for CIS

−

33 MHz PCI clock support

•

Device packages:

−

Bus Interface in 176-pin TQFP

−

MDP in 144-pin TQFP

•

+3.3V operation

* See Note 6 in Table 1-1.

1-2

ROCKWELL PROPRIETARY INFORMATION

1129

Page 9

RCV56HCF PCI/CardBus Modem Designer’s Guide

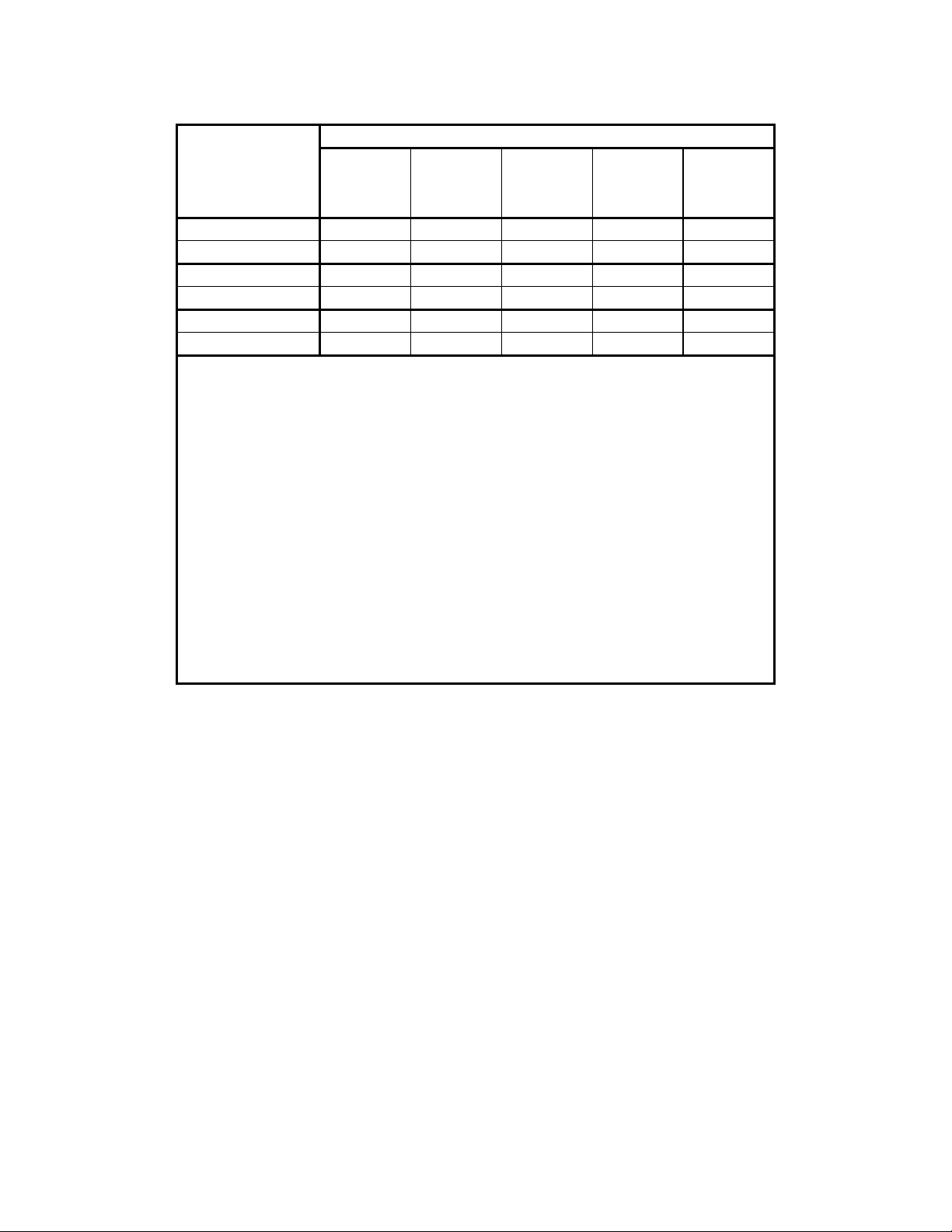

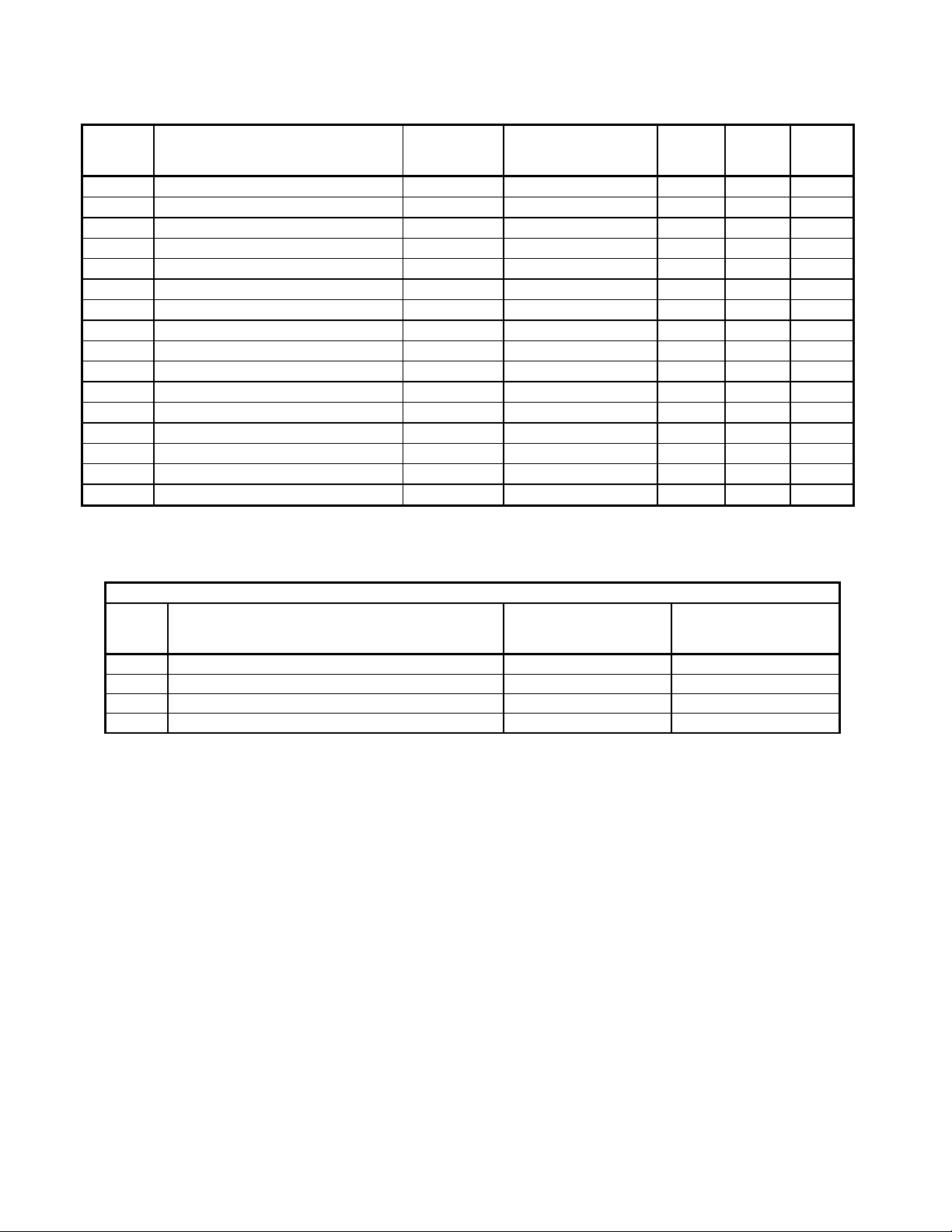

Table 1-1. Modem Models and Functions

Supported Functions

Marketing

Model Number

RCV56HCF/ISDN Y Y Y Y –

RCV56HCFW/ISDN Y Y Y Y Y

RCV56HCF/SP Y Y – Y –

RCV56HCFW/SP Y Y – Y Y

RC56HCF Y – – – –

RC56HCFW Y – – – Y

Notes:

1. The two-device set manufacturing part numbers are:

2

. Lege

3. Model options:

4. Supported functions (Y = Supported; – = Not supported):

5. Provides ISDN functionality with the addition of a U or S/T transceiver device.

6. Initial production does not include support for ISDN, V.34 fax, and AudioSpan.

1

PCI Bus Interface in 176-pin TQFP: 11229-XX.

MDP in 144-pin TQFP: R6776-XX.

nd:

Y = Function supported.

– = Function not supported.

SP Speakerphone and DSVD.

V Voice, audio, and VoiceView.

W World-class (W-class).

FDSP Full-duplex speakerphone.

DSVD Digital simultaneous voice and data.

Voice/Audio Voice and audio functions.

VoiceView VoiceView alternating voice and data.

W-Class World-class functions supporting multiple country requirements.

K56flex,

V.34 Fax

6

Voice/Audio/

VoiceView/

AudioSpan

6

5,6 Full-duplex

ISDN

Speakerphone

(FDSP)

and DSVD

W-Class

1129

ROCKWELL PROPRIETARY INFORMATION

1-3

Page 10

RCV56HCF PCI/CardBus Modem Designer’s Guide

PC Software

Win32-based

communications

application

Modem Hardware

on Motherboard

or Plug-in Module

Win16-based

communications

application

Communications Stack

RC56HCF

Serial Port Driver*

MS-DOS

application

(MS-DOS Box)

Win95

RCV56HCF

Modem Device Set Hardware

Bus

Interface

(BIF)*

Modem

Data Pump

(MDP)*

Win32

NDIS

application

RC56HCF

WAN Miniport Driver*

* Rockwell supplied

1123F1 SO

Figure 1-1. RCV56HCF System Overview

1-4

ROCKWELL PROPRIETARY INFORMATION

1129

Page 11

RCV56HCF PCI/CardBus Modem Designer’s Guide

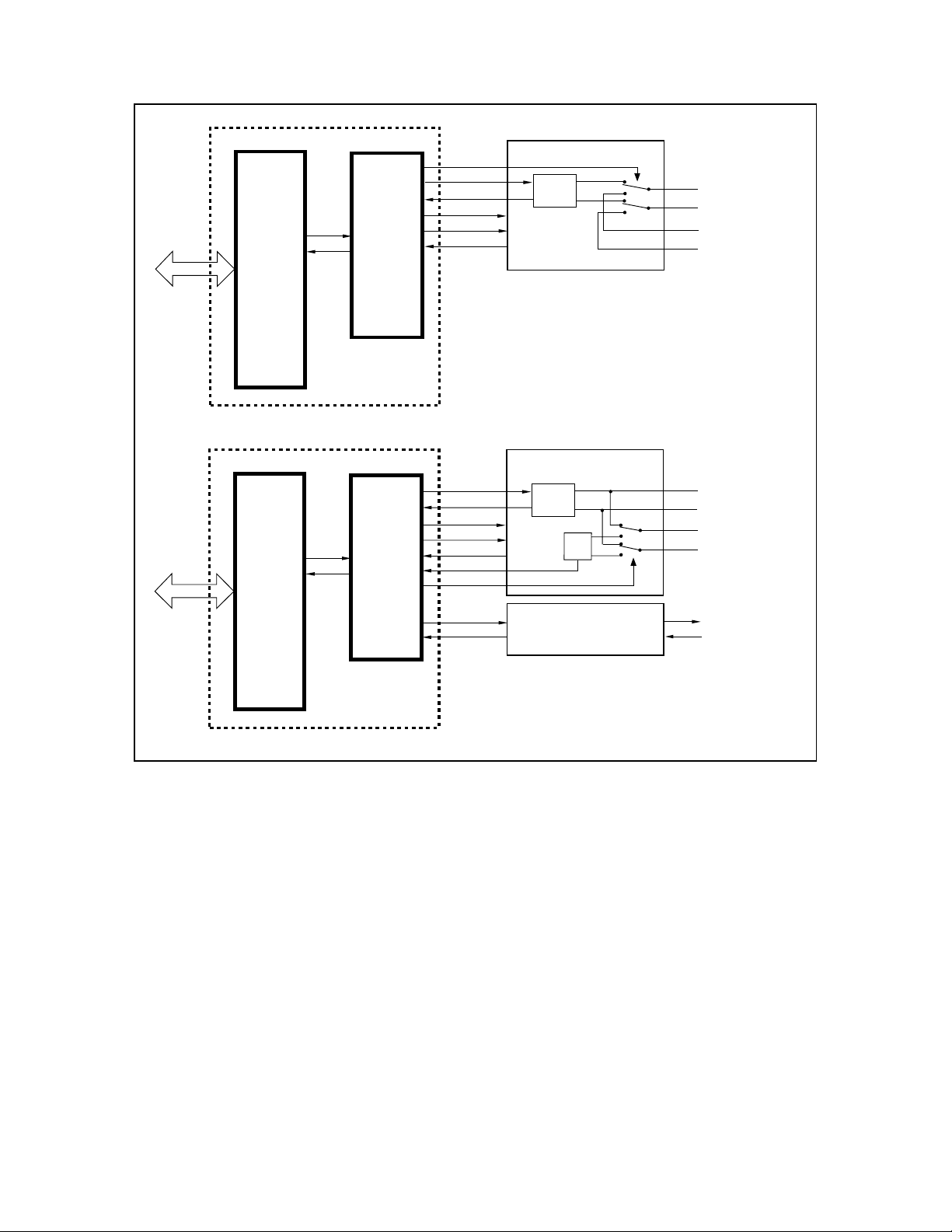

RC56HCF MODEM DEVICE SET

BUS

INTERFACE

(BIF)

MODEM

DATA PUMP

(MDP)

DAA AND TELEPHONE

HANDSET INTERFACE

TELEPHONE

HANDSET*

TELEPHONE

LINE

a. Data/Fax - PSTN Configuration (RC56HCF and RC56HCFW)

VOICE*

TXA

RXA

CID*

OH

RING

RCV56HCF MODEM DEVICE SET

BUS

INTERFACE

(BIF)

MODEM

DATA PUMP

(MDP)

b. Data/Fax/Voice/Speakerphone, SVD - PSTN Configuration (RCV56HCF/SP and RCV56HCFW/SP)

HOST

INTERFACE

HOST

INTERFACE

* OPTIONAL USE (SUPPORTED BY MODEL HARDWARE AND SOFTWARE).

* OPTIONAL USE (SUPPORTED BY MODEL HARDWARE AND SOFTWARE).

MICROPHONE

SPEAKER

AUDIO

INTERFACE

SPKR

MIC

TXA

RXA

CID*

OH

RING

LCS*

VOICE*

DAA AND TELEPHONE

HANDSET INTERFACE

TELEPHONE

HANDSET

(OPTIONAL)

TELEPHONE

LINE

DC

FEED

Figure 1-2. RCV56HCF Hardware Configuration Block Diagram

1129

ROCKWELL PROPRIETARY INFORMATION

1-5

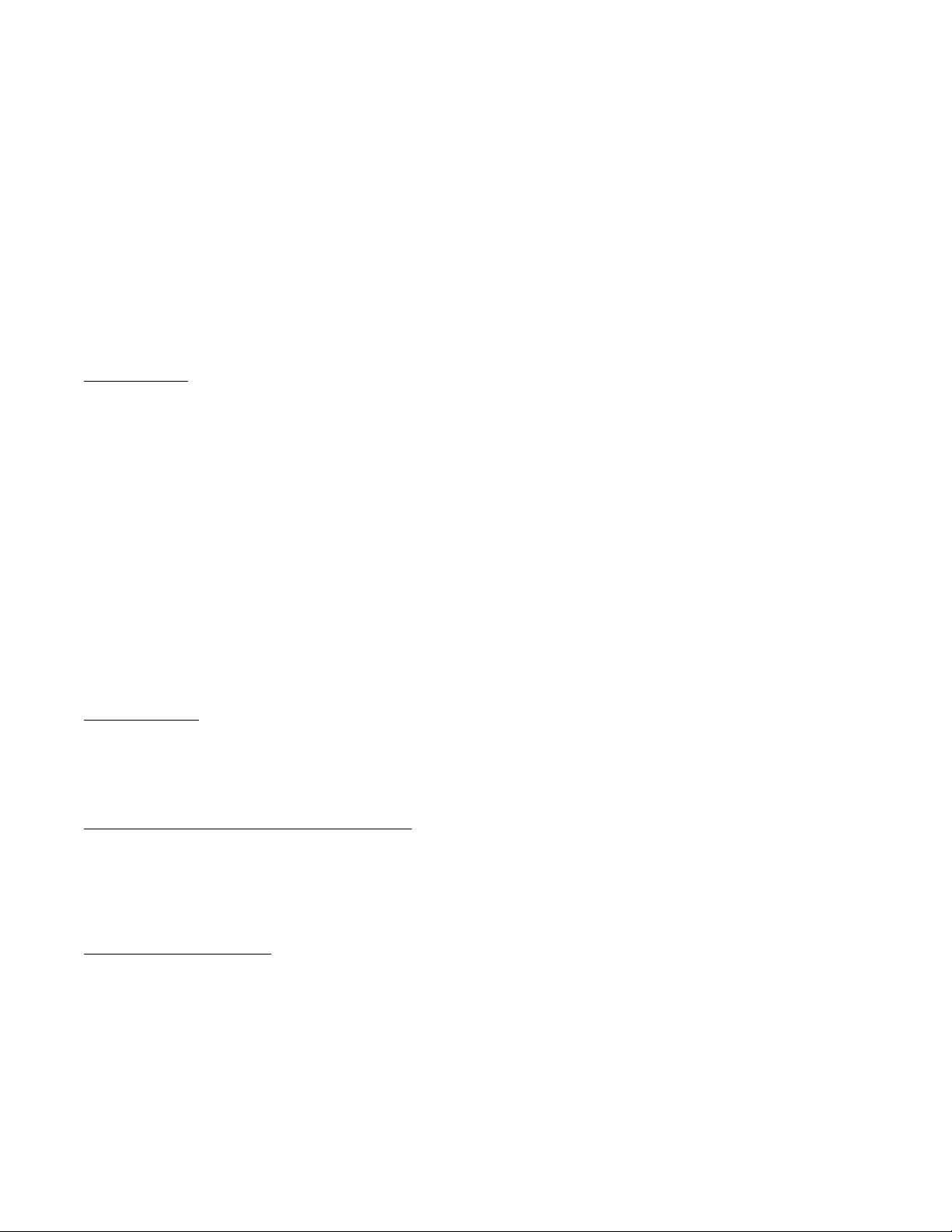

Page 12

RCV56HCF PCI/CardBus Modem Designer’s Guide

ISDN

U OR S/T

INTERFACE

RCV56HCF MODEM DEVICE SET

BUS

INTERFACE

(BIF)

MODEM

DATA PUMP

(MDP)

ISDN LINE

c. Data/Fax/Voice/Speakerphone, SVD/ISDN - PSTN and ISDN Configuration (RCV56HCF/ISDN and RCV56HCFW/ISDN)

MICROPHONE*

SPEAKER*

AUDIO

INTERFACE

(OPTIONAL)

SPKR*

MIC*

ISDN

U OR S/T

INTERFACE

RCV56HCF MODEM DEVICE SET

BUS

INTERFACE

(BIF)

MODEM

DATA PUMP

(MDP)

TELEPHONE

HANDSET INTERFACE

(OPTIONAL)

ISDN LINE

d. Data/Fax/Voice/Speakerphone, SVD/ISDN - ISDN Only Configuration (RCV56HCF/ISDN and RCV56HCFW/ISDN)

TELEPHONE

HANDSET 2

RING*

LCS*

DC

FEED

TELEPHONE

HANDSET 1

RING*

LCS

DC

FEED

* OPTIONAL USE (SUPPORTED BY MODEL HARDWARE AND SOFTWARE).

MD189F1 CONF

HOST

INTERFACE

HOST

INTERFACE

* OPTIONAL USE (SUPPORTED BY MODEL HARDWARE AND SOFTWARE).

TXA

RXA

CID*

OH

RING

LCS*

VOICE*

DAA AND TELEPHONE

HANDSET INTERFACE

TELEPHONE

HANDSET

(OPTIONAL)

TELEPHONE

LINE

DC

FEED

Figure 1-2. RCV56HCF Hardware Configuration Block Diagram (Continued)

1-6

ROCKWELL PROPRIETARY INFORMATION

1129

Page 13

RCV56HCF PCI/CardBus Modem Designer’s Guide

1.3 TECHNICAL OVERVIEW

1.3.1 General Description

The RCV56HCF Device Set provides the processing core for a complete system design featuring data/fax modem, DSVD,

AudioSpan, speakerphone, voice/audio, and VoiceView depending on specific model (Table 1-1). Note: RCV56HCF Device

Set refers to the family of single device modem models listed in Table 1-1.

The modem is the full-featured, self-contained data modem/fax modem/DSVD/voice/audio/speakerphone solution. Dialing,

call progress, telephone line interface, AudioSpan, DSVD, speakerphone, voice/audio, and VoiceView functions are

supported and controlled through the command set.

The modem hardware connects to the host PC via a PCI bus interface. The OEM adds a crystal circuit, telephone line

interface, telephone interface (optional), audio interface (optional), and ISDN interface (optional) to complete the system.

1.3.2 Operating Modes

Data/Fax Modes

In K56flex mode, the modem can receive data from a digital source using a K56flex -compatible central site modem (e.

g., Rockwell RC56CSM) over the digital telephone network portion of the PSTN at line speeds up to 56 kbps. Asymmetrical

data transmission supports sending data at V.34 rates. This mode can fall back to full-duplex V.34 mode, and to slower rates

as supported by line conditions.

In V.34 data modem mode, the modem can also operate in 2-wire, full-duplex, asynchronous modes at line rates up to

33600 bps. Data modem modes perform complete handshake and data rate negotiations. Using V.34 modulation to optimize

modem configuration for line conditions, the modem can connect at the highest data rate that the channel can support from

33600 bps to 2400 bps with automatic fallback. Automode operation in V.34 is provided in accordance with PN3320 and in

V.32 bis in accordance with PN2330. All tone and pattern detection functions required by the applicable ITU or Bell standard

are supported.

In fax modem modes, the modem fully supports Group 3 facsimile send and receive speeds of 28800, 14400, 12000, 9600,

7200, 4800, or 2400 bps. Fax modes support Group 3 fax requirements. Fax data transmission and reception performed by

the modem are controlled and monitored through the fax EIA-578 Class 1 command interface. Full HDLC formatting, zero

insertion/deletion, and CRC generation/checking are provided.

Both transmit and receive fax data are buffered within the modem. Data transfer to and from the DTE is flow controlled by

XON/XOFF and RTS/CTS.

AudioSpan Modes

AudioSpan provides full-duplex analog simultaneous audio/voice and data over a single telephone line at a data rate with

audio of 4800 bps using V.61 modulation. AudioSpan can send any type of audio waveform, including music. Data can be

sent with or without error correction. The audio/voice interface can be in the form of a headset, handset, or microphone and

speaker (half-duplex speakerphone). Handset echo cancellation is provided.

Host-Controlled DSVD Mode (ISDN and SP Models)

ISDN and SP models support host-controlled DSVD. A microphone and a speaker are required.

ITU-T interoperable G.729 and G.729 Annex A with interoperable G.729 Annex B Operation.

supports speech coding at an average bit rate significantly lower than 8.0 kbps.

SIG DigiTalk.

Voice/Audio Mode (V Models)

Voice/Audio Mode features include 8-bit linear and 8-bit µ-Law coding/decoding, tone detection/generation and call

discrimination, concurrent DTMF detection, and 8-bit monophonic audio data encoding at 11.025 kHz or 8000 Hz.

Voice/Audio Mode is supported by three submodes:

1. Online Voice Command Mode supports connection to the telephone line or a voice/audio I/O device (e.g., microphone,

speaker, or handset).

2. Voice Receive Mode supports recording voice or audio data input at the MIC_M pin, typically from a

microphone/handset or the telephone line.

3. Voice Transmit Mode supports playback of voice or audio data to the TXA1_L1/TXA2_L1 output, typically to a

speaker/handset or to the telephone line.

Speech coding is performed at 8.5 kbps.

Voice activity detection

1129

ROCKWELL PROPRIETARY INFORMATION

1-7

Page 14

RCV56HCF PCI/CardBus Modem Designer’s Guide

Speakerphone Mode (ISDN and SP Models)

The speakerphone mode features an advanced proprietary speakerphone algorithm which supports full-duplex voice

conversation with both acoustic and line echo cancellation. Parameters are constantly adjusted to maintain stability with

automatic fallback from full-duplex to pseudo-duplex operation. The speakerphone algorithm allows position independent

placement of microphone and speaker.

The speakerphone mode provides hands-free full-duplex telephone operation under host control. The host can separately

control volume, muting, and AGC in microphone and speaker channels.

Synchronous Access Mode (SAM)

V.80 and Rockwell Video Ready synchronous access modes between the modem and the host/DTE are provided for host-

controlled communication protocols, e.g., H.324 video conferencing applications.

Voice-call-first (VCF) before switching to a videophone call is also supported.

1.3.3 Host-Controlled Modem Software

Host-controlled modem software performs processing of general modem control, command sets, fax Class 1, AudioSpan,

DSVD, speakerphone, voice/audio/TAM, error correction, data compression, and operating system interface functions.

Configurations of the modem software are provided to support modem models listed in Table 1-1.

Binary executable modem software is provided for the OEM.

1.3.4 Downloadable Modem Data Pump Firmware

Binary executable code controlling MDP operation is downloaded as required during operation.

1.3.5 Hardware Interfaces

1.3.5.1 PCI Bus Host Interface

The Bus Interface conforms to the PCI Local Bus Specification, Production Version, Revision 2.1, June 1, 1995. It is a

memory slave (burst transactions) and a bus master for PC host memory accesses (burst transactions). Configuration is by

PCI configuration protocol.

The following interface signals are supported:

•

Address and data

−

32 bidirectional Address/Data (AD[31-0]; bidirectional

−

Four Bus Command and Byte Enable (CBE [3:0]), bidirectional

−

Bidirectional Parity (PAR); bidirectional

•

Interface control

−

Cycle Frame (FRAME#); bidirectional

−

Initiator Ready (IRDY#); bidirectional

−

Target Ready (TRDY#); bidirectional

−

Stop (STOP#); bidirectional

−

Initialization Device Select (IDSEL); input

−

Device Select (DEVSEL#); bidirectional

•

Arbitration

−

Request (REQ#); output

−

Grant (GRANT#); input

•

Error reporting

−

Parity Error ((PERR#); bidirectional

−

System Error ; bidirectional

•

Interrupt

−

Interrupt A (INTA#); output

•

System

−

Clock (PCICLK); input

−

Reset (PCIRST#); input

−

Clock Running (CLKRUN#); input

1-8

ROCKWELL PROPRIETARY INFORMATION

1129

Page 15

RCV56HCF PCI/CardBus Modem Designer’s Guide

1.3.5.2 Serial EEPROM Interface

A serial EEPROM is required to store the Maximum Latency, Minimum Grant, Device ID, Vendor ID, Subsystem ID, and

Subsystem Vendor ID parameters for the PCI Configuration Space Header.

Microchip 93LC66B, Atmel AT93C66,

line from the EEPROM (SROMIN), a serial data output line to the EEPROM (SROMOUT), Clock to the EEPROM

(SROMCLK), and chip select to the EEPROM (SROMCS).

1.3.5.3 Audio Interface

One Speaker output (SPKROUT_M) is provided for an optional OEM-supplied speaker circuit. Two microphone inputs are

supported: one for Voice Microphone input (MIC_V) and one for Music Microphone input (MIC_M), e.g., music-on-hold.

The MIC_V and SPKROUT_M lines connect to the handset and speaker to support functions such as AudioSpan headset

and speakerphone modes, FDSP, telephone emulation, microphone voice record, speaker voice playback, and call progress

monitor.

The MIC_M input can accept an external audio signal to support the music-on-hold function and routes it to the telephone

line. If music-on-hold function is not required, the microphone signal can be connected to the MIC_M input to support

telephone emulation mode.

The Speaker output (SPKROUT_M) carries the normal speakerphone audio or reflects the received analog signals in the

modem.

1.3.5.4 Telephone Line/Telephone/Audio Interface

The Telephone Line/Telephone/Audio Signal Interface can support a 3-relay telephone line interface (Figure 1-3). Signal

routing for Voice mode is shown in Table 1-2. Relay positions for VoiceView are shown in Table 1-3.

The following signals are supported:

•

A single-ended Receive Analog input (RXA_L1) and a differential Transmit Analog output (TXA1_L1 and TXA2_L1) to the

telephone line.

•

Off-hook (OH_L1#), Caller ID (CID_L1#), and Voice (VOICE_L1#) relay control outputs.

•

A Ring Indicate (IRING_L1) input.

•

A Loop Current Sense (LCS) input.

•

An input from the telephone microphone (TELIN_L1) and an output to the telephone speaker (TELOUT_L1 ) are supported

in AudioSpan modes. These lines connect voice record/playback and AudioSpan audio to the local handset.

or equivalent 256 x 16 serial EEPROM. The interface signals are: a serial data input

The EEPROM is programmable by the PC via the BIF.

The serial EEPROM interface connects to an

1129

ROCKWELL PROPRIETARY INFORMATION

1-9

Page 16

RCV56HCF PCI/CardBus Modem Designer’s Guide

LCS_L1#

IRING_L1#

VOICE#

OH_L1#

CID_L1#

VC_L1

RCV56HCF

MODEM

DEVICE

TXA1_L1

TXA2_L1

RXA_L1

TELOUT_L1

TELIN_L1

MIC_M

MIC_V

SPKROUT_M

HYBRD

&

XFRMR

CALLID

RELAY

TELEPHONE LINE/TELEPHONE HANDSET

SSI

&

BRDGE

OH

RELAY

HANDSET

HYBRID

VOICE

RELAY

CUR

SRC

INTERFACE CIRCUIT

BIAS

SOUNDUCER

(OPTIONAL)

AUDIO/HEADPHONE

INTERFACE CIRCUIT

Figure 1-3. Typical Audio Signal Interface (U.S.)

AMP/

SURG

PROT

RNG

DET

TEL LINE

TEL HANDSET

LCS

MICROPHONE

HEADPHONE

1123F1-3 AIF 3R-US

1-10

ROCKWELL PROPRIETARY INFORMATION

1129

Page 17

RCV56HCF PCI/CardBus Modem Designer’s Guide

Table 1-2. Typical Signal Routing - Voice Mode

+VLS=

Command

0 Modem on hook. Phone connected to Line . . No No Yes

1 Modem connected to Line. RXA_L1 TXA1/2_L1 Yes Yes No

2 Modem connected to Handset TELIN_L1 TELOUT_L1 No Yes Yes

3 Modem connected to Line and Handset RXA_L1 TXA Yes No No

4 Modem connected to Speaker SPKROUT_M No No Yes

5 Modem connected to Line and Speaker RXA_L1 TXA1/2_L1, SPKROUT_M Yes Yes No

6 Modem connected to Microphone MIC_V . No No Yes

7 Speaker and Mic. routed to Line via Modem RXA_L1, MIC_M TXA1/2_L1, SPKROUT_M Yes Yes No

8 Modem connected to Speaker . SPKROUT_M No No Yes

9 Modem connected to Line and Speaker RXA_L1 TXA1/2_L1, SPKROUT_M Yes Yes No

10 Speaker and Mic. routed to Line via Modem RXA_L1, MIC_M TXA1/2_L1, SPKROUT_M Yes Yes No

11 Modem connected to Microphone MIC_V . No No Yes

12 Speaker and Mic. routed to Line via Modem RXA_L1, MIC_M TXA1/2_L1, SPKROUT_M Yes Yes No

13 Speaker and Mic. routed to Line via Modem RXA_L1, MIC_M TXA1/2_L1, SPKROUT_M Yes Yes No

14 Modem connected to Headset MIC_V SPKROUT_M No No Yes

15 Speaker and Mic. routed to Line via Modem

Description Input Selected Output Selected OH_L1#

RXA_L1, MIC_M TXA1/2_L1, SPKROUT_M

Output

Activated

Yes Yes No

VOICE#

Output

Activated

CID_L1#

Output

Activated

Table 1-3. Relay Positions - VoiceView Mode

2-Relay DAA

Off-Hook Relay (OH_L1)

Activated

Stage Function

1 On-hook No No

2a Detected tone - on-hook No No

2b Detected tone - off-hook for handset and speakerphone Yes No

3 Off-hook Yes Yes

Voice Relay (VOICE#)

Activated

1129

ROCKWELL PROPRIETARY INFORMATION

1-11

Page 18

RCV56HCF PCI/CardBus Modem Designer’s Guide

This page is intentionally blank.

1-12

ROCKWELL PROPRIETARY INFORMATION

1129

Page 19

RCV56HCF PCI/CardBus Modem Designer’s Guide

2. TECHNICAL SPECIFICATIONS

2.1 ESTABLISHING DATA MODEM CONNECTIONS

Dialing

DTMF Dialing.

complies with Bell Publication 47001.

Pulse Dialing.

Blind Dialing.

Modem Handshaking Protocol

If a tone is not detected within the time specified in the S7 register after the last digit is dialed, the modem aborts the call

attempt.

Call Progress Tone Detection

Ringback, equipment busy, and progress tones can be detected in accordance with the applicable standard.

Answer Tone Detection

Answer tone can be detected over the frequency range of 2100 ± 40 Hz in ITU-T modes and 2225 ± 40 Hz in Bell modes.

Ring Detection

A ring signal can be detected from a TTL-compatible square wave input (frequency is country-dependent).

DTMF dialing using DTMF tone pairs is supported in accordance with ITU-T Q.23. The transmit tone level

Pulse dialing is supported in accordance with EIA/TIA-496-A.

The modem can blind dial in the absence of a dial tone if enabled by the X0, X1, or X3 command.

Billing Protection

When the modem goes off-hook to answer an incoming call, both transmission and reception of data are prevented for a

period of time determined by country requirement to allow transmission of the billing signal.

Connection Speeds

Data modem line connection can be selected using the +MS command in accordance with V.25 ter. The +MS command

selects modulation, enables/disables automode, and selects transmit and receive minimum and maximum line speeds.

Automode

Automode detection can be enabled by the +MS command to allow the modem to connect to a remote modem in

accordance with V.25 ter.

2.2 DATA MODE

Data mode exists when a telephone line connection has been established between modems and all handshaking has been

completed.

Speed Buffering (Normal Mode)

Speed buffering allows a DTE to send data to, and receive data from, a modem at a speed different than the line speed. The

modem supports speed buffering at all line speeds.

DTE-to-Modem Flow Control

If the modem-to-line speed is less than the DTE-to-modem speed, the modem supports XOFF/XON or RTS/CTS flow control

with the DTE to ensure data integrity.

Escape Sequence Detection

The “+++” escape sequence can be used to return control to the command mode from the data mode. Escape sequence

detection is disabled by an S2 Register value greater than 127.

GSTN Cleardown (K56flex, V.34, V.32 bis, V.32)

Upon receiving GSTN Cleardown from the remote modem in a non-error correcting mode, the modem cleanly terminates the

call.

1129

ROCKWELL PROPRIETARY INFORMATION

2-1

Page 20

RCV56HCF PCI/CardBus Modem Designer’s Guide

Fall Forward/Fallback (K56flex, V.34/V.32 bis/V.32)

During initial handshake, the modem will fallback to the optimal line connection within K56flex/V.34/V.32 bis/V.32 mode

depending upon signal quality if automode is enabled by the +MS command.

When connected in K56flex/V.34/V.32 bis/V.32 mode, the modem will fall forward or fallback to the optimal line speed within

the current modulation depending upon signal quality if fall forward/fallback is enabled by the %E1 command.

Retrain

The modem may lose synchronization with the received line signal under poor line conditions. If this occurs, retraining may

be initiated to attempt recovery depending on the type of connection.

The modem initiates a retrain if line quality becomes unacceptable if enabled by the %E command. The modem continues to

retrain until an acceptable connection is achieved, or until 30 seconds elapse resulting in line disconnect.

2.3 ERROR CORRECTION AND DATA COMPRESSION

V.42 Error Correction

V.42 supports two methods of error correction: LAPM and, as a fallback, MNP 4. The modem provides a detection and

negotiation technique for determining and establishing the best method of error correction between two modems.

MNP 2-4 Error Correction

MNP 2-4 is a data link protocol that uses error correction algorithms to ensure data integrity. Supporting stream mode, the

modem sends data frames in varying lengths depending on the amount of time between characters coming from the DTE.

V.42 bis Data Compression

V.42 bis data compression mode operates when a LAPM or MNP connection is established.

The V.42 bis data compression employs a “string learning” algorithm in which a string of characters from the DTE is encoded

as a fixed length codeword. Two dictionaries, dynamically updated during normal operation, are used to store the strings.

MNP 5 Data Compression

MNP 5 data compression mode operates during an MNP connection.

In MNP 5, the modem increases its throughput by compressing data into tokens before transmitting it to the remote modem,

and by decompressing encoded received data before sending it to the DTE.

2.4 MNP 10EC™ ENHANCED CELLULAR CONNECTION

A traditional landline modem, when used for high-speed cellular data transmission, typically encounters frequent signal

interference and degradation in the connection due to the characteristics of the analog cellular network. In this case, cellularspecific network impairments, such as non-linear distortion, fading, hand-offs, and high signal-to-noise ratio, contribute to an

unreliable connection and lower data transfer performance. Implementations relying solely on protocol layer methods, such

as MNP 10, generally cannot compensate for the landline modem's degraded cellular channel performance.

The modem achieves higher cellular performance by implementing enhanced cellular connection techniques at both the

physical and protocol layers, depending on modem model. The modem enhances the physical layer within the modulation by

optimizing its responses to sudden changes in the cellular connection. The MNP 10EC protocol layer implemented in the

modem software improves data error identification/correction and maximizes data throughput by dynamically adjusting speed

and packet size based on signal quality and data error performance.

2.5 FAX CLASS 1 OPERATION

Facsimile functions operate in response to fax class 1 commands when +FCLASS=1.

In the fax mode, the on-line behavior of the modem is different from the data (non-fax) mode. After dialing, modem operation

is controlled by fax commands. Some AT commands are still valid but may operate differently than in data modem mode.

Calling tone is generated in accordance with T.30.

2.6 VOICE/AUDIO MODE

Voice and audio functions are supported by the Voice Mode. Voice Mode includes three submodes: Online Voice Command

Mode, Voice Receive Mode, and Voice Transmit Mode.

2-2

ROCKWELL PROPRIETARY INFORMATION

1129

Page 21

RCV56HCF PCI/CardBus Modem Designer’s Guide

2.6.1 Online Voice Command Mode

This mode results from the connection to the telephone line or a voice/audio I/O device (e.g., microphone, speaker, or

handset) through the use of the +FCLASS=8 and +VLS commands. After mode entry, AT commands can be entered without

aborting the connection.

2.6.2 Voice Receive Mode

This mode is entered when the +VRX command is active in order to record voice or audio data input at the RXA_L1 pin,

typically from a microphone/handset or the telephone line.

Received analog voice samples are converted to digital form and compressed for reading by the host. AT commands control

the codec bits-per-sample rate.

Received analog mono audio samples are converted to digital form and formatted into 8-bit unsigned linear or µ-Law PCM

format for reading by the host. AT commands control the bit length and sampling rate. Concurrent DTMF/tone detection is

available.

2.6.3 Voice Transmit Mode

This mode is entered when the +VTX command is active in order to playback voice or audio data to the TXA1_L1 output,

typically to a speaker/handset or to the telephone line. Digitized audio data is converted to analog form then output to the

TXA1_L1 output.

2.6.4 Tone Detectors

The tone detector signal path is separate from the main received signal path thus enabling tone detection to be independent

of the configuration status. In Tone Mode, all three tone detectors are operational.

2.6.5 Speakerphone Modes

Speakerphone modes are selected in voice mode with the following commands:

Speakerphone ON/OFF (+VSP).

Microphone Gain (+VGM)=<gain>.

unsigned octet where values greater than 128 indicate a gain larger than nominal and values smaller than 128 indicate a

gain smaller than nominal.

Speaker Gain (+VGS=<gain>).

octet where values greater than 128 indicate a gain larger than nominal and values smaller than 128 indicate a gain smaller

than normal.

This command turns the Speakerphone function ON (+VSP = 1) or OFF (+VSP = 0).

This command sets the microphone gain of the Speakerphone function. <gain> is an

This command sets the speaker gain of the Speakerphone function. <gain> is an unsigned

2.7 SIMULTANEOUS AUDIO/VOICE AND DATA (AudioSpan)

The modem can operate in AudioSpan Mode if the remote modem is also configured for AudioSpan Mode operation.

AT commands are used to select the AudioSpan Mode, to enable automatic AudioSpan modulation selection or select a

specific AudioSpan modulation, and to enable AudioSpan data burst operation.

V.61 modulation supports 4800 bps data speed with audio, and a data-only speed of 4800 bps.

The AudioSpan audio interface defaults to the local handset connected to the modem and can be configured to interface

through the modem microphone and speaker pins to support use of a headset or a speakerphone.

2.8 HOST-BASED DSVD MODE

Host-based DSVD operation is enabled by the -SSE or -SMS command. In Host-based DSVD Mode, the modem supports

the transfer of data and voice occurs simultaneously during a data connection.

2.9 FULL-DUPLEX SPEAKERPHONE (FDSP) MODE

The modem operates in FDSP mode when +FCLASS=8 and +VSP=1 (see 2.6.5).

In FDSP Mode, speech from a microphone or handset is converted to digital form, shaped, and output to the telephone line

through the line interface circuit. Speech received from the telephone line is shaped, converted to analog form, and output to

the speaker or handset. Shaping includes both acoustic and line echo cancellation.

2.10 VOICEVIEW

Voice and data can be alternately sent and received in a time-multiplexed fashion over the telephone line whenever the

+FCLASS=80 command is active. This command and other VoiceView commands embedded in host communications

1129

ROCKWELL PROPRIETARY INFORMATION

2-3

Page 22

RCV56HCF PCI/CardBus Modem Designer’s Guide

software control modem operation. Most VoiceView commands use an extended syntax starting with the characters "-S",

which signifies the capability to switch between voice and data.

2.11 CALLER ID

Caller ID can be enabled/disabled using the +VCID command. When enabled, caller ID information (date, time, caller code,

and name) can be passed to the DTE in formatted or unformatted form. Inquiry support allows the current caller ID mode

and mode capabilities of the modem to be retrieved from the modem.

2.12 WORLD CLASS COUNTRY SUPPORT

The W-class models include functions which support modem operation in multiple countries. The following capabilities are

provided in addition to the data modem functions previously described. Country dependent parameters are included in the

.INF file for customization by the OEM.

2.12.1 Programmable Parameters

The following parameters are programmable:

•

Dial tone detection levels and frequency ranges.

•

DTMF dialing transmit output level, DTMF signal duration, and DTMF interdigit interval parameters.

•

Pulse dialing parameters such as make/break times, set/clear times, and dial codes.

•

Ring detection frequency range.

•

Blind dialing disable/enable.

•

The maximum, minimum, and default carrier transmit level values.

•

Calling tone, generated in accordance with V.25, may also be disabled.

•

Call progress frequency and tone cadence for busy, ringback, congested, dial tone 1, and dial tone 2.

•

Answer tone detection period.

•

On-hook/off-hook, make/break, and set/clear relay control parameters.

2.12.2 Blacklist Parameters

The modem can operate in accordance with requirements of individual countries to prevent misuse of the network by limiting

repeated calls to the same number when previous call attempts have failed. Call failure can be detected for reasons such as

no dial tone, number busy, no answer, no ringback detected, voice (rather than modem) detected, and key abort (dial

attempt aborted by user). Actions resulting from such failures can include specification of minimum inter-call delay, extended

delay between calls, and maximum numbers of retries before the number is permanently forbidden ("blacklisted"). Up to 20

such numbers may be tabulated. The blacklist parameters are programmable.

2.13 DIAGNOSTICS

2.13.1 Commanded Tests

Diagnostics are performed in response to &T commands per V.54.

Analog Loopback (&T1 Command).

DTE.

Analog Loopback with Self Test (&T8 Command).

is sent to the modem. An error detector within the modem checks for errors in the string of reversals.

Remote Digital Loopback (RDL) (&T6 Command).

data back to the local DTE.

Remote Digital Loopback with Self Test (&T7 Command).

to the remote modem, which loops the data back to the local modem.

Local Digital Loopback (&T3 Command).

in the local modem. Data from the local DTE is looped back to the local DTE (path 1) and data received from the remote

modem is looped back to the remote modem (path 2).

Data from the local DTE is sent to the modem, which loops the data back to the local

An internally generated test pattern of alternating 1s and 0s (reversals)

Data from the local DTE is sent to the remote modem which loops the

An internally generated pattern is sent from the local modem

When local digital loop is requested by the local DTE, two data paths are set up

2.13.2 Power On Reset Tests

Upon power on, an MDP test is performed. If the MDP is not operational, an error indication is generated.

2.14 LOW POWER SLEEP MODE

When not being used, the MDP is placed in a low power state.

2-4

ROCKWELL PROPRIETARY INFORMATION

1129

Page 23

RCV56HCF PCI/CardBus Modem Designer’s Guide

3. HARDWARE INTERFACE

3.1 HARDWARE SIGNAL PINS AND DEFINITIONS

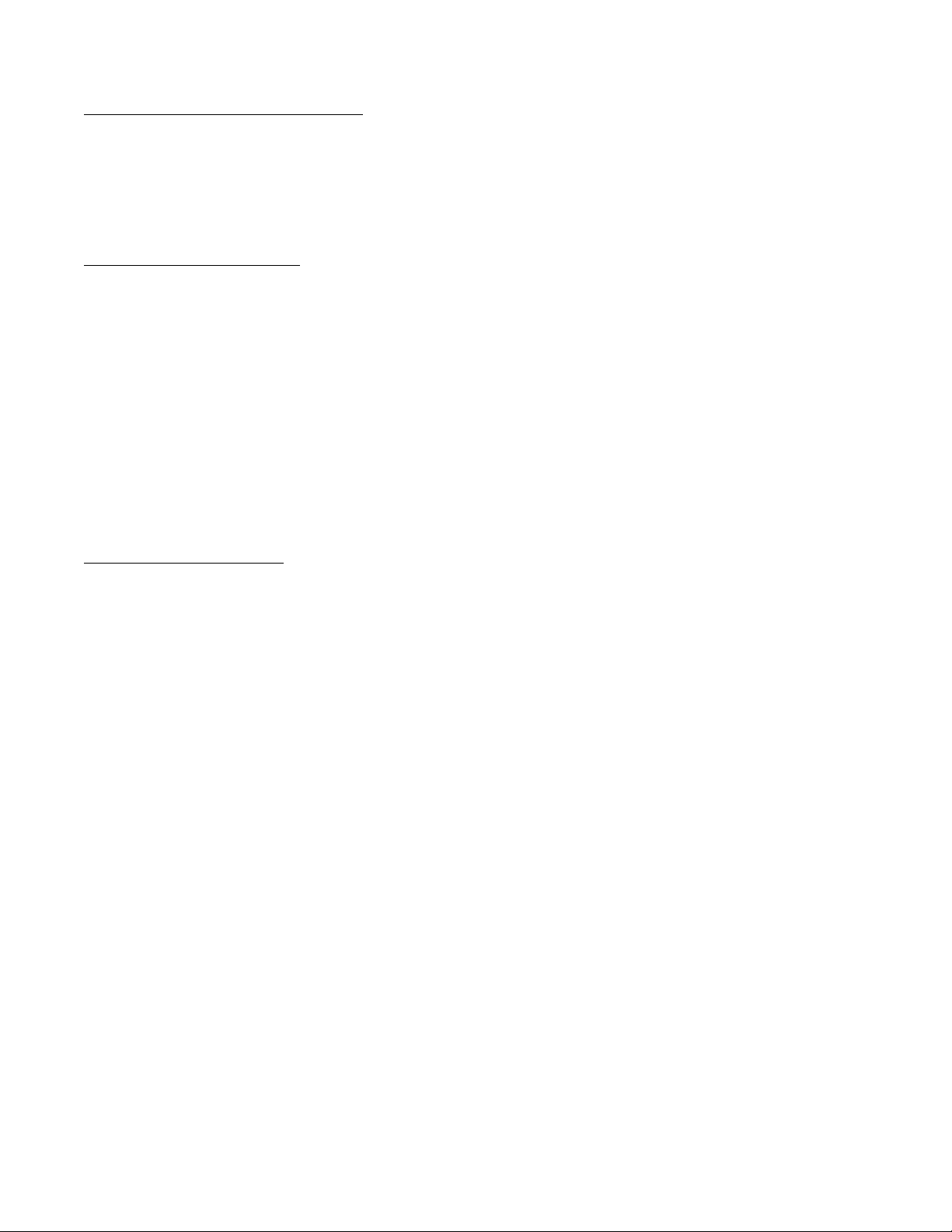

The RCV56HCF (PCI) functional interface signals are shown in Figure 3-1.

The Bus Interface hardware interface signals are shown by major interface in Figure 3-2.

The Bus Interface pin assignments for the 176-pin TQFP are shown Figure 3-3 and are listed Table 3-1.

The Bus Interface hardware interface signals are defined in Table 3-2.

The MDP hardware interface signals are shown by major interface in Figure 3-4.

The MDP pin assignments for the 144-pin TQFP are shown in Figure 3-5 and are listed in Table 3-3.

The MDP hardware interface signals are defined in Table 3-4.

1129

ROCKWELL PROPRIETARY INFORMATION

3-1

Page 24

RCV56HCF PCI/CardBus Modem Designer’s Guide

PCI

BUS

28.224 MHZ

CRYSTAL

CIRCUIT

256 x 16

PCI

SERIAL

EEPROM

VDD

AVDD

GND

GND

AGND

AGND

AGND

AD[31:0]

CBE0#

CBE1#

CBE2#

CBE3#

PCICLK

PCIRST#

FRAME#

IDSEL

DEVSEL#

IRDY#

TRDY#

PAR

REQ#

GNT#

INTA#

STOP#

PERR#

SERR#

XIN

XOUT

SROMCLK

SROMCS

SROMIN

SROMOUT

VDD

AVDD_IA

GND

GND_IA

AGND

AGND_V1

AGND_M1

RCV56HCF

BUS INTERFACE

(176-TQFP)

[11229]

AND

RCV56HCF

MDP

(144-PIN TQFP)

[R6776]

OH_L1#

CID_L1#

VOICE#

MUTE_L1#

IRING_L1#

LCS_L1#

RH_L1#

USED_L1

LCS_H1#

ORING_H1

LCS_H2#

ORING_H2

I/O[4:0]

TELIN_L1

TELOUT_L1

RXA_L1

TXA1_L1

TXA2_L1

VC_L1

SPKROUT_M

MIC_M

MIC_V

IOM_FRAME

IOM_CLK

IOM_DD

IOM_DU

DA[4:0]

DD[7:0]

DRD#

DWR#

ISDN_CS#

ISDN_INT#

DRESET

DRESET#

UNIVERSAL

DAA AND

TELEPHONE

INTERFACE

AUDIO

INTERFACE

ISDN

U OR S/T

INTERFACE

(OPTIONAL)

3-2

Figure 3-1. RCV56HCF Interface Signals

ROCKWELL PROPRIETARY INFORMATION

MD189F2 ISF

1129

Page 25

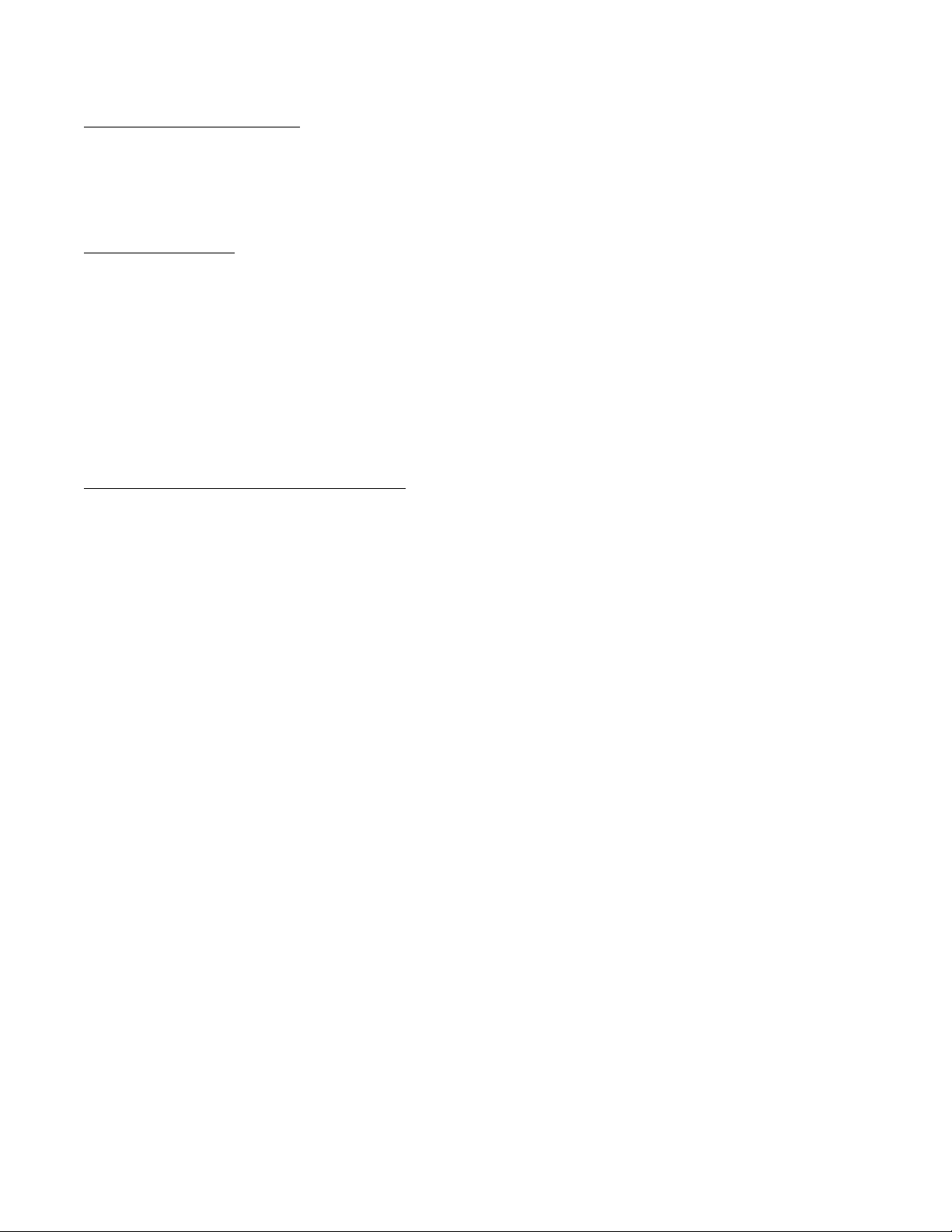

RCV56HCF PCI/CardBus Modem Designer’s Guide

27pF

28.224 MHz

PCI

BUS

EEPROM

NC

5%

27pF

5%

GND

VDD

132

XIN

1M

131

XOUT

27

PCICLK

25

PCIRST#

62

FRAME#

46

IDSEL

66

DEVSEL#

63

IRDY#

64

TRDY#

86

CBE0#

73

CBE1#

61

CBE2#

43

CBE3#

98

AD0

97

AD1

96

AD2

95

AD3

92

AD4

91

AD5

90

AD6

89

AD7

85

AD8

84

AD9

81

AD10

80

AD11

79

AD12

78

AD13

75

AD14

74

AD15

59

AD16

58

AD17

57

AD18

56

AD19

53

AD20

52

AD21

51

AD22

50

AD23

42

AD24

41

40

37

36

35

34

32

72

30

29

24

67

68

69

13

10

11

12

19

20

21

22

23

2

3

6

7

8

14

15

45

151

152

153

160

162

174

175

1K

31

1K

9

PCI BUS INTERFACE

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PAR

REQ#

GNT#

INTA#

STOP#

PERR#

SERR#

SROMCLK

SROMCS

SROMIN

SROMOUT

NC

NC

NC

NC

NC

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

CLKRUN#

CARDBUS#

176-TQFP

[11229]

MODEM_CS#

MODEM_IRQ

M_STROBE

V_STROBE

M_TXCLK

M_TX

M_RXCLK

M_RX

WKRES#

SI_FRAME

SI_CLK

SI_DD

SI_DU

M_CLK

L85CLK

M_RXOUT

M_SCLK

M_CTRL

M_TXSIN

V_RXOUT

V_SCLK

V_CTRL

V_TXSIN

OH_L1#

CID_L1#

VOICE#

MUTE_L1#

IRING_L1#

LCS_L1#

RH_L1#

USED_L1

LCS_H1#

ORING_H1

LCS_H2#

ORING_H2

I/O0

I/O1

I/O2

I/O3

I/O4

DA0

DA1

DA2

DA3

DA4

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

DRD#

DWR#

DRESET#

DRESET

ISDN_CS#

ISDN_INT#

VIO1

VIO2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VGG1

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

113

135

106

105

108

136

107

103

102

100

101

147

130

144

145

143

148

146

141

140

142

138

139

167

166

165

164

170

171

161

173

172

163

174

162

158

157

156

155

154

118

117

116

115

114

128

127

126

125

124

123

122

121

111

112

104

137

16

17

44

47

5

26

38

49

55

70

76

88

94

110

119

149

168

83

1

133

134

4

18

176

28

33

39

48

54

60

65

71

77

82

87

93

99

109

120

129

150

159

169

MDP

DAA

MDP AND

ISDN U OR S/T

INTERFACE

ISDN U OR S/T

INTERFACE

3.3 V

VDD

GND

MD189F3 11221HS-176TQFP

1129

Figure 3-2. Bus Interface 176-Pin TQFP Hardware Interface Signals

ROCKWELL PROPRIETARY INFORMATION

3-3

Page 26

VDD

RESERVED

RESERVED

GND

VDD

RESERVED

RESERVED

RESERVED

CARDBUS#

SROMCS

SROMIN

SROMOUT

SROMCLK

RESERVED

RESERVED

ISDN_CS#

ISDN_INT#

GND

INTA#

PCIRST#

VDD

PCICLK

GND

GNT#

REQ#

CLKRUN#

AD31

GND

AD30

AD29

AD28

AD27

VDD

GND

AD26

AD25

AD24

CBE3#

VIO1

RCV56HCF PCI/CardBus Modem Designer’s Guide

GND

RESERVED

LCS_H2#

USED_L1

LCS_H1#

LCS_L1#

IRING_L1#

GND

VDD

OH_L1#

CID_L1#

VOICE#

MUTE_L1#

ORING_H1

ORING_H2

RH_L1#

RESERVED

GND

I/O0

I/O1

I/O2

I/O3

I/O4

RESERVED

RESERVED

RESERVED

GND

VDD

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

M_RX

MODEM_IRQ

VGG1

VDD

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

NC

19

NC

20

NC

21

NC

22

NC

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

XIN

XOUT

MODEM_CLK

GND

DD0

DD1

DD2

DD3

DD4

DD5

DD6

DD7

GND

VDD

DA0

DA1

DA2

DA3

DA4

MODEM_CS#

DWR#

DRD#

VDD

GND

M_RXCLK

WKRES#

M_TXCLK

M_TX

DRESET#

SI_FRAME

SI_CLK

SI_DU

SI_DD

99

GND

98

AD0

97

AD1

96

AD2

95

AD3

94

VDD

93

GND

92

AD4

91

AD5

90

AD6

89

AD7

88

3-4

VIO2

IDSEL

RESERVED

GND

VDD

AD23

AD22

AD21

AD20

GND

VDD

AD19

AD18

AD17

AD16

GND

CBE2#

IRDY#

FRAME#

GND

TRDY#

STOP#

DEVSEL#

PERR#

SERR#

VDD

GND

PAR

CBE1#

Figure 3-3. Bus Interface 176-Pin TQFP Pin Signals

ROCKWELL PROPRIETARY INFORMATION

AD15

AD14

VDD

GND

AD13

AD12

AD11

AD10

GND

VDD

AD9

AD8

VDD

GND

CBE0#

MS189F4-BIF-PO-176TQFP

1129

Page 27

RCV56HCF PCI/CardBus Modem Designer’s Guide

Table 3-1. Bus Interface 176-Pin TQFP Pin Signals

Pin Signal Label I/O

1 VDD P PWR To 3.3V 89 AD7 I/O I/Opts PCI Bus: AD7

2 RESERVED I It To GND 90 AD6 I/O I/Opts PCI Bus: AD6

3 RESERVED I It To GND 91 AD5 I/O I/Opts PCI Bus: AD5

4 GND G GND Ground 92 AD4 I/O I/Opts PCI Bus: AD4

5 VDD P PWR To 3.3V 93 GND G GND Ground

6 RESERVED O Ot2 NC 94 VDD P PWR To 3.3V

7 RESERVED O Ot2 NC 95 AD3 I/O I/Opts PCI Bus: AD3

8 RESERVED O Ot2 NC 96 AD2 I/O I/Opts PCI Bus: AD2

9 CARDBUS# I PWR VCC through 10KΩ for PCI 97 AD1 I/O I/Opts PCI Bus: AD1

10 SROMCS O Ot2 SROM Chip Select 98 AD0 I/O I/Opts PCI Bus: AD0

11 SROMOUT O Ot2 SROM Data Out 99 GND G GND Ground

12 SROMIN I It SROM Data In 100 SI_DD I It MDP: SI Data Downstream

13 SROMCLK O Ot2 SROM Clock 101 SI_DU O Ot2 MDP: SI Data Upstream

14 RESERVED O Ot2 NC 102 SI_CLK I/O It/Ot MDP: SI Clock

15 RESERVED I It To GND 103 SI_FRAME I/O It/Ot MDP: SI Frame

16 ISDN_CS# O Ot2 ISDN: CS# or NC 104 DRESET# O Ot2 DB: DRESET#

17 ISDN_INT# I It ISDN: IRQ or to GND 105 M_TX O Ot2 MDP: M_TX

18 GND G GND Ground 106 M_TXCLK I It MDP: M_RXCLK

19 NC I Itpd NC 107 WKRES# O Ot12 Wakeup Reset

20 NC I It NC 108 M_RXCLK I It MDP: M_RXCLK

21 NC I It NC 109 GND G GND Ground

22 NC O Ot4ts NC 110 VDD P PWR To 3.3V

23 NC I It NC 111 DRD# O Ot2 DB: DRD#

24 INTA# O Opod PCI Bus: INTA# 112 DWR# O Ot2 DB: DWR#

25 PCIRST# I Ip PCI Bus: PCIRST# 113 MODEM_CS# O Ot2 MDP: CS#

26 VDD P PWR To 3.3V 114 DA4 O Ot2 DB: DA4

27 PCICLK I Ip PCI Bus: PCICLK 115 DA3 O Ot2 DB: DA3

28 GND G GND Ground 116 DA2 O Ot2 DB: DA2

29 GNT# I Ipts PCI Bus: GNT# 117 DA1 O Ot2 DB: DA1

30 REQ# O Opts PCI Bus: REQ# 118 DA0 O Ot2 DB: DA0

31 CLKRUN# I It GND through 1K 119 VDD P PWR To 3.3V

32 AD31 I/O I/Opts PCI Bus: AD31 120 GND G GND Ground

33 GND G GND Ground 121 DD7 I/O It/Ot2 DB: DD7

34 AD30 I/O I/Opts PCI Bus: AD30 122 DD6 I/O It/Ot2 DB: DD6

35 AD29 I/O I/Opts PCI Bus: AD29 123 DD5 I/O It/Ot2 DB: DD5

36 AD28 I/O I/Opts PCI Bus: AD28 124 DD4 I/O It/Ot2 DB: DD4

37 AD27 I/O I/Opts PCI Bus: AD27 125 DD3 I/O It/Ot2 DB: DD3

38 VDD P PWR To 3.3V 126 DD2 I/O It/Ot2 DB: DD2

39 GND G GND Ground 127 DD1 I/O It/Ot2 DB: DD1

40 AD26 I/O I/Opts PCI Bus: AD26 128 DD0 I/O It/Ot2 DB: DD0

41 AD25 I/O I/Opts PCI Bus: AD25 129 GND G GND Ground

42 AD24 I/O I/Opts PCI Bus: AD24 130 MODEM_CLK O Ot2 MDP:XTLI

43 CBE3# I/O I/Opts PCI Bus: CBE3# 131 XOUT O Ot2 Crystal Output

44 VIO1 P PWR To VIO 132 XIN I It Crystal Input

45 RESERVED I Itpd NC 133 VDD P PWR To 3.3V

46 IDSEL I Ip PCI Bus: IDSEL 134 VGG1 P PWR To VDD or 3.3V

47 VIO2 P PWR To VIO 135 MODEM_IRQ I It MDP: IRQ#

48 GND G GND Ground 136 M_RX I It MDP: M_RX

49 VDD P PWR To 3.3V 137 MSWRESET O Ot2 NC

50 AD23 I/O I/Opts PCI Bus: AD23 138 RESERVED O Ot2 NC

51 AD22 I/O I/Opts PCI Bus: AD22 139 RESERVED O Ot NC

52 AD21 I/O I/Opts PCI Bus: AD21 140 RESERVED I It To GND

53 AD20 I/O I/Opts PCI Bus: AD20 141 RESERVED I It2 To GND

54 GND G GND Ground 142 RESERVED I It To GND

55 VDD P PWR To 3.3V 143 RESERVED I It To GND

56 AD19 I/O I/Opts PCI Bus: AD19 144 RESERVED I It2 To GND

57 AD18 I/O I/Opts PCI Bus: AD18 145 RESERVED I It To GND

58 AD17 I/O I/Opts PCI Bus: AD17 146 RESERVED O Ot2 NC

59 AD16 I/O I/Opts PCI Bus: AD16 147 RESERVED O Ot2 NC

60 GND G GND Ground 148 RESERVED O Ot2 NC

61 CBE2# I/O I/Opts PCI Bus: CBE2# 149 VDD P PWR To 3.3V

62 FRAME# I/O I/Opsts PCI Bus: FRAME# 150 GND G GND Ground

63 IRDY# I/O I/Opsts PCI Bus: IRDY# 151 RESERVED I Itpd NC

64 TRDY# I/O I/Opsts PCI Bus: TRDY# 152 RESERVED I/O It/Ot12 To 3.3V through 47K

I/O Type

1

Interface Pin Signal Label I/O

I/O Type

1

Interface

1129

ROCKWELL PROPRIETARY INFORMATION

3-5

Page 28

RCV56HCF PCI/CardBus Modem Designer’s Guide

Table 3-1. Bus Interface 176-Pin TQFP Pin Signals

Pin Signal Label I/O

65 GND G GND Ground 153 RESERVED I/O It/Ot12 To 3.3V through 47K

66 DEVSEL# I/O I/Opsts PCI Bus: DEVSEL# 154 I/O4 I/O It/Ot12 DAA: Reserved