HARRIS Semiconductor DG200, DG201 Service Manual

查询DG200供应商

SEMICONDUCTOR

December 1993

Features

• Switches Greater than 28V

• Break-Before-Make Switching t

Typical

• TTL, DTL, CMOS, PMOS Compatible

• Non-Latching with Supply Turn-Off

• Complete Monolithic Construction

• Industry Standard (DG200, DG201)

Signals with ±15 Supplies

P-P

250ns, tON 700ns

OFF

Applications

• Data Acquisition

• Sample and Hold Circuits

• Operational Amplifier Gain Switching Networks

DG200, DG201

CMOS Dual/Quad SPST Analog Switches

Description

The DG200 and DG201 solid state analog gates are

designed using an improved, high voltage CMOS monolithic

technology. They provide ease-of-use and performance

advantages not previously available from solid state

switches. Destructive latch-up of solid state analog gates

has been eliminated by Harris's CMOS technology.

The DG200 and DG201 are completely specification and

pinout compatible with the industry standard devices.

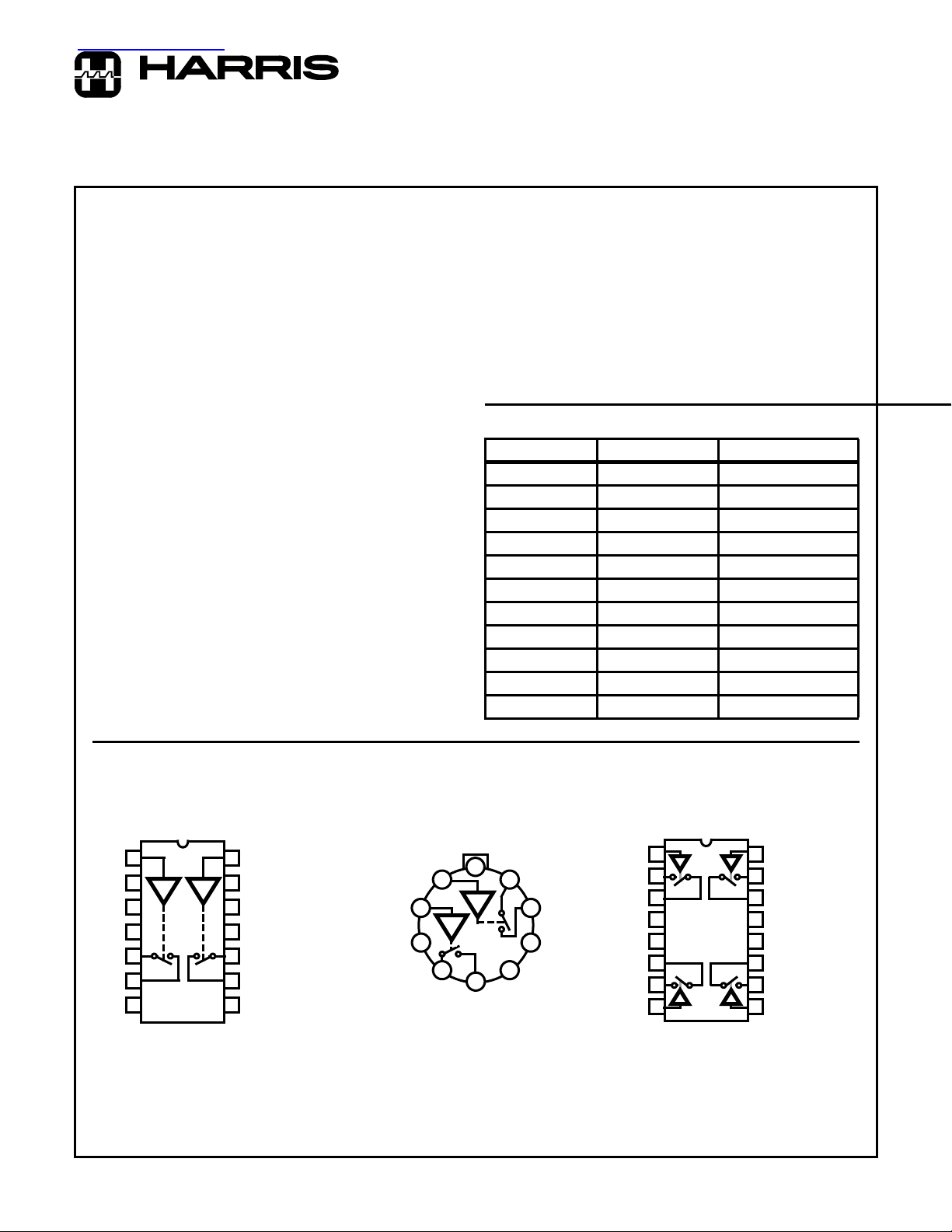

Ordering Information

PART NUMBER TEMPERATURE PACKAGE

DG200AA -55oC to +125oC 10 Pin Metal Can

DG200AK -55oC to +125oC 14 Lead Ceramic DIP

DG200BA -25oC to +85oC 10 Pin Metal Can

DG200BK -25oC to +85oC 14 Lead Ceramic DIP

DG200CJ 0oC to +70oC 14 Lead Plastic DIP

DG200AA/883B -55oC to +125oC 10 Pin Metal Can

DG200AK/883B -55oC to +125oC 14 Lead Ceramic DIP

DG201AK -55oC to +125oC 16 Lead Ceramic DIP

DG201BK -25oC to +85oC 16 Lead Ceramic DIP

DG201CJ 0oC to +70oC 16 Lead Plastic DIP

DG201AK/883B -55oC to +125oC 16 Lead Ceramic DIP

Pinouts

DG200

(CDIP, PDIP)

TOP VIEW

IN

1

2

NC

2

GND

3

NC

4

S

5

2

D

6

2

V-

7

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper I.C. Handling Procedures.

Copyright

© Harris Corporation 1993

14

IN

1

NC

13

V+ (SUBSTRATE)

12

NC

11

S

10

1

D

9

1

V

8

REF

(SUBSTRATE AND CASE)

IN

2

GND

DG200

(TO-100 METAL CAN)

TOP VIEW

V+

IN

2

3

S

10

1

1

4

2

9

6

5

D

2

9-13

IN

S

1

D

8

1

7

V

REF

V-

D

S

V-

GND

S

D

IN

DG201

(CDIP, PDIP)

TOP VIEW

16

1

1

2

1

3

1

4

5

6

4

7

4

8

4

IN

2

15

D

2

14

S

2

13

V+(SUBSTRATE)

V

12

REF

11

S

3

10

D

3

9

IN

3

File Number 3115

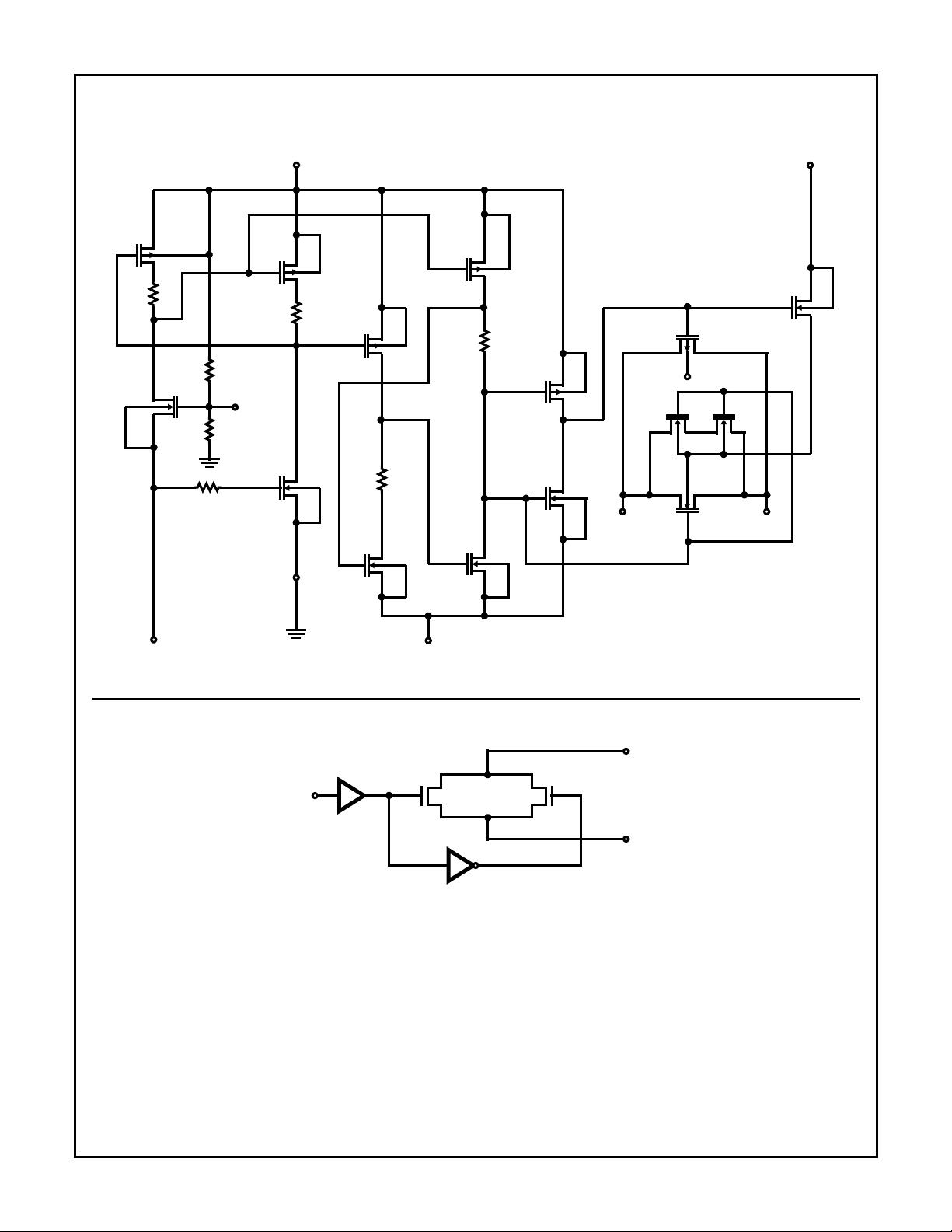

DG200, DG201

Schematic Diagram

Q3

V

Q1

PROTECTION

RESISTOR

REF

GATE

(1/2 DG200,1/4 DG201)

V+

Q7

Q8

Q2

Q5

Q10

Q9

V-

Q14

Q15

V+

Q12

S

1

Q11

Q13

D

1

INPUT

Functional Diagram

Q4

V-

IN

N

Q6

S

P

D

DG200, DG201 SWITCH CELL

9-14

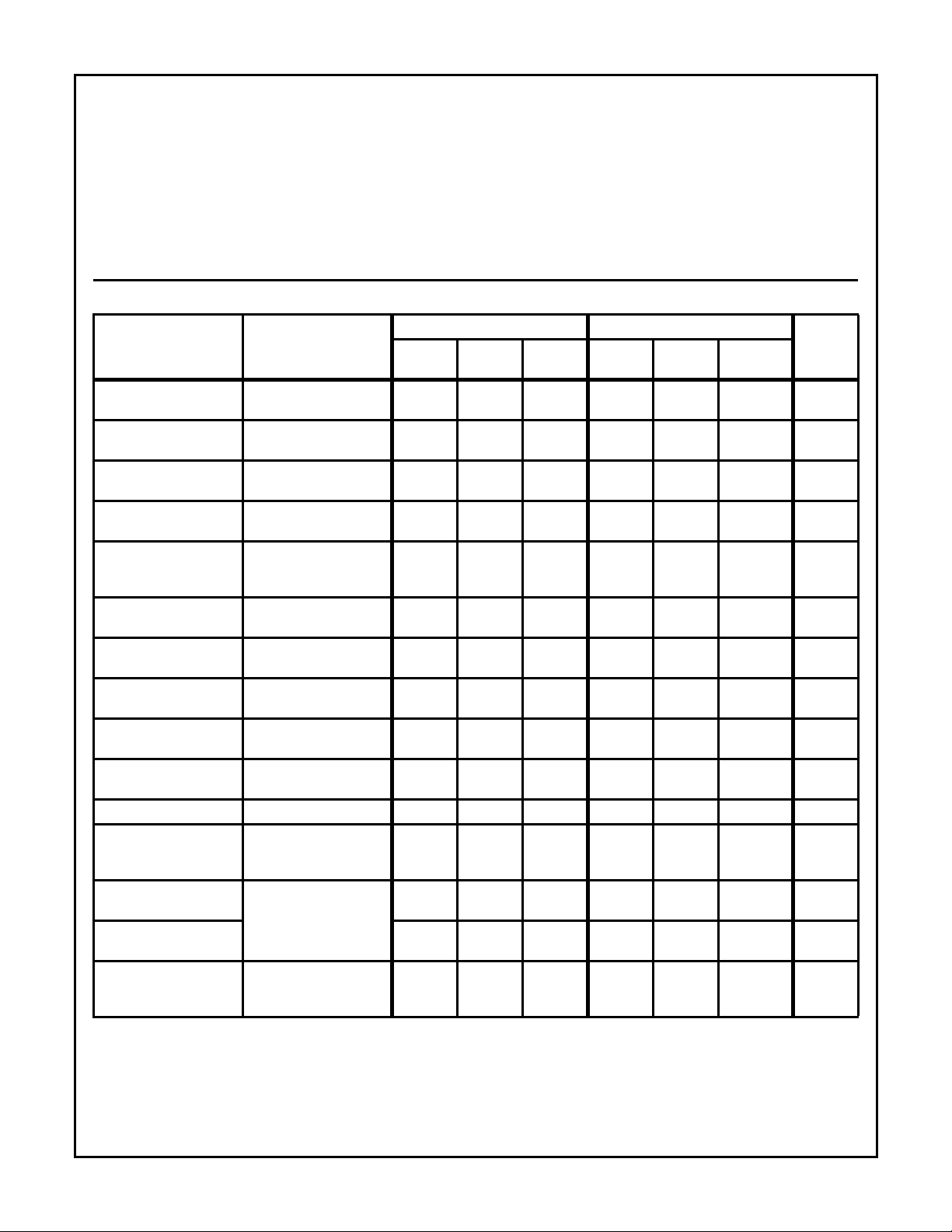

Specifications DG200

Absolute Maximum Ratings Thermal Information

V+, V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <36V

V+ - VD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <30V

VD - V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <30V

VD - VS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <28V

VIN - GND. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <20V

Storage Temperature Range . . . . . . . . . . . . . . . . . -65oC to +150oC

Lead Temperature (Soldering 10s). . . . . . . . . . . . . . . . . . . . +300oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Thermal Resistance θ

JA

Ceramic DIP Package. . . . . . . . . . . . . . . 95oC/W 24oC/W

Plastic DIP Package . . . . . . . . . . . . . . . . 100oC/W -

Metal Can Package. . . . . . . . . . . . . . . . . 136oC/W 65oC/W

Operating Temperature Range

“A” Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-55oC to +125oC

“B” Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-25oC to +85oC

“C” Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to +70oC

θ

JC

Electrical Specifications (T

= +25oC, V+ = +15V, V- = -15V)

A

MILITARY COMMERCIAL / INDUSTRIAL

PARAMETER TEST CONDITIONS

Input Logic Current,

I

IN(ON)

Input Logic Current,

I

N(OFF)

Drain-Source On Resistance, r

DS(ON)

VIN = 0.8V (Notes 2, 3)

VIN = 2.4V (Notes 2, 3) ±10 ±1 ±10 - ±10 ±10 µA

IS = 10mA, V

±10V

Channel-to-Channel

r

Match, r

DS(ON)

DS(ON)

Minimum Analog Signal

ANALOG

o

C +25oC +125oC

10

±

=

70 70 100 80 80 100 Ω

±1 ±10 - ±10 ±10 µA

0oC TO

-25oC +25oC

- 25 (Typ) - - 30 (Typ) - Ω

- ±15V - - ±15V - V

+70oC TO

+85oC

UNITS-55

Handling Capability,

V

ANALOG

Switch OFF Leakage

Current, I

D(OFF)

Switch OFF Leakage

Current, I

S(OFF)

Switch ON Leakage Current, I

D(ON)

+ I

S(ON)

Switch “ON” Time

(Note 1), t

ON

Switch “OFF” Time, t

V

V

= -14V to +14V - ±2 100 -

ANALOG

= -14V to +14V - ±2 100 - ±5 100 nA

ANALOG

5

±

100 nA

VD = VS = -14V to +14V - ±2 200 - ±10 200 nA

RL = 1kΩ, V

ANALOG

=

- 1.0 - - 1.0 - µs

-10V to +10V (Figure 5)

OFFRL

= 1kΩ, V

ANALOG

=

- 0.5 - - 0.5 - µs

-10V to +10V (Figure 5)

Charge Injection, Q

Minimum Off Isolation

Rejection Ratio, OIRR

Figure 6 - 15 (Typ) - - 20 (Typ) - mV

(INJ.)

f = 1MHz, RL = 100Ω,

- 54 (Typ) - - 50 (Typ) - dB

CL≤ 5pF

(Figure 7, Note 1)

+Power Supply

Quiescent Current, I

-Power Supply

Quiescent Current, I

Minimum Channel to

VIN = 0V or VIN = 5V 1000 1000 2000 1000 1000 2000 µA

V1

1000 1000 2000 1000 1000 2000 µA

V2

One Channel Off - 54 (Typ) - - 50 (Typ) - dB

Channel Cross Coupling

Rejection Ratio, CCRR

NOTES:

1. Pull Down Resistor must be ≤ 2kΩ.

2. Typical values are for design aid only, not guaranteed and not subject to production testing.

3. All channels are turned off by high “1” logic inputs and all channels are turned on by low “0” inputs; however 0.8V to 2.4V describes the

minimum range for switching properly. Peak input current required for transition is typically -120µA.

9-15

Loading...

Loading...