Harris Semiconductor CA3130T, CA3130M96, CA3130M, CA3130E, CA3130BT Datasheet

...

SEMICONDUCTOR

3-64

November 1996

CA3130, CA3130A

15MHz, BiMOS Operational Amplifier

with MOSFET Input/CMOS Output

Features

• MOSFET Input Stage Provides:

- Very High Z

I

= 1.5 TΩ (1.5 x 1012Ω) (Typ)

- Very Low I

I

= 5pA (Typ) at 15V Operation

= 2pA (Typ) at 5V Operation

• Ideal for Single-Supply Applications

• Common-Mode Input-Voltage Range Includes

Negative Supply Rail; Input Terminals can be Swung

0.5V Below Negative Supply Rail

• CMOS Output Stage Permits Signal Swing to Either

(or both) Supply Rails

Applications

• Ground-Referenced Single Supply Amplifiers

• Fast Sample-Hold Amplifiers

• Long-Duration Timers/Monostables

• High-Input-Impedance Comparators

(Ideal Interface with Digital CMOS)

• High-Input-Impedance Wideband Amplifiers

• V oltage Followers (e.g. Follower f or Single-Supply D/A

Converter)

• V oltage Regulators (P ermits Contr ol of Output Voltage

Down to 0V)

• Peak Detectors

• Single-Supply Full-Wave Precision Rectifiers

• Photo-Diode Sensor Amplifiers

Description

CA3130A and CA3130 are op amps that combine the

advantage of both CMOS and bipolar transistors.

Gate-protected P-Channel MOSFET (PMOS) transistors are

used in the input circuit to provide very-high-input

impedance, very-low-input current, and exceptional speed

performance. The use of PMOS transistors in the input stage

results in common-mode input-voltage capability down to

0.5V below the negative-supply terminal, an important

attribute in single-supply applications.

A CMOS transistor-pair, capable of swinging the output voltage to within 10mV of either supply-voltage terminal (at very

high values of load impedance), is employed as the output

circuit.

The CA3130 Series circuits operate at supply voltages

ranging from 5V to 16V, (±2.5V to ±8V). They can be phase

compensated with a single external capacitor, and have terminals for adjustment of offset voltage for applications

requiring offset-null capability. Terminal provisions are also

made to permit strobing of the output stage.

The CA3130A offers superior input characteristics over

those of the CA3130.

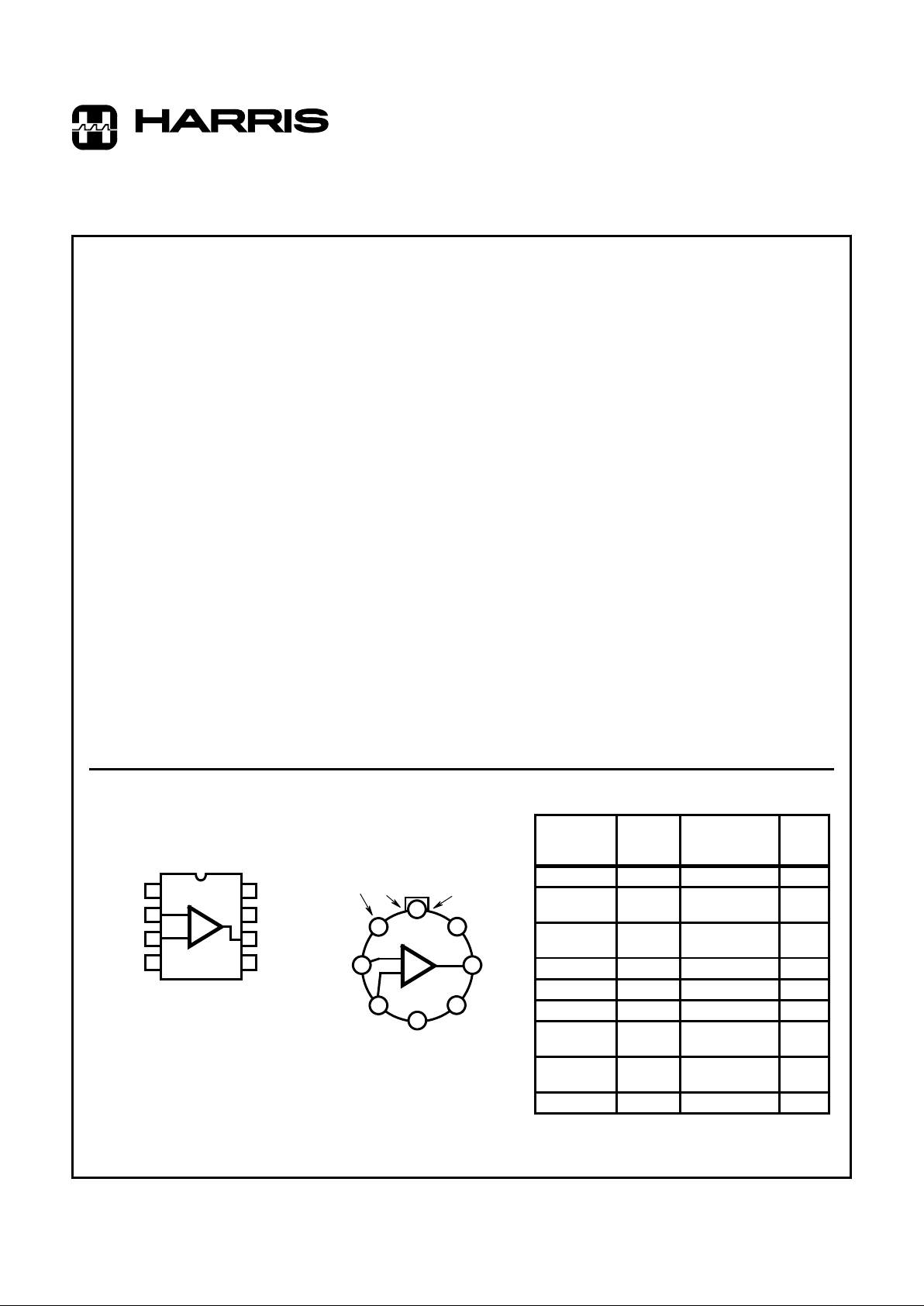

Pinouts

CA3131, CA3130A

(PDIP, SOIC)

TOP VIEW

CA3130, CA3130A

(METAL CAN)

TOP VIEW

OFFSET

INV.

NON-INV.

V-

1

2

3

4

8

7

6

5

STROBE

V+

OUTPUT

OFFSET

-

+

NULL

INPUT

INPUT

NULL

TAB

OUTPUT

INV.

V- AND CASE

OFFSET

NON-INV.

V

+

OFFSET

2

4

6

1

3

7

5

8

-

+

STROBE

PHASE

COMPENSATION

NULL

INPUT

INPUT

NULL

Ordering Information

PART NO.

(BRAND)

TEMP.

RANGE

(oC) PACKAGE

PKG.

NO.

CA3130AE

-55 to 125 8 Ld PDIP

E8.3

CA3130AM

(3130A)

-55 to 125 8 Ld SOIC

M8.15

CA3130AM96

(3130A)

-55 to 125 8 Ld SOIC (Note)

M8.15

CA3130AT

-55 to 125 8 Pin Metal Can

T8.C

CA3130BT

-55 to 125 8 Pin Metal Can

T8.C

CA3130E

-55 to 125 8 Ld PDIP

E8.3

CA3130M

(3130)

-55 to 125 8 Ld SOIC

M8.15

CA3130M96

(3130)

-55 to 125 8 Ld SOIC (Note)

M8.15

CA3130T

-55 to 125 8 Pin Metal Can

T8.C

NOTE: Denotes Tape and Reel.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1996

File Number 817.3

3-65

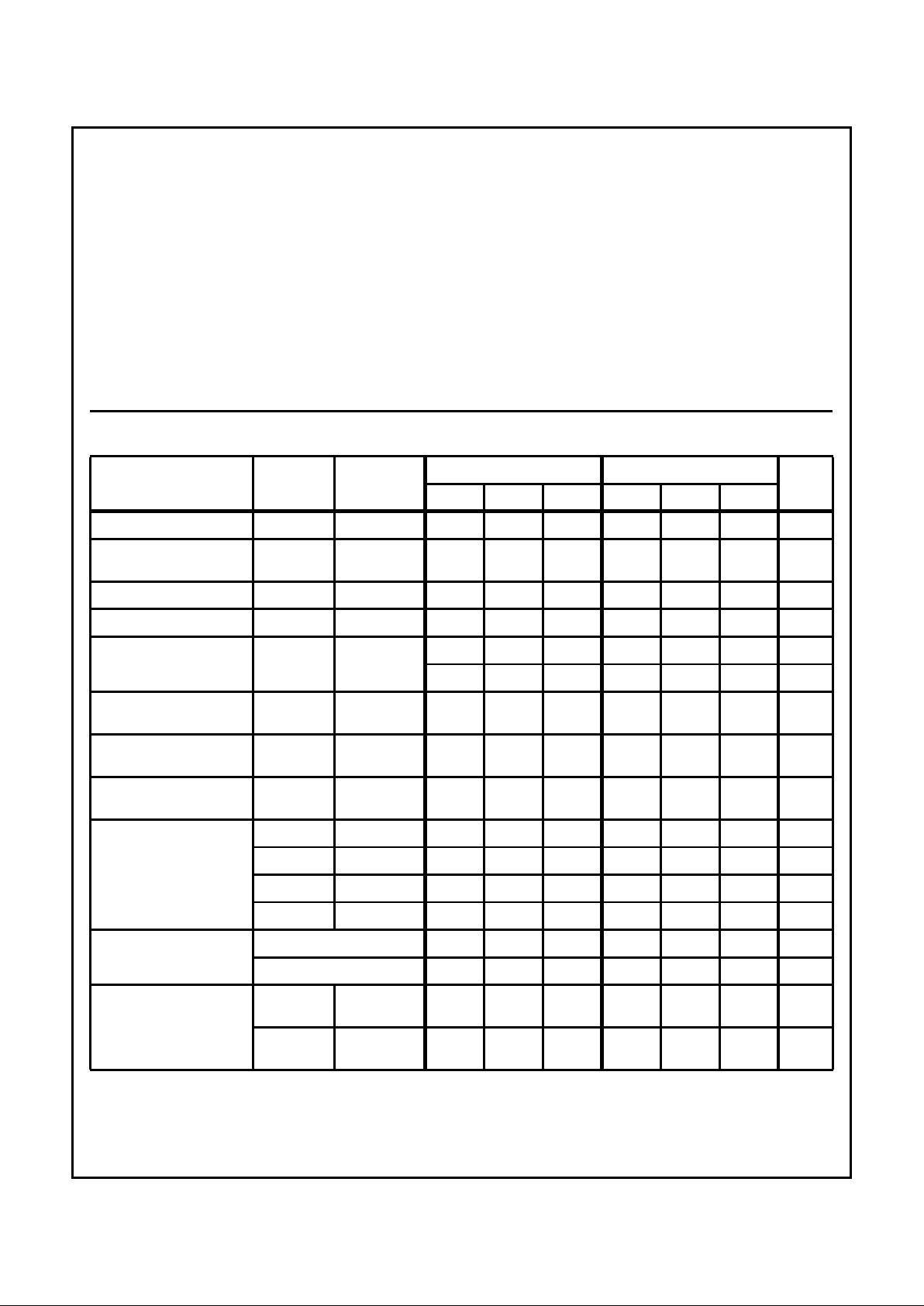

Absolute Maximum Ratings Thermal Information

DC Supply Voltage (Between V+ And V- Terminals) . . . . . . . . . 16V

Differential Input Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8V

DC Input Voltage . . . . . . . . . . . . . . . . . . . . . . (V+ +8V) to (V- -0.5V)

Input-Terminal Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1mA

Output Short-Circuit Duration (Note 1). . . . . . . . . . . . . . . . Indefinite

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . -50oC to 125oC

Thermal Resistance (Typical, Note 2) θJA (oC/W) θJC (oC/W)

PDIP Package. . . . . . . . . . . . . . . . . . . 100 N/A

SOIC Package. . . . . . . . . . . . . . . . . . . 160 N/A

Metal Can Package. . . . . . . . . . . . . . . 170 85

Maximum Junction Temperature (Metal Can Package). . . . . . .175oC

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. Short circuit may be applied to ground or to either supply.

2. θJA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications T

A

= 25oC, V+ = 15V, V- = 0V, Unless Otherwise Specified

PARAMETER SYMBOL

TEST

CONDITIONS

CA3130 CA3130A

UNITSMIN TYP MAX MIN TYP MAX

Input Offset Voltage |V

IO

|V

S

= ±7.5V - 8 15 - 2 5 mV

Input Offset Voltage

Temperature Drift

∆V

IO

/∆T - 10 - - 10 - µV/oC

Input Offset Current |I

IO

|V

S

= ±7.5V - 0.5 30 - 0.5 20 pA

Input Current I

I

VS = ±7.5V - 5 50 - 5 30 pA

Large-Signal Voltage Gain A

OL

VO = 10V

P-P

RL = 2kΩ

50 320 - 50 320 - kV/V

94 110 - 94 110 - dB

Common-Mode

Rejection Ratio

CMRR 70 90 - 80 90 - dB

Common-Mode Input

Voltage Range

V

ICR

0 -0.5 to

12

10 0 -0.5 to

12

10 V

Power-Supply

Rejection Ratio

∆V

IO

/∆VSVS = ±7.5V - 32 320 - 32 150 µV/V

Maximum Output Voltage V

OM

+R

L

= 2kΩ 12 13.3 - 12 13.3 - V

V

OM

-R

L

= 2kΩ - 0.002 0.01 - 0.002 0.01 V

V

OM

+R

L

= ∞ 14.99 15 - 14.99 15 - V

V

OM

-R

L

= ∞ - 0 0.01 - 0 0.01 V

Maximum Output Current I

OM

+ (Source) at VO = 0V 12 22 45 12 22 45 mA

I

OM

- (Sink) at VO = 15V 12 20 45 12 20 45 mA

Supply Current I+ V

O

= 7.5V,

RL = ∞

- 10 15 - 10 15 mA

I+ V

O

= 0V,

RL = ∞

-23-23mA

CA3130, CA3130A

3-66

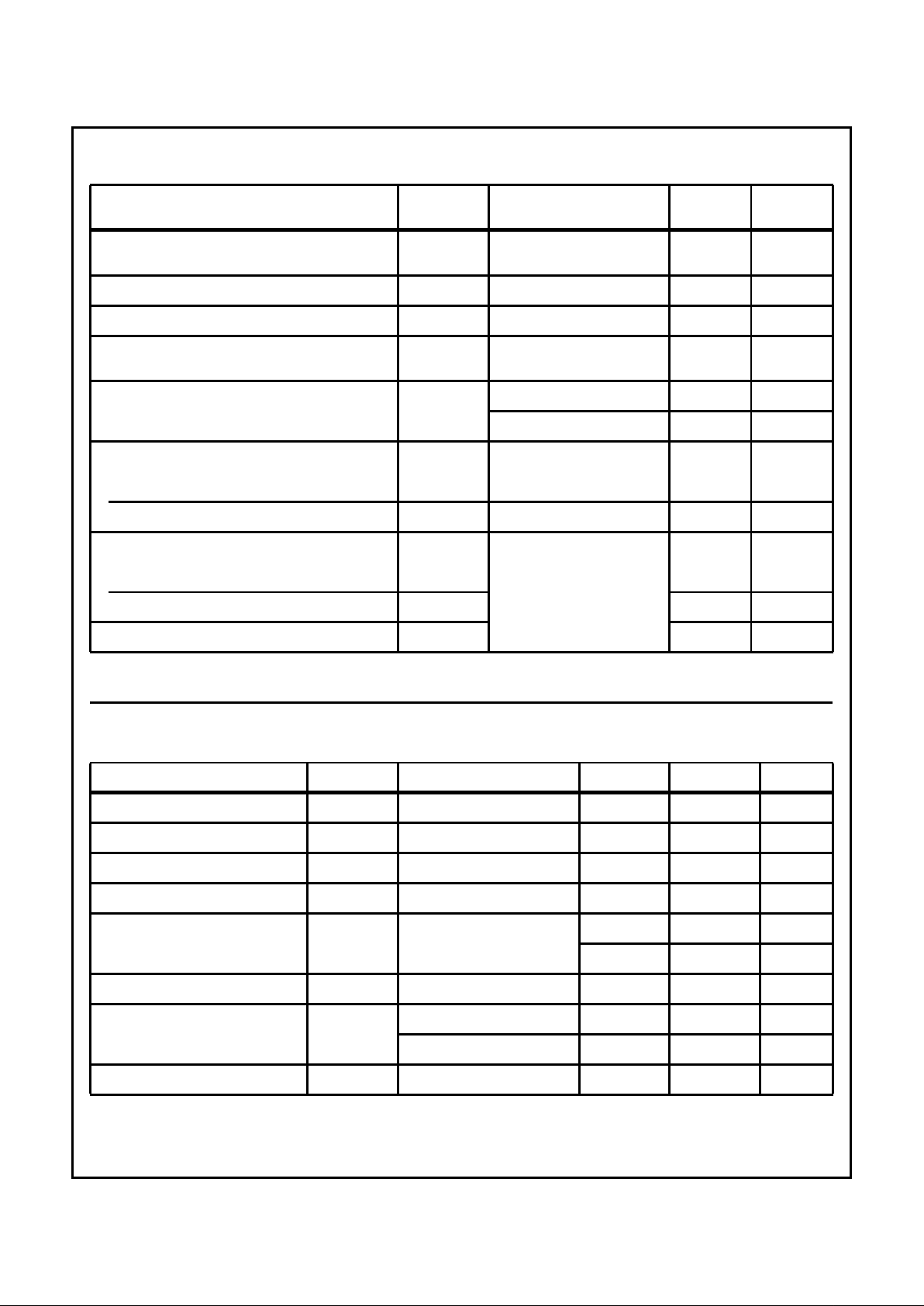

Electrical Specifications Typical Values Intended Only for Design Guidance, V

SUPPLY

= ±7.5V, TA = 25oC

Unless Otherwise Specified

PARAMETER SYMBOL TEST CONDITIONS

CA3130,

CA3130A UNITS

Input Offset Voltage Adjustment Range 10kΩ Across Terminals 4 and 5

or 4 and 1

±22 mV

Input Resistance R

I

1.5 TΩ

Input Capacitance C

I

f = 1MHz 4.3 pF

Equivalent Input Noise Voltage e

N

BW = 0.2MHz, RS = 1MΩ

(Note 3)

23 µV

Open Loop Unity Gain Crossover Frequency

(For Unity Gain Stability ≥47pF Required.) f

T

CC = 0 15 MHz

CC = 47pF 4 MHz

Slew Rate: SR

CC = 0 30 V/µsOpen Loop

Closed Loop CC = 56pF 10 V/µs

Transient Response: CC = 56pF,

CL = 25pF,

RL = 2kΩ

(Voltage Follower)

0.09 µsRise Time t

r

Overshoot OS 10 %

Settling Time (To <0.1%, VIN = 4V

P-P

)t

S

1.2 µs

NOTE:

3. Although a 1MΩ source is used for this test, the equivalent input noise remains constant for values of RS up to 10MΩ.

Electrical Specifications Typical Values Intended Only for Design Guidance, V+ = 5V, V- = 0V, T

A

= 25oC

Unless Otherwise Specified (Note 4)

PARAMETER SYMBOL TEST CONDITIONS CA3130 CA3130A UNITS

Input Offset Voltage V

IO

82mV

Input Offset Current I

IO

0.1 0.1 pA

Input Current I

I

22pA

Common-Mode Rejection Ratio CMRR 80 90 dB

Large-Signal Voltage Gain A

OL

VO = 4V

P-P

, RL = 5kΩ 100 100 kV/V

100 100 dB

Common-Mode Input Voltage Range V

ICR

0 to 2.8 0 to 2.8 V

Supply Current I+ VO = 5V, RL = ∞ 300 300 µA

VO = 2.5V, RL = ∞ 500 500 µA

Power Supply Rejection Ratio ∆VIO/∆V+ 200 200 µV/V

NOTE:

4. Operation at 5V is not recommended for temperatures below 25oC.

CA3130, CA3130A

3-67

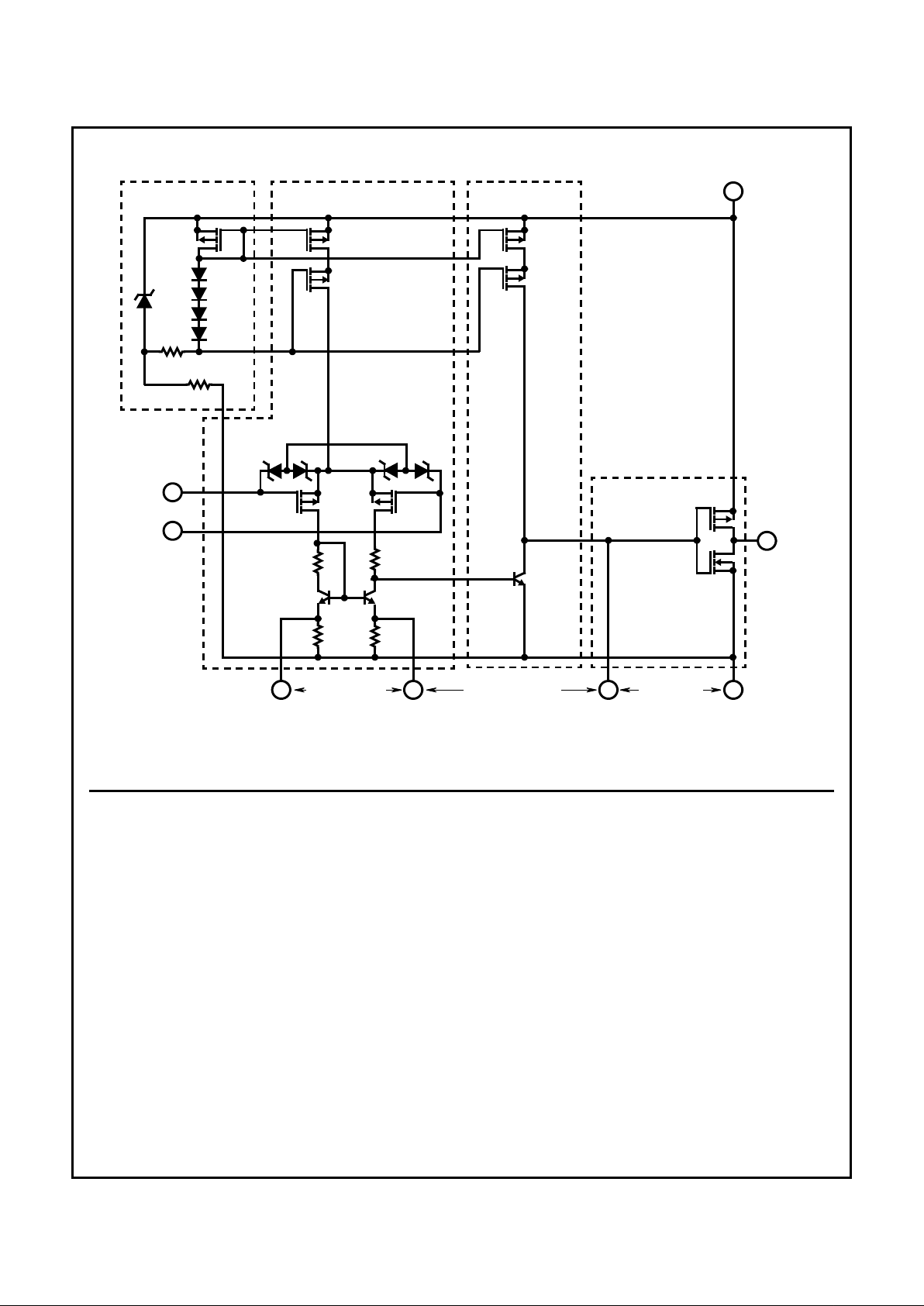

Schematic Diagram

Application Information

Circuit Description

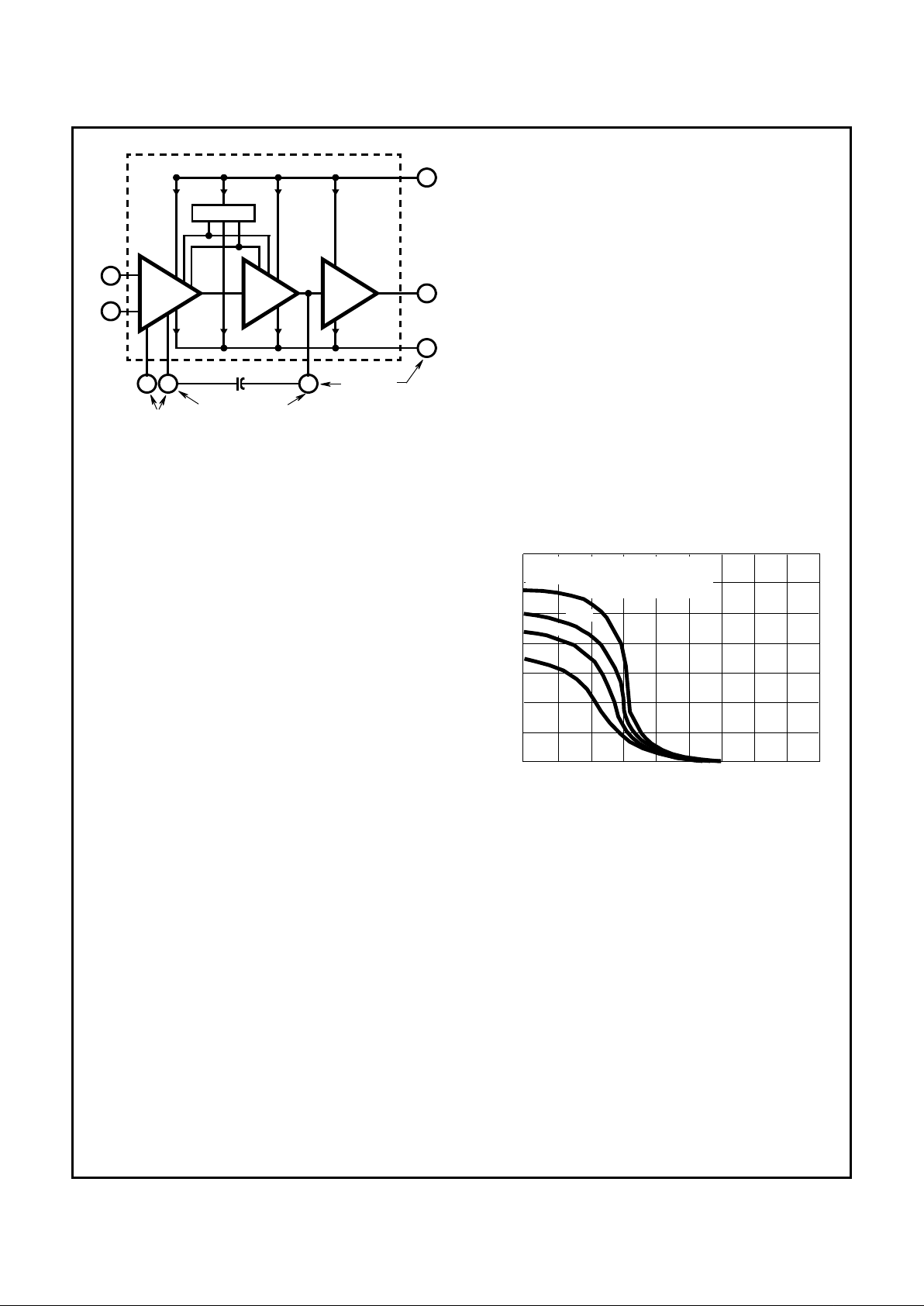

Figure 1 is a block diagram of the CA3130 Series CMOS

Operational Amplifiers. The input terminals may be operated

down to 0.5V below the negative supply rail, and the output

can be swung very close to either supply rail in many

applications. Consequently, the CA3130 Series circuits are

ideal for single-supply operation. Three Class A amplifier

stages, having the individual gain capability and current

consumption shown in Figure 1, provide the total gain of the

CA3130. A biasing circuit provides two potentials for

common use in the first and second stages. Terminal 8 can

be used both for phase compensation and to strobe the output stage into quiescence. When Terminal 8 is tied to the

negative supply rail (Terminal 4) by mechanical or electrical

means, the output potential at Terminal 6 essentially rises to

the positive supply-rail potential at Terminal 7. This condition

of essentially zero current drain in the output stage under the

strobed “OFF” condition can only be achieved when the

ohmic load resistance presented to the amplifier is very high

(e.g.,when the amplifier output is used to drive CMOS digital

circuits in Comparator applications).

Input Stage

The circuit of the CA3130 is shown in the schematic diagram.

It consists of a differential-input stage using PMOS field-effect

transistors (Q

6

, Q7) working into a mirror-pair of bipolar tran-

sistors (Q

9

, Q10) functioning as load resistors together with

resistors R

3

through R6. The mirror-pair transistors also function as a differential-to-single-ended conv erter to provide base

drive to the second-stage bipolar transistor (Q

11

). Offset nulling, when desired, can be effected by connecting a 100,000Ω

potentiometer across Terminals 1 and 5 and the potentiometer slider arm to Terminal 4. Cascade-connected PMOS

transistors Q

2

, Q4 are the constant-current source for the

input stage. The biasing circuit for the constant-current source

is subsequently described. The small diodes D

5

through D

8

provide gate-oxide protection against high-voltage transients,

including static electricity during handling for Q

6

and Q7.

3

2

1 8 4

6

7

Q

1

Q

2

Q

4

D

1

D

2

D

3

D

4

Q

3

Q

5

D5D

6

D7D

8

Q

9

Q

10

Q

6

Q

7

5

Z

1

8.3V

INPUT STAGE

R

3

1kΩ

R

4

1kΩ

R

6

1kΩ

R

5

1kΩ

NON-INV.

INPUT

INV.-INPUT

+

-

R

1

40kΩ

5kΩ

R

2

BIAS CIRCUIT

CURRENT SOURCE FOR

“CURRENT SOURCE

LOAD” FOR Q

11

Q6AND Q

7

V+

OUTPUT

OUTPUT

STAGE

Q

8

Q

12

V-

Q

11

SECOND

STAGE

OFFSET NULL

COMPENSATION STROBING

(NOTE 5)

NOTE:

5. Diodes D5 through D8 provide gate-oxide protection for MOSFET input stage.

CA3130, CA3130A

3-68

Second-Stage

Most of the voltage gain in the CA3130 is provided by the

second amplifier stage, consisting of bipolar transistor Q

11

and its cascade-connected load resistance provided by

PMOS transistors Q

3

and Q5. The source of bias potentials

for these PMOS transistors is subsequently described. Miller

Effect compensation (roll-off) is accomplished by simply

connecting a small capacitor between Terminals 1 and 8. A

47pF capacitor provides sufficient compensation for stable

unity-gain operation in most applications.

Bias-Source Circuit

At total supply voltages, somewhat above 8.3V, resistor R

2

and zener diode Z1 serve to establish a voltage of 8.3V across

the series-connected circuit, consisting of resistor R

1

, diodes

D

1

through D4, and PMOS transistor Q1. A tap at the junction

of resistor R

1

and diode D4 provides a gate-bias potential of

about 4.5V for PMOS transistors Q

4

and Q5 with respect to

Terminal 7. A potential of about 2.2V is developed across

diode-connected PMOS transistor Q

1

with respect to Terminal

7 to provide gate bias for PMOS transistors Q

2

and Q3. It

should be noted that Q

1

is “mirror-connected (see Note 8)” to

both Q

2

and Q3. Since transistors Q1, Q2, Q3 are designed to

be identical, the approximately 200µA current in Q

1

estab-

lishes a similar current in Q

2

and Q3 as constant current

sources for both the first and second amplifier stages, respectively.

At total supply voltages somewhat less than 8.3V, zener

diode Z

1

becomes nonconductive and the potential,

developed across series-connected R

1

, D1-D4, and Q1, varies directly with variations in supply voltage. Consequently,

the gate bias for Q

4

, Q5 and Q2, Q3 varies in accordance

with supply-voltage variations. This variation results in

deterioration of the power-supply-rejection ratio (PSRR) at

total supply voltages below 8.3V. Operation at total supply

voltages below about 4.5V results in seriously degraded

performance.

Output Stage

The output stage consists of a drain-loaded inverting amplifier using CMOS transistors operating in the Class A mode.

When operating into very high resistance loads, the output

can be swung within millivolts of either supply rail. Because

the output stage is a drain-loaded amplifier, its gain is

dependent upon the load impedance. The transfer characteristics of the output stage for a load returned to the negative supply rail are shown in Figure 2. Typical op amp loads

are readily driven by the output stage. Because large-signal

excursions are non-linear , requiring feedback for good wa veform reproduction, transient delays may be encountered. As

a voltage follower, the amplifier can achieve 0.01% accuracy

levels, including the negative supply rail.

NOTE:

8. For general information on the characteristics of CMOS transistor-pairs in linear-circuit applications, see File Number 619, data

sheet on CA3600E “CMOS Transistor Array”.

Input Current Variation with Common Mode Input

Voltage

As shown in the Table of Electrical Specifications, the input

current for the CA3130 Series Op Amps is typically 5pA at

T

A

= 25oC when Terminals 2 and 3 are at a common-mode

potential of +7.5V with respect to negative supply Terminal 4.

Figure 3 contains data showing the variation of input current

as a function of common-mode input voltage at T

A

=25oC.

These data show that circuit designers can advantageously

exploit these characteristics to design circuits which typically

require an input current of less than 1pA, provided the common-mode input voltage does not exceed 2V. As previously

noted, the input current is essentially the result of the leakage

current through the gate-protection diodes in the input circuit

and, therefore, a function of the applied voltage. Although the

finite resistance of the glass terminal-to-case insulator of the

3

2

7

4

815

6

BIAS CKT.

COMPENSATION

(WHEN REQUIRED)

AV≈ 5X

AV≈

A

V

≈

6000X

30X

INPUT

+

-

200µA 200µA

1.35mA

8mA

0mA

V+

OUTPUT

V-

STROBE

C

C

OFFSET

NULL

CA3130

(NOTE 7)

(NOTE 5)

NOTES:

6. Total supply voltage (for indicated voltage gains) = 15V with input

terminals biased so that Terminal 6 potential is +7.5V above Terminal 4.

7. Total supply voltage (for indicated voltage gains) = 15V with output terminal driven to either supply rail.

FIGURE 1. BLOCK DIAGRAM OF THE CA3130 SERIES

22.5

GATE VOLTAGE (TERMINALS 4 AND 8) (V)

OUTPUT VOLTAGE (TERMINALS 4 AND 8) (V)

17.5 2012.5 15107.52.5 50

2.5

7.5

5

10

15

12.5

17.5

0

SUPPLY VOLTAGE: V+ = 15, V- = 0V

T

A

= 25oC

LOAD RESISTANCE = 5kΩ

500Ω

1kΩ

2kΩ

FIGURE 2. VOL T A GE TRANSFER CHARA CTERISTICS OF

CMOS OUTPUT STAGE

CA3130, CA3130A

Loading...

Loading...