Harris Semiconductor CA3126M1, CA3126E Datasheet

May 1999

OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

Call Central Applications 1-800-442-7747

or email: centapp@harris.com

CA3126

TV Chroma Processor

[ /Title

(CA31

26)

/Subject

(TV

Chrom

a Processor)

/Autho

r ()

/Keywords

(Harris

Semiconductor,

TV

chroma

processor,

subcarrier

regeneration,

ntsc,

acc,

overload

detector,

keyed

chroma

output,

color

processor,

industrial

Features

• Phase Locked Subcarrier Regeneration Utilizes

Sample-and-Hold Techniques

• Automatic Chrominance Control (ACC)/Killer Detector

Employs Sample-and-Hold Techniques

• Supplementary ACC with an Overload Detector to

Prevent Oversaturation of this Picture Tube

• Sinusoidal Subcarrier Output

• Keyed Chroma Output

• Emitter Follower Buffered Outputs for Low Output

Impedance

• Linear DC Saturation Control

Applications

• TV/CATV Receiver Circuits

• NTSC Color Decoder/Processor

• Computer Graphics Subcarrier Regenerator

• Timing Reference for Frame Grabbers

• DSP Clock Timing Reference Source

Pinouts

CA3126

(PDIP)

TOP VIEW

CHROMA GAIN CONT.

CHROMA IN

AFPC FILTER +

AFPC FILTER -

RF BYPASS

GROUND

VCO OUT

VCO IN

CARRIER OUT

1

2

3

4

5

6

7

8

16

15

CHROMA OUT

14

ZENER REF

13

OVERLOAD DET.

12

V+

11

ACC+

10

ACC-

9

HORIZ. KEY IN

Description

The Harris CA3126 is a monolithic silicon integrated circuit

designed for TV chroma processing and is ideally suited for

NTSC color graphic applications that require subcarrier

regeneration of the color burst signal.

Part Number Information

TEMP.

PART NUMBER

CA3126E -40 to 85 16 Ld PDIP E16.3

CA3126M1 -40 to 85 20 Ld SOIC M20.3

CHROMA IN

AFPC FILTER +

AFPC FILTER -

RF BYPASS

GROUND

VCO OUT

VCO IN

RANGE (oC) PACKAGE

CA3126

(SOIC)

TOP VIEW

1

2

NC

3

4

5

6

7

8

9

NC

NC

10

CHROMA GAIN CONT.

20

CHROMA OUT

19

NC

18

ZENER REF

17

OVERLOAD DET.

16

V+

15

ACC +

14

ACC -

13

12

HORIZ. KEY IN

11

CARRIER OUT

PKG.

NO.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1999

8-33

File Number 860.5

CA3126

Absolute Maximum Ratings Thermal Information

DC Supply Voltage (V+ to GND) (Note 1). . . . . . . . . . . . . . . . .13.2V

DC Current:

Into V+ Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38mA

Into Zener Reference Pin . . . . . . . . . . . . . . . . . . . . . . . . . . .20mA

DC Voltage (Horizontal Key In)

Negative Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -5V

Positive Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3V

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. This rating does not apply when using the internal zener reference in conjunction with an external pass transistor.

2. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 1) θJA (oC/W)

PDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Maximum Junction Temperature (Plastic Packages) . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

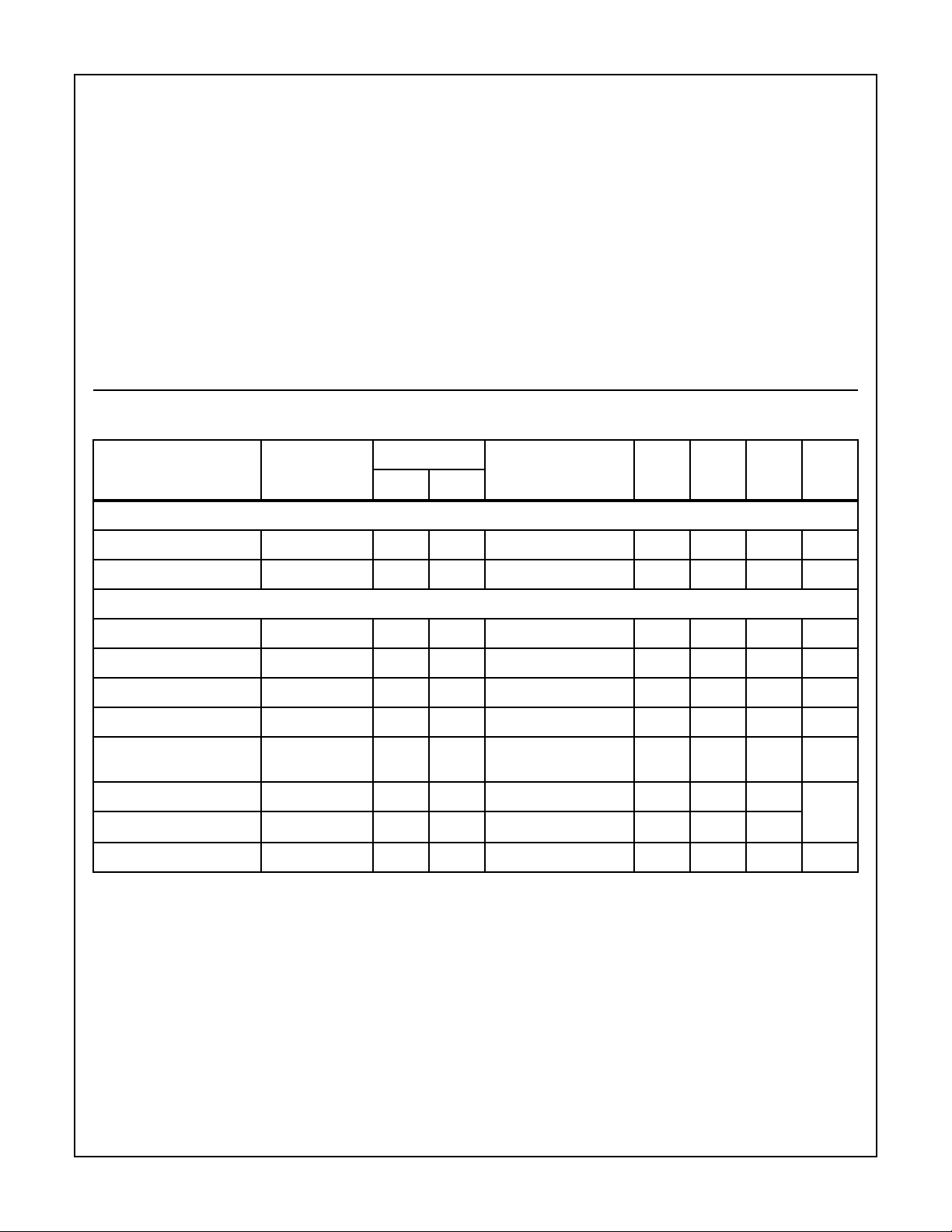

Electrical Specifications T

= 25oC, Chroma Gain Control at maximum position for all tests except as noted. Electrical

A

specifications referenced to test circuit.

TERMINAL,

SWITCH POS.

MEASUREMENT

PARAMETER

AND SYMBOL

1

S

V

2

CHROMA

INPUT TP

MIN TYP MAX

1

DC ELECTRICAL SPECIFICATIONS

Voltage Regulator V

Supply Current I

12

12

2 2 0 10.1 11.2 12.1 V

2 2 0 162538mA

SWITCHING ELECTRICAL SPECIFICATIONS (Note 3)

Pull-In Range (Note 4) V

Oscillator Output V

100% Chroma Output V

Overload Detector V

Minimum Chroma Output

8

8

15

15

V

15

(Note 6) 2 0.5V

P-P

±250 - - Hz

2 2 0 0.6 1.0 - V

1 2 0.5V

1 1 0.5V

1 2 0.5V

P-P

P-P

P-P

1.4 2.7 - V

0.4 - 0.7 V

- - 20 mV

(Note 5)

200% Chroma Output V

20% Chroma Output V

Kill Level V

15

15

TP1

12 1V

1 2 0.1V

P-P

P-P

70 100 140 % of

40 - 105

1 2 Vary 5 - 60 mV

NOTES:

3. Except for pull-in range testing, tune oscillator trimmer capacitor for free running frequency of 3.579545MHz±10Hz.

4. Set Switch 1 to Position 2, detune oscillator±250Hz, set Switch 1 to Position 1, and check for oscillator pull-in.

5. Set Chroma Gain Control to minimum position (CCW).

UNITSS

P-P

P-P

P-P

P-P

100%

Reading

P-P

8-34

Test Circuit

CA3126

+24V

CW

10kΩ

CCW

CHROMA

GAIN

CONTROL

V

REG

47kΩ

1µF

0.01µF

TP

CHROMA

INPUT

SIGNAL

10kΩ

3.9kΩ

16 15 14 13

1 2 3 4 5 6 7 8

2

kΩ

2.45kΩ

1

S

1

1

0.1µF

0.01µF 0.01µF 0.01µF

2

50Ω

270Ω

2N2102

1

2

S

2

0.01µF

12 11 10 9

CA3126

VARIABLE

ATTENUATOR

0.05µF

I

XTAL

3.579545MHz

0.02µF 0.02µF

1µF

680Ω

10pF

NPO

TEST SIGNAL

GENERATOR

20pF

N750

0.01µF

33pF

N750

BURST

SYNC.

OSCILLOSCOPE

2kΩ

COUNTER

SUBCARRIER

OUTPUT

KEY

PULSE

PULSE

GENERATOR

Pin numbers refer to the PDIP package.

(A) Chroma input signal

(B) Key pulse input signal

(A)

(B)

2.5µs

BURST

63.5µs

3.579545MHz

4µs

5µs CENTERED ON BURST

0.46V

1.0V

V

CHROMA

PEAK

CHROMA

(MIN)

8-35

Loading...

Loading...