S8380/S8381 series are designed to have higher sensitivity in the infrared and soft X-ray regions when compared to standard NMOS linear image

sensors. The peak sensitivity wavelength is in the near IR region (λp=750 nm).

The photodiodes of S8380 series have a height of 2.5 mm and are arrayed in a row at a spacing of 50 µm. The photodiodes of S8381 series also

have a height of 2.5 mm but are arrayed at a spacing of 25 µm. The photodiodes are available in 3 different pixel quantities for each series, 128

(S8380-128Q), 256 (S8380-256Q, S8381-256Q) and 512 (S8380-512Q, S8381-512Q) and 1024 (S8381-1024Q). Quartz glass is the standard

window material.

Features

l

High sensitivity in the IR and soft X-ray regions

l

Wide active area

Pixel pitch: 50 µm (S8380 series)

25 µm (S8381 series)

Pixel height: 2.5 mm

l

High UV sensitivity with good stability

l

Low dark current and high saturation charge allow a long

integration time and a wide dynamic range at room temperature

l

Excellent output linearity and sensitivity spatial uniformity

l

Lower power consumption: 1 mW Max.

l

Start pulse and clock pulses are CMOS logic compatible

Applications

l

Multichannel spectrophotometry

l

Image readout system

IMAGE SENSOR

NMOS linear image sensor

NMOS linear image sensors with high IR sensitivity

S8380/S8381 series

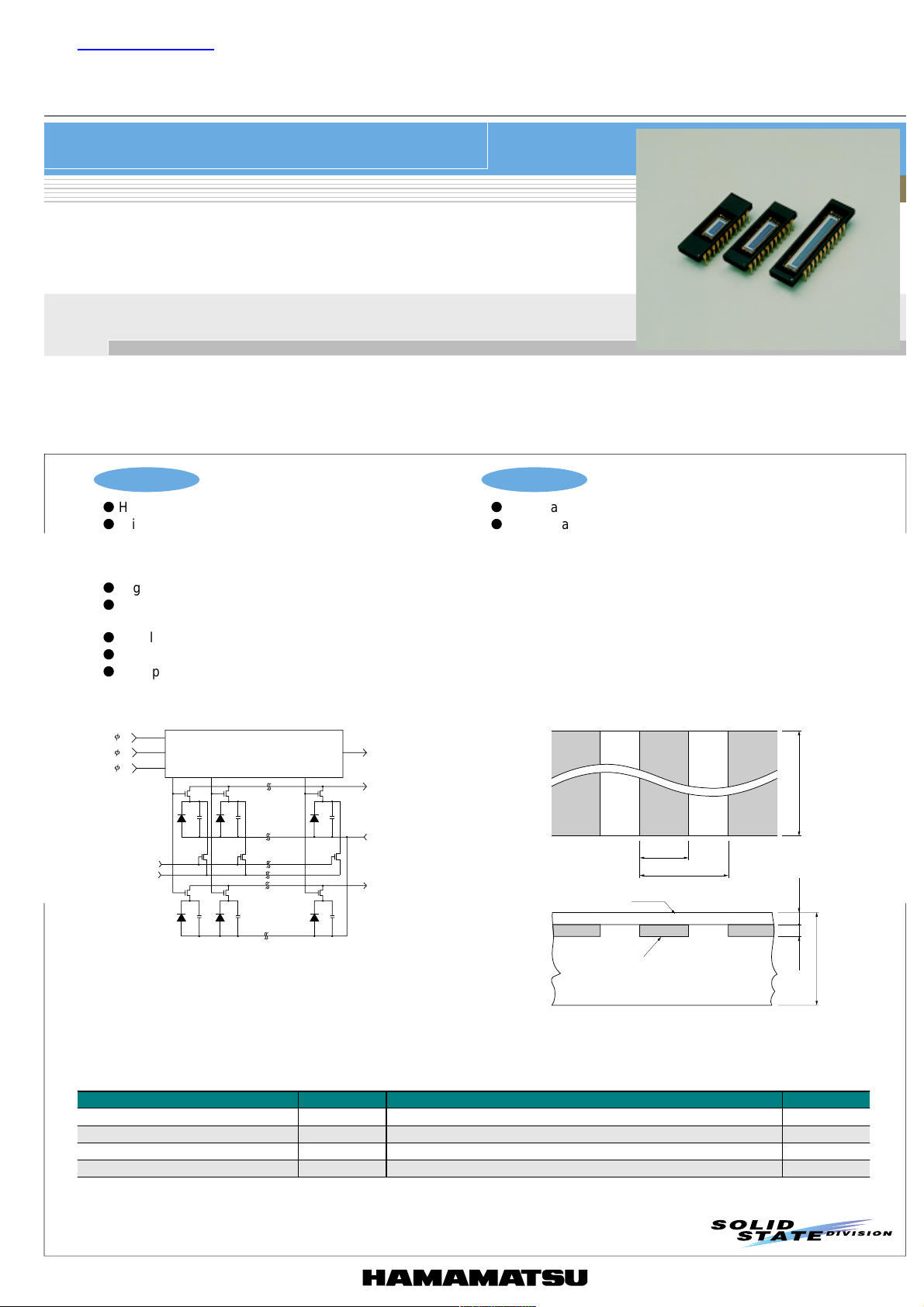

2.5 mm

1.0 µm

1.0 µm

400 µm

OXIDATION SILICON

N TYPE SILICON

P TYPE SILICON

S8380 SERIES: a=50 µm, b=45 µm

S8381 SERIES: a=25 µm, b=20 µm

b

a

KMPDC0020EA

Figure 1 Equivalent circuit

Vss

START st

CLOCK

CLOCK12

ACTIVE

PHOTODIODE

SATURATION

CONTROL GATE

SATURATION

CONTROL DRAIN

DUMMY DIODE

DUMMY VIDEO

ACTIVE VIDEO

END OF SCAN

DIGITAL SHIFT RE

GISTER

(MOS SHIFT RE

GISTER)

Figure 2 Active area structure

KMPDA0125EA

■

Absolute maximum ratings

Parameter Symbol Value Unit

Input pulse (φ1, φ2, φst) voltage Vφ

15 V

Power consumption *

1

P 1 mW

Operating temperature *

2

Topr -40 to +65 °C

Storage temperature Tstg -40 to +85 °C

*1: Vφ=5.0 V

*2: No condensation

1

查询S8380供应商

NMOS linear image sensor

S8380/S8381 series

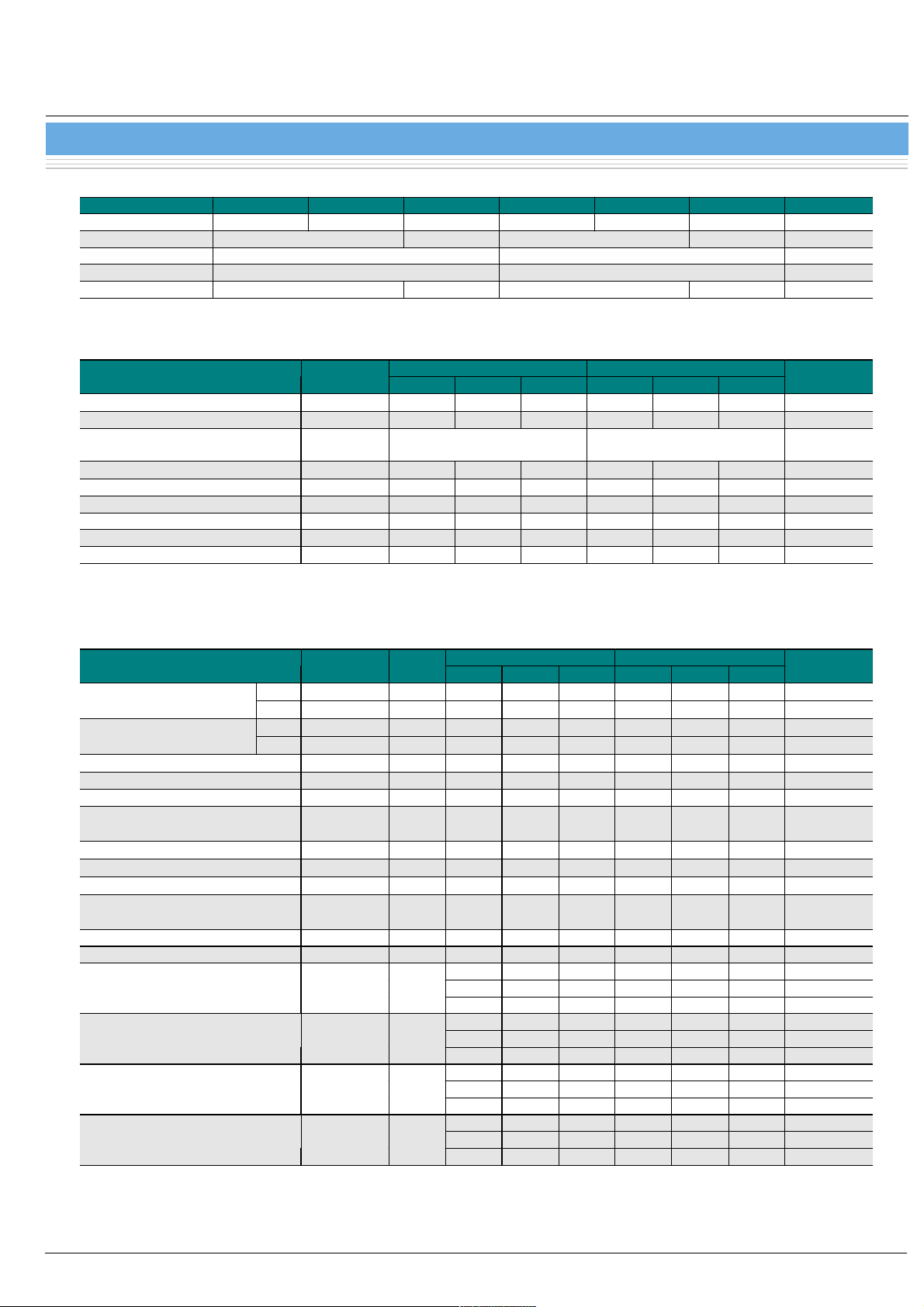

■

Shape specifications

Parameter S8380-128Q S8380-256Q S8380-512Q S8381-256Q S8381-512Q S8381-1024Q Unit

Number of pixels 128 256 512 256 512 1024 -

Package length 31.75 40.6 31.75 40.6 mm

Number of pin 22 22 Window material *

3

Quartz Quartz -

Weight 3.0 3.5 3.0 3.5 g

*3: Fiber optic plate is available.

■

Specifications (Ta=25 °C)

S8380 series S8381 series

Parameter Symbol

Min. Typ. Max. Min. Typ. Max.

Unit

Pixel pitch - -50- -25-

µ

m

Pixel height - - 2.5 - - 2.5 - mm

Spectral response range

(10 % of peak)

λ

200 to 1000 200 to 1000 nm

Peak sensitivity wavelength

λ

p

- 750 - - 750 - nm

Photodiode dark current *

4

I

D

- 0.2 0.6 - 0.1 0.3 pA

Photodiode capacitance *

4

Cph - 20 - - 10 - pF

Saturation exposure *4, *

5

Esat -90- -90-m

lx

· s

Saturation output charge *

4

Qsat - 50 - - 25 - pC

Photo response non-uniformity *

6

PRNU--±3--±3 %

*4: Vb=2.0 V, Vφ=5.0 V

*5: 2856 K, tungsten lamp

*6: 50 % of saturation, excluding the start pixel and last pixel

■

Electrical characteristics (Ta=25 °C)

S8380 series S8381 series

Parameter Symbol

Condition

Min. Typ. Max. Min. Typ. Max.

Unit

High

Vφ1, Vφ2 (H)

4.5 5 10 4.5 5 10 V

Clock pulse (φ1, φ2)

voltage

Low

Vφ1, Vφ2 (L)

0-0.40-0.4 V

High

Vφs (H)

4.5

Vφ1

10 4.5

Vφ1

10 V

Start pulse (φst) voltage

Low

Vφs (L)

0 - 0.4 0 - 0.4 V

Video bias voltage *

7

Vb 1.5

Vφ - 3.0 Vφ - 2.5

1.5

Vφ - 3.0 Vφ - 2.5

V

Saturation control gate voltage Vscg - 0 - - 0 - V

Saturation control drain voltage Vscd - Vb - - Vb - V

Clock pulse (φ1, φ2) rise / fa ll tim e

*

8

trφ1, trφ2

tfφ1, tfφ2

- 20 - - 20 - ns

Clock pulse (φ1, φ2) pulse width tpwφ1, tpwφ2

200 - - 200 - - ns

Start pulse (φst) rise / fall time trφs, tfφs

- 20 - - 20 - ns

Start pulse (φst) pulse width tpwφs

200 - - 200 - - ns

Start pulse (φst) and clock pulse

(φ2) overlap

tφov

200 - - 200 - - ns

Clock pulse space *

8

X1, X

2

trf - 20 - - trf - 20 - - ns

Data rate *

9

f 0.1 - 2000 0.1 - 2000 kHz

-

80 (-128 Q)

--

100 (-256 Q)

-ns

-

120 (-256 Q)

--

150 (-512 Q)

-ns

Video delay time tvd

50 % of

sa tu ratio n

*

9, *10

-

160 (-512 Q)

--

200 (-1024 Q)

-ns

-

21 (-128 Q)

- -

27 (-256 Q)

- pF

-

36 (-256 Q)

- -

50 (-512 Q)

- pF

Clock pulse (φ1, φ2)

line capacitance

C

φ

5 V bias

-

67 (-512 Q)

- -

100 (-1024 Q)

- pF

-

12 (-128 Q)

--

14 (-256 Q)

-pF

-

20 (-256 Q)

--

24 (-512 Q)

-pF

Saturation control gate (Vscg)

line capacitance

Cscg 5 V bias

-

35 (-512 Q)

--

45 (-1024 Q)

-pF

-

7 (-128 Q)

- -

10 (-256 Q)

- pF

-

11 (-256 Q)

- -

16 (-512 Q)

- pFVideo line capacitance C

V

2 V bias

-

20 (-512 Q)

- -

30 (-1024 Q)

- pF

*7: Vφ is input pulse voltage (refer to figure 8).

*8: trf is the clock pulse rise or fall time. A clock pulse space of

“rise time/fall time - 20 ” ns (nanoseconds) or more should be

input if the clock pulse rise or fall time is longer than 20

ns (refer to figure 7).

*9: Vb=2.0 V, Vφ=5.0 V

*10: Measured with C7883 driver circuit.

2

NMOS linear image sensor

S8380/S8381 series

Figure 3 Dimensional outlines (unit: mm)

S8380-128Q, S8381-256Q S8380-256Q, S8381-512Q

0.51

25.4

2.54

3.0

31.75

10.4

5.4 ± 0.25.0 ± 0.2

3.2 ± 0.3

ACTIVE AREA

6.4 × 2.5

0.25

10.16

1.3 ± 0.2 *

PHOTOSENSITIVE

SURFACE

* Optical distance from the outer surface

of the quartz window to the chip surface

0.51

25.4

2.54

3.0

ACTIVE AREA

12.8 × 2.5

6.4 ± 0.3

31.75

10.4

5.4 ± 0.25.0 ± 0.2

0.25

10.16

1.3 ± 0.2 *

PHOTOSENSITIVE

SURFACE

* Optical distance from the outer surface

of the quartz window to the chip surface

KMPDA0060EA

KMPDA0061EA

S8380-512Q, S8381-1024Q

0.51

25.4

3.0

40.6

10.4

5.4 ± 0.25.0 ± 0.2

12.8 ± 0.3

ACTIVE AREA

25.6 × 2.5

0.25

10.16

1.3 ± 0.2 *

PHOTOSENSITIVE

SURFACE

* Optical distance from the outer surface

of the quartz window to the chip surface

2.54

KMPDA0062EA

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

END OF SCAN

1

2

3

4

5

6

7

8

9

10

11

22

21

20

19

18

17

16

15

14

13

12

2

1

st

Vss

Vscg

NC

Vscd

Vss

ACTIVE VIDEO

DUMMY VIDEO

Vsub

Vss, Vsub and NC should be grounded.

KMPDC0056EA

Figure 4 Pin connection

3

NMOS linear image sensor

S8380/S8381 series

HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81) 53-434-3311, Fax: (81) 53-434-5184,

www.hamamatsu.com

U.S.A.: Hamamatsu Corporation: 360 Foothill Road, P.O.Box 6910, Bridgewater, N.J. 08807-0910, U.S.A., Telephone: (1) 908-231-0960, Fax: (1) 908-231-1218

Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49) 08152-3750, Fax: (49) 08152-2658

France: Hamamatsu Photonics France S.A.R.L.: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: 33-(1) 69 53 71 00, Fax: 33-(1) 69 53 71 10

United Kingdom: Hamamatsu Photonics UK Limited: 2 Howard Court, 10 Tewin Road, Welwyn Garden City, Hertfordshire AL7 1BW, United Kingdom, Telephone: (44) 1707-294888, Fax: (44) 1707-325777

North Europe: Hamamatsu Photonics Norden AB: Smidesvägen 12, SE-171 41 Solna, Sweden, Telephone: (46) 8-509-031-00, Fax: (46) 8-509-031-01

Italy: Hamamatsu Photonics Italia S.R.L.: Strada della Moia, 1/E, 20020 Arese, (Milano), Italy, Telephone: (39) 02-935-81-733, Fax: (39) 02-935-81-741

Information furnished by HAMAMATSU is believed to be reliable. However, no responsibility is assumed for possible inaccuracies or omissions.

Specifications are subject to change without notice. No patent rights are granted to any of the circuits described herein. ©200

5 Hamamatsu Photonics K.K.

Cat. No. KMPD1045E01

Oct. 2005 DN

tvd

tpw

1

tpw

2

tpw

s

st

V

s (H)

V

s (L)

V

1 (H)

V

1 (L)

V

2 (H)

V

2 (L)

1

2

END OF SCAN

st

1

2

tr

s tf s

tr

1 tf 1

X1 X2

t

ov

tf 2

tr

2

ACTIVE VIDEO OUTPUT

Figure 7 Timing chart for driver circuit

Figure 8 Video bias voltage margin

4

0

6

8

10

45678 10

CLOCK PULSE AMPLITUDE (V)

VIDEO BIAS VOLTAGE (V)

2

9

MIN.

VIDEO BIAS RANGE

MAX.

RECOMMENDED BIAS

0.5

0.4

0.3

0.2

0.1

0

200

400

600

800

1000

1200

WAVELENGTH (nm)

PHOTO SENSITIVITY (A/W)

(Ta=25 ˚C)

STANDARD TYPE

IR HIGH-SENSITIVITY TYPE

S8380/S8381 SERIES

■

Recommended operating conditions

Terminal Input or output Description

φ

1, φ2

Input

(CMOS logic compatible)

Pulses for operating the MOS shift register. The video data rate is equal to the

clock pulse frequency since the video output signal is obtained synchronously

with the rise of φ2 pulse.

φ

st

Input

(CMOS logic compatible)

Pulse for starting the MOS shift register operation. The time interval between

start pulses is equal to the signal accumulation time.

Vss - Connected to the anode of each photodiode. This should be grounded.

Vscg Input Used for restricting blooming. This should be grounded.

Vscd Input

Used for restricting blooming. This should be biased at a voltage equal to

the video bias voltage.

Active video Output

Video output signal. Connects to photodiode cathodes when the address is

on. A positive voltage should be applied to the video line in order to use

photodiodes with a reverse voltage. When the amplitude of φ1 and φ2 is 5 V,

a video bias voltage of 2 V is recommended.

Dummy video Output

This has the same structure as the active video, but is not connected to

photodiodes, so only spike noise is output. This should be biased at a

voltage equal to the active video or left as an open-circuit when not needed.

Vsub - Connected to the silicon substrate. This should be grounded.

End of scan

Output

(CMOS logic compatible)

This should be pulled up at 5 V by using a 10 kΩ resistor. This is a negative

going pulse that appears synchronously with the φ2 timing right after the last

photodiode is addressed.

NC - Should be grounded.

10

-5

10

2

10

1

10

0

10

-1

10

-2

10

-3

10-410-310-210-110

0

OUTPUT CHARGE (pC)

EXPOSURE (lx · s)

(Typ. Vb=2 V, V =5 V, light source: 2856 K)

S8380 SERIES

S8381 SERIES

SATURATION EXPOSURE

SATURATION

CHARGE

Figure 5 Spectral response (typical example) Figure 6 Output charge vs. exposure

KMPDB0043EA

KMPDB0161EA KMPDB0162EB

KMPDC0022EA

4

Loading...

Loading...