GSI GS8322Z36C-225I, GS8322Z36C-225, GS8322Z36C-200I, GS8322Z36C-200, GS8322Z36C-166I Datasheet

...

Rev: 1.00 10/2001 1/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

NoBL is a trademark of Cypress Semiconductor Corp.. NtRAM is a trademark of Samsung Electronics Co.. ZBT is a trademark of Integrated Device Technology, Inc.

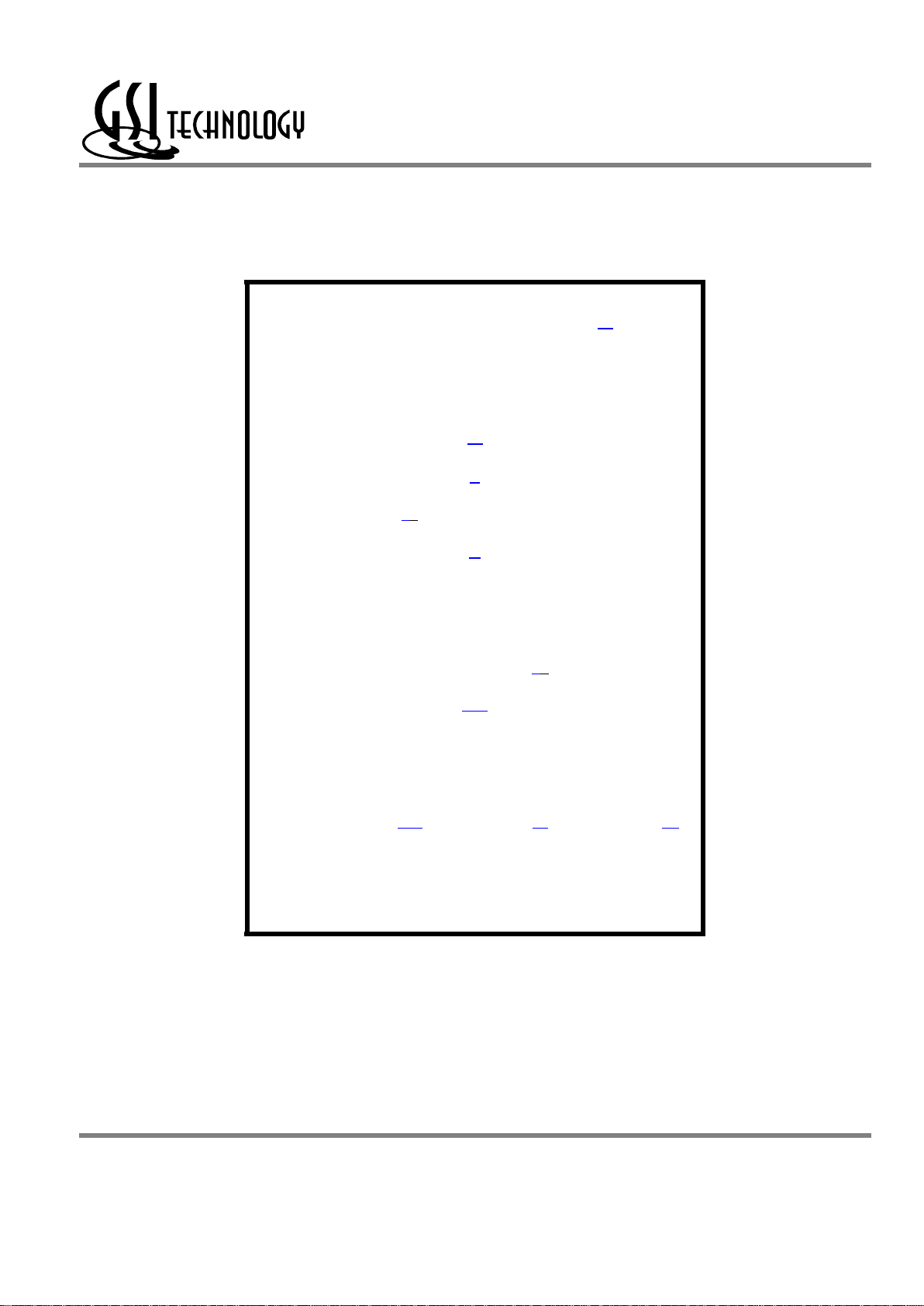

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

36Mb Pipelined and Flow Through

Synchronous NBT SRAM

250 MHz–133 MHz

2.5 V or 3.3 V V

DD

2.5 V or 3.3 V I/O

119 and 209 BGA

Commercial Temp

Industrial Temp

Product Preview

Features

• NBT (No Bus Turn Around) functionality allows zero wait

Read-Write-Read bus utilization; fully pin-compatible with

both pipelined and flow through NtRAM™, NoBL™ and

ZBT™ SRAMs

• 2.5 V or 3.3 V +10%/–5% core power supply

• 2.5 V or 3.3 V I/O supply

• User-configurable Pipeline and Flow Through mode

• ZQ mode pin for user-selectable high/low output drive

• IEEE 1149.1 JTAG-compatible Boundary Scan

• On-chip write parity checking; even or odd selectable

• On-chip parity encoding and error detection

• LBO pin for Linear or Interleave Burst mode

• Pin-compatible with 2Mb, 4Mb, 8Mb, and 16Mb devices

• Byte write operation (9-bit Bytes)

• 3 chip enable signals for easy depth expansion

• ZZ Pin for automatic power-down

• JEDEC-standard 119- or 209-Bump BGA package

Functional Description

The GS8322Z18/36/72 is a 36Mbit Synchronous Static

SRAM. GSI's NBT SRAMs, like ZBT, NtRAM, NoBL or

other pipelined read/double late write or flow through read/

single late write SRAMs, allow utilization of all available bus

bandwidth by eliminating the need to insert deselect cycles

when the device is switched from read to write cycles.

Because it is a synchronous device, address, data inputs, and

read/write control inputs are captured on the rising edge of the

input clock. Burst order control (LBO) must be tied to a power

rail for proper operation. Asynchronous inputs include the

Sleep mode enable (ZZ) and Output Enable. Output Enable can

be used to override the synchronous control of the output

drivers and turn the RAM's output drivers off at any time.

Write cycles are internally self-timed and initiated by the rising

edge of the clock input. This feature eliminates complex offchip write pulse generation required by asynchronous SRAMs

and simplifies input signal timing.

The GS8322Z18/36/72 may be configured by the user to

operate in Pipeline or Flow Through mode. Operating as a

pipelined synchronous device, in addition to the rising-edgetriggered registers that capture input signals, the device

incorporates a rising edge triggered output register. For read

cycles, pipelined SRAM output data is temporarily stored by

the edge-triggered output register during the access cycle and

then released to the output drivers at the next rising edge of

clock.

The GS8322Z18/36/72 is implemented with GSI's high

performance CMOS technology and is available in a JEDECstandard 119-bump or 209-bump BGA package.

-250 -225 -200 -166 -150 -133 Unit

Pipeline

3-1-1-1

t

KQ

tCycle

2.3

4.0

2.5

4.4

3.0

5.0

3.5

6.0

3.8

6.6

4.0

7.5nsns

3.3 V

Curr (x18)

Curr (x36)

Curr (x72)

365

560

660

335

510

600

305

460

540

265

400

460

245

370

430

215

330

380

mA

mA

mA

2.5 V

Curr (x18)

Curr (x36)

Curr (x72)

360

550

640

330

500

590

305

460

530

260

390

450

240

360

420

215

330

370

mA

mA

mA

Flow

Through

2-1-1-1

t

KQ

tCycle

6.0

7.0

6.5

7.5

7.5

8.5

8.51010101115ns

ns

3.3 V

Curr (x18)

Curr (x36)

Curr (x72)

235

300

350

230

300

350

210

270

300

200

270

300

195

270

300

150

200

220

mA

mA

mA

2.5 V

Curr (x18)

Curr (x36)

Curr (x72)

235

300

340

230

300

340

210

270

300

200

270

300

195

270

300

145

190

220

mA

mA

mA

Rev: 1.00 10/2001 2/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

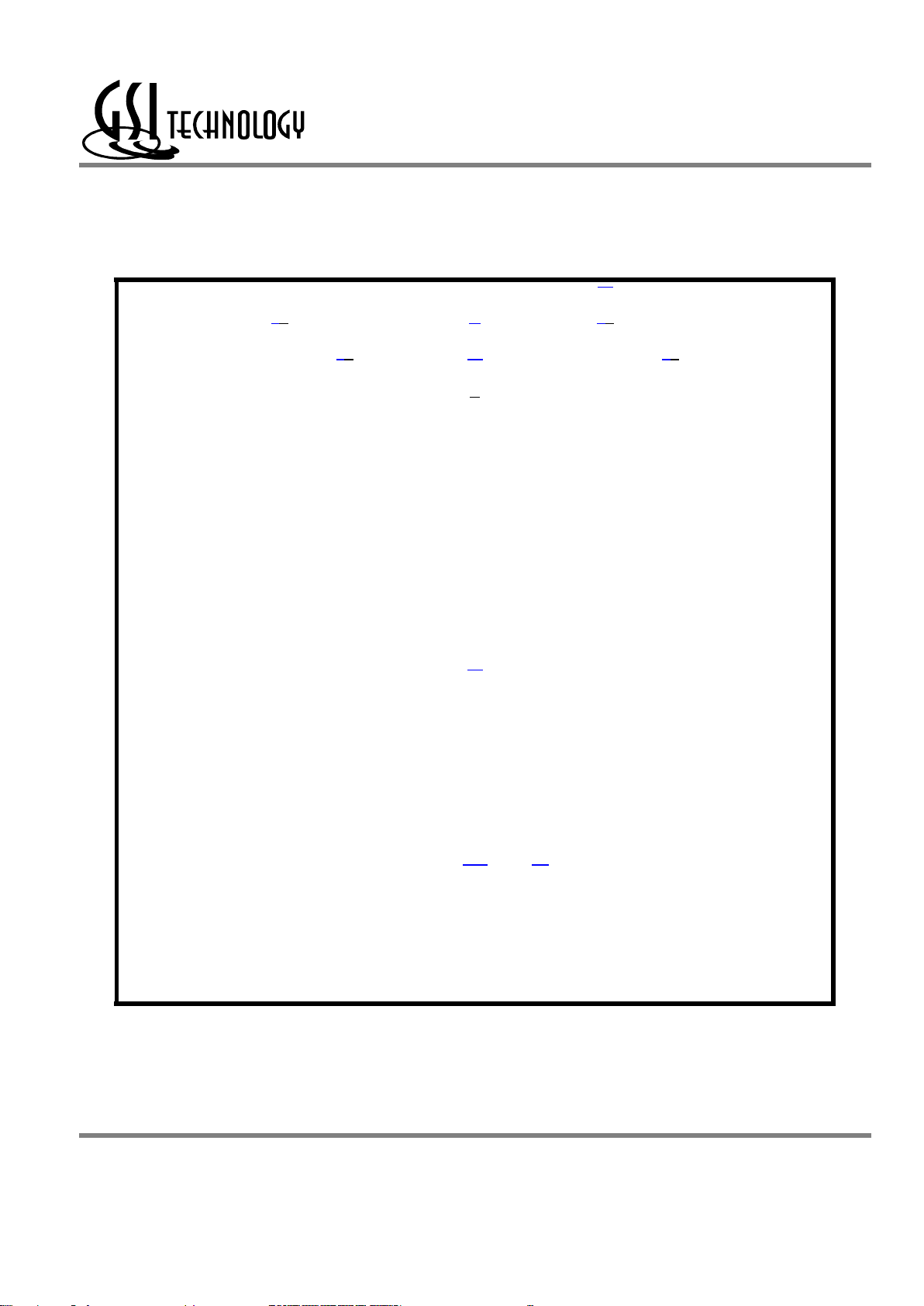

GS8322Z72B Pad Out

209-Bump BGA—Top View

1 2 3 4 5 6 7 8 9 10 11

A DQG5 DQG1 A13 E2 A14 ADV A15 E3 A17 DQB1 DQB5 A

B DQG6 DQG2 BC BG NC W A16 BB BF DQB2 DQB6 B

C DQG7 DQG3 BH BD NC E1 NC BE BA DQB3 DQB7 C

D DQG8 DQG4

V

SS

NC NC G NC NC

V

SS

DQB4 DQB8 D

E DQPG9 DQPC9

V

DDQ

V

DDQ

V

DD

V

DD

V

DD

V

DDQ

V

DDQ

DQPF9 DQPB9 E

F DQC4 DQC8

V

SS

V

SS

V

SS

ZQ

V

SS

V

SS

V

SS

DQF8 DQF4 F

G DQC3 DQC7

V

DDQ

V

DDQ

V

DD

MCH

V

DD

V

DDQ

V

DDQ

DQF7 DQF3 G

H DQC2 DQC6

V

SS

V

SS

V

SS

MCL

V

SS

V

SS

V

SS

DQF6 DQF2 H

J DQC1 DQC5

V

DDQ

V

DDQ

V

DD

MCH

V

DD

V

DDQ

V

DDQ

DQF5 DQF1 J

K NC NC CK NC

V

SS

MCL

V

SS

NC NC NC NC K

L DQH1 DQH5

V

DDQ

V

DDQ

V

DD

FT

V

DD

V

DDQ

V

DDQ

DQA5 DQA1 L

M DQH2 DQH6

V

SS

V

SS

V

SS

MCL

V

SS

V

SS

V

SS

DQA6 DQA2 M

N DQH3 DQH7

V

DDQ

V

DDQ

V

DD

MCH

V

DD

V

DDQ

V

DDQ

DQA7 DQA3 N

P DQH4 DQH8

V

SS

V

SS

V

SS

ZZ

V

SS

V

SS

V

SS

DQA8 DQA4 P

R DQPD9 DQPH9

V

DDQ

V

DDQ

V

DD

V

DD

V

DD

V

DDQ

V

DDQ

DQPA9 DQPE9 R

T DQD8 DQD4

V

SS

NC NC LBO PE NC

V

SS

DQE4 DQE8 T

U DQD7 DQD3 NC A12 NC A11 A18 A10 NC DQE3 DQE7 U

V DQD6 DQD2 A9 A8 A7 A1 A6 A5 A4 DQE2 DQE6 V

W DQD5 DQD1 TMS TDI A3 A0 A2 TDO TCK DQE1 DQE5 W

11 x 19 Bump BGA—14 x 22 mm2 Body—1 mm Bump Pitch

Rev: 1.00 10/2001 3/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

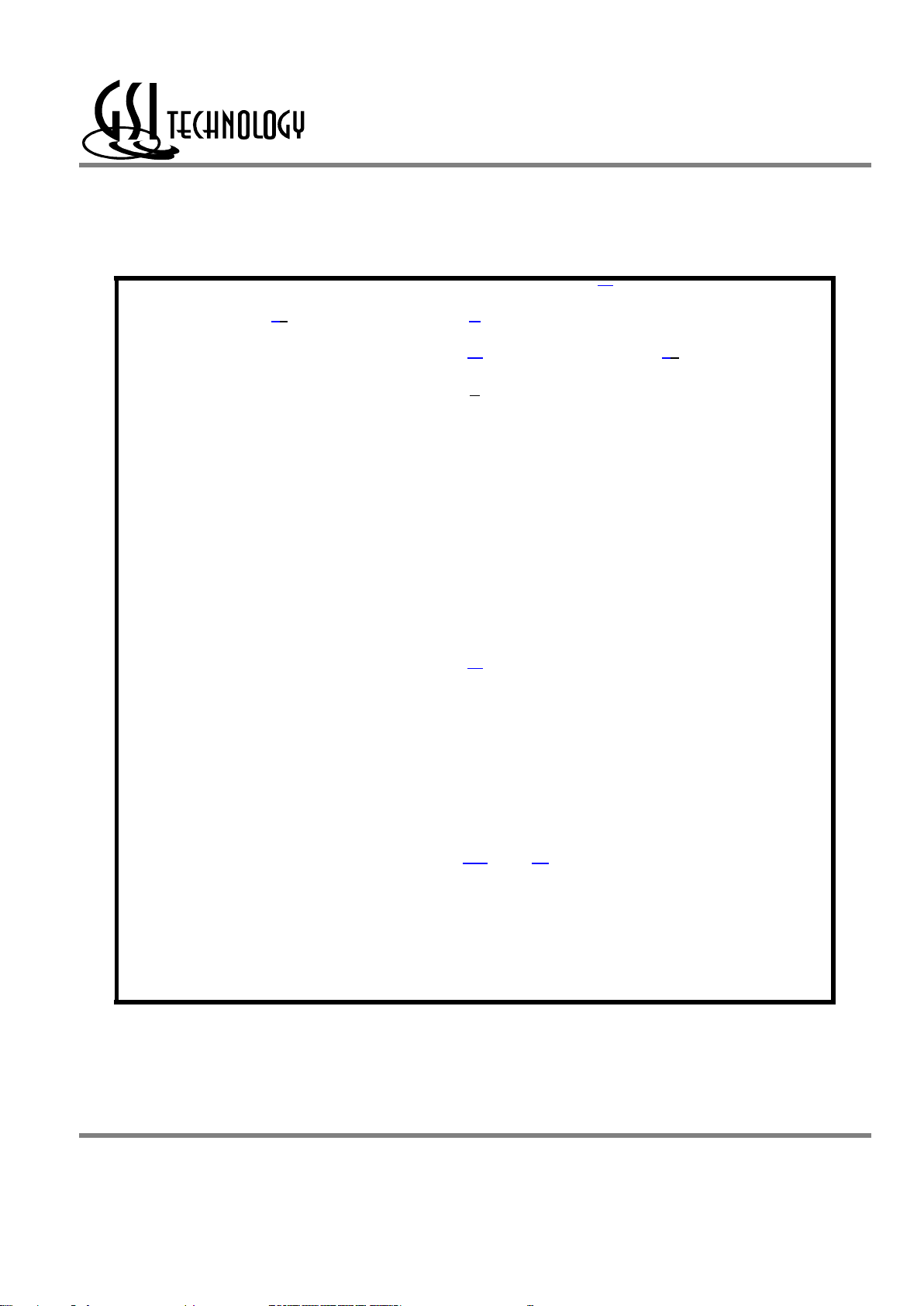

GS8322Z36C Pad Out

209-Bump BGA—Top View

1 2 3 4 5 6 7 8 9 10 11

A NC NC A13 E2 A14 ADV A15 E3 A17 DQB1 DQB5 A

B NC NC BC NC A19 W A16 BB NC DQB2 DQB6 B

C NC NC NC BD NC E1 NC NC BA DQB3 DQB7 C

D NC NC

V

SS

NC NC G NC NC

V

SS

DQB4 DQB8 D

E NC DQPC9

V

DDQ

V

DDQ

V

DD

V

DD

V

DD

V

DDQ

V

DDQ

NC DQPB9 E

F DQC4 DQC8

V

SS

V

SS

V

SS

ZQ

V

SS

V

SS

V

SS

NC NC F

G DQC3 DQC7

V

DDQ

V

DDQ

V

DD

MCH

V

DD

V

DDQ

V

DDQ

NC NC G

H DQC2 DQC6

V

SS

V

SS

V

SS

MCL

V

SS

V

SS

V

SS

NC NC H

J DQC1 DQC5

V

DDQ

V

DDQ

V

DD

MCH

V

DD

V

DDQ

V

DDQ

NC NC J

K NC NC CK NC

V

SS

MCL

V

SS

NC NC NC NC K

L NC NC

V

DDQ

V

DDQ

V

DD

FT

V

DD

V

DDQ

V

DDQ

DQA5 DQA1 L

M NC NC

V

SS

V

SS

V

SS

MCL

V

SS

V

SS

V

SS

DQA6 DQA2 M

N NC NC

V

DDQ

V

DDQ

V

DD

MCH

V

DD

V

DDQ

V

DDQ

DQA7 DQA3 N

P NC NC

V

SS

V

SS

V

SS

ZZ

V

SS

V

SS

V

SS

DQA8 DQA4 P

R DQPD9 NC

V

DDQ

V

DDQ

V

DD

V

DD

V

DD

V

DDQ

V

DDQ

DQPA9 NC R

T DQD8 DQD4

V

SS

NC NC LBO PE NC

V

SS

NC NC T

U DQD7 DQD3 NC A12 NC A11 A18 A10 NC NC NC U

V DQD6 DQD2 A9 A8 A7 A1 A6 A5 A4 NC NC V

W DQD5 DQD1 TMS TDI A3 A0 A2 TDO TCK NC NC W

11 x 19 Bump BGA—14 x 22 mm2 Body—1 mm Bump Pitch

Rev: 1.00 10/2001 4/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

GS8322Z18C Pad Out

209-Bump BGA—Top View

1 2 3 4 5 6 7 8 9 10 11

A NC NC A13 E2 A14 ADV A15 E3 A17 NC NC A

B NC NC BB NC A19 W A16 NC NC NC NC B

C NC NC NC NC NC E1 A20 NC BA NC NC C

D NC NC

V

SS

NC NC G NC NC

V

SS

NC NC D

E NC DQPB9

V

DDQ

V

DDQ

V

DD

V

DD

V

DD

V

DDQ

V

DDQ

NC NC E

F DQB4 DQB8

V

SS

V

SS

V

SS

ZQ

V

SS

V

SS

V

SS

NC NC F

G DQB3 DQB7

V

DDQ

V

DDQ

V

DD

MCH

V

DD

V

DDQ

V

DDQ

NC NC G

H DQB2 DQB6

V

SS

V

SS

V

SS

MCL

V

SS

V

SS

V

SS

NC NC H

J DQB1 DQB5

V

DDQ

V

DDQ

V

DD

MCH

V

DD

V

DDQ

V

DDQ

NC NC J

K NC NC CK NC

V

SS

MCL

V

SS

NC NC NC NC K

L NC NC

V

DDQ

V

DDQ

V

DD

FT

V

DD

V

DDQ

V

DDQ

DQA5 DQA1 L

M NC NC

V

SS

V

SS

V

SS

MCL

V

SS

V

SS

V

SS

DQA6 DQA2 M

N NC NC

V

DDQ

V

DDQ

V

DD

MCH

V

DD

V

DDQ

V

DDQ

DQA7 DQA3 N

P NC NC

V

SS

V

SS

V

SS

ZZ

V

SS

V

SS

V

SS

DQA8 DQA4 P

R NC NC

V

DDQ

V

DDQ

V

DD

V

DD

V

DD

V

DDQ

V

DDQ

DQPA9 NC R

T NC NC

V

SS

NC NC LBO PE NC

V

SS

NC NC T

U NC NC NC A12 NC A11 A18 A10 NC NC NC U

V NC NC A9 A8 A7 A1 A6 A5 A4 NC NC V

W NC NC TMS TDI A3 A0 A2 TDO TCK NC NC W

11 x 19 Bump BGA—14 x 22 mm2 Body—1 mm Bump Pitch

Rev: 1.00 10/2001 5/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

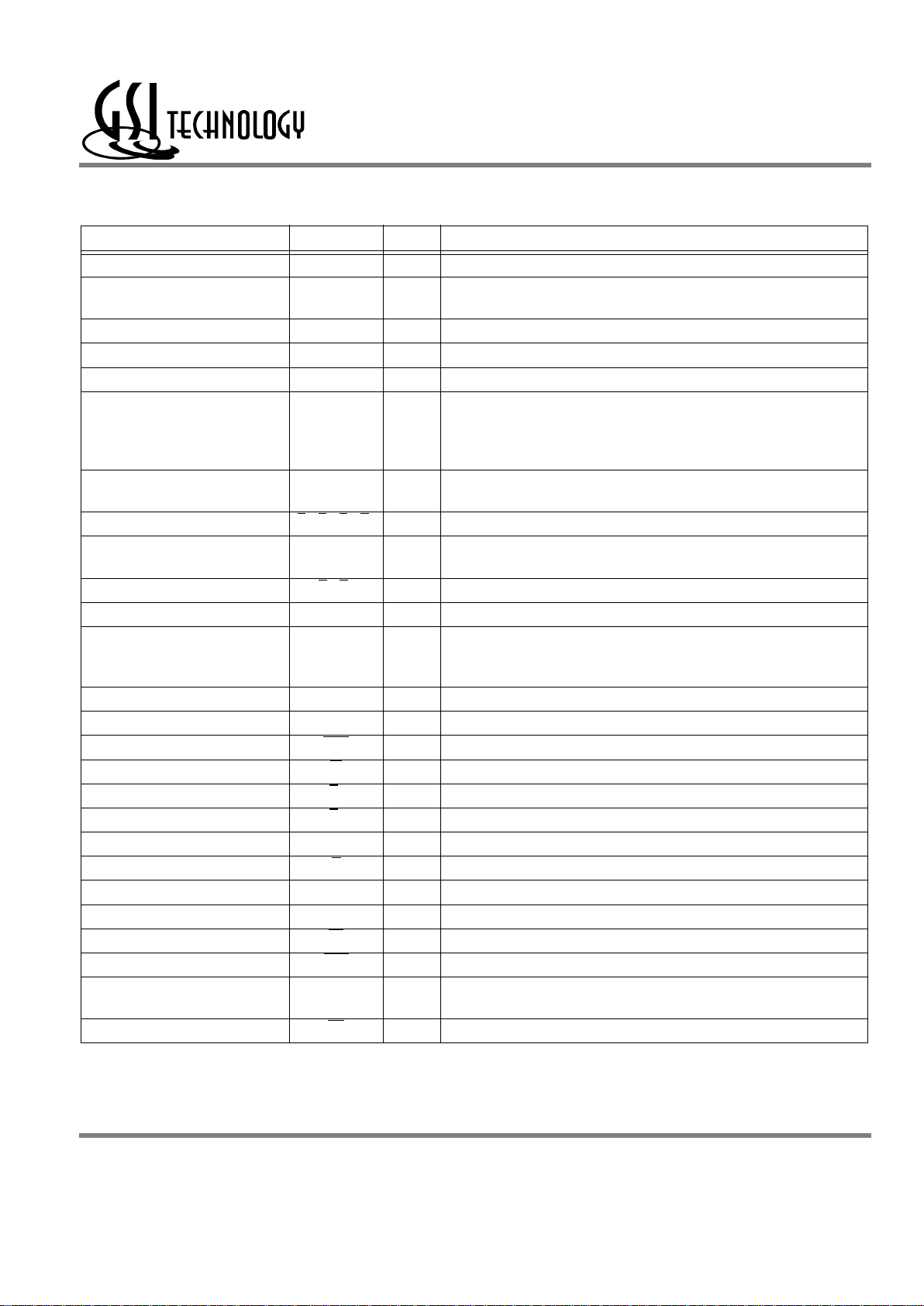

GS8322Z18/36/72 209-Bump BGA Pin Description

Pin Location Symbol Type Description

W6, V6 A0, A1 I Address field LSBs and Address Counter Preset Inputs.

W7, W5, V9, V8, V7, V5, V4, V3, U8, U6, U4,

A3, A5, A7, B7, A9, U7

An I Address Inputs

B5 A19 I Address Inputs (x36/x18 Versions)

C7 A20 I Address Inputs (x18 Version)

L11, M11, N11, P11, L10, M10, N10, P10, R10

A10, B10, C10, D10, A11, B11, C11, D11, E11

J1, H1, G1, F1, J2, H2, G2, F2, E2

W2, V2, U2, T2, W1, V1, U1, T1, R1

W10, V10, U10, T10, W11, V11, U11, T11, R11

J11, H11, G11, F11, J10, H10, G10, F10, E10

A2, B2, C2, D2, A1, B1, C1, D1, E1

L1, M1, N1, P1, L2, M2, N2, P2, R2

DQA1–DQA9

DQB1–DQB9

DQC1–DQC9

DQD1–DQD9

DQE1–DQE9

DQF1–DQF9

DQG1–DQG9

DQH1–DQH9

I/O Data Input and Output pins (x72 Version)

L11, M11, N11, P11, L10, M10, N10, P10, R10

A10, B10, C10, D10, A11, B11, C11, D11, E11

J1, H1, G1, F1, J2, H2, G2, F2, E2

W2, V2, U2, T2, W1, V1, U1, T1, R1

DQA1–DQA9

DQB1–DQB9

DQC1–DQC9

DQD1–DQD9

I/O Data Input and Output pins (x36 Version)

L11, M11, N11, P11, L10, M10, N10, P10, R10

J1, H1, G1, F1, J2, H2, G2, F2, E2

DQA1–DQA9

DQB1–DQB9

I/O Data Input and Output pins (x18 Version)

C9, B8

BA, BB

I Byte Write Enable for DQA, DQB I/Os; active low

B3, C4

BC,BD

I

Byte Write Enable for DQC, DQD I/Os; active low

(x72/x36 Versions)

C8, B9, B4, C3

BE, BF, BG,BH

I

Byte Write Enable for DQE, DQF, DQG, DQH I/Os; active low

(x72 Version)

B5 NC — No Connect (x72 Version)

C7 NC — No Connect (x72/x36 Versions)

W10, V10, U10, T10, W11, V11, U11, T11, R11

J11, H11, G11, F11, J10, H10, G10, F10, E10

A2, B2, C2, D2, A1, B1, C1, D1, E1

L1, M1, N1, P1, L2, M2, N2, P2, R2, C8, B9,

B4, C3

NC — No Connect (x36/x18 Versions)

B3, C4 NC — No Connect (x18 Version)

C5, D4, D5, D7, D8, K1, K2, K4, K8, K9, K10,

K11, T4, T5, T7, T8, U3, U5, U9

NC — No Connect

K3 CK I Clock Input Signal; active high

C6

E1

I Chip Enable; active low

A8

E3

I Chip Enable; active low

A4

E2

I Chip Enable; active high

D6

G

I Output Enable; active low

A6

ADV

I Burst address counter advance enable

Rev: 1.00 10/2001 6/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

P6

ZZ

I Sleep Mode control; active high

L6

FT

I Flow Through or Pipeline mode; active low

T6

LBO

I Linear Burst Order mode; active low

G6, J6

MCH

I Must Connect High

N6

MCH

I Must Connect High

H6, J6, K6, M6

MCL

Must Connect Low

A8, N6

MCL

Must Connect Low (x18 version)

B6

W

I Write Enable; active low

T7

PE

I

Parity Bit Enable; active low (High = x16/32 Mode, Low = x18/36

Mode)

F6

ZQ

I

FLXDrive Output Impedance Control

(Low = Low Impedance [High Drive], High = High Impedance [Low

Drive])

W3

TMS

I Scan Test Mode Select

W4

TDI

I Scan Test Data In

W8

TDO

O Scan Test Data Out

W9

TCK

I Scan Test Clock

E5, E6, E7, G5, G7, J5, J7, L5, L7, N5, N7, R5,

R6, R7

V

DD

I Core power supply

D3, D9, F3, F4, F5, F7, F8, F9, H3, H4, H5, H7,

H8, H9, K5, K7, M3, M4, M5, M7, M8, M9, P3,

P4, P5, P7, P8, P9, T3, T9

V

SS

I I/O and Core Ground

E3, E4, E8, E9, G3, G4, G8, G9, J3, J4, J8, J9,

L3, L4, L8, L9, N3, N4, N8, N9, R3, R4, R8, R9

V

DDQ

I Output driver power supply

GS8322Z18/36/72 209-Bump BGA Pin Description

Pin Location Symbol Type Description

Rev: 1.00 10/2001 7/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

GS8322Z36B Pad Out

119-Bump BGA—Top View

1 2 3 4 5 6 7

A

V

DDQ

A6 A7 A18 A8 A9

V

DDQ

A

B NC E2 A4 ADV A15 E3 NC B

C NC A5 A3

V

DD

A14 A16 NC C

D DQC DQPC

V

SS

ZQ

V

SS

DQPB DQB D

E DQC DQC

V

SS

E1

V

SS

DQB DQB E

F

V

DDQ

DQC

V

SS

G

V

SS

DQB

V

DDQ

F

G DQC DQC BC A17 BB DQB DQB G

H DQC DQC

V

SS

W

V

SS

DQB DQB H

J

V

DDQ

V

DD

NC

V

DD

NC

V

DD

V

DDQ

J

K DQD DQD

V

SS

CK

V

SS

DQA DQA K

L DQD DQD BD NC BA DQA DQA L

M

V

DDQ

DQD

V

SS

CKE

V

SS

DQA

V

DDQ

M

N DQD DQD

V

SS

A1

V

SS

DQA DQA N

P DQD DQPD

V

SS

A0

V

SS

DQPA DQA P

R NC A2 LBO

V

DD

FT A13 PE R

T NC NC A10 A11 A12 A19 ZZ T

U

V

DDQ

TMS TDI TCK TDO NC

V

DDQ

U

7 x 17 Bump BGA—14 x 22 mm2 Body—1.27 mm Bump Pitch

Rev: 1.00 10/2001 8/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

GS8322Z18B Pad Out

119-Bump BGA—Top View

1 2 3 4 5 6 7

A

V

DDQ

A6 A7 A18 A8 A9

V

DDQ

A

B NC E2 A4 ADV A15 E3 NC B

C NC A5 A3

V

DD

A14 A16 NC C

D DQB NC

V

SS

ZQ

V

SS

DQPA NC D

E NC DQB

V

SS

E1

V

SS

NC DQA E

F

V

DDQ

NC

V

SS

G

V

SS

DQA

V

DDQ

F

G NC DQB BB A17 NC NC DQA G

H DQB NC

V

SS

W

V

SS

DQA NC H

J

V

DDQ

V

DD

NC

V

DD

NC

V

DD

V

DDQ

J

K NC DQB

V

SS

CK

V

SS

NC DQA K

L DQB NC NC NC BA DQA NC L

M

V

DDQ

DQB

V

SS

CKE

V

SS

NC

V

DDQ

M

N DQB NC

V

SS

A1

V

SS

DQA NC N

P NC DQPB

V

SS

A0

V

SS

NC DQA P

R NC A2 LBO

V

DD

FT A13 PE R

T NC A10 A11 A20 A12 A19 ZZ T

U

V

DDQ

TMS TDI TCK TDO NC

V

DDQ

U

7 x 17 Bump BGA—14 x 22 mm2 Body—1.27 mm Bump Pitch

Rev: 1.00 10/2001 9/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

GS8322Z18/36 119-Bump BGA Pin Description

Pin Location Symbol Type Description

P4, N4 A0, A1 I Address field LSBs and Address Counter Preset Inputs

R2, C3, B3, C2, A2, A3, A5, A6, T3,

T5, R6, C5, B5, C6, G4, A4

An I Address Inputs

T4, T6 An Address Input (x36 Version)

T2 NC — No Connect (x36 Version)

T2, T6, T4 An I Address Input (x18 Version)

K7, L7, N7, P7, K6, L6, M6, N6

H7, G7, E7, D7, H6, G6, F6, E6

H1, G1, E1, D1, H2, G2, F2, E2

K1, L1, N1, P1, K2, L2, M2, N2

DQA1–DQA8

DQB1–DQB8

DQC1–DQC8

DQD1–DQD8

I/O Data Input and Output pins. (x36 Version)

P6, D6, D2, P2

DQA9, DQB9,

DQC9, DQD9

I/O Data Input and Output pins. (x36 Version)

L5, G5, G3, L3 BA, BB, BC, BD I Byte Write Enable for DQA, DQB, DQC, DQD I/Os; active low (x36 Version)

P7, N6, L6, K7, H6, G7, F6, E7, D6

D1, E2, G2, H1, K2, L1, M2, N1, P2

DQA1–DQA9

DQB1–DQB9

I/O Data Input and Output pins (x18 Version)

L5, G3 BA, BB I Byte Write Enable for DQA, DQB I/Os; active low (x18 Version)

B1, C1, R1, T1, U6, B7, C7, J3, J5 NC — No Connect

P6, N7, M6, L7, K6, H7, G6, E6, D7,

D2, E1, F2, G1, H2, K1, L2, N2, P1,

G5, L3

NC — No Connect (x18 Version)

L4 NC — No Connect

K4 CK I Clock Input Signal; active high

M4 CKE I Clock Enable; active low

H4 W I Write Enable; active low

E4 E1 I Chip Enable; active low

B6 E3 I Chip Enable; active low

B2 E2 I Chip Enable; active high

F4 G I Output Enable; active low

B4 ADV I Burst address counter advance enable

T7 ZZ I Sleep mode control; active high

R5 FT I Flow Through or Pipeline mode; active low

R3 LBO I Linear Burst Order mode; active low

D4 ZQ I

FLXDrive Output Impedance Control (Low = Low Impedance [High Drive],

High = High Impedance [Low Drive])

R7 PE I Parity Bit Enable; active low

Rev: 1.00 10/2001 10/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

BPR1999.05.18

Functional Details

Clocking

Deassertion of the Clock Enable (CKE) input blocks the Clock input from reaching the RAM's internal circuits. It may be used to

suspend RAM operations. Failure to observe Clock Enable set-up or hold requirements will result in erratic operation.

Pipeline Mode Read and Write Operations

All inputs (with the exception of Output Enable, Linear Burst Order and Sleep) are synchronized to rising clock edges. Single cycle

read and write operations must be initiated with the Advance/Load pin (ADV) held low, in order to load the new address. Device

activation is accomplished by asserting all three of the Chip Enable inputs (E1, E2, and E3). Deassertion of any one of the Enable

inputs will deactivate the device.

Read operation is initiated when the following conditions are satisfied at the rising edge of clock: CKE is asserted low, all three

chip enables (E1, E2, and E3) are active, the write enable input signals W is deasserted high, and ADV is asserted low. The address

presented to the address inputs is latched into the address register and presented to the memory core and control logic. The control

logic determines that a read access is in progress and allows the requested data to propagate to the input of the output register. At

the next rising edge of clock the read data is allowed to propagate through the output register and onto the output pins.

Write operation occurs when the RAM is selected, CKE is active, and the Write input is sampled low at the rising edge of clock.

U2

TMS

I Scan Test Mode Select

U3

TDI

I Scan Test Data In

U5

TDO

O Scan Test Data Out

U4

TCK

I Scan Test Clock

J2, C4, J4, R4, J6

V

DD

I Core power supply

D3, E3, F3, H3, K3, M3, N3, P3, D5,

E5, F5, H5, K5, M5, N5, P5

V

SS

I I/O and Core Ground

A1, F1, J1, M1, U1, A7, F7, J7, M7,

U7

V

DDQ

I Output driver power supply

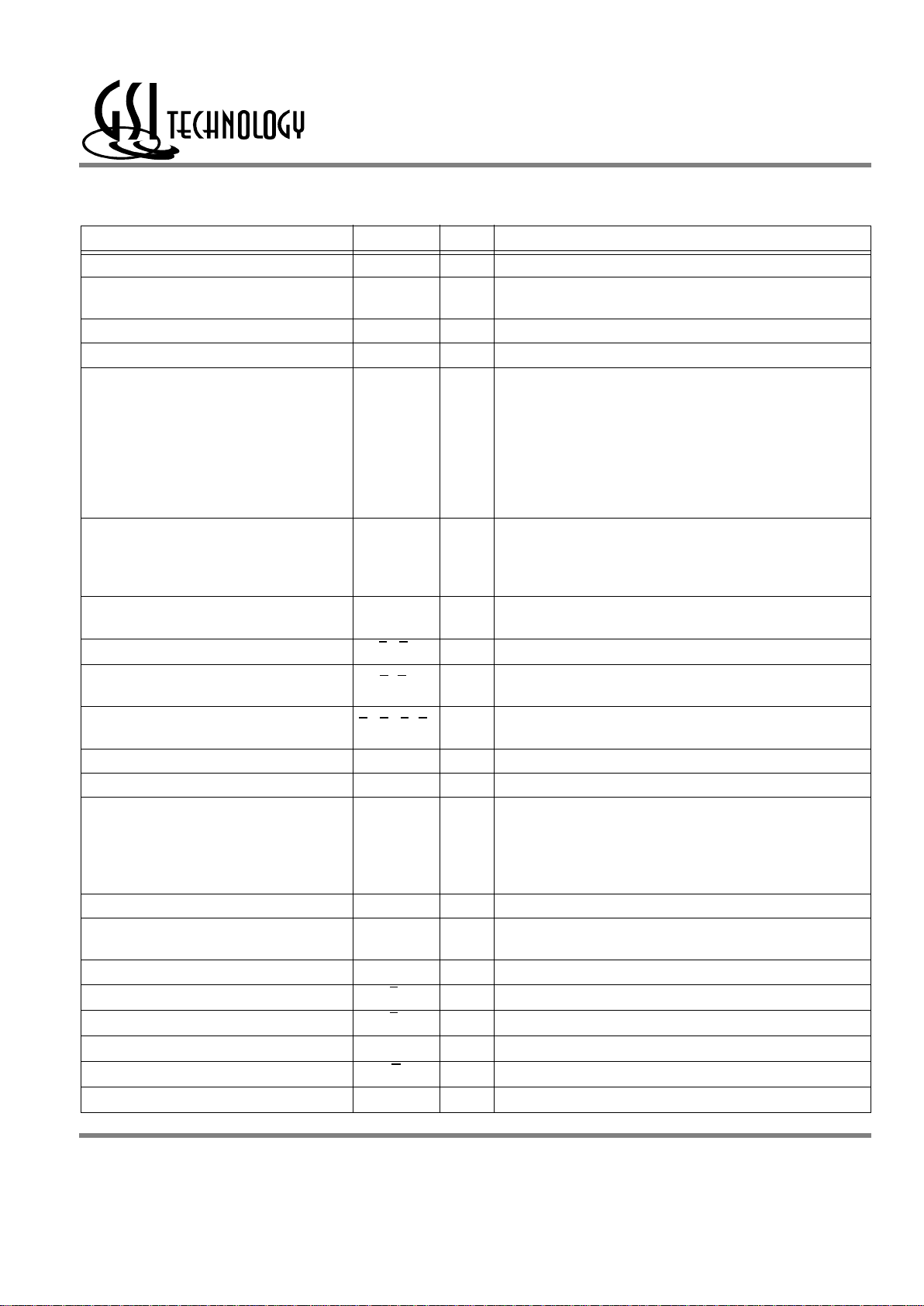

Function W BA BB BC BD

Read H X X X X

Write Byte “a” L L H H H

Write Byte “b” L H L H H

Write Byte “c” L H H L H

Write Byte “d” L H H H L

Write all Bytes L L L L L

Write Abort/NOP L H H H H

GS8322Z18/36 119-Bump BGA Pin Description

Pin Location Symbol Type Description

Rev: 1.00 10/2001 11/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

The Byte Write Enable inputs (BA, BB, BC, and BD) determine which bytes will be written. All or none may be activated. A write

cycle with no Byte Write inputs active is a no-op cycle. The pipelined NBT SRAM provides double late write functionality,

matching the write command versus data pipeline length (2 cycles) to the read command versus data pipeline length (2 cycles). At

the first rising edge of clock, Enable, Write, Byte Write(s), and Address are registered. The Data In associated with that address is

required at the third rising edge of clock.

Flow Through Mode Read and Write Operations

Operation of the RAM in Flow Through mode is very similar to operations in Pipeline mode. Activation of a Read Cycle and the

use of the Burst Address Counter is identical. In Flow Through mode the device may begin driving out new data immediately after

new address are clocked into the RAM, rather than holding new data until the following (second) clock edge. Therefore, in Flow

Through mode the read pipeline is one cycle shorter than in Pipeline mode.

Write operations are initiated in the same way, but differ in that the write pipeline is one cycle shorter as well, preserving the ability

to turn the bus from reads to writes without inserting any dead cycles. While the pipelined NBT RAMs implement a double late

write protocol in Flow Through mode a single late write protocol mode is observed. Therefore, in Flow Through mode, address

and control are registered on the first rising edge of clock and data in is required at the data input pins at the second rising edge of

clock.

Rev: 1.00 10/2001 12/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

Synchronous Truth Table

Operation Type Address E1 E2 E3 ZZ ADV W Bx G CKE CK DQ Notes

Deselect Cycle, Power Down D None H X X L L X X X L L-H High-Z

Deselect Cycle, Power Down D None X X H L L X X X L L-H High-Z

Deselect Cycle, Power Down D None X L X L L X X X L L-H High-Z

Deselect Cycle, Continue D None X X X L H X X X L L-H High-Z 1

Read Cycle, Begin Burst R External L H L L L H X L L L-H Q

Read Cycle, Continue Burst B Next X X X L H X X L L L-H Q 1,10

NOP/Read, Begin Burst R External L H L L L H X H L L-H High-Z 2

Dummy Read, Continue Burst B Next X X X L H X X H L L-H High-Z 1,2,10

Write Cycle, Begin Burst W External L H L L L L L X L L-H D 3

Write Cycle, Continue Burst B Next X X X L H X L X L L-H D 1,3,10

NOP/Write Abort, Begin Burst W None L H L L L L H X L L-H High-Z 2,3

Write Abort, Continue Burst B Next X X X L H X H X L L-H High-Z 1,2,3,10

Clock Edge Ignore, Stall Current X X X L X X X X H L-H - 4

Sleep Mode None X X X H X X X X X X High-Z

Notes:

1. Continue Burst cycles, whether Read or Write, use the same control inputs. A Deselect continue cycle can only be entered into if a

Deselect cycle is executed first.

2. Dummy Read and Write abort can be considered NOPs because the SRAM performs no operation. A Write abort occurs when the W pin

is sampled low but no Byte Write pins are active, so no write operation is performed.

3. G can be wired low to minimize the number of control signals provided to the SRAM. Output drivers will automatically turn off during write

cycles.

4. If CKE High occurs during a pipelined read cycle, the DQ bus will remain active (Low Z). If CKE High occurs during a write cycle, the bus

will remain in High Z.

5. X = Don’t Care; H = Logic High; L = Logic Low; Bx = High = All Byte Write signals are high; Bx = Low = One or more Byte/Write signals

are Low

6. All inputs, except G and ZZ must meet setup and hold times of rising clock edge.

7. Wait states can be inserted by setting CKE high.

8. This device contains circuitry that ensures all outputs are in High Z during power-up.

9. A 2-bit burst counter is incorporated.

10. The address counter is incriminated for all Burst continue cycles.

Rev: 1.00 10/2001 13/42 © 2001, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8322Z18(B/C)/GS8322Z36(B/C)/GS8322Z72(C)

Product Preview

Deselect

New Read New Write

Burst Read Burst Write

W

R

B

R

B

W

DD

B

B

W

R

D

B

W

R

D

D

Pipelined and Flow Through Read Write Control State Diagram

Current State (n)

Next State (n+1)

Transition

ƒ

Input Command Code

Key Notes

1. The Hold command (CKE Low) is not

shown because it prevents any state change.

2. W, R, B, and D represent input command

codes as indicated in the Synchronous Truth Table.

Clock (CK)

Command

Current State Next State

ƒ

n n+1 n+2 n+3

ƒ ƒ ƒ

Current State and Next State Definition for Pipelined and Flow through Read/Write Control State Diagram

W

R

Loading...

Loading...