Page 1

Manual de Serviço

Multimedia DVD Player D-470

rev. 0

Jul/2005

Page 2

INTRODUÇÃO

O SAT através deste Manual de Serviço tem a finalidade de mostrar todas as etapas necessárias para a correta

manutenção dos produtos Gradiente.

Nossa maior preocupação é oferecer aos técnicos da rede de Serviços Autorizados Gradiente em todo território

nacional, condições de conhecer profundamente o DVD Player D-470 e assim capacitá-los a desenvolver um

serviço de qualidade junto aos nossos clientes.

Para isso, é indispensável uma leitura cuidadosa e atenta de todas as instruções contidas neste manual.

Divisão Nacional de Serviços

ÍNDICE

INTRODUÇÃO ...................................................................................................................................... 1

PRECAUÇÕES DE SEGURANÇA .............................................................................................................. 2

ESPECIFICAÇÕES TÉCNICAS ................................................................................................................. 5

DESCRIÇÃO DOS PINOS DOS PRINCIPAIS CIRCUITOS INTEGRADOS......................................................... 6

ESQUEMAS ELÉTRICOS ....................................................................................................................... 28

VISTA EXPLODIDA .............................................................................................................................. 39

PROCEDIMENTOS DE MANUTENÇÃO .....................................................................................................43

Manual de Serviço 1

Page 3

PRECAUÇÕES DE SEGURANÇA

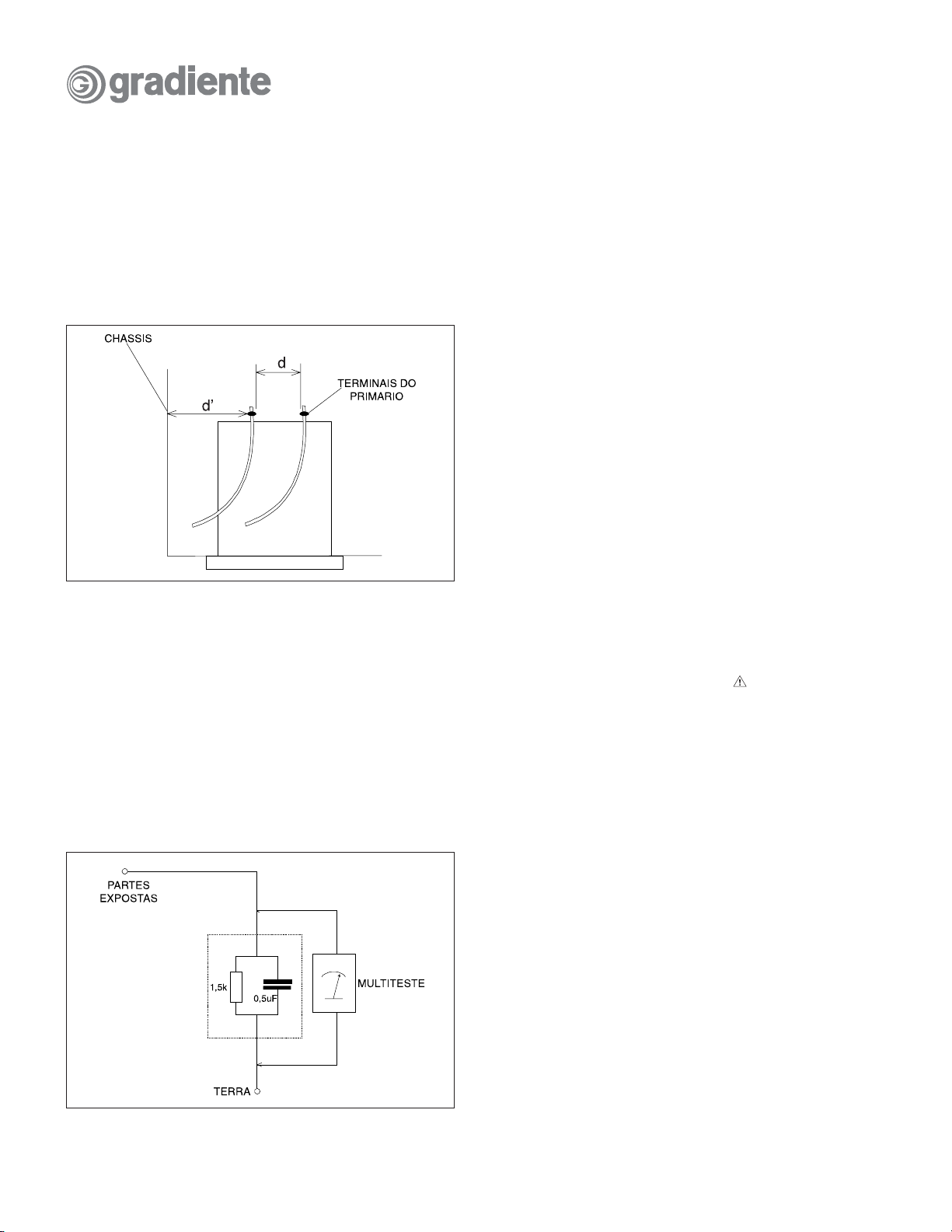

DISTÂNCIA DE FOLGA

Ao substituir componentes do circuito primário, confirme

a distância da folga especificada (d), (d’) para que seja

maior que 3,2 mm, entre terminais soldados e entre

terminais e partes metálicas.

CHECAGEM DA CORRENTE DE FUGA:

No aparelho completamente montado, conecte o cabo

de força a linha AC em uma tomada de 120V (não utilize

transformador de isolação de rede durante este teste).

Utilize um voltímetro AC com sensibilidade de no mínimo

1KΩ/V conectado conforme a figura ao lado:

Meça a tensão AC sobre o resistor conectando uma das

pontas de prova em todas as partes metálicas expostas

do aparelho (conexões de antena, plugs de entrada/

saída de áudio e vídeo, ofereçam um retorno elétrico

ao chassi. Qualquer tensão medida não deve exceder a

0,35VAC. Inverta o plug do cabo de força do aparelho

na tomada e repita o teste.

NOTAS DE SEGURANÇA

1- Antes de devolver o aparelho ao proprietário,

certifique-se de que nenhum dispositivo interno

de proteção esteja defeituoso ou tenha sido

prejudicado durante a manutenção. Componentes,

partes, e/ou fiação que estejam danificados devem

ser substituídos por componentes, partes, ou fiação

que obedeçam as especificações originais.

2- Não opere este aparelho ou deixe que seja operado

sem todos os dispositivos protetores devidamente

instalados e funcionando. Técnicos que danifiquem

as características de segurança ou falhem ao

realizar checagens de segurança são responsáveis

por qualquer defeito resultante, e poderá expor a

si próprio e aos outros a possíveis danos.

3- Leia e obedeça todas as precauções e as notas

relacionadas a segurança no lado de dentro e sobre

o gabinete do produto.

4- NOTA DE SEGURANÇA: Alguns componentes

elétricos e mecânicos têm características especiais

de segurança e são identificados no esquema e na

lista de materiais pelo símbolo

imprescindível que a substituição seja feita por

componentes originais fornecidos pela Gradiente,

a substituição por componentes fora de

especificação poderá causar, choque, incêndio, e/

ou outros riscos.

5- Componentes que não são de segurança devem

ser substituídos por componentes com as mesmas

especificações técnicas que consta na lista de

materiais.

, nesses casos é

2 Manual de Serviço

6- AVISO SOBRE ALTERAÇÕES NO APARELHO:

Não faça alterações ou modificações nos sistemas

elétricos ou mecânicos deste aparelho. Alterações

ou acréscimos de ítens como conexões auxiliares,

cabos e acessórios poderão alterar as

características de segurança deste aparelho e criar

risco para o usuário. Quaisquer alterações não

autorizadas pelo fabricante invalidarão a garantia

deste produto e farão do técnico, responsável por

danos a pessoa ou à propriedade.

Page 4

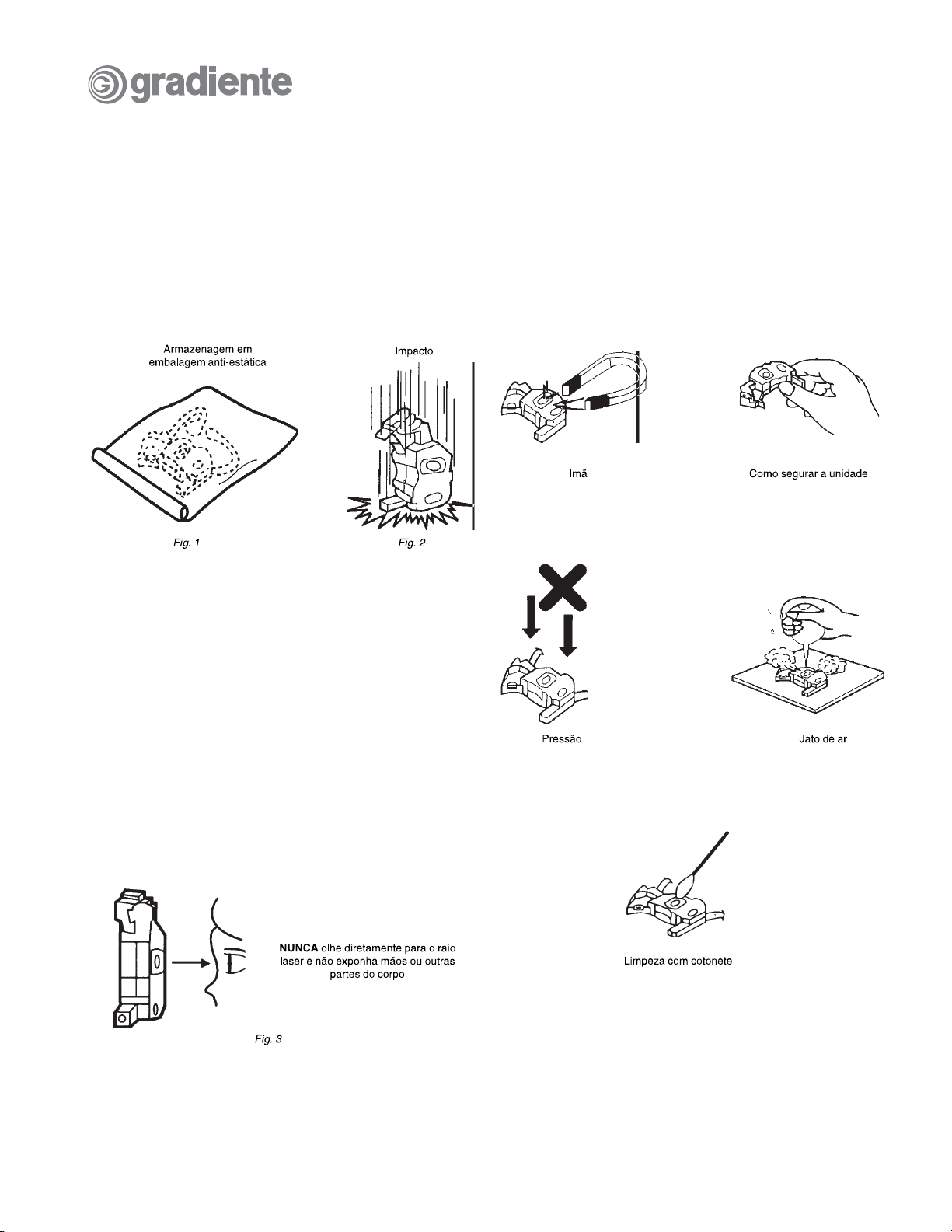

PRECAUÇÕES DE MANUTENÇÃO

Nota a respeito do manuseio da unidade óptica

1. Transporte e armazenagem

a) A unidade deve permanecer em sua embalagem antí-

estática até o momento de ser usada (Fig. 1).

b) A unidade nunca deve ser submetida a pressões

externas ou impactos (Fig. 2).

2. Reparos

a) A unidade incorpora um forte magneto e nunca deve

ser envolvida em materiais magnéticos.

b) A unidade deve ser sempre manuseada de forma

adequada e cuidadosamente, evite exercer pressões

externas e impactos. Se for submetida a fortes

pressões ou impactos, o resultado pode ser um mal

funcionamento ou danos ao PCI.

c) Cada unidade é ajustada com um alto grau de

precisão, e por esta razão os parafusos de ajuste

nunca devem ser tocados.

d) O raio laser pode danificar a visão!

Nunca olhe diretamente para o raio laser.

Nunca alimente uma unidade que tenha partes

externas (lentes e etc) danificados.

3. Limpeza da lente

a) Se houver poeira na superfície da lente, esta deve

ser limpa com um jato de ar (como o usado para

lentes de câmera). A lente é suportada por uma

delicada mola. Quando for limpar a lente, um

cotonete pode ser usado com cuidado.

Manual de Serviço 3

Page 5

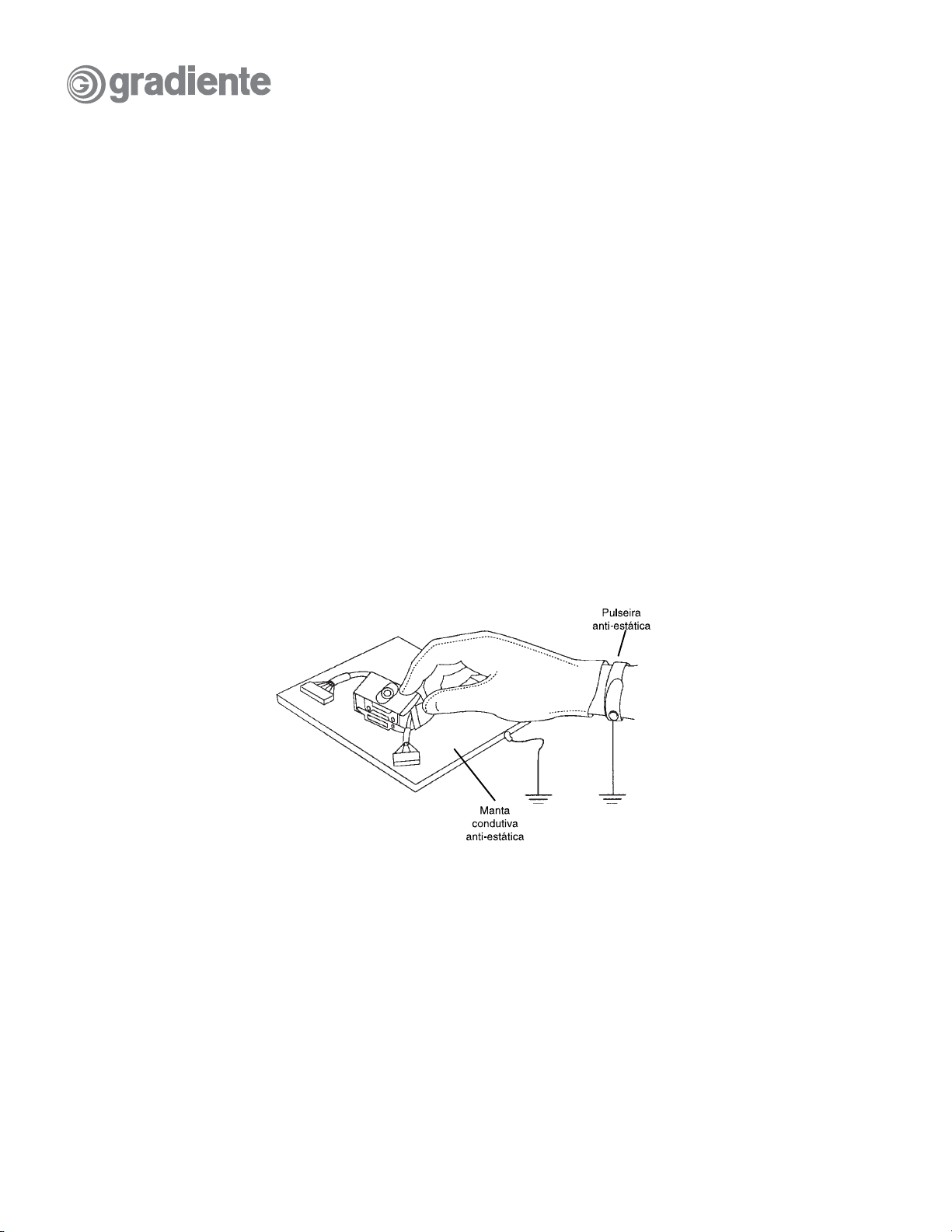

NOTA SOBRE A MANUTENÇÃO DE CD/DVD PLAYERS

1. Preparação

a) Os CD Players incorporam um grande número de

CI’s e uma unidade óptica (diodo laser). Estes

componentes são sensíveis e facilmente afetados

por eletricidade estática. Se a eletricidade estática

for de alta voltagem, estes componentes podem ser

danficados e por isso devem ser manuseados com

cuidado.

b) A unidade é composta de alguns componentes

ópticos e outros componentes de alta precisão. É

necessário muito cuidado e deve-se evitar o reparo

ou a armazenagem em locais onde a temperatura e

a umidade forem altas, onde fortes campos

magnéticos estiverem presentes e onde houver

muita poeira.

2. Reparo

a) Antes de trocar qualquer componente desligue o

cabo de força da tomada.

b) Todos os instrumentos de medição e as ferramentas

devem estar aterradas.

c) A bancada de trabalho deve estar coberta com uma

manta condutiva anti-estática aterrada.

d) Para evitar fuga de AC, as partes metálicas do ferro

de soldar devem estar aterradas.

e) O corpo do técnico deve estar aterrado por uma

pulseira anti-estática com um resistor de 1MΩ.

f) Deve-se evitar que a unidade entre em contato com

a roupa e receba descarga de estática não desviada

pela pulseira.

g) O raio laser emitido pela unidade NUNCA deve ser

direcionado aos olhos ou partes do corpo.

4 Manual de Serviço

Page 6

ESPECIFICAÇÕES TÉCNICAS D-470

Modelo ......................................................................................................................................... D-470

Tipo ................................................................................................................... Multimedia DVD Player

GERAL

Alimentação de rede ................................................................................................ 90~250Vc.a 50/60Hz

Consumo standby ........................................................................................................................... 4,5W

Consumo máximo ............................................................................................................................ 15W

Peso ............................................................................................................................... 2,1kg (líquido)

Dimensões (L x P x A em mm) ........................................................................................... 360 x 251 x 48

Temperatura de Operação ......................................................................................................... 5°C~40°C

Umidade de Operação ............................................................................................................ 20% a 80%

DISCOS

DVD (Disco Versátil Digital)

Velocidade de leitura ...........................................................................................................3,4 m/s

Tempo de reprodução apropriado ................................................................................... 135 minutos

(Disco de lado único, camada única)

CD 8cm (Disco Compacto)

Velocidade de leitura .................................................................................................. 1,2 a 1,4 m/s

Tempo de reprodução máximo ......................................................................................... 74 minutos

CD 12cm

Velocidade de leitura .................................................................................................. 1,2 a 1,4 m/s

Tempo de reprodução máximo ......................................................................................... 20 minutos

MP3

Sistema de arquivos ................................................................................................................. ISO 9660

Formato......................................................................................................................... MPEG 1, Layer 3

Bitrate ............................................................................................................ 128~256 kbps (@44,1kHz)

SAÍDAS DE VÍDEO

Vídeo composto ............................................................................................................ 1,0 Vp-p, 75ohms

Component video....................................................................................................... Y=1,0Vp-p, 75ohms

Pr-0,70 Vp-p, 75ohms

Pb=0,70 Vp-p, 75ohms

S-Vídeo

Sinal de luminância ....................................................................................................... 1,0 Vp-p, 75ohms

Sinal de crominância .................................................................................................. 0,286 Vp-p, 75ohms

SAÍDAS DE ÁUDIO

Nível de saida

Analógica ............................................................................................................................. 2Vp-p

Digital Coaxial.................................................................................................................... 0,5Vp-p

Resposta de frequência*

CD (EIAT) ................................................................................................................... 20Hz~20kHz

DVD (@ 48kHz)........................................................................................................... 20Hz~22kHz

DVD (@ 96kHz)........................................................................................................... 20Hz~44kHz

Relação S/N ................................................................................................................................ >92 dB

Distorção Harmônica Total ........................................................................................................... <0,04%

* Especificação nominal.

Projeto e especificações técnicas sujeitos a alteração sem aviso prévio.

Manual de Serviço 5

Page 7

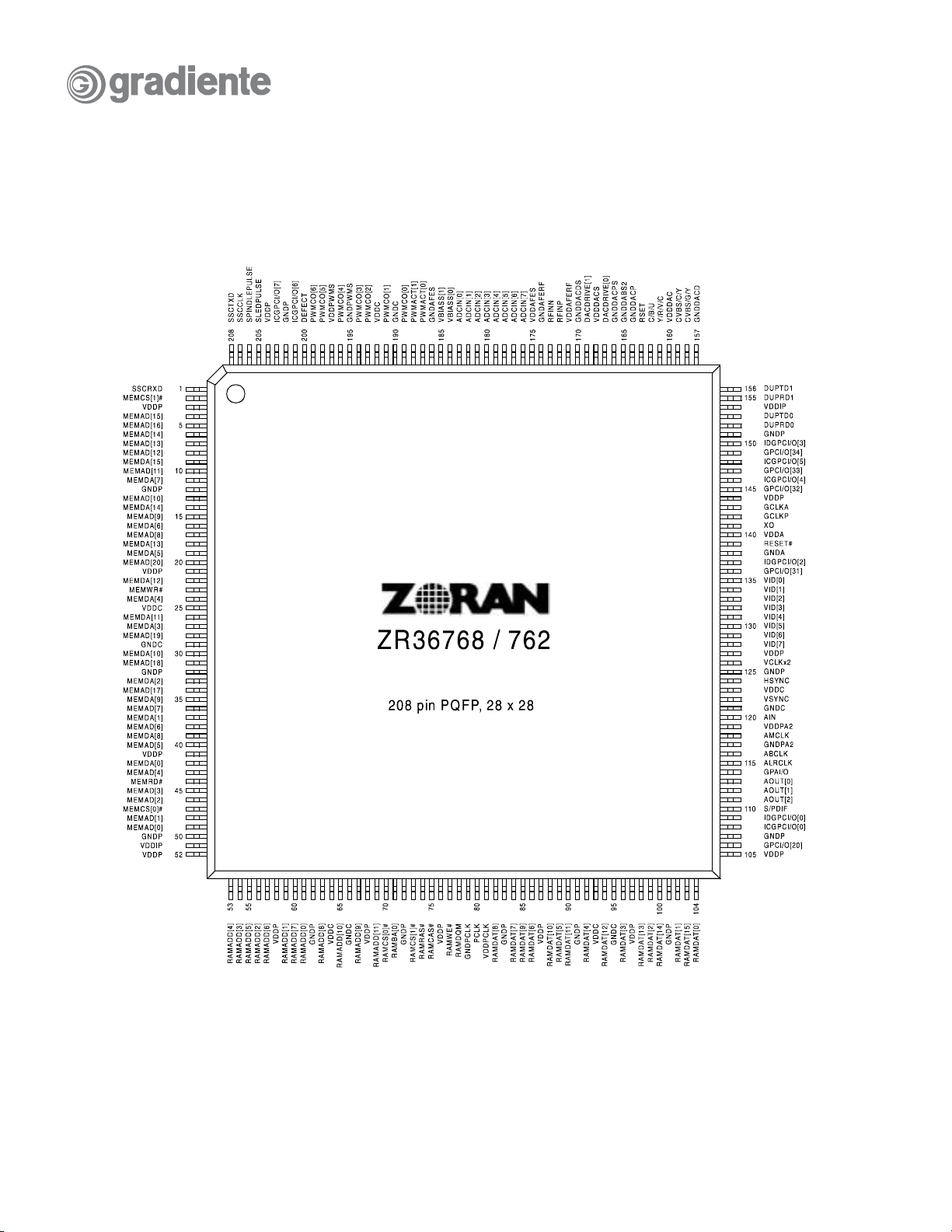

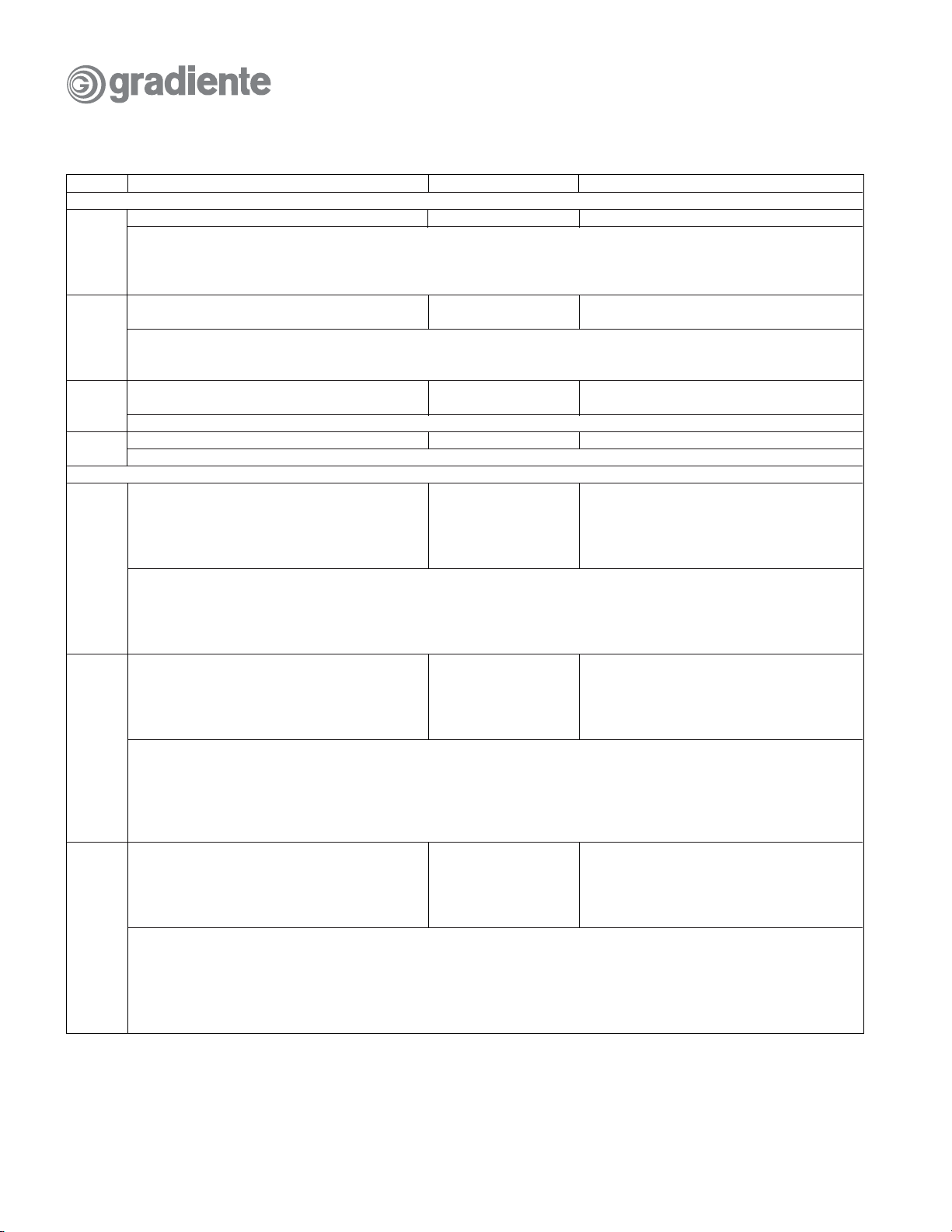

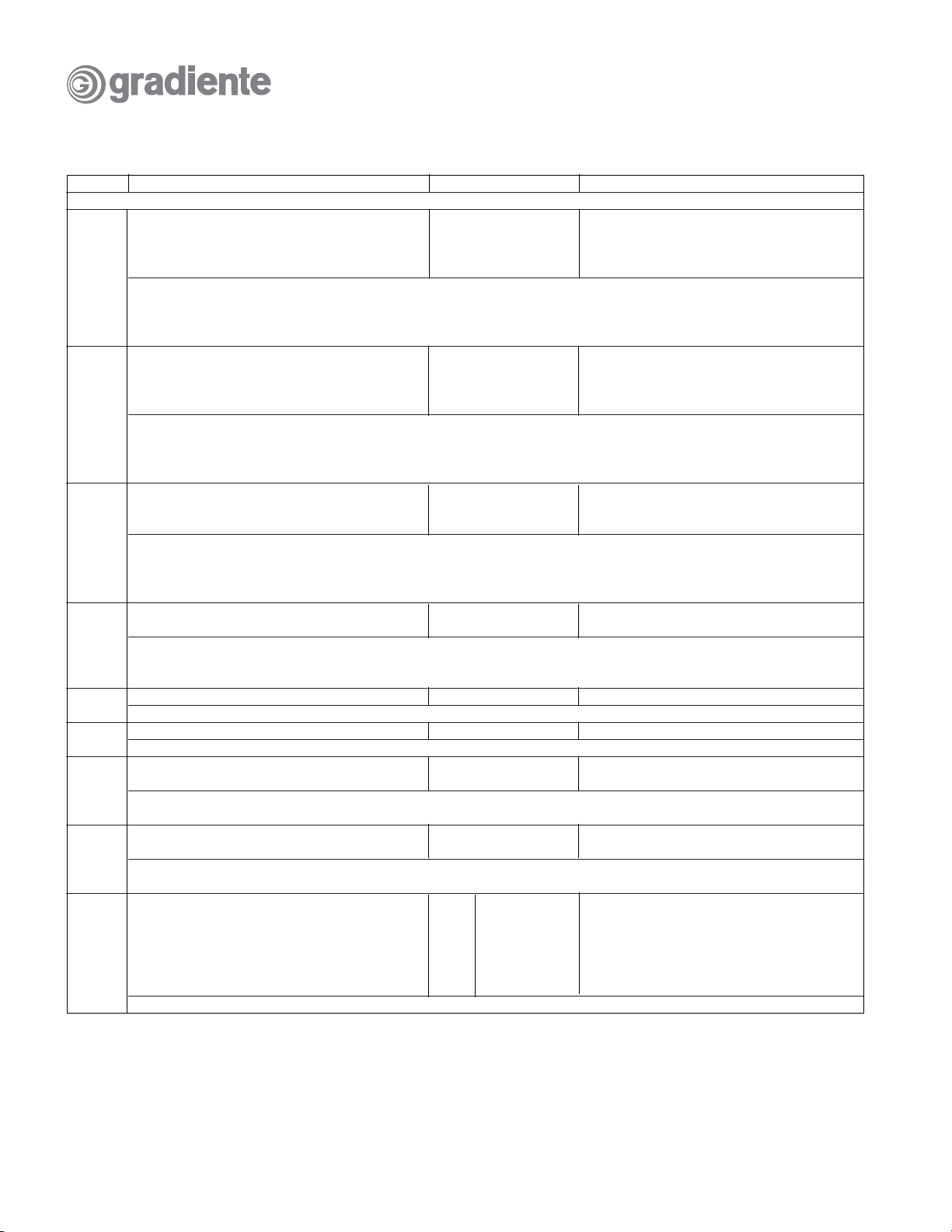

DESCRIÇÃO DOS PINOS DOS PRINCIPAIS CIRCUITOS INTEGRADOS

1. Diagrama de blocos do CI MPEG

6 Manual de Serviço

ZR36768/762

Page 8

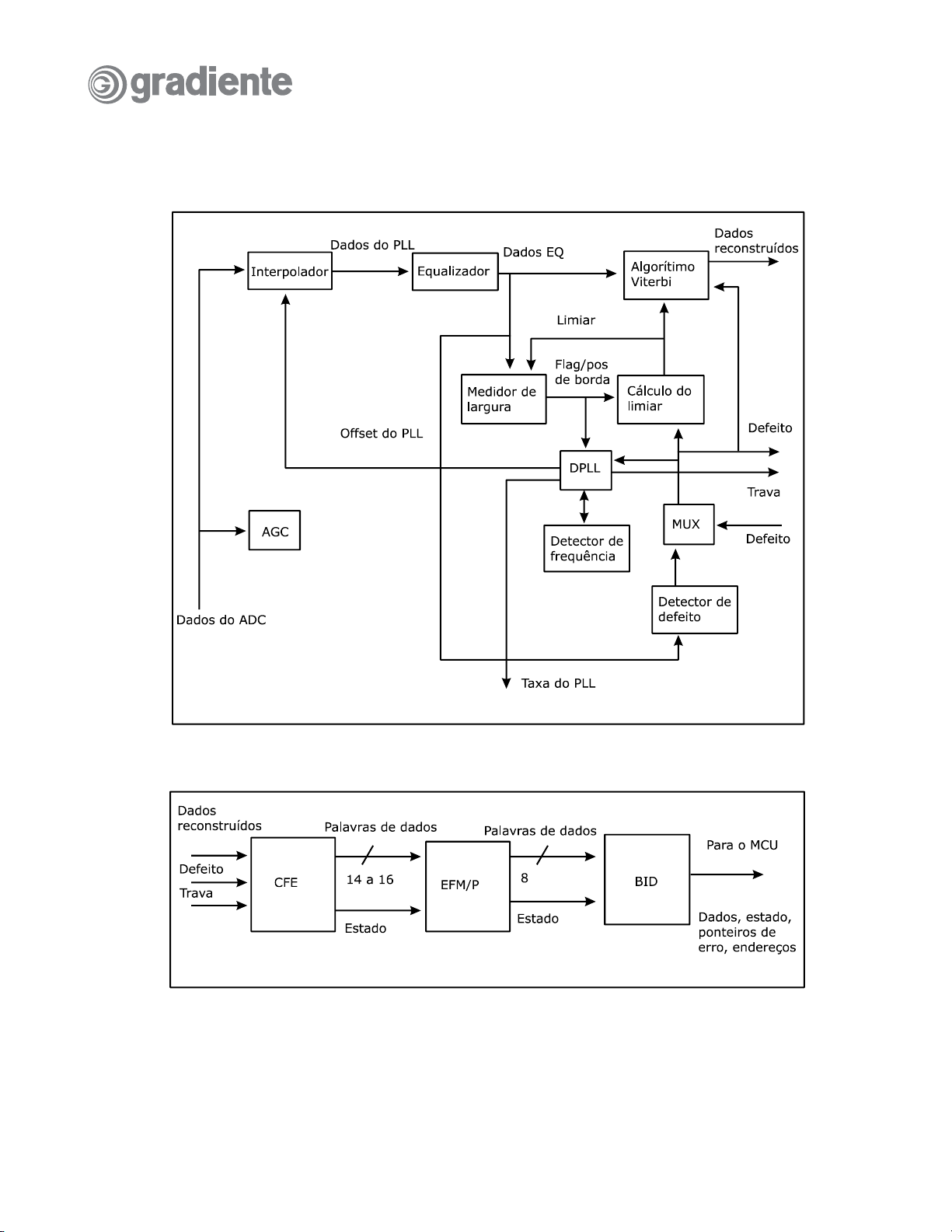

Diagrama de blocos DRC

Diagrama de blocos CSTP

Manual de Serviço 7

Page 9

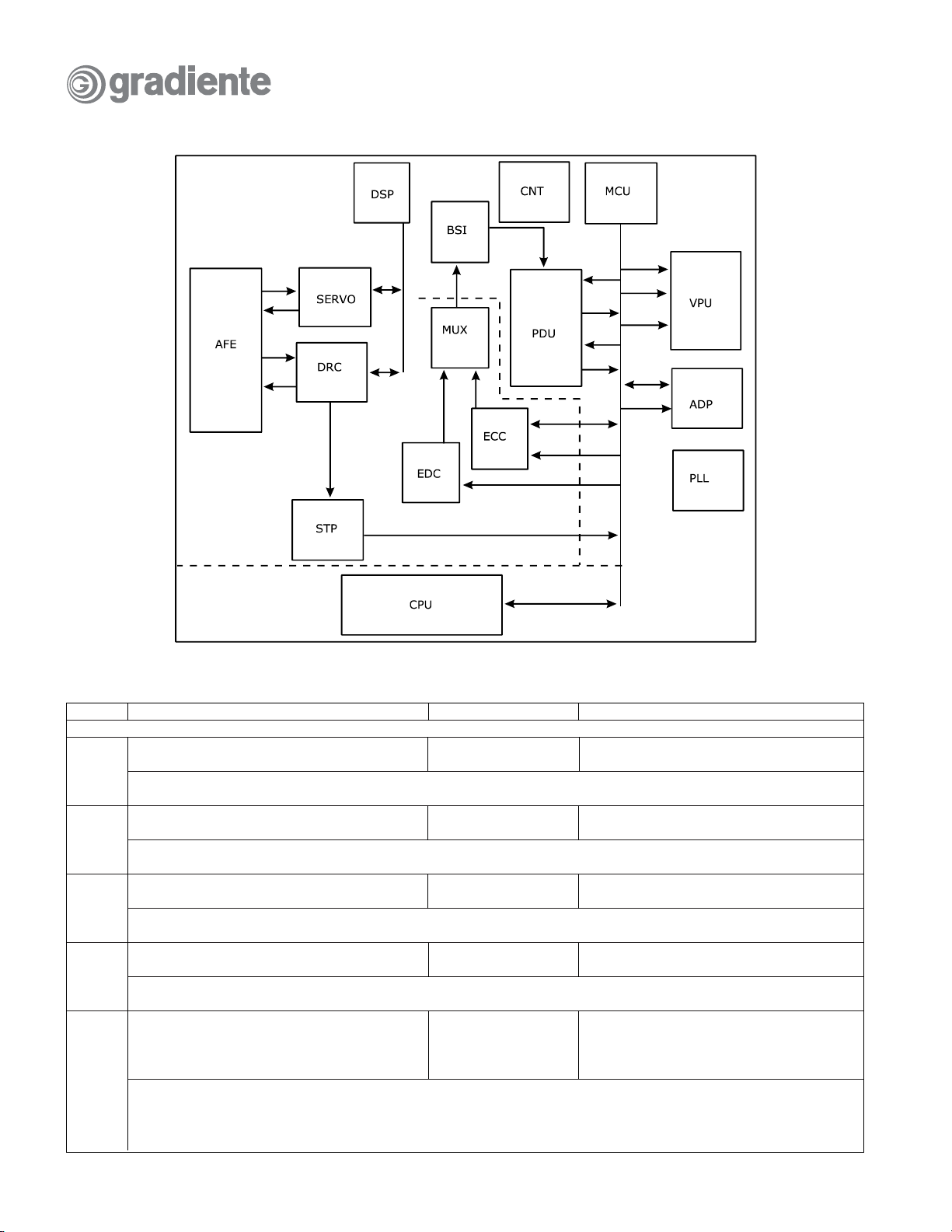

Diagrama de blocos do Vaddis ZR36768/762

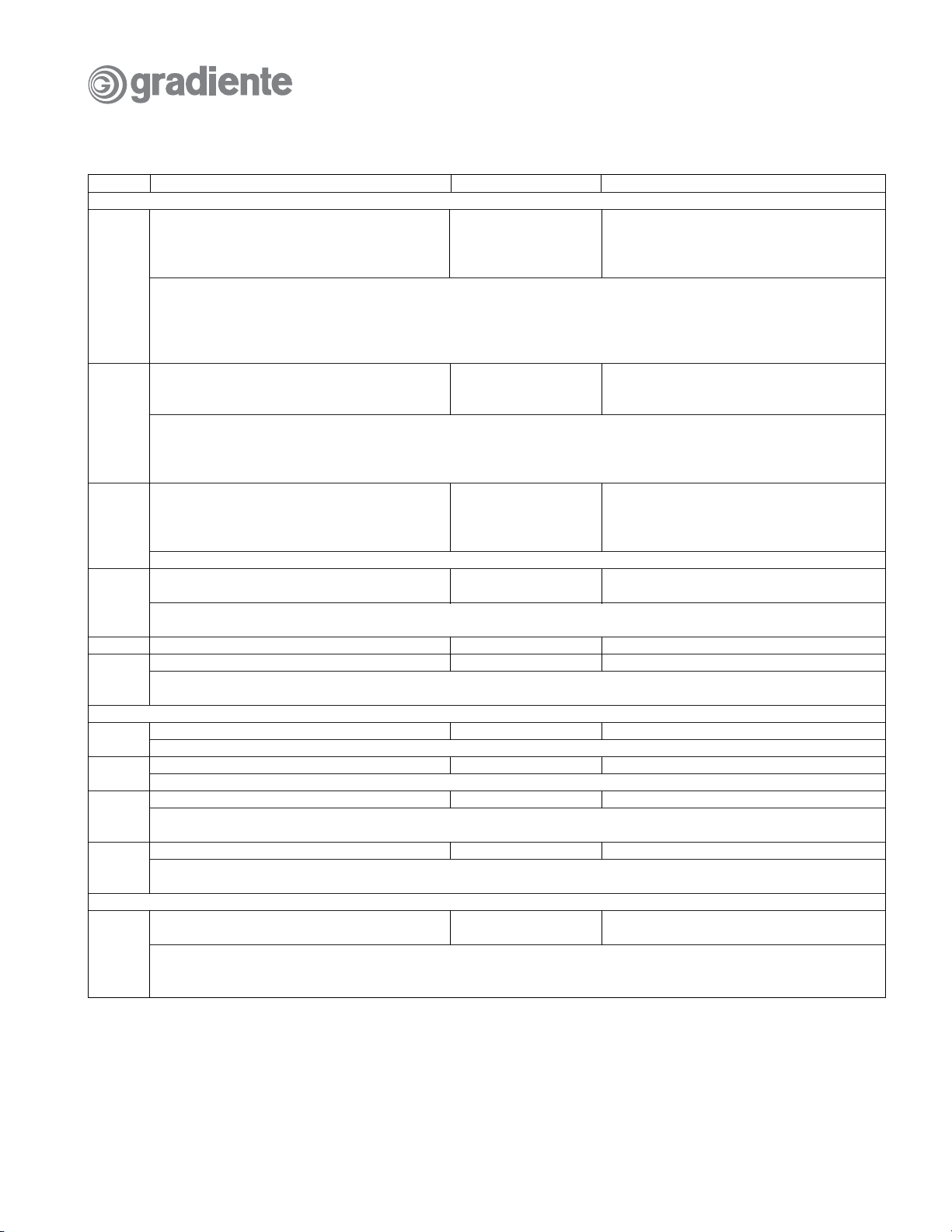

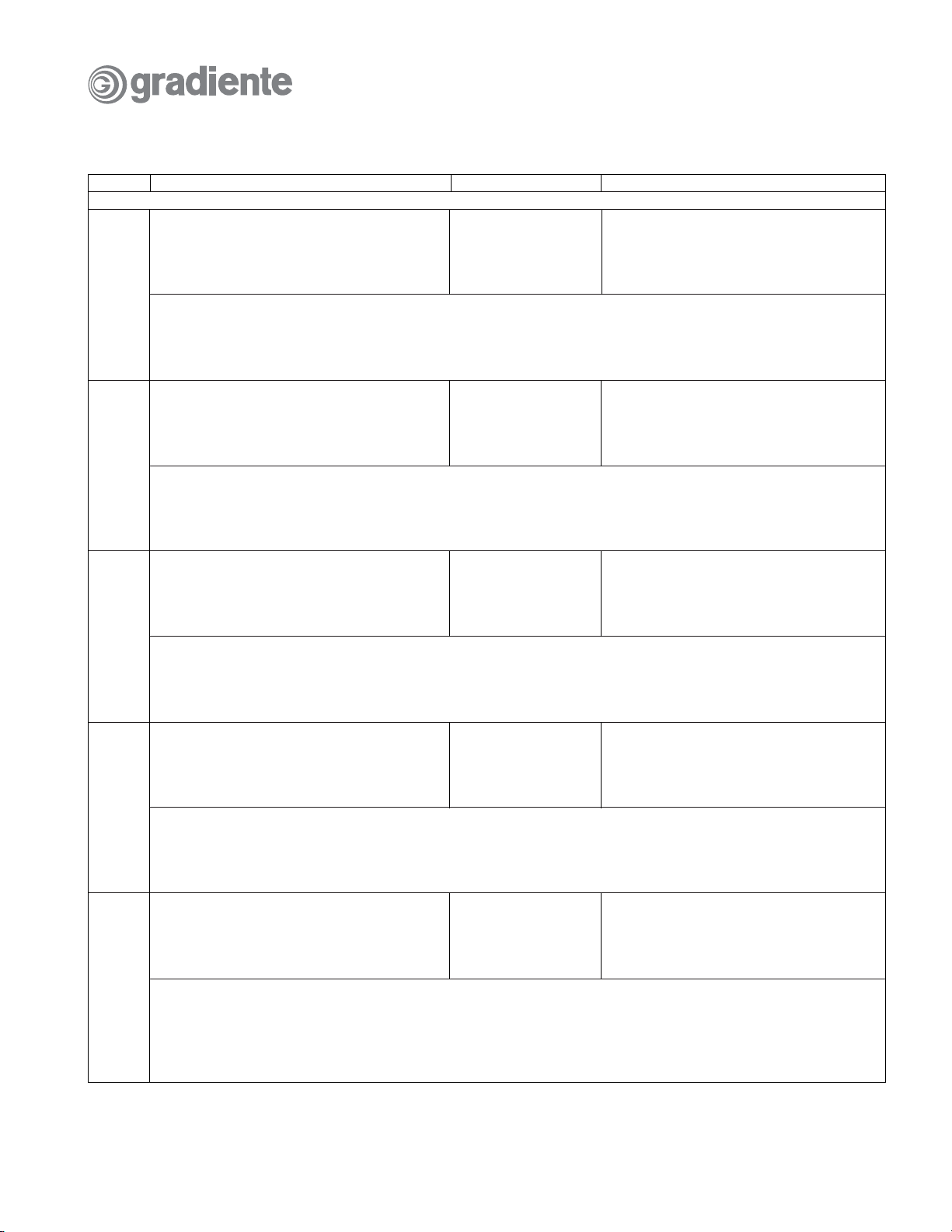

Descrição dos pinos do Vaddis 6E

Pino Nome Direção Estado durante/depois do RESET

Interface da CPU (15 pinos)

153 DUPTD0 O Durante RESET: Saida (alta)

GPCI/O[36] I/O Depois RESET: Entrada(r.t.)

DUPTD0: Primeira saída de dados de debug da UART

GPCI/O[36]:Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP

152 DUPRD0 I Durante RESET: Entrada (p.u.)

GPCI/O[35] I/O Depois RESET: Entrada (r.t.)

DUPRD0: Primeira saída de dados de debug da UART

GPCI/O[35]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP

156 DPUTD1 O Durante RESET: Entrada (p.u.)

GPCI/O[38] I/O Depois RESET: Entrada (r.t.)

DPUTD1: Segunda saída de dados de debug da UART

GPCI/O[38]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP

155 DPUTD1 O Durante RESET: Entrada (p.u.)

GPCI/O[37] I/O Depois RESET: Entrada (r.t.)

DPUTD1: Segunda saída de dados de debug da UART

GPCI/O[37]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP

106 GPCI/O[20] I/O Durante RESET: Entrada (p.d.)

CPUNMI I Depois RESET: Entrada (r.t.)

SDATA[0] I

PM[0] O

GPCI/O[20]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP

CPUNMI: Entrada de interrupção não-mascarável da CPU

SDATA[0]: Entrada de dados de amostragem do canal do SERVO para bypass do front-end analógico.

PM[0]: Saída de dados de prova do mux.

8 Manual de Serviço

Page 10

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Interface da CPU (15 pinos) - continuação

108 ICGPCI/O[0] I/O Durante RESET: Entrada (p.d.)

AOUT[3] O Depois RESET: Entrada (r.t.)

SDATA[1] I

PM[1] O

ICGPCI/O[0]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para a CPU.

AOUT[3]: Saída serial de áudio digital estéreo.

SDATA[1]: Entrada de dados de amostragem do canal do SERVO para bypass do front-end analógico.

PM[1]: Saída de dados de prova do mux.

109 IDGPCI/O[0] I/O Durante RESET: Entrada (p.d.)

SDATA[2] O Depois RESET: Entrada (r.t.)

PM[2] I

IDGPCI/O[0]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para a CPU.

SDATA[2]: Entrada de dados de amostragem do canal do SERVO para bypass do front-end analógico.

PM[2]: Saída de dados de prova do mux.

149 GPCI/O[34] I/O Durante RESET: Entrada (p.d.)

147 GPCI/O[33] I/O Depois RESET: Entrada (r.t.)

145 GPCI/O[32] I/O

136 GPCI/O[31] I/O

Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

148 ICGPCI/O[5] I/O Durante RESET: Entrada (p.d.)

146 ICGPCI/O[4] I/O Depois RESET: Entrada (r.t.)

Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para a CPU.

150 IDGPCI/O[3] I/O Durante RESET: Entrada (p.d.)

137 IDGPCI/O[2] I/O Depois RESET: Entrada (r.t.)

Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para a CPU.

Sinais do PLL (4 pinos)

139 RESET# ID Entrada

Entrada de reset. Depois que este sinal for desativado, o Vaddis 6E começa o processo de inicialização.

142 GCLKP ID Entrada

Entrada de clock ou de cristal de 27,000MHz para geração de clock do processmento principal.

141 XO AO Saída

Saída para um cristal que for conectado ao GCLKP. Se um cristal não for usado em GCLKP, XO deve ser

mantido desconectado.

143 GCLKA ID Entrada

Entrada de clock de 27,000MHz para geração de clock de áudio principal. Deve ser conectado ao GCLKP

em operação normal.

Porta de vídeo analógica (5 pinos)

158 CVBS/G/Y AO

(DAC A)

Quando a saída do Vaddis 6E for vídeo composto, este sinal é CVBS.

Quando a saída do Vaddis 6E for RGB, este é o sinal verde.

Quando a saída do Vaddis 6E for YUV, este é o sinal Y.

Manual de Serviço 9

Page 11

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Porta de vídeo analógica (5 pinos) - Continuação

161 Y/R/V/C AO

Quando a saída do Vaddis 6E for vídeo composto, este sinal é Y.

Quando a saída do Vaddis 6E for RGB, este é o sinal vermelho

Quando a saída do Vaddis 6E for YUV, este é o sinal V.

Quando a saída do Vaddis 6E for SCART, este é o sinal C.

162 C/B/U AO

(DAC C)

Quando a saída do Vaddis 6E for vídeo composto, este sinal é C.

Quando a saída do Vaddis 6E for RGB, este é o sinal azul.

Quando a saída do Vaddis 6E for YUV, este é o sinal U.

159 CVBS/C/Y AO

(DAC D)

A saída desta linha pode ser CVBS, C ou Y. A seleção é independente da seleção dos outros três DACs.

163 RSET AI

Carga resisitiva para ajuste de ganho dos DACs.

Porta de vídeo digital, CPU, DSP e debug do ADP (11 pinos)

128 VID[7] O Durante RESET: Entrada (p.d.)

ICETMS I Depois RESET: Entrada (r.t.)

DJTMS I

GPCI/O[26] I/O

DACTEST[7] I

VID[7]: Saída de lum./crom. do vídeo digital, multiplexados no tempo de acordo com o padrão CCIR656.

ICETMS: Interface de debug do ADP

DJTDS: Interface de debug do DSP

GPCI/O[26]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP

DACTEST[7]: Entrada de teste do DAC

128 VID[6] O Durante RESET: Entrada (p.d.)

ICETMI I Depois RESET: Entrada (r.t.)

DJTDI I

ICGPCI/O[2] I/O

DACTEST[6] I

VID[6]: Saída de lum./crom. do vídeo digital, multiplexados no tempo de acordo com o padrão CCIR656.

ICETMI: Interface de debug do ADP

DJTDI: Interface de debug do DSP

ICGPCI/O[2]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para a CPU.

DACTEST[6]: Entrada de teste do DAC

130 VID[5] O Durante RESET: Entrada (p.d.)

ICETDO O Depois RESET: Entrada (r.t.)

DJTDO O

IDGPCI/O[1] I/O

DACTEST[5] I

VID[5]: Saída de lum./crom. do vídeo digital, multiplexados no tempo de acordo com o padrão CCIR656.

ICETDO: Interface de debug do ADP

DJTDO: Interface de debug do DSP

IDGPCI/O[1]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para a CPU.

DACTEST[5]: Entrada de teste do DAC

10 Manual de Serviço

Page 12

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Porta de vídeo digital, CPU, DSP e debug do ADP (11 pinos) - continuação

131 VID[4] O Durante RESET: Entrada (p.d.)

ICETCK I Depois RESET: Entrada (r.t.)

DJTCK I

GPCI/O[27] I/O

DACTEST[4] I

VID[4]: Saída de lum./crom. do vídeo digital, multiplexados no tempo de acordo com o padrão CCIR656.

ICETCK: Interface de debug do ADP

DJTCK: Interface de debug do DSP

GPCI/O[27]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DACTEST[4]: Entrada de teste do DAC

132 VID[3] O Durante RESET: Entrada (p.d.)

DJTMS I Depois RESET: Entrada (r.t.)

GPCI/O[28] I/O

DACTEST[3] I

SERVOCLK O

VID[3]: Saída de lum./crom. do vídeo digital, multiplexados no tempo de acordo com o padrão CCIR656.

DJTMS: Interface de debug do DSP

GPCI/O[28]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DACTEST[3]: Entrada de teste do DAC

SERVOCLK: Saída de dados de amostragem do canal do SERVO para bypass do front-end analógico.

133 VID[2] O Durante RESET: Entrada (p.d.)

DJTDI I Depois RESET: Entrada (r.t.)

GPCI/O[29] I/O

DACTEST[2] I

SSEL[0] O

VID[2]: Saída de lum./crom. do vídeo digital, multiplexados no tempo de acordo com o padrão CCIR656.

DJTDI: Interface de debug do DSP

GPCI/O[29]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DACTEST[2]: Entrada de teste do DAC

SSEL[0]: Saída de seleção do canal do SERVO para bypass do front-end analógico.

134 VID[1] O Durante RESET: Entrada (p.d.)

DJTDO O Depois RESET: Entrada (r.t.)

GPCI/O[30] I/O

DACTEST[1] I

SSEL[1] O

VID[1]: Saída de lum./crom. do vídeo digital, multiplexados no tempo de acordo com o padrão CCIR656.

DJTDO: Interface de debug do DSP

GPCI/O[30]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DACTEST[1]: Entrada de teste do DAC

SSEL[1]: Saída de seleção do canal do SERVO para bypass do front-end analógico.

135 VID[0] O Durante RESET: Entrada (p.d.)

DJTCK I Depois RESET: Entrada (r.t.)

ICGPCI/O[3] I/O

DACTEST[0] I

SSEL[2] O

VID[0]: Saída de lum./crom. do vídeo digital, multiplexados no tempo de acordo com o padrão CCIR656.

DJTCK: Interface de debug do DSP

ICGPCI/O[3]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para a CPU.

DACTEST[0]: Entrada de teste do DAC

SSEL[2]: Saída de seleção do canal do SERVO para bypass do front-end analógico.

Manual de Serviço 11

Page 13

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Porta de vídeo digital, CPU, DSP e debug do ADP (11 pinos) - continuação

126 VCLKx2 O Durante RESET: Entrada (p.d.)

COSYNC O Depois RESET: Entrada (r.t.)

ICGPCI/O[1] I/O

CJTMS I

DACTEST[10] I

PM[11] O

VCLKx2: Saída de clock do vídeo digital. 27,000MHz.

COSYNC: Saída de sincronismo composto. Ativo somente quando a saída de analógico componente for

selecionada.

ICGPCI/O[1]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para a CPU.

CJTMS: Interface de debug da CPU

DACTEST[10]: Entrada de teste do DAC

PM[11]: Saída de dados de prova do mux.

124 HSYNC# O Durante RESET: Entrada (p.d.)

GPCI/O[25] I/O Depois RESET: Entrada (r.t.)

CJTDO O

DACTEST[8] I

PM[10] O

HSYNC#: Sinal de sincronismo horizontal do vídeo digital.

GPCI/O[25]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

CJTDO: Interface de debug da CPU

DACTEST[8]: Entrada de teste do DAC

PM[10]: Saída de dados de prova do mux.

122 VSYNC# O Durante RESET: Entrada (p.d.)

GPCI/O[24] I/O Depois RESET: Entrada (r.t.)

CJTDI I

DACTEST[9] I

PM[9] O

VSYNC#: Sinal de sincronismo vertical do vídeo digital.

GPCI/O[24]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

CJTDI: Interface de debug da CPU

DACTEST[9]: Entrada de teste do DAC

PM[9]: Saída de dados de prova do mux.

Porta de áudio digital e Debug da CPU (9 pinos)

120 AIN I Durante RESET: Entrada (p.d.)

GPCI/O[23] I/O Depois RESET: Entrada (r.t.)

CJTCK I

PM[8] O

AIN: Entrada serial do áudio digital estéreo

GPCI/O[23]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

CJTCK: Interface de debug da CPU

PM[8]: Saída de dados de prova do mux.

118 AMCLK I/O Durante RESET: Entrada (p.d.)

Depois RESET: Entrada (r.t.)

Entrada/saída de clock principal do áudio. 128,192,256 ou 384 vezes a frequência de amostragem.

110 S/PDIF O Durante RESET: Entrada (p.d.)

SDATA[3] I Depois RESET: Entrada (r.t.)

PM[3] O

S/PDIF: Saída do transmissor S/PDIF para dados de áudio digital codificado ou reconstruído.

SDATA[3]: Entrada de dados de amostragem do canal do SERVO para bypass do front-end analógico.

PM[3]: Saída de dados de prova do mux.

12 Manual de Serviço

Page 14

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Porta de áudio digital e Debug da CPU (9 pinos) - continuação

111 AOUT[2] O Durante RESET: Entrada (p.d.)

GPCI/O[21] I/O Depois RESET: Entrada (r.t.)

SDATA[4] I

PM[4] O

AOUT[2]: Saída serial do áudio digital estéreo

GPCI/O[21]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

SDATA[4]: Entrada de dados de amostragem do canal do SERVO para bypass do front-end analógico.

PM[4]: Saída de dados de prova do mux.

112 AOUT[1] O Durante RESET: Entrada (p.d.)

GPCI/O[22] I/O Depois RESET: Entrada (r.t.)

SDATA[5] I

PM[5] O

AOUT[1]: Saída serial do áudio digital estéreo

GPCI/O[22]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

SDATA[5]: Entrada de dados de amostragem do canal do SERVO para bypass do front-end analógico.

PM[5]: Saída de dados de prova do mux.

113 AOUT[0] O Durante RESET: Entrada (p.d.)

SDATA[5] I Depois RESET: Entrada (r.t.)

PM[6] O

AOUT[0]: Saída serial do áudio digital estéreo

SDATA[5]: Entrada de dados de amostragem do canal do SERVO para bypass do front-end analógico.

PM[6]: Saída de dados de prova do mux.

115 ALRCLK O Durante RESET: Entrada (p.d.)

Depois RESET: Entrada (r.t.)

Saída de seleção de áudio digital esquerdo/direito para a porta de áudio. Onda quadrada, na frequência

de amostragem.

116 ABCLK O Durante RESET: Entrada (p.d.)

Depois RESET: Entrada (r.t.)

Saída de clock de bit para áudio digital. O dados em AOUT e AIN são enviados ou retidos, respectivamente,

na borda deste clock.

114 GPAI/O I/O Durante RESET: Entrada (p.d.)

AOUT[3] O Depois RESET: Entrada (r.t.)

SDATA[7] I

PM[7] O

GPAI/O: Saída/Entrada de uso geral, monitorada/controlada pelo SW ADP.

AOUT[3]: Saída serial do áudio digital estéreo

SDATA[7]: Entrada de dados de amostragem do canal do SERVO para bypass do front-end analógico.

PM[7]: Saída de dados de prova do mux.

Interface do carregador, Interface do amplificador de RF, Interface de fluxo de AV (28 pinos)

185 VBIASS[1] AI

184 VBIASS[0] AI

Entradas de tensão de referência do sinal analógico do servo.

169 DACDRIVE[1] AO

167 DACDRIVE[0] AO

Saída de sinais do drive do DAC

Manual de Serviço 13

Page 15

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Interface do carregador, Interface do amplificador de RF, Interface de fluxo de AV (28 pinos)

187 PWMACT[0] O Durante RESET: Entrada (p.d.)

GPCI/O[39] I/O Depois RESET: Entrada (r.t.)

DVDDAT[0] I

NRZDATA I

PWMACT[0]: Saída do sinal PWM0.

GPCI/O[39]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DVDDAT[0]: Linha de entrada de dados AV para bypass do front-end.

NRZDATA: Entrada de dados NRZ para front-end analógico e bypass do canal de leitura de dados.

188 PWMACT[1] O Durante RESET: Entrada (p.d.)

GPCI/O[40] I/O Depois RESET: Entrada (r.t.)

DVDDAT[1] I

NRZCLK I

PWMACT[1]: Saída do sinal PWM1.

GPCI/O[40]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DVDDAT[1]: Linha de entrada de dados AV para bypass do front-end.

NRZCLK: Entrada de dados NRZ para front-end analógico e bypass do canal de leitura de dados.

205 SLEDPULSE I Durante RESET: Entrada (p.d.)

IDGPCI/O[6] I/O Depois RESET: Entrada (r.t.)

DVDSOS I

SLEDPULSE: Entrada do codificador óptico do Sled.

IDGPCI/O[6]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para o DSP.

DVDSOS: Entrada de indicação de início de setor AV para bypass do front-end.

206 SPINDLEPULSE I Durante RESET: Entrada (p.d.)

IDGPCI/O[7] I/O Depois RESET: Entrada (r.t.)

SPINDLEPULSE: Entrada do codificador óptico do Spindle.

IDGPCI/O[7]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para o DSP.

172 RFINP AI

Entrada de sinal positivo de RF (entrada diferencial) ou entrada de sinal de RF (linha única)

173 RFINN AI

Entrada de sinal negativo de RF (entrada diferencial) ou entrada de sinal de RF de referência.

176 ADCIN[7] AI

AFETESTN AI/O

ADCIN[7]: Entrada de sinal do ADC do SERVO do amplificador de RF.

AFETESTN: Entrada ou saída diferencial de sinal (negativo) de teste do front-end analógico.

177 ADCIN[6] AI

AFETESTP AI/O

ADCIN[6]: Entrada de sinal do ADC do SERVO do amplificador de RF.

AFETESTP: Entrada ou saída diferencial de sinal (positivo) de teste do front-end analógico.

178 ADCIN[5] AI

179 ADCIN[4] AI

180 ADCIN[3] AI

181 ADCIN[2] AI

182 ADCIN[1] AI

183 ADCIN[0] AI

Entradas de sinal do ADC do SERVO do amplificador de RF.

14 Manual de Serviço

Page 16

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Interface do carregador, Interface do amplificador de RF, Interface de fluxo de AV (28 pinos)

189 PWMCO[0] O Durante RESET: Entrada (p.d.)

GPCI/O[41] I/O Depois RESET: Entrada (r.t.)

DVDDAT[2] I

NRZLOCK I

PWMCO[0]: Saída do sinal PWM2.

GPCI/O[41]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DVDDAT[2]: Linha de entrada de dados AV para bypass do front-end.

NRZLOCK: Entrada de dados NRZ para front-end analógico e bypass do canal de leitura de dados.

191 PWMCO[1] O Durante RESET: Entrada (p.d.)

GPCI/O[42] I/O Depois RESET: Entrada (r.t.)

DVDDAT[3] I

NRZDFCT I

PWMCO[1]: Saída do sinal PWM3.

GPCI/O[42]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DVDDAT[3]: Entrada de dados AV para bypass do front-end.

NRZDFCT: Entrada de defeito NRZ para front-end analógico e bypass do canal de leitura de dados.

193 PWMCO[2] O Durante RESET: Entrada (p.d.)

GPCI/O[43] I/O Depois RESET: Entrada (r.t.)

DVDDAT[4] I

RFDAT[0] I

PWMCO[2]: Saída do sinal PWM4.

GPCI/O[43]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DVDDAT[4]: Entrada de dados AV para bypass do front-end.

RFDAT[0]: Entrada de dados de amostragem do canal de RF para bypass do front-end analógico.

194 PWMCO[3] O Durante RESET: Entrada (p.d.)

GPCI/O[44] I/O Depois RESET: Entrada (r.t.)

DVDDAT[5] I

RFDAT[1] I

PWMCO[3]: Saída do sinal PWM5.

GPCI/O[44]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DVDDAT[5]: Entrada de dados AV para bypass do front-end.

RFDAT[1]: Entrada de dados de amostragem do canal de RF para bypass do front-end analógico.

196 PWMCO[4] O Durante RESET: Entrada (p.d.)

GPCI/O[45] I/O Depois RESET: Entrada (r.t.)

DVDDAT[6] I

RFDAT[2] I

PWMCO[4]: Saída do sinal PWM6.

GPCI/O[45]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DVDDAT[6]: Entrada de dados AV para bypass do front-end.

RFDAT[2]: Entrada de dados de amostragem do canal de RF para bypass do front-end analógico.

198 PWMCO[5] O Durante RESET: Entrada (p.d.)

GPCI/O[46] I/O Depois RESET: Entrada (r.t.)

DVDDAT[7] I

RFDAT[3] I

PWMCO[5]: Saída do sinal PWM7.

GPCI/O[46]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

DVDDAT[7]: Entrada de dados AV para bypass do front-end.

RFDAT[3]: Entrada de dados de amostragem do canal de RF para bypass do front-end analógico.

Manual de Serviço 15

Page 17

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Interface do carreg., Interface do amplif. de RF, Interface de fluxo de AV (28 pinos) - continuação

199 PWMCO[6] O Durante RESET: Entrada (p.d.)

IDGPCI/O[4] I/O Depois RESET: Entrada (r.t.)

DVDREQ O

RFDAT[4] I

PWMCO[6]: Saída do sinal PWM8.

IDGPCI/O[4]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para o DSP.

DVDREQ: Saída de requisição de dados AV para bypass do front-end.

RFDAT[4]: Entrada de dados de amostragem do canal de RF para bypass do front-end analógico.

203 ICGPCI/O[7] I/O Durante RESET: Entrada (p.d.)

DVDERR I Depois RESET: Entrada (r.t.)

RFCLK O

PM[12] O

ICGPCI/O[7]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para o CPU.

DVDERR: Entrada de erro de AV para bypass do front-end.

RFCLK: Saída de clock de amostragem do canal de RF para bypass do front-end analógico.

PM[12]: Saída de dados de prova do mux.

200 DEFECT I/O Durante RESET: Entrada (p.d.)

IDGPCI/O[5] I/O Depois RESET: Entrada (r.t.)

DVDSTRB O

RFDAT[5] I

DEFECT: Saída ou entrada de sinal de defeito do disco

IDGPCI/O[5]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para o DSP.

DVDSTRB: Entrada de strobe de bit de dados (clock) para bypass do front-end.

RFDAT[5]: Entrada de dados de amostragem do canal de RF para bypass do front-end analógico.

201 ICGPCI/O[6] I/O Durante RESET: Entrada (p.d.)

DVDALID I Depois RESET: Entrada (r.t.)

RFCLK O

PM[16] O

ICGPCI/O[6]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP. Pode ser usada

como interrupção externa de uso geral para o CPU.

DVDALID: Entrada de dados válidos de AV para bypass do front-end.

RFCLK: Saída de clock de amostragem do canal de RF para bypass do front-end analógico.

PM[16]: Saída de dados de prova do mux.

16 Manual de Serviço

Page 18

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Interface da SDRAM (36 pinos)

103 RAMDAT[15] I/O Durante RESET: Entrada (p.d.)

100 RAMDAT[14] I/O Depois RESET: Entrada (r.t.)

98 RAMDAT[13] I/O

94 RAMDAT[12] I/O

90 RAMDAT[11] I/O

88 RAMDAT[10] I/O

85 RAMDAT[9] I/O

82 RAMDAT[8] I/O

84 RAMDAT[7] I/O

86 RAMDAT[6] I/O

89 RAMDAT[5] I/O

92 RAMDAT[4] I/O

96 RAMDAT[3] I/O

99 RAMDAT[2] I/O

102 RAMDAT[1] I/O

104 RAMDAT[0] I/O

Barramento de dados bidirecional da SDRAM

69 RAMADD[11] O Durante RESET: Saída (baixo)

65 RAMADD[10] O Depois RESET: Saída (baixo)

67 RAMADD[9] O

63 RAMADD[8] O

60 RAMADD[7] O

57 RAMADD[6] O

55 RAMADD[5] O

53 RAMADD[4] O

54 RAMADD[3] O

56 RAMADD[2] O

59 RAMADD[1] O

61 RAMADD[0] O

Saída do barramento de endereço da SDRAM

74 RAMRAS# O Durante RESET: Saída (alto)

Depois RESET: Saída (alto)

Seleção de linha da SDRAM.

75 RAMCAS# O Durante RESET: Saída (alto)

Depois RESET: Saída (alto)

Seleção de coluna da SDRAM.

80 PCLK O Durante RESET: Saída

Depois RESET: Saída

Saída de clock da SDRAM (o mesmo que o clock de processamento interno).

78 RAMDQM O Durante RESET: Saída (alto)

Depois RESET: Saída (alto)

Mascaramento de dados da SDRAM.

71 RAMBA[0] O Durante RESET: Saída (alto)

Depois RESET: Saída (alto)

Seleção de banco da SDRAM.

70 RAMCS[0]# O Durante RESET: Saída (alto)

RAMBA[1] O Depois RESET: Saída (alto)

RAMCS[0]#: Seleção de chip da SDRAM.

RAMBA[1]: Seleção de banco da SDRAM.

73 RAMCS[1]# O Durante RESET: Saída (alto)

Depois RESET: Saída (alto)

Seleção de chip da SDRAM.

Manual de Serviço 17

Page 19

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Interface da SDRAM (36 pinos) - continuação

77 RAMWE# O Durante RESET: Saída (Alto)

Depois RESET: Saída (Alto)

Habilitação de escrita da SDRAM

Interface SSC (3 pinos)

208 SSCTXD O Durante RESET: Entrada (p.d.)

GPCI/O[16] I/O Depois RESET: Entrada (r.t.)

PM[14] O

SSCTXD: Sinal de saída de dados SSC.

GPCI/O[16]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

PM[14]: Saída de dados de prova do mux.

1 SSCRXD I Durante RESET: Entrada (p.d.)

GPCI/O[17] I/O Depois RESET: Entrada (r.t.)

PM[15] O

SSCRXD: Entrada de dados SSC.

GPCI/O[17]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

PM[15]: Saída de dados de prova do mux.

207 SSCCLK I/O Durante RESET: Entrada (p.d.)

GPCI/O[47] I/O Depois RESET: Entrada (r.t.)

PM[13] O

SSCCLK: Entrada ou saída de sinal de clock SSC.

GPCI/O[47]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

PM[13]: Saída de dados de prova do mux.

Interface da PNVM/SRAM (41 pinos)

9 MEMDA[15] I/O Durante RESET: Entrada (p.d.)

14 MEMDA[14] I/O Depois RESET: Entrada (r.t.)

18 MEMDA[13] I/O

22 MEMDA[12] I/O

26 MEMDA[11] I/O

30 MEMDA[10] I/O

35 MEMDA[9] I/O

39 MEMDA[8] I/O

11 MEMDA[7] I/O

16 MEMDA[6] I/O

19 MEMDA[5] I/O

24 MEMDA[4] I/O

27 MEMDA[3] I/O

33 MEMDA[2] I/O

37 MEMDA[1] I/O

42 MEMDA[0] I/O

Barramento de dados bidirecional PNVM/SRAM

20 MEMAD[20] O Durante RESET: Entrada (p.u.)

MEMCS[2]# O Depois RESET: Entrada (r.t.)

GPCI/O[9] I/O

MEMAD[20]: Barramento de endereço PNVM/SRAM.

MEMCS[2]#: Seleção de chip PNVM/SRAM.

GPCI/O[9]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

28 MEMAD[19] O Durante RESET: Entrada (p.u.)

PLLSEL I Depois RESET: Saída (Alto)

MEMAD[19]: Barramento de endereço PNVM/SRAM.

PLLSEL: Seleção de frequência do PLL - 108MHz (baixo) ou 135MHz (alto), amostrado durante o RESET.

18 Manual de Serviço

Page 20

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Interface da PNVM/SRAM (41 pinos) - Continuação

31 MEMAD[18] O Durante RESET: Saída (baixo)

34 MEMAD[17] O Depois RESET: Saída (baixo)

5 MEMAD[16] O

4 MEMAD[15] O

6 MEMAD[14] O

Barramento de endereço PNVM/SRAM.

7 MEMAD[13] O Durante RESET: Entrada (p.d.)

AFETESTEN I Depois RESET: Saída (baixo)

MEMAD[13]: Barramento de endereço PNVM/SRAM.

AFETESTEN: Entrada de habilitação do modo de teste do front-end analógico. Nível amostrado durante o

RESET. Em operação normal, este pino deve estar em nível baixo durante o RESET.

8 MEMAD[12] O Durante RESET: Entrada (p.d.)

PLLCFGA I Depois RESET: Saída (baixo)

MEMAD[12]: Barramento de endereço PNVM/SRAM.

PLLCFGA: Entrada de configuração do PLL de áudio. Nível amostrado durante o RESET. Em operação

normal, este pino deve estar em nível baixo durante o RESET.

10 MEMAD[11] O Durante RESET: Entrada (p.d.)

PLLCFGP I Depois RESET: Saída (baixo)

MEMAD[11]: Barramento de endereço PNVM/SRAM.

PLLCFGP: Entrada de configuração do PLL de processo. Nível amostrado durante o RESET. Em operação

normal, este pino deve estar em nível baixo durante o RESET.

13 MEMAD[10] O Durante RESET: Entrada (p.d.)

TESTMODE I Depois RESET: Saída (baixo)

MEMAD[10]: Barramento de endereço PNVM/SRAM.

TESTMODE: Seleção de modo operacional. Nível amostrado durante o RESET. Em operação normal, este

pino deve estar em nível baixo durante o RESET.

15 MEMAD[9] O Durante RESET: Saída (baixo)

17 MEMAD[8] O Durante RESET: Saída (baixo)

36 MEMAD[7] O

38 MEMAD[6] O

40 MEMAD[5] O

43 MEMAD[4] O

45 MEMAD[3] O

46 MEMAD[2] O

Barramento de endereço PNVM/SRAM.

48 MEMAD[1] O Durante RESET: Entrada (p.d.)

BOOTSEL[2] I Durante RESET: Saída (baixo)

MEMAD[1]: Barramento de endereço PNVM/SRAM.

BOOTSEL[2]: Seleção de fonte de execução e software de boot da CPU. Veja BOOTSEL[1] abaixo.

49 MEMAD[0] O Durante RESET: Entrada (p.d.)

BOOTSEL[1] I Durante RESET: Saída (baixo)

MEMAD[0]: Barramento de endereço PNVM/SRAM.

BOOTSEL[1]: Seleção de fonte de execução e software de boot da CPU.

BOOTSEL[2:1]: Teste de produção

BOOTSEL[2:1]: Flash + SRAM (para debug/monitoramento)

BOOTSEL[2:1]: Debug da primeira UART

BOOTSEL[2:1]: Flash

23 MEMWR# O Durante RESET: Saída (Alto)

Durante RESET: Saída (Alto)

Habilitação de escrita da PNVM/SRAM.

44 MEMRD# O Durante RESET: Saída (Alto)

Durante RESET: Saída (Alto)

Habilitação de leitura da PNVM/SRAM.

Manual de Serviço 19

Page 21

Descrição dos pinos do Vaddis 6E (continuação)

Pino Nome Direção Estado durante/depois do RESET

Interface da PNVM/SRAM (41 pinos) - Continuação

47 MEMCS[0]# O Durante RESET: Saída (Alto)

Depois RESET: Saída (Alto)

Seleção de chip da PNVM/SRAM.

2 MEMCS[1]# O Durante RESET: Entrada (p.u.)

GPCI/O[18] I/O Depois RESET: Entrada (r.t.)

MEMCS[1]#: Seleção de chip da PNVM/SRAM.

GPCI/O[18]: Saída/Entrada de uso geral, monitorada/controlada pela CPU ou SW DSP.

Sinais de alimentação (56 pinos)

* GNDP (*pinos 12, 32, 50, 62, 72, 83, 91, 101,

107, 125, 151, 202)

Terra dos periféricos digitais da fonte de 3,3V (12 pinos)

* VDDP (* pinos 3, 21, 41, 52, 58, 68, 76, 87,

97, 105, 127, 144, 204)

Alimentação dos periféricos digitais de 3,3V (13 pinos)

* VDDIP (*pinos 51,154)

Tensão de referência de 3,3V dos periféricos (2 pinos)

117 GNDPA2

Terra digital da alimentação filtrada de 3,3V para AMCLK

119 VDDPA2

Alimentação digital filtrada de 3,3V para AMCLK

79 GNDPCLK

Terra digital da alimentação filtrada de 3,3V para PCLK

81 VDDPCLK

Alimentação digital filtrada de 3,3V para PCLK

* GNDC (*pinos 29, 66, 95, 121, 190)

Terra da alimentação de 1,8V para o núcleo digital (5 pinos)

* VDDC (*pinos 25, 64, 93, 123, 192)

Alimentação de 1,8V para o núcleo digital (5 pinos)

138 GNDA

Plano terra do circuito PLL interno

140 VDDA

Alimentação de 1,8V para o circuito PLL interno.

160 VDDDAC

Alimentação analógica de 3,3V para os DACs

164 GNDDACP

157 GNDDACD

Terra para a alimentação analógica de 3,3V dos DACs

165 GNDDABS2

Terra comum para os DACs de servo e vídeo.

166 GNDDACPS

170 GNDDACDS

Terra para a alimentação analógica de 3,3V do DAC do SERVO.

174 GNDAFERF

Terra da alimentação analógica de 3,3V do RF

171 VDDAFERF

Alimentação analógica de 3,3V do RF

186 GNDAFES

Terra analógico da alimentação de 3,3V do SERVO

175 VDDAFES

Alimentação analógica de 3,3V do SERVO

168 VDDDACS

Alimentação de 3,3V do DAC do SERVO

195 GNDPWMS

Terra da alimentação de 3,3V do PWM do SERVO

197 VDDPWMS

Alimentação de 3,3V do PWM do SERVO

20 Manual de Serviço

Page 22

CI M24C02 - WMN6T (MEM. EEPROM)

1. NM24C02 - EEPROM de 2 kbits de Interface

Serial de padrão 2-fios

Descrição geral

Os dispositivos NM24C02/03 são memórias CMOS de

2048 bits não voláteis de apagamento elétrico.

Esses dispositivos atendem a todas as especificações

do padrão de protocolo “Standard IIC 2-Wire” e são

projetados para minimizar o número de pinos e

simplificar os requisitos de layout da placa.

A metade superior (acima de 1Kbit) da memória do

NM24C03 pode ser protegida contra gravação

conectando-se o pino WP ao Vcc. Essa seção da memória

torna-se então inalterável a menos que o pino WP seja

ligado ao Vss.

Esse protocolo de comunicação usa as linhas CLOCK

(SCL) e DATA I/O (SDA) para transferir dados de modo

síncrono (entre o dispositivo mestre (por exemplo um

microprocessador) e o dispositivo EEPROM escravo.

O protocolo Standard IIC permite um máximo de 16K

de memória EEPROM que é suportada pela família

Fairchild em dispositivos de 2K,4K,8K e 16K, permitindo

ao usuário configurar a memória conforme a aplicação

requer com qualquer combinação de EEPROMs. Para

implementar densidades de memória EEPROM mais altas

no barramento IIC, o protocolo Extended IIC deve ser

usado. (Veja os datasheets do NM24C32 ou NM24C65

para mais informação.)

As EEPROMs Fairchild são projetadas e testadas para

aplicações que requerem alta durabilidade, alta

confiabilidade e baixo consumo de energia.

Características

• Larga faixa de tensão de operação 2.7V - 5.5V

• Freqüência de clock (F) de 400 KHz em 2.7V - 5.5V

• Corrente de ativo típica de 200µA

Corrente de standby típica de 10µA

Corrente de standby típica(L) de 1µA

Corrente de standby típica(LZ) de 0,1µA

• Interface compatível com IIC

– Provê protocolo de transferência de dados

bidirecional Entradas “Schmitt trigger”

• Modo de escrita em página de dezesseis bytes

– Minimiza o tempo total de escrita por byte.

• Ciclo de escrita auto-temporizado

Típico tempo do ciclo de escrita de 6ms

• Proteção de escrita por Hardware para a metade

superior (somente NM24C03)

• Durabilidade: 1,000,000 de mudanças de dados

• Retenção de dados maior que 40 anos.

• Encapsulamentos disponíveis: 8 pinos DIP, 8 pinos

SO, e 8 pinos TSSOP

• Disponível em três faixas de temperatura

- Comercial: 0° a +70°C

- Estendida (E): -40° a +85°C

- Automotiva (V): -40° a +125°C

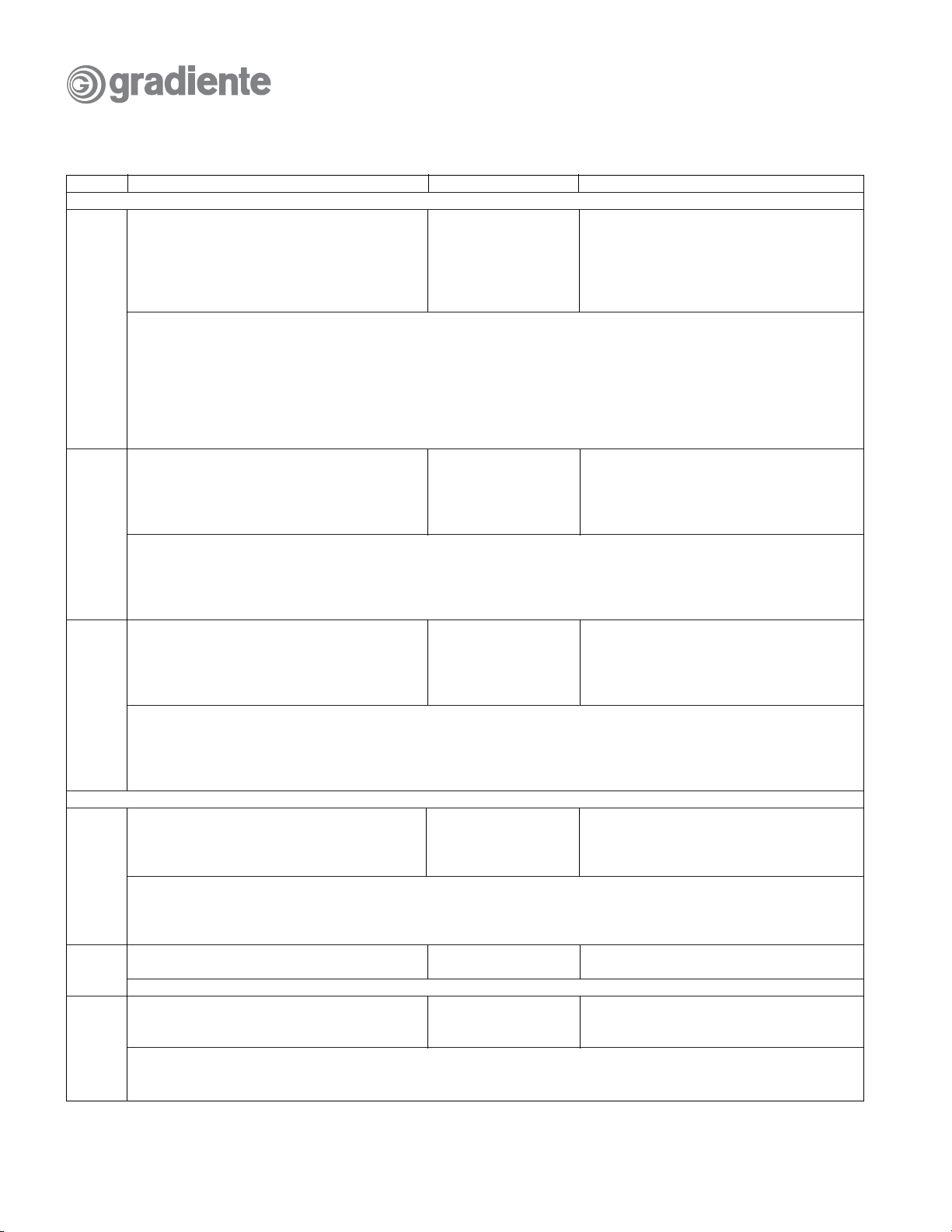

Diagrama de Blocos

Manual de Serviço 21

Page 23

Diagrama de Conexão

Encapsulamento Dual - in - line (N), Encapsulamento SO (M8) e Esncapsulamento TSSOP (MT8)

Nome dos pinos

Informações para pedido

Especificações do produto

Valores máximos absolutos

Temperatura ambiente de armazenamento -65°C a +150°C

Todas as tensões de entrada ou saída

em relação ao terra 6.5V a -0.3V

Temperatura do terminal

(Soldagem, 10 segundos) +300°C

Resistência a ESD 2000V min.

22 Manual de Serviço

Condições de operação

Temperatura ambiente de operação

NM24C02/03 0°C a +70°C

NM24C02E/03E -40°C a +85°C

NM24C02V/03V -40°C a +125°C

Alimentação positiva

NM24C02/03 4.5V a 5.5V

NM24C02L/03L 2.7V a 5.5V

NM24C02LZ/03LZ 2.7V a 5.5V

Page 24

Condições de teste AC

Nível dos pulsos de entrada VCC X 0.1 to VCC x 0.9

Tempos de subida e descida da entrada 10 ns

Níveis de temporização de entrada e saída Vcc x 0.3 to VCC x 0.7

Carga de saída 1 TTL Gate and CL = 100 pF

Formas de onda de entrada/saída em teste AC

Símbolo

f

SCL

T

I

t

AA

t

BUF

t

HD:STA

t

LOW

t

HIGH

t

SU:STA

t

HD:DAT

t

SU:DAT

t

R

t

F

t

SU:STO

t

DH

t

WR

(Note 3)

Parâmetro

Frequência de clock SCL

Constante de tempo de supressão de

ruído em SCL, Entradas SDA (mínima

largura de pulso vin).

SCL baixo para saída de dados SDA válida

Tempo que o barramento deve ficar

livre antes que uma nova transmissão

possa começar.

Tempo de espera da condição de início

Período do clock baixo

Período do clock alto

Tempo de Setup da condição de início.

(Para uma condição de inicio repetida).

Tempo de espera de entrada de dados

Tempo de setup da entrada de dados

Tempo de subida SDA e SCL

Tempo de descida SDA e SCL

Tempo de setup da condição de parado

Tempo de espera de saída de dados

Tempo do ciclo de escrita - NM24C02/03

- NM24C02/03L, NM24C02/03LZ

100 KHz 400 KHz

Min

Max

Min

100

100

0.3

4.7

4.0

4.7

4.0

4.7

20

250

3.5

0.1

1.3

0.6

1.5

0.6

0.6

20

100

1

300

4.7

300

0.6

50

10

15

Max

400

50

0.9

0.3

300

10

15

Unidades

KHz

ns

µs

µs

µs

µs

µs

µs

ns

ns

µs

ns

µs

ns

ms

Nota 3: o tempo do ciclo de escrita (twr) é o tempo de uma condição de parado válida de uma sequência de escrita até o fim do ciclo interno de

programação/apagamento. Durante esse ciclo de escrita, os circuitos de interface do NM 24C02 / 03 são desabilitados e o SDA é permitido

se manter alto pelo resistor de pull-up do barramento, e o dispositivo não responde ao endereço escravo. Veja o diagrama “Temporização

do ciclo de escrita”.

Tempo de barramento

Manual de Serviço 23

Page 25

24 Manual de Serviço

Page 26

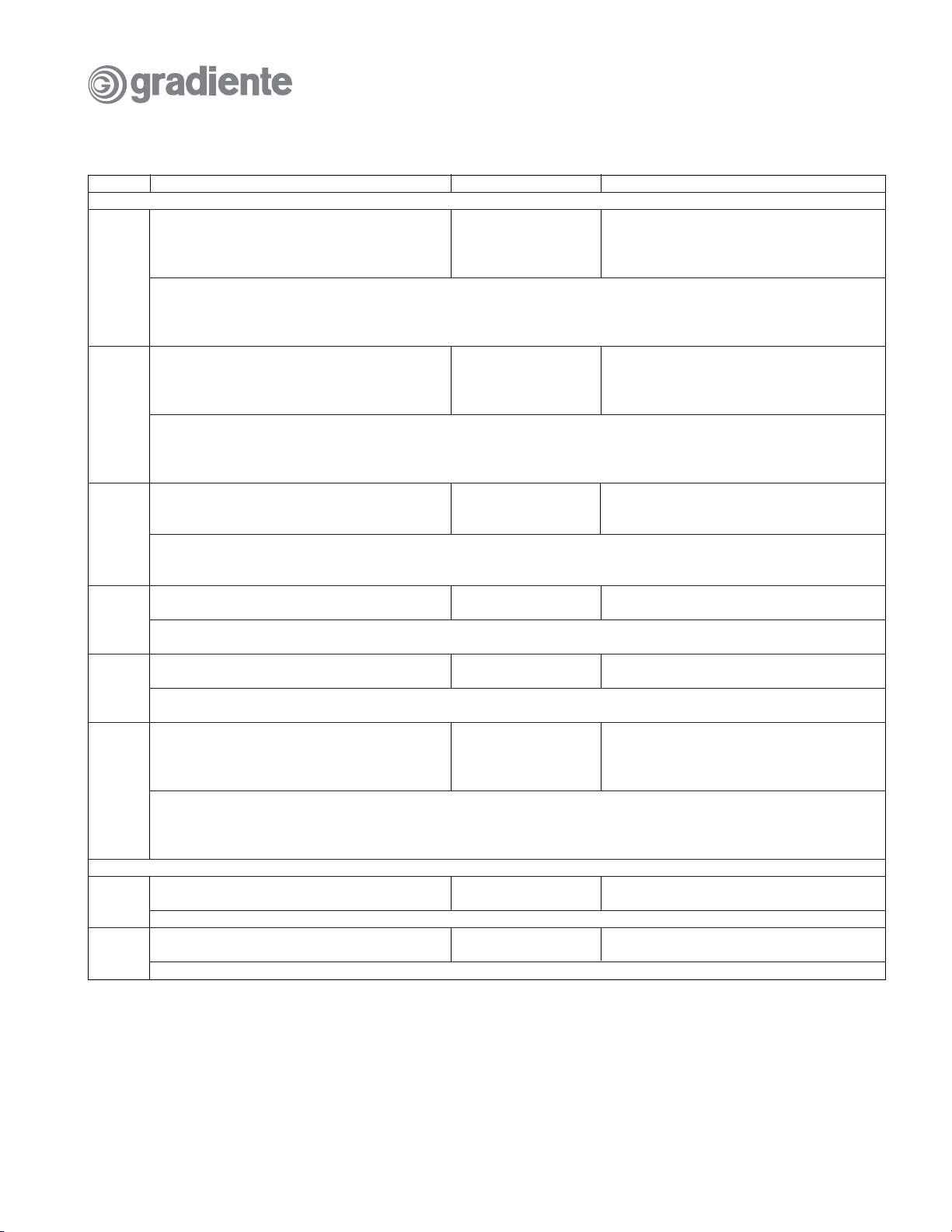

CI REGULADOR RC1117M33T DE TENSÃO 3V3

CI REGULADOR RC1117ST DE TENSÃO AJUSTÁVEL

Características

- Baixa corrente de queda

- Regulagem de carga: tipicamente 0,05%

- Limite de corrente ajustado

- Limitação térmica no chip

- Encapsulamento padrões SOT-223, TO-263 e TO-252

- Tensão Ajustável pelo terceiro terminal ou fixa em

2.5V, 2.85V, 3.3V ou 5V

Aplicações

- Terminações SCSI ativas

- Reguladores lineares de alta eficiência

- Pós-reguladores para fontes chaveadas

- Carregadores de bateria

- Reguladores lineares de 5V a 3,3V

- Fontes de clock para placa-mãe

Descrição

Os RC1117 e RC1117-2.5, -2.85, -3.3 e -5 são

reguladores de três terminais de baixa queda com

capacidade de corrente de saída de 1A. Esses

dispositivos foram otimizados para baixas tensões onde

a resposta a transientes e tensão de entrada mínima

são críticas.

A versão de 2,85V foi projetada especificamente para

ser usada em Terminações Ativas para barramento SCSI.

A limitação de corrente é ajustada para garantir a

corrente de saída especificada e corrente de curto

circuito controlada. A limitação térmica no chip fornece

uma proteção contra qualquer combinação de

sobrecarga e temperatura ambiente que poderia criar

uma temperatura de junção excessiva.

Ao contrário de reguladores tipo PNP onde até 10% da

corrente de entrada é perdida como corrente de repouso,

a corrente de repouso do RC1117 flue pela carga,

aumentando a eficiência.

A série de reguladores RC1117 está disponível nos

padrões de encapsulamento de potência SOT-223, TO263 (D2PAK) e TO-252 (DPAK).

Aplicações típicas

Manual de Serviço 25

Page 27

Designação dos Pinos

26 Manual de Serviço

Page 28

Características elétricas

Condições de operação: V

IN ≤=7V, TJ=25°C, exceto se mencionado o contrário.

O sinal esférico denota especificações que se aplicam na faixa de temperatura especificada.

Notas:

1. Vejas as especificações de regulagem térmicas para mudanças na tensão de saída devido a efeitos térmicos. A

regulagem de linha e carga são medidas em uma temperatura de junção constante devido à baixa duração do

pulso de teste.

2. A regulagem de linha e carga são garantidas até a dissipação máxima de potência. A dissipação de potência é

determinada pela diferença de tensão entre entrada e saída e a corrente de saída. A potência de saída máxima

garantida não está disponível em toda a faixa de tensões de entrada/saída.

3. Somente RC1117.

Manual de Serviço 27

Page 29

ESQUEMA ELÉTRICO MPEG MEMÓRIA SDRAM- D470

28 Manual de Serviço

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Page 30

ESQUEMA ELÉTRICO MPEG PCI PRINCIPAL - D470

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Manual de Serviço 29

Page 31

ESQUEMA ELÉTRICO SAÍDA DE ÁUDIO - D470

30 Manual de Serviço

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Page 32

Usando memória FLASH INTEL:

R122=0 ohm, R121=NC

DIAGRAMA DO CIRCUITO MEMÓRIA MPEG - D470

Usando memória FLASH SST:

R121=0 ohm, R122=NC

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Manual de Serviço 31

Page 33

DIAGRAMA MPEG - D470ELÉTRICO SAÍDA VÍDEO

32 Manual de Serviço

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Page 34

DIAGRAMA PAINEL FRONTAL - D470

U3

REMO

123

U1

F11

F12

NC

P16

P15

P14

P13

P12

P11

P10

NC

NC

NC

NC

NC

1G

2G

3G

4G

5G

NP

F21

F22

P9

P8

P7

P6

P5

P4

P3

P2

P1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

3.5V~1

3.5V~1

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

GRID5

GRID4

GRID3

GRID2

GRID1

3.5V~2

3.5V~2

SEG9

SEG10

SEG11

SEG12

-25V

SEG13

SEG14

SEG15

SEG16

GRID5

23

24

25

26

27

28

29

30

31

32

33

S9

S10

S11

S12/G1

VEE

S13/G1

S14/G9

S15/G8

S16/G7

G6

G5

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

+5V

12

13

22

14

S115S216S317S418S519S620S721S8

VDD

KEY4

U2

UPD16312

G434G335G236G137VDD38LED439LED340LED241LED142VSS43OSC

44

GRID4

GRID3

GRID2

GRID1

+5V

KSO4

KSO3

KSO2

LED

GND

KEY3

KEY2

KEY1

STB

CLK

VSS

DIN

DO

SW4

SW3

SW2

SW1

R13

33K

R5 33K

R6 33K

11

R7 33K

R8 33K

10

9

8

GND

7

6

5

GND

4

GND

3

GND

2

GND

1

R1

10K

33K

R2

10K

R9

33K

R3

10K

R10

33K

C3

101

IR

R4

10K

+5V

KEY4

KEY3

KEY2

KEY1

C6

100U/16V

C7

104

3.5V~2

3.5V~1

-25V

GND

+5V

1

2

3

4

5

JP2

5PIN

R12

R11

33K

C4

101

VFDST

VFDCK

VFDAT

C5

101

VFDAT

VFDCK

VFDST

GND

IR

5

4

3

2

1

5PIN

JP1

C2

104

+5V

C1

100/10

+5V

R14

1k

VFD0503F

SEG1

SEG2

D1

1N4148

D2

1N4148

K1

K2

OP/CL

SW-1

2

play

SW-1

2

FF

SW-1

power

SW-1

D3

1

1

2

1

2

DIODE-LIGHT

LED

REV

SW-1

1

KEY1

1

2

KEY2

STOP

SW-1

2

1

KEY3

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Manual de Serviço 33

Page 35

D902

1N4007

D901

1N4007

C902

0.1/275Vac

LF901

R901

330K/1W

C907

104

D903

1N4007

D904

1N4007

C905

47u/400V

C908

47U/25V

U901

ICE2A0565

C910

1U/50V

Z901

18V

270K

270K

C911

103

R902

R903

7

8

VCC

GND

RES1FB2S3D

R907

2R

6

5

NC

4

R904

47K/1W

D

R908

2R

C906

103/1KV

D906

HER107

C912

471

D905

HER104

Q901

2N5551

R909 22R

R905

100R

ESQUEMA ELÉTRICO POWER SUPPLY - D470

L101

33uH

R906

20K

Z902

15V

TR901

5

4

2

1

C110

10U/100V

U902

PC817

D105

IN5822

8

7

6

9

11

12

10

R109

100R

1

2

R110 1k

D101

HER104

C121

103

R118

10R

D102

HER104

D103

2200u/10V

HER104

C111

R111

10K

L102

33uH

C104

100u/16V

C101

100u/35V

100u/16V

Z101

12V

C105

R101

910R

100u/16V

C108

330u/16V

C103

L105

10uH

D106

C102

100u/35V

1N4007

33uH

R115

4.7K

R102

10K

C109

100u/16V

C112

330/10

C120

104

C107

104

R107

200R

R104

470R

Z102

5V1

C113

104

R105

22k

D108

1N5392

D109

1N5392

C114

104

R108

100R

C115

100u/16V

+5V

GND

-25V

FIP1

FIP2

GND

-12

+12

GND

+5V

3V3

GND

CN903

5P2.0

5

4

3

2

1

CN904

7P2.5

7

6

5

4

3

2

1

C904

102/400~

C903

102/400~

34 Manual de Serviço

40mH BC20229

R900

1M 1/2W

1

2

CN901

3P4.0

C901

0.1/275Vac

1

CN902

3P4.0

F901

0.5A/250v

2

C909

102/400~

Q104

TL431

C117

3

1

104

2

R112

10k

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Page 36

DIAGRAMA MPEG - D470

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Manual de Serviço 35

Page 37

DIAGRAMA MPEG - D470

36 Manual de Serviço

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Page 38

DIAGRAMA MPEG - D470

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Manual de Serviço 37

Page 39

GUIA DE PLACA FONTE HY328 - D470

38 Manual de Serviço

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Page 40

VISTA EXPLODIDA DO CUBO - D470

3

PCI110

2

PCI328

MEC1

PCI651

CABO1

POS./ESQ.

1

2

3

4

5

6

7

MEC1

PCI110

PCI328

PCI651

CABO1

ITENS VISTA EXPLODIDA D-470

DESCRIÇÃO

PAINEL FRONTAL (D-470)

COMPLEMENTO MECANISMO

TAMPA SUPERIOR (D-470)

TAMPA TRASEIRA

CHASSIS

TECLA POWER

TECLA FUNÇÕES

MEC. COMPLETO

PCI PAINEL FRONTAL (D-470)

PCI FONTE

PCI PRINCIPAL

CABO FORÇA

CÓDIGO

953641001901D

958984001901D

953638001901D

953639001901D

95364001901D

953507001901D

953508001901D

958983001901D

959249001901D

958985001901D

959248001901D

953504001901D

6

1

4

5

7

Manual de Serviço 39

Page 41

DIAGRAMA MPEG - D470

40 Manual de Serviço

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Page 42

GUIA DE PLACA FONTE HY328 - D470

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Manual de Serviço 41

Page 43

GUIA DE PLACA FRONTAL - D470

42 Manual de Serviço

Revisão: A

Data: 01/06/05

Obs.: 1º versão do Esquema elétrico

enviado pelo fornecedor

Page 44

PROCEDIMENTOS DE MANUTENÇÃO

1. Fluxograma de manutenção da fonte de

alimentação

Problema na fonte

de alimentação

NÃO OK

Verifique a condição do F901

OK

Substitua F901

Verifique as

condições dos pinos

4/6/8 do U901

OK

Verifique a tensão de saída

em D101/D102/D103/D105

NÃO OK

Verifique o pino 1 do Q103.

(Tensão 2~5V).

NÃO OK

NÃO OK

Substitua U902

NÃO OK

Substitua U901

NÃO OK

Substitua Q103

Substitua Tr901

OK

Verifique a tensão de

saída em

CON901~904

OK

Manual de Serviço 43

Page 45

2. Fluxograma de manutenção de problema de

leitura do disco

ProblemaS de leitura do disco em um player de

DVD são complexos. Este problema não está

somente relacionado ao circuito eletrônico, mas

também ao ambiente de operação.

A unidade de carregamento do DVD é uma peça

complexa que contém um grande número de

componentes ESD, que exigem técnicas,

equipamentos e ferramentas específicas para

reparo. Em geral, não é recomendado que o técnico

de manutenção desmonte a unidade de

carregamento do DVD. É recomendado fazer o

diagnóstico e substituição da unidade de

carregamento inteira, ao invés de repará-la.

Antes de iniciar o diagnóstico de uma situação de

"NO Disc", verifique e exclua todas as possibilidades

abaixo:

O disco de teste está danificado.

A tensão da rede AC caiu abaixo do nível mínimo.

A região ou sistema de cores do disco DVD não

está de acordo com o player de DVD ou configuração

do sistema.

Umidade condensada dentro da unidade. (Ligue a

unidade, sem disco, por 1/2 a 2 horas)

Problema de leitura de

disco

Verifique o conector DVD

LOADER

OK

Substitua a unidade de

carregamento do DVD

NÃO OK

Verifique o circuito de interface

ATAPI MPEG

NÃO OK

Substitua o conector

Verifique as outras peças pelo

método de substituição

44 Manual de Serviço

Page 46

3. Fluxogramas de manutenção de problemas de

vídeo

Problemas de vídeo composto

NÃO OK

Verifique o item SETUP

OK

NÃO OK

Verifique o sinal de saída em

Y1

OK

NÃO OK

Verifique o sinal em C128

Veja o Manual do

Usuário

Substitua o Y1

Substitua C128/U1

OK

Verifique o sinal em C130

OK

Verifique o sinal no pino Cn8

NÃO OK

Substitua Cn8

NÃO OK

Substitua C130/L6

OK

Verifique a parte externa

Manual de Serviço 45

Page 47

4. Fluxograma de manutenção de problemas de

áudio analógico composto

Problema de áudio analógico composto

NÃO OK

Verifique o sinal R8

OK

Verifique o sinal no pino 1~3

do U11

OK

Verifique sinal de +5V no

pino 7 do U11.

Substitua U1

NÃO OK

Substitua U1

NÃO OK

Verifique a fonte de

alimentação

OK

Verifique o sinal nos pinos 5/8

do U11

OK

Verifique as peças Q15/Q16 do

Mudo

NÃO OK

Substitua U11

46 Manual de Serviço

Page 48

5. Fluxograma de manutenção do controle frontal

Problemas no controle

Verifique a conexão entre JP2 e a Alimentação

frontal

OK

Verifique a conexão entre JP1 e o MPEG

OK

Verifique a tensão nos pinos 14/27/38

OK

de U2

Verifique o sinal

SEG em U2

NÃO OK

Substitua

NÃO OK

NÃO OK

Veja 3.1

OK

Substitua VFD

Verifique o sinal de alimentação em U1

NÃO OK

Substitua U1

NÃO OK

OK

Substitua U2

Manual de Serviço 47

Page 49

6. Fluxograma de manutenção de problemas do

Controle Remoto

48 Manual de Serviço

Page 50

Gradiente e você www.gradienteservices.com.br

SAT (Serviço de Atendimento Técnico)

Setor de Treinamento Técnico

Suporte.tecnico@gradiente.com

Loading...

Loading...