Page 1

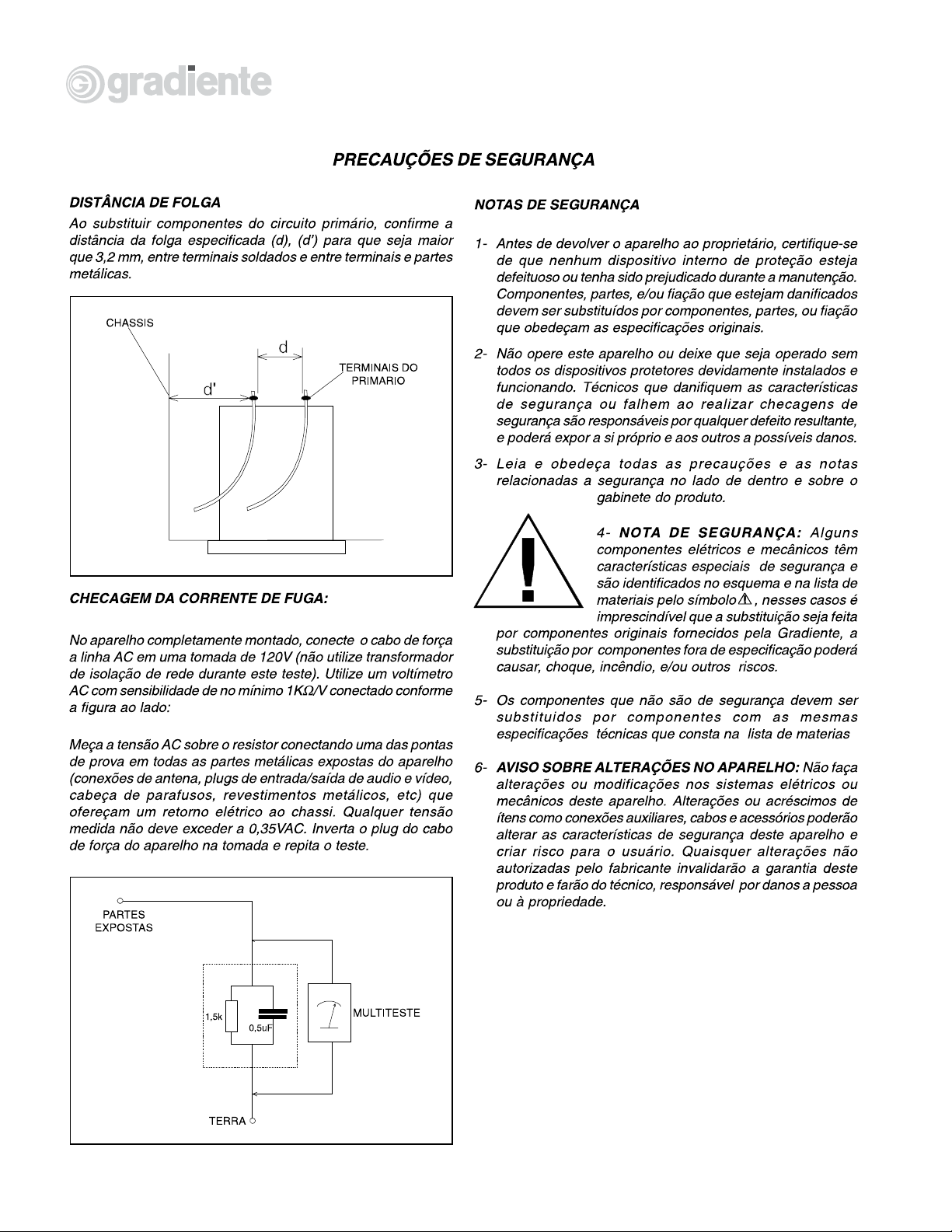

Page 2

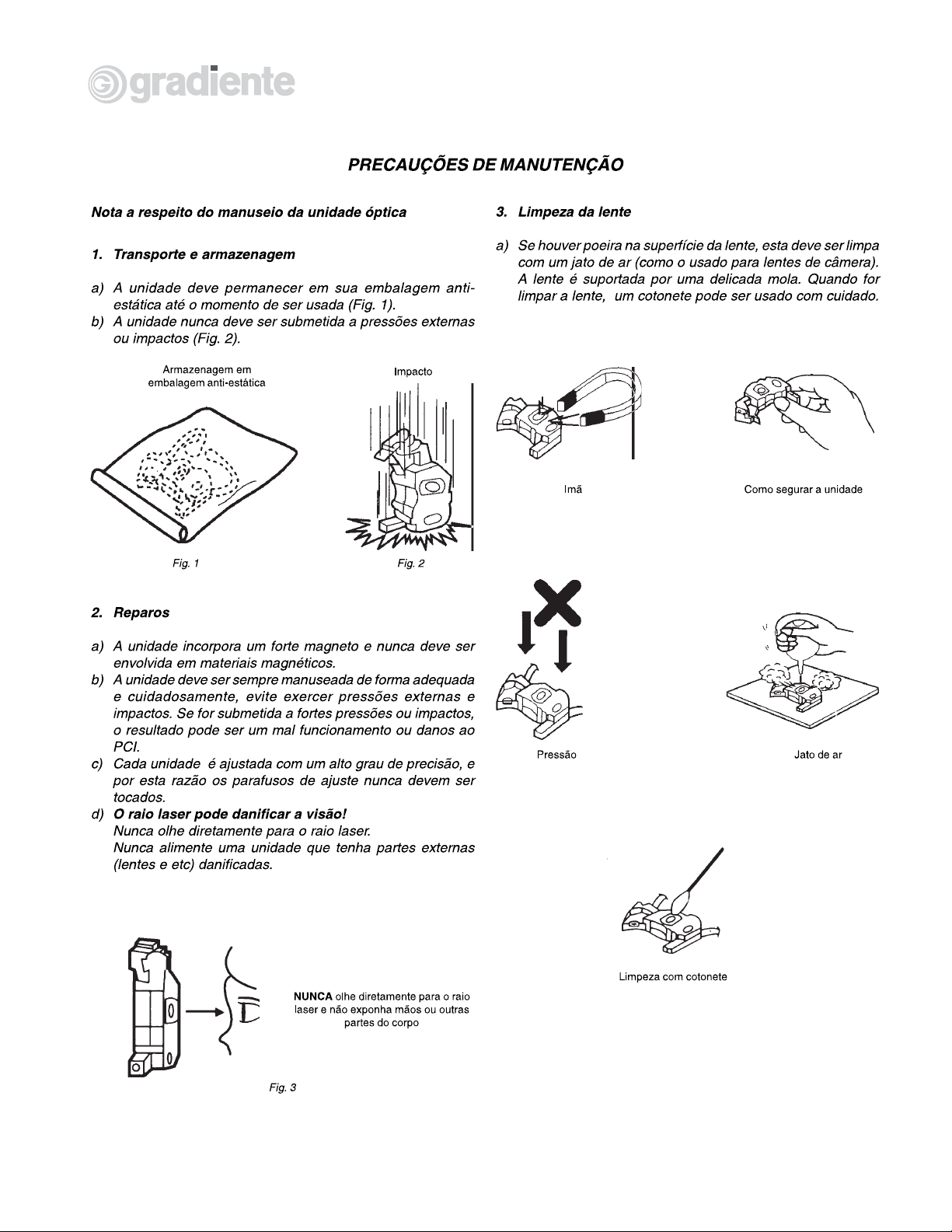

Page 3

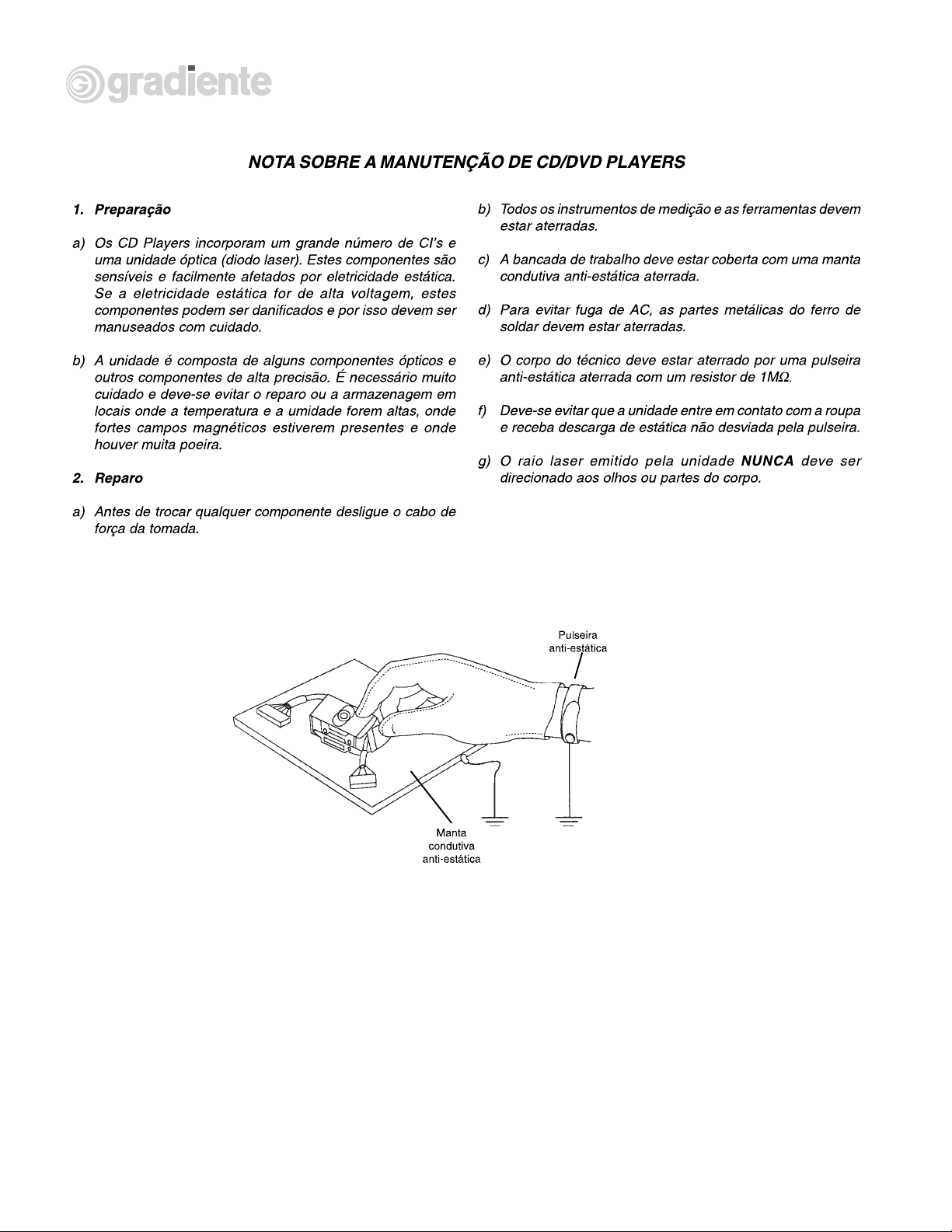

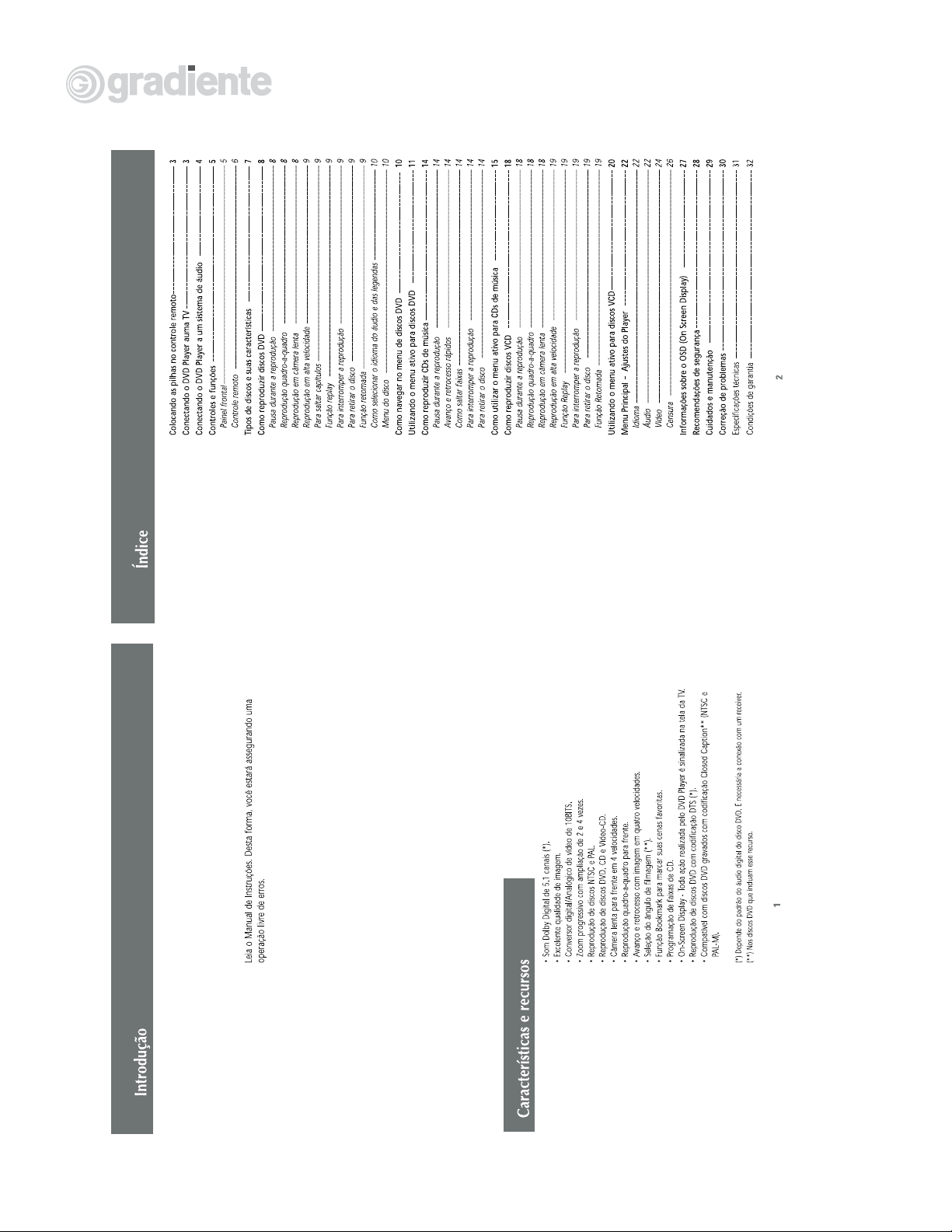

INTRODUÇÃO

O SAT através deste Manual de Serviço tem a finalidade de mostrar todas as etapas necessárias para a correta manutenção

dos produtos Gradiente.

Nossa maior preocupação é oferecer aos técnicos da rede de Serviços Autorizados Gradiente em todo território nacional, condições

de conhecer profundamente o DVD D-10/2 (Compact DVD) e assim capacitá-los a desenvolver um serviço de qualidade junto

aos nossos clientes.

Para isso, é indispensável uma leitura cuidadosa e atenta de todas as instruções contidas neste manual.

Divisão Nacional de Serviços

ÍNDICE

INTRODUÇÃO ................................................................................................................................................................................... 1

PRECAUÇÕES DE SEGURANÇA ................................................................................................................................................... 3

ESPECIFICAÇÕES TÉCNICAS ....................................................................................................................................................... 5

MANUAL DE INSTRUÇÕES ............................................................................................................................................................. 6

MONTAGEM E DESMONTAGEM DO CUBO ................................................................................................................................22

PROCEDIMENTOS: TESTE E VERIFICAÇÃO ELÉTRICA GERAL ............................................................................................. 30

MECANISMO: PROCEDIMENTOS PARA VERIFICAÇÃO E MANTENÇÃO (TVM 502H / TVM-502P *) .................................. 34

DESCRIÇÃO DOS PINOS DOS PRINCIPAIS CIRCUITOS INTEGRADOS ................................................................................35

DESCRIÇÃO DO TRANSISTOR DE POTÊNCIA 2SD88Q (T505) ............................................................................................... 84

ESQUEMAS ELÉTRICOS ............................................................................................................................................................... 85

GUIAS DE PLACAS ......................................................................................................................................................................... 89

VISTAS EXPLODIDAS .................................................................................................................................................................... 91

LISTA DE MATERIAIS ELÉTRICOS DVD D-10/2 (Compact DVD) ..............................................................................................92

Manual de Serviço 1

Page 4

2 Manual de Serviço

Page 5

Manual de Serviço 3

Page 6

4 Manual de Serviço

Page 7

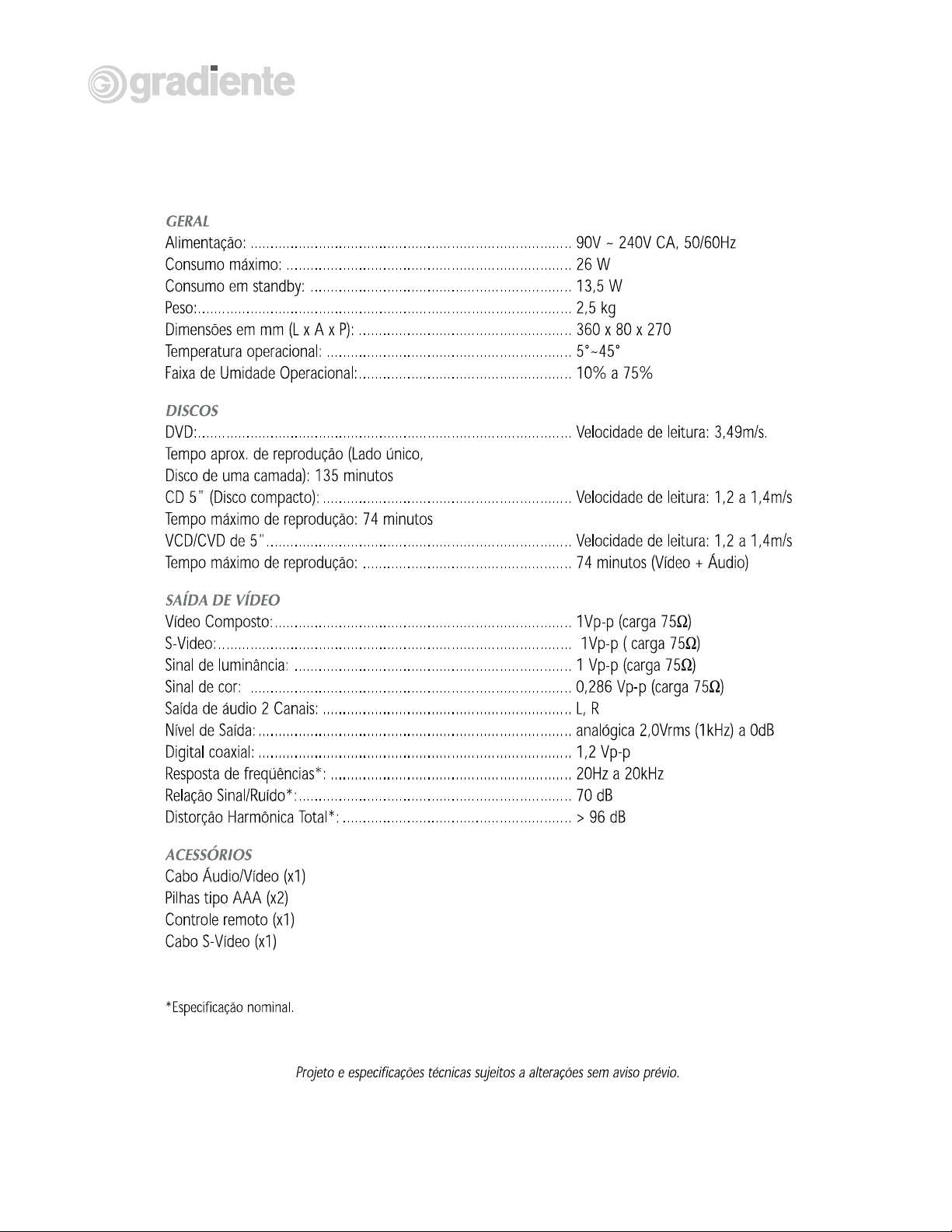

ESPECIFICAÇÕES TÉCNICAS

Manual de Serviço 5

Page 8

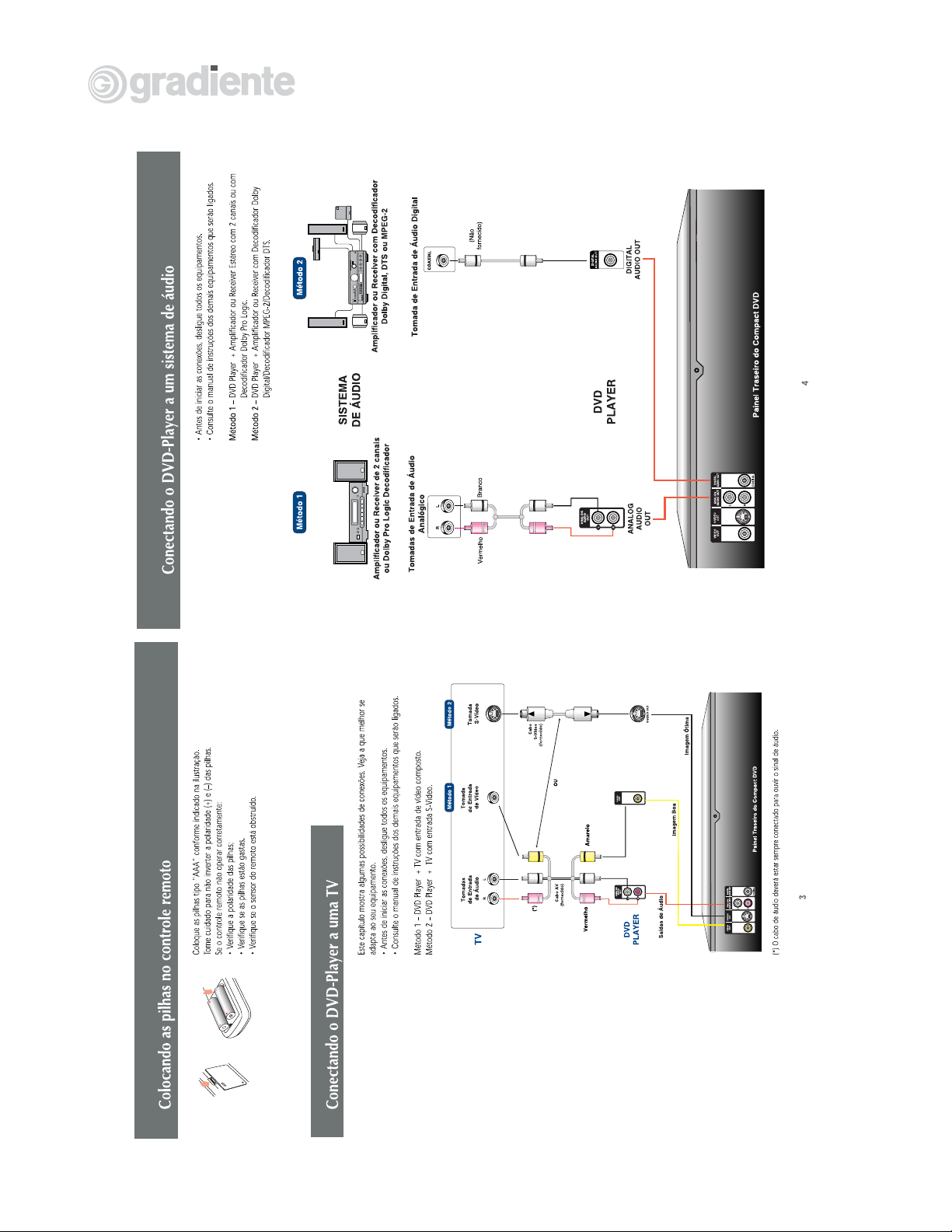

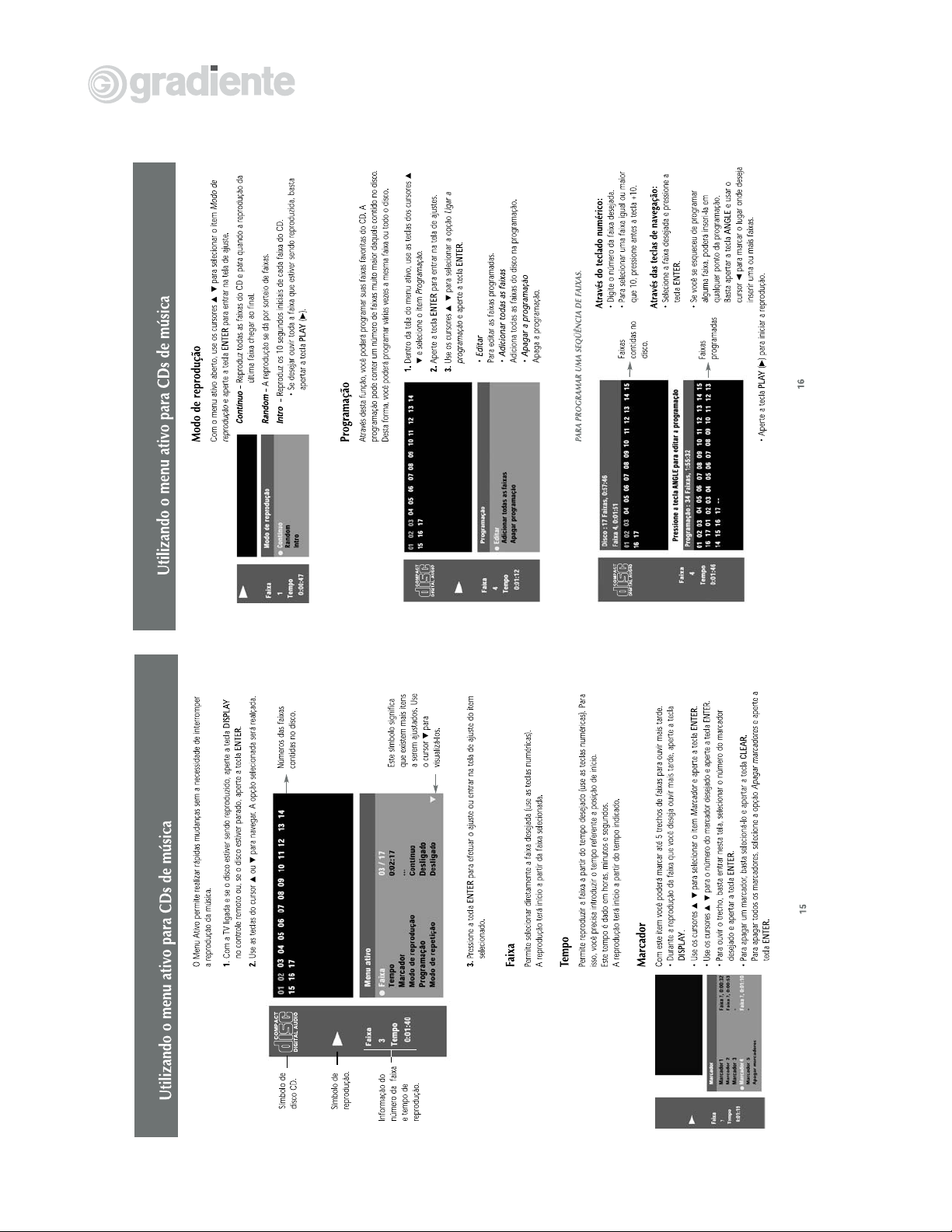

MANUAL DE INSTRUÇÕES

6 Manual de Serviço

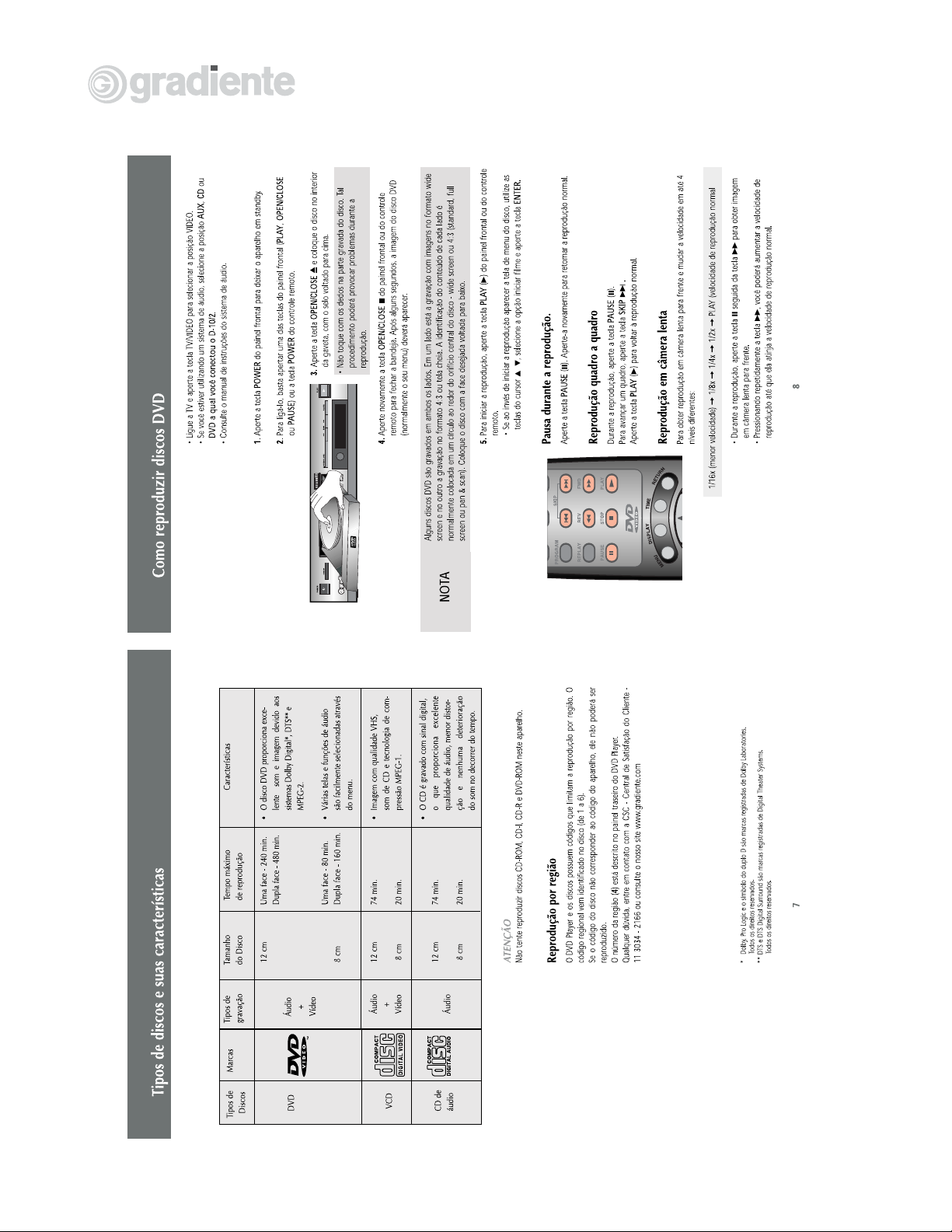

Page 9

Manual de Serviço 7

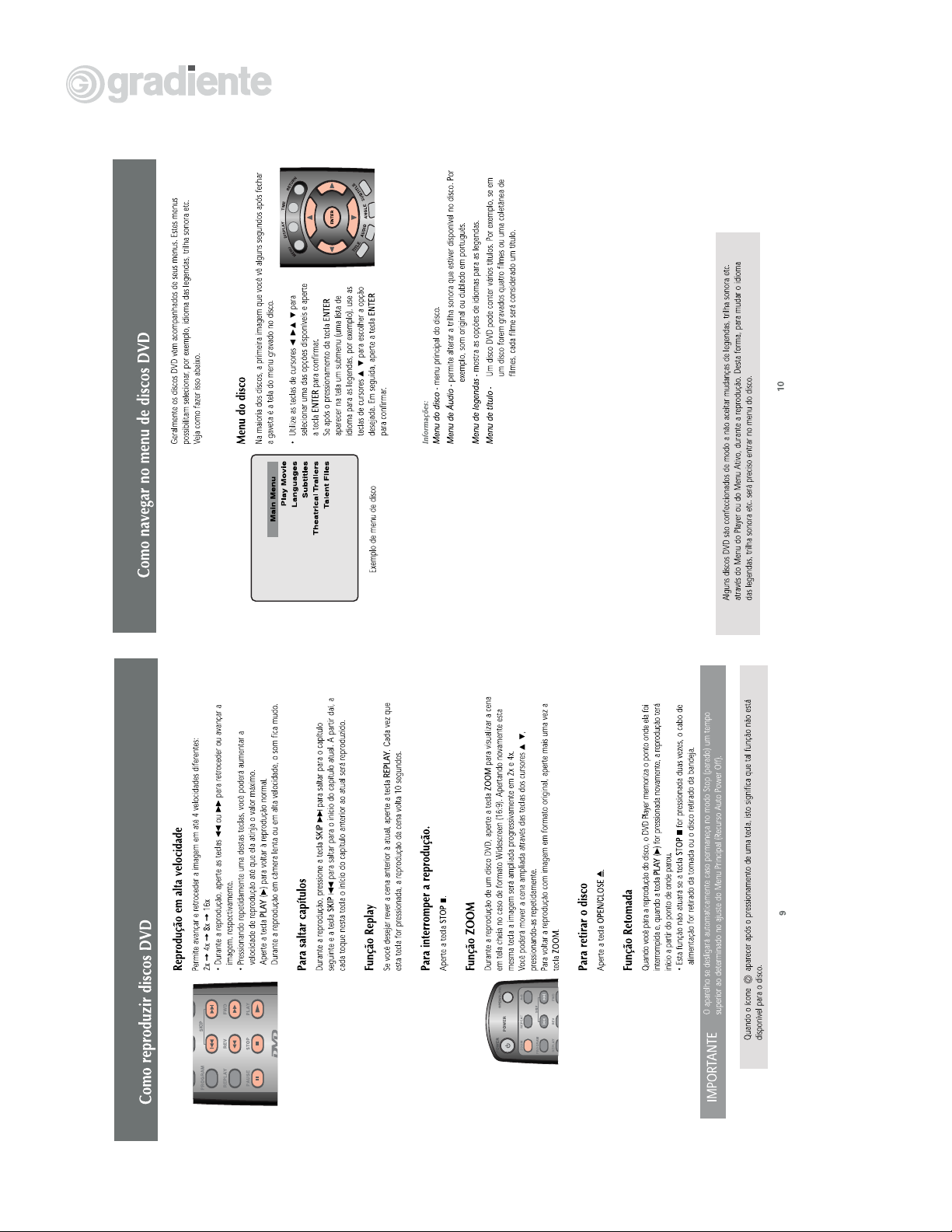

Page 10

8 Manual de Serviço

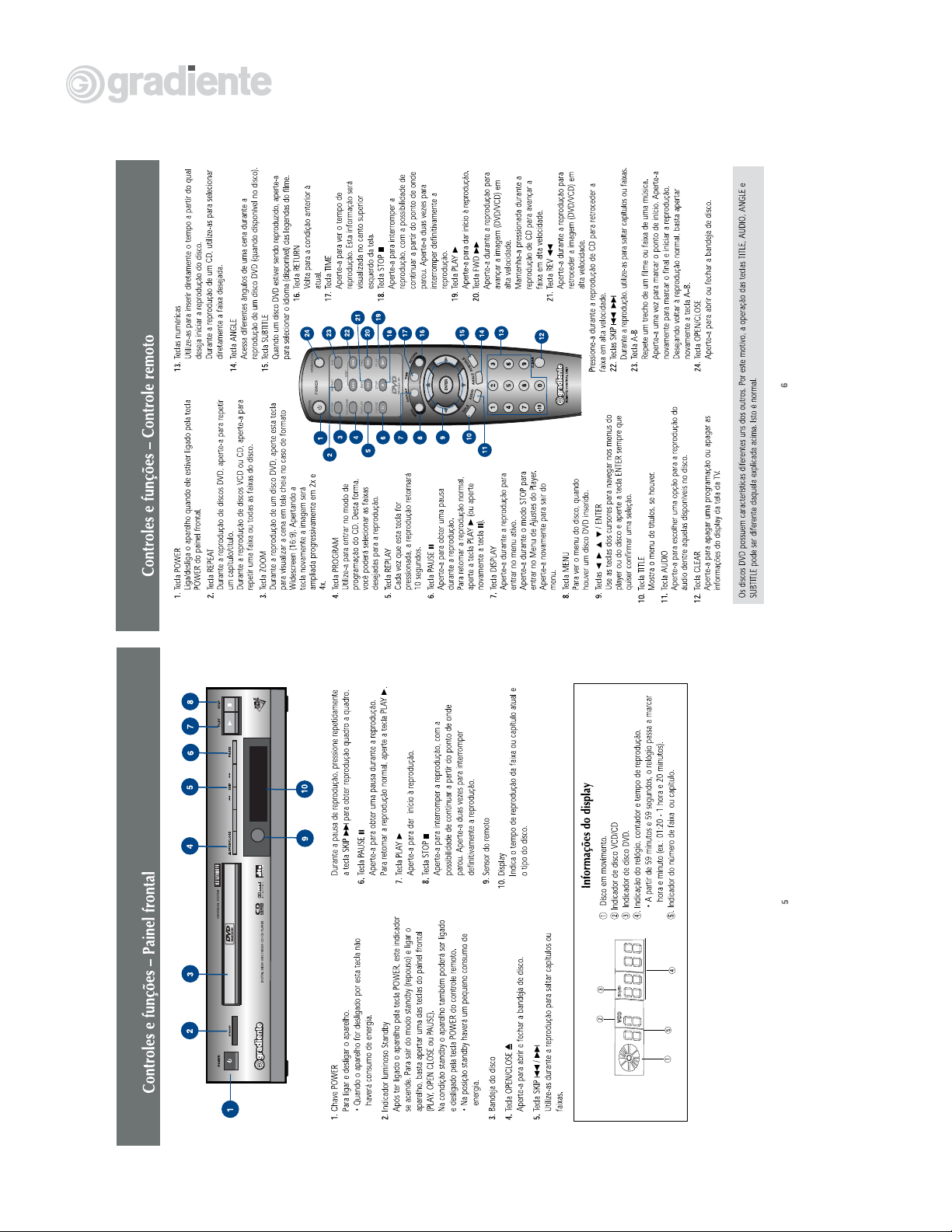

Page 11

Manual de Serviço 9

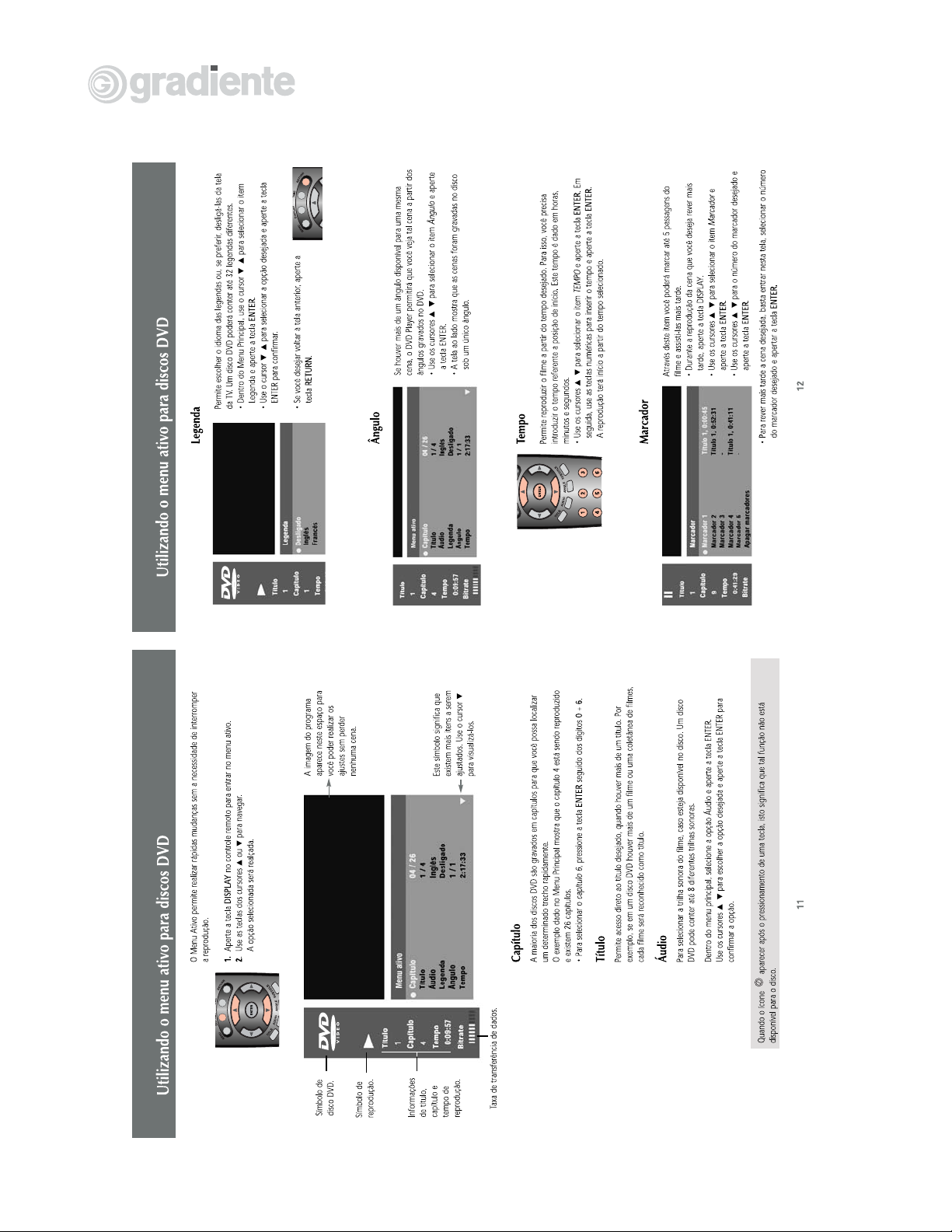

Page 12

10 Manual de Serviço

Page 13

Manual de Serviço 11

Page 14

12 Manual de Serviço

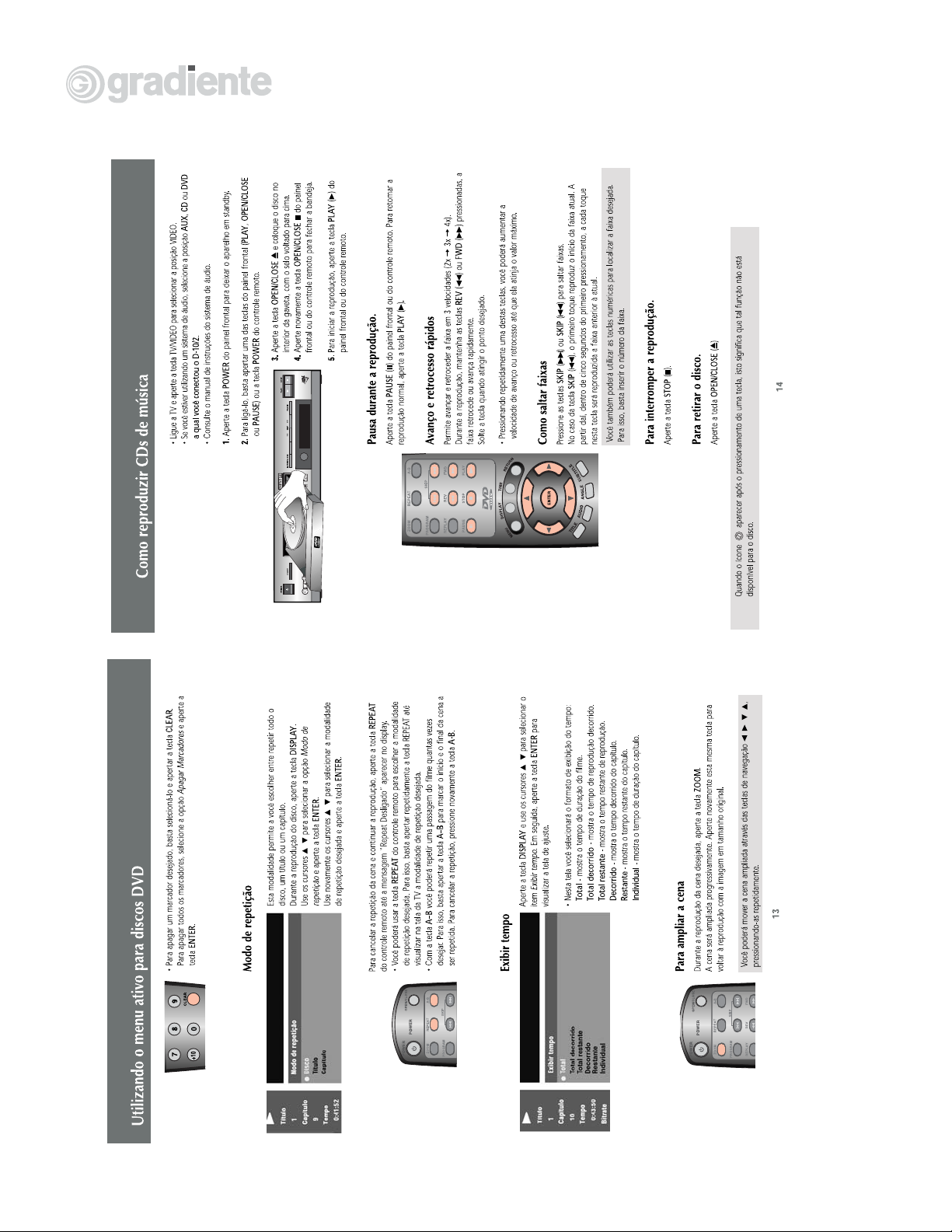

Page 15

Manual de Serviço 13

Page 16

14 Manual de Serviço

Page 17

Manual de Serviço 15

Page 18

16 Manual de Serviço

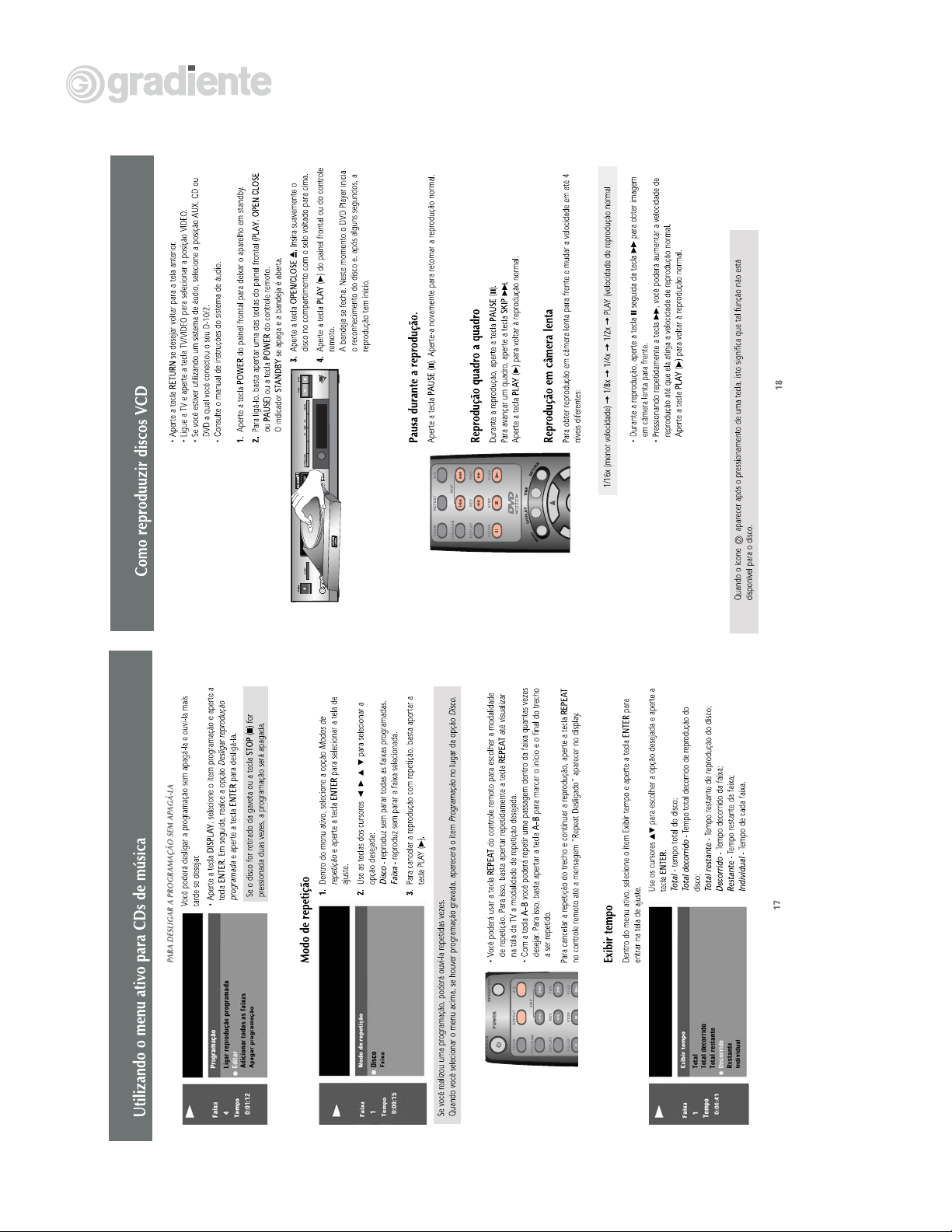

Page 19

Manual de Serviço 17

Page 20

18 Manual de Serviço

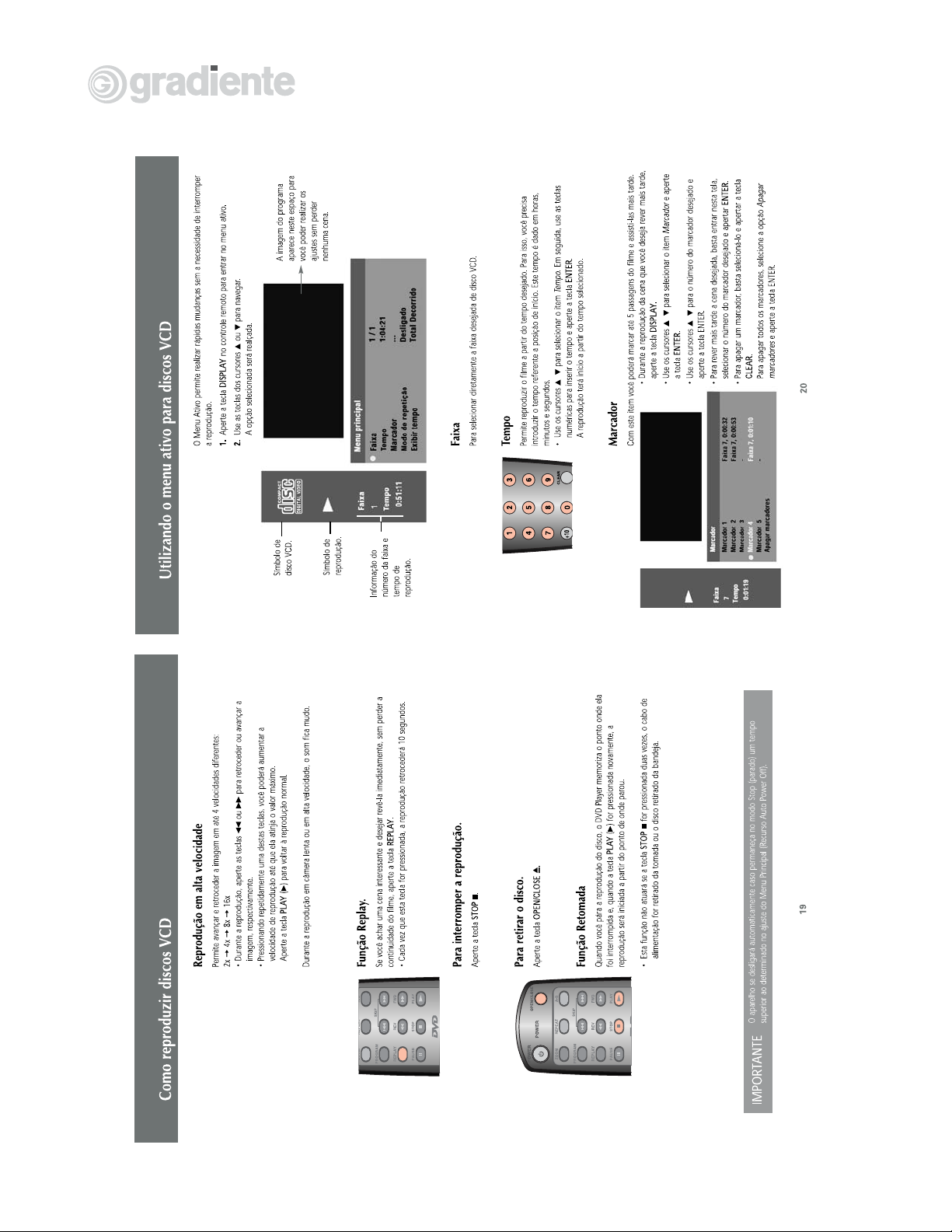

Page 21

Manual de Serviço 19

Page 22

20 Manual de Serviço

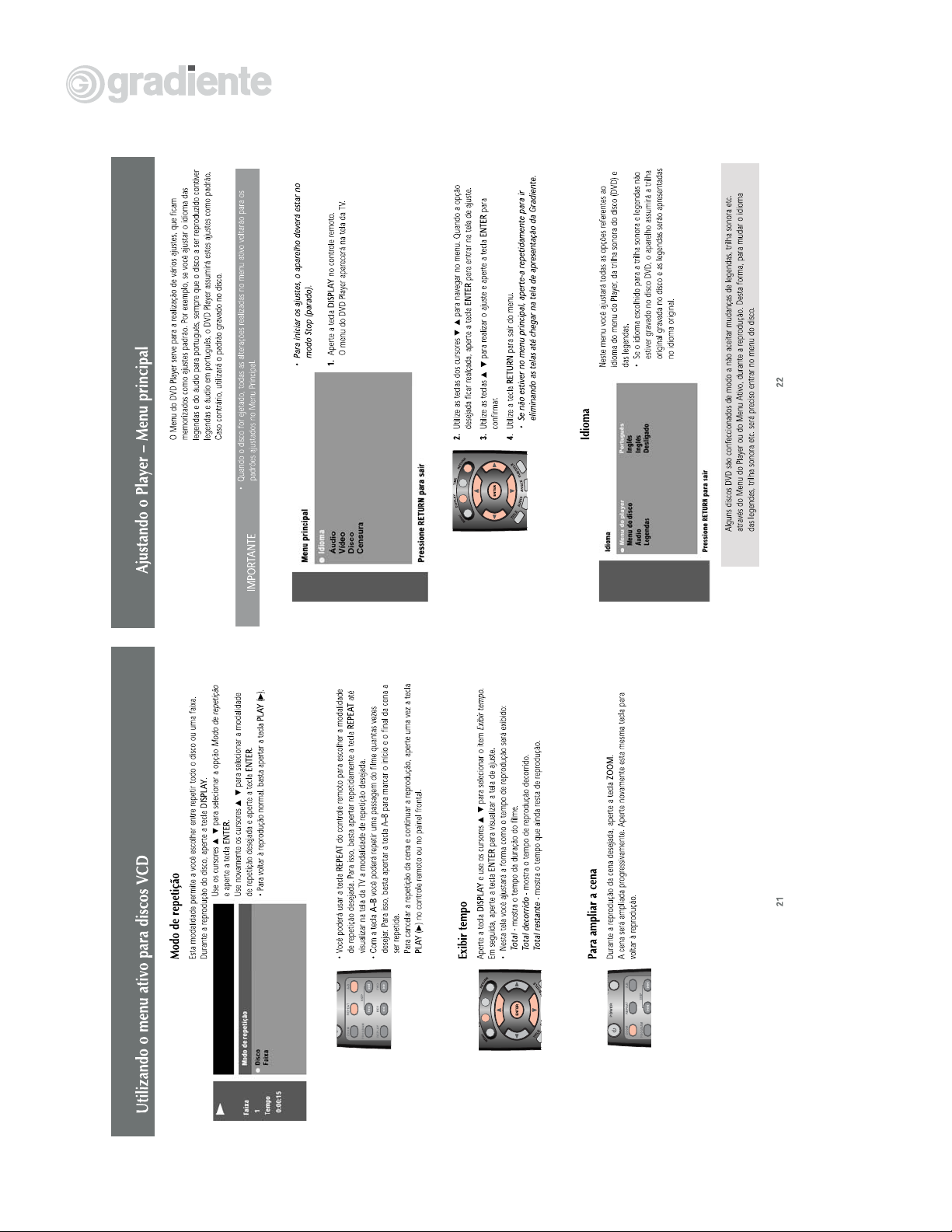

Page 23

Manual de Serviço 21

Page 24

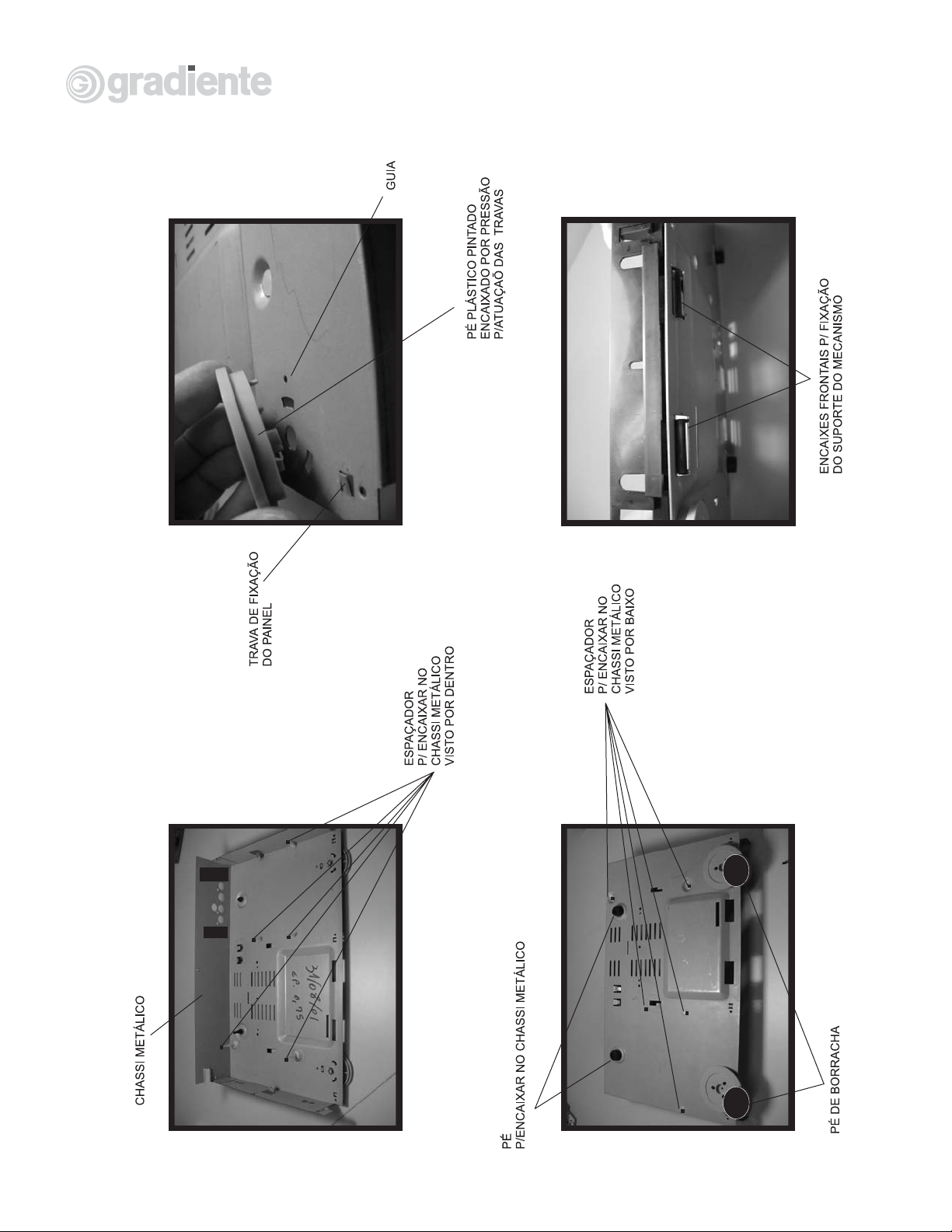

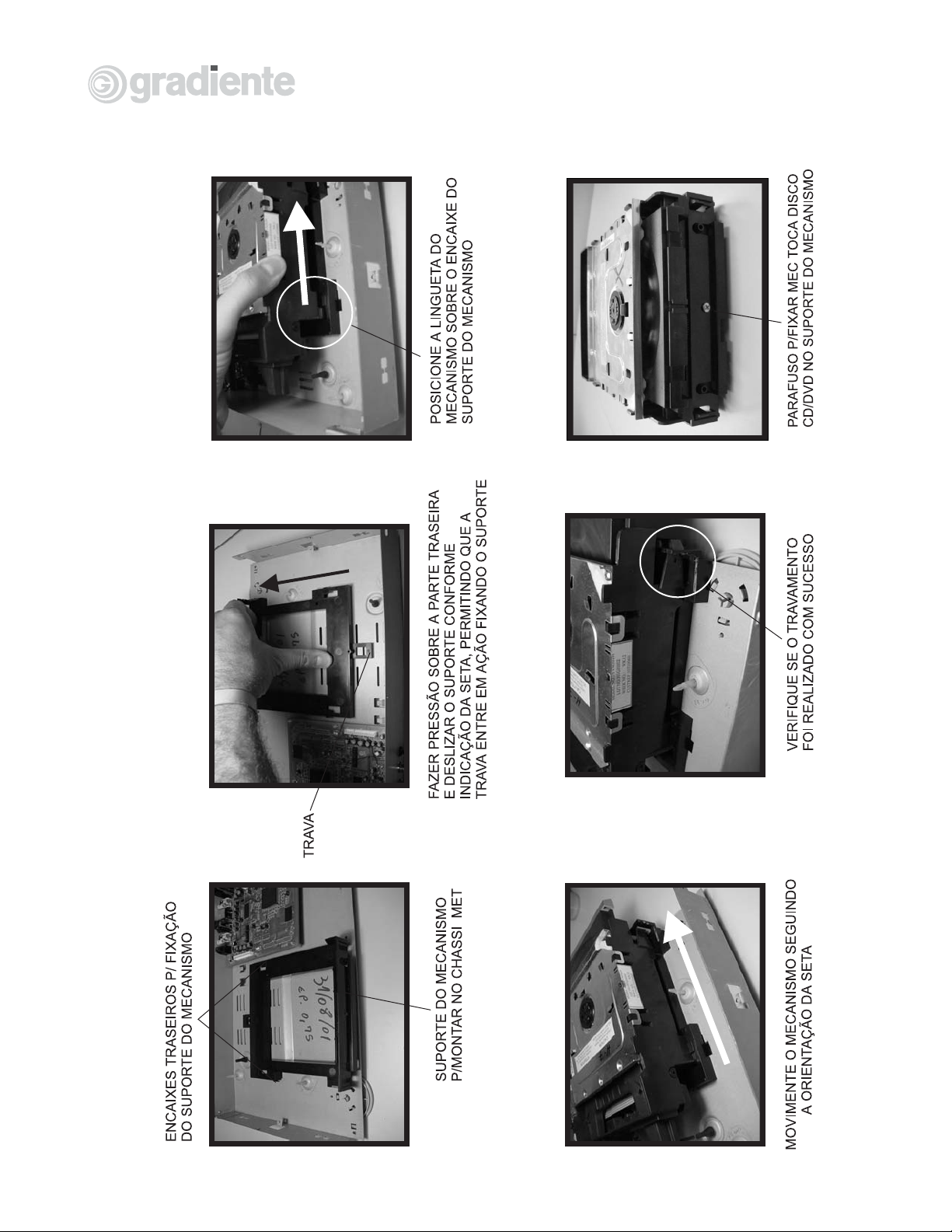

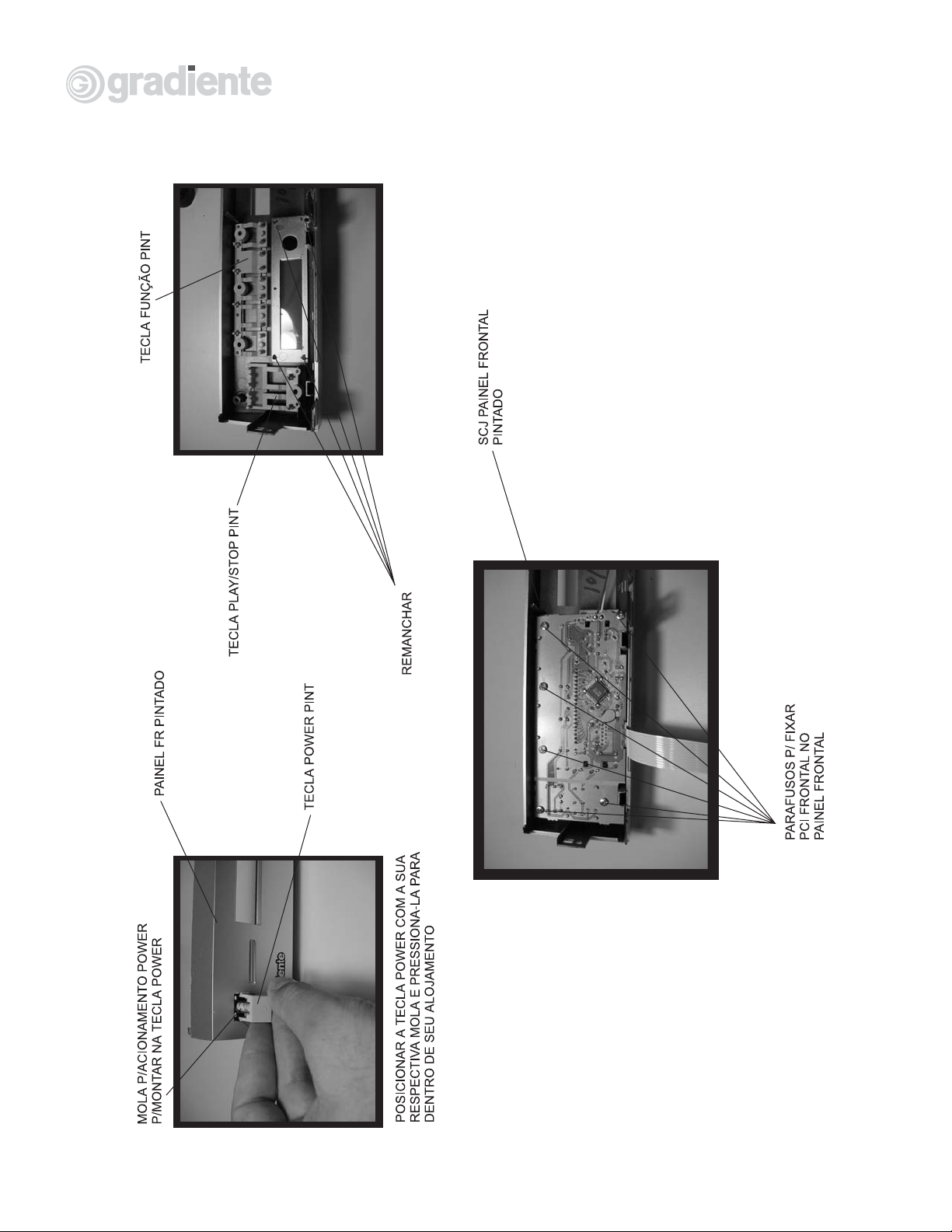

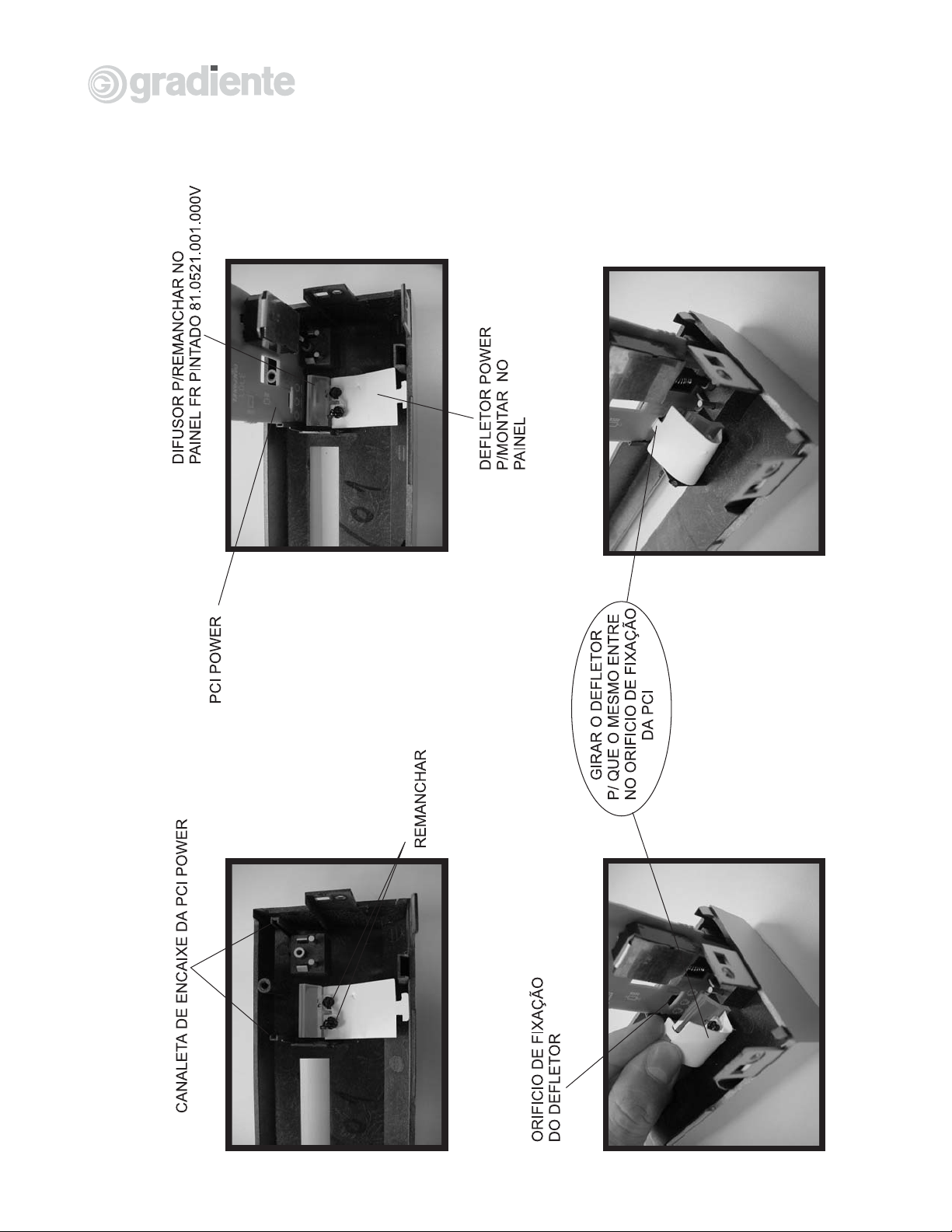

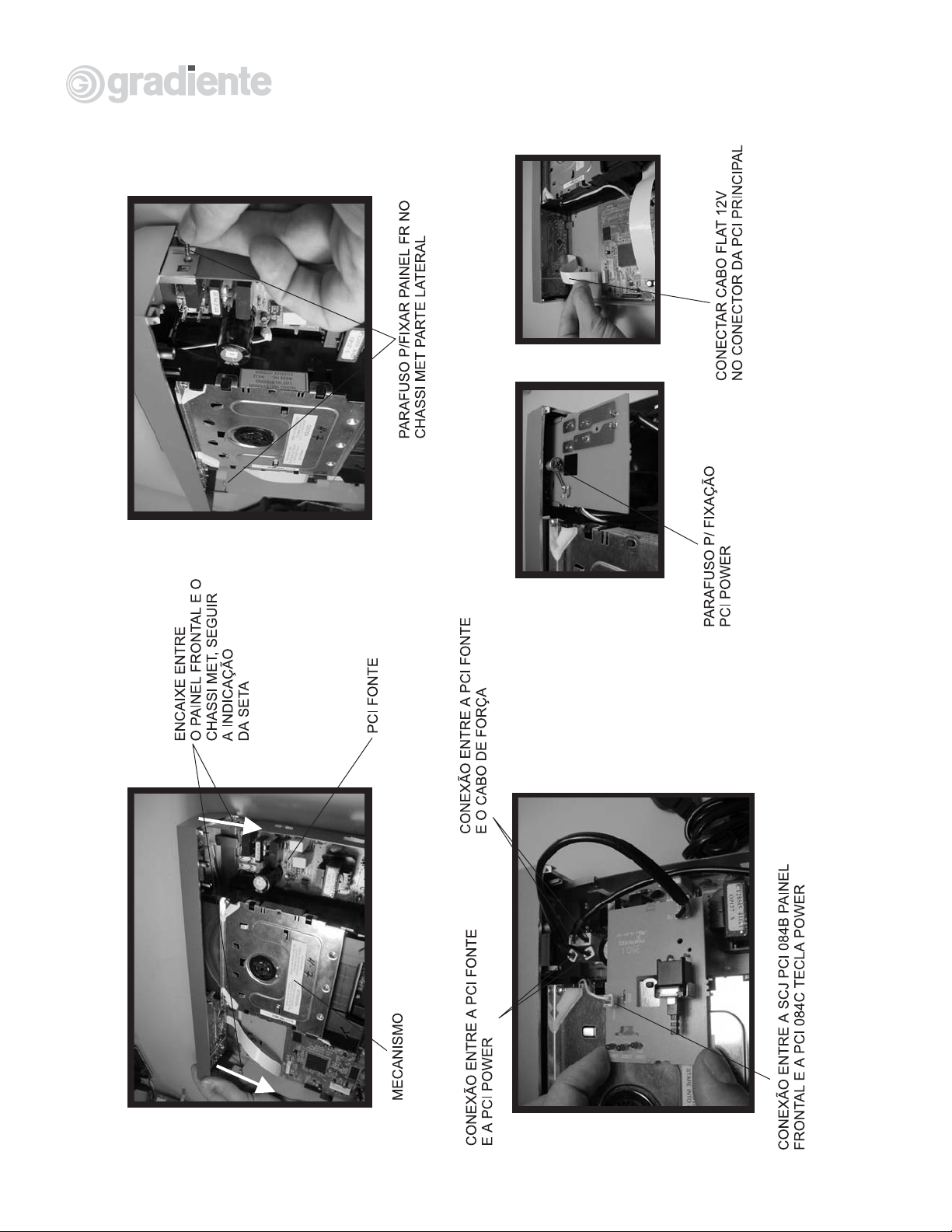

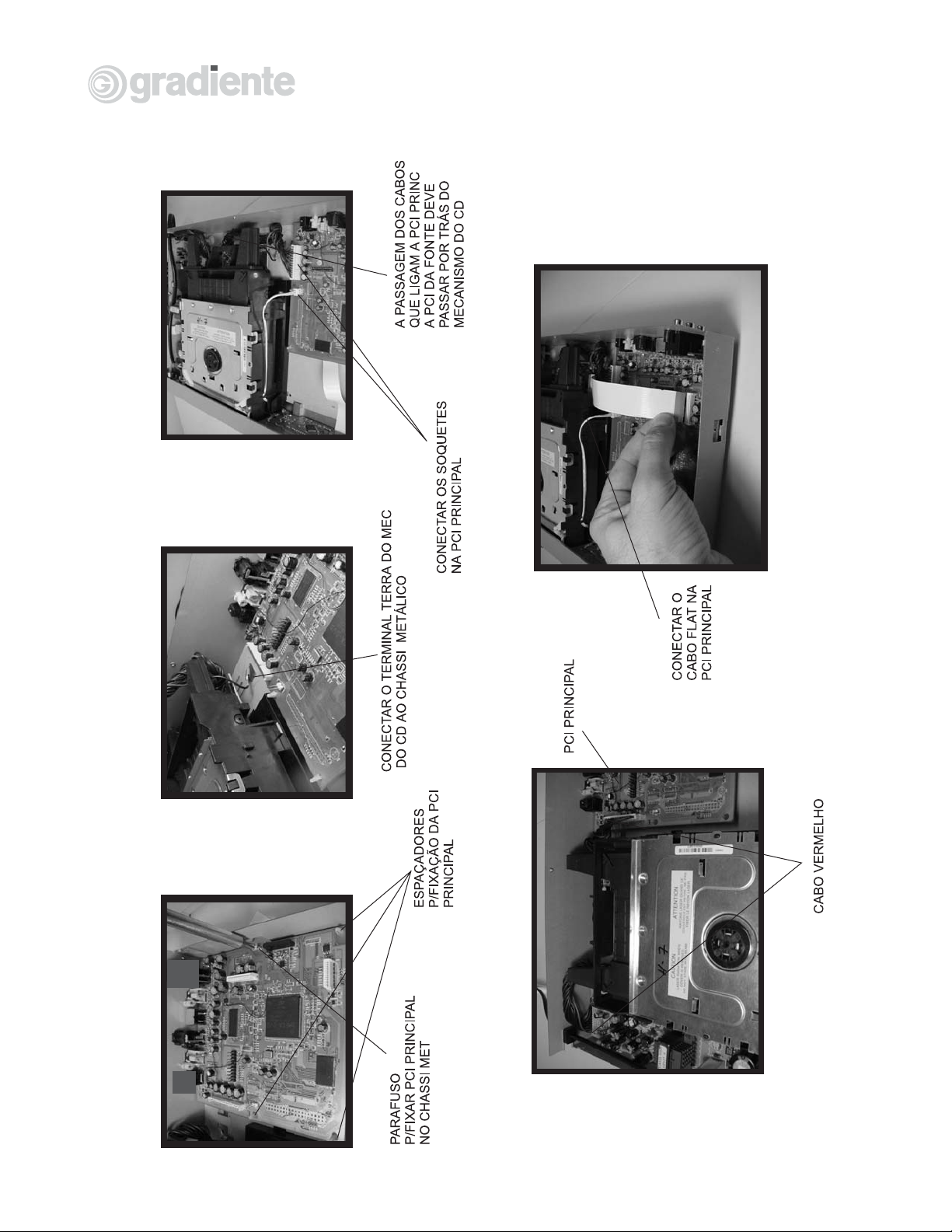

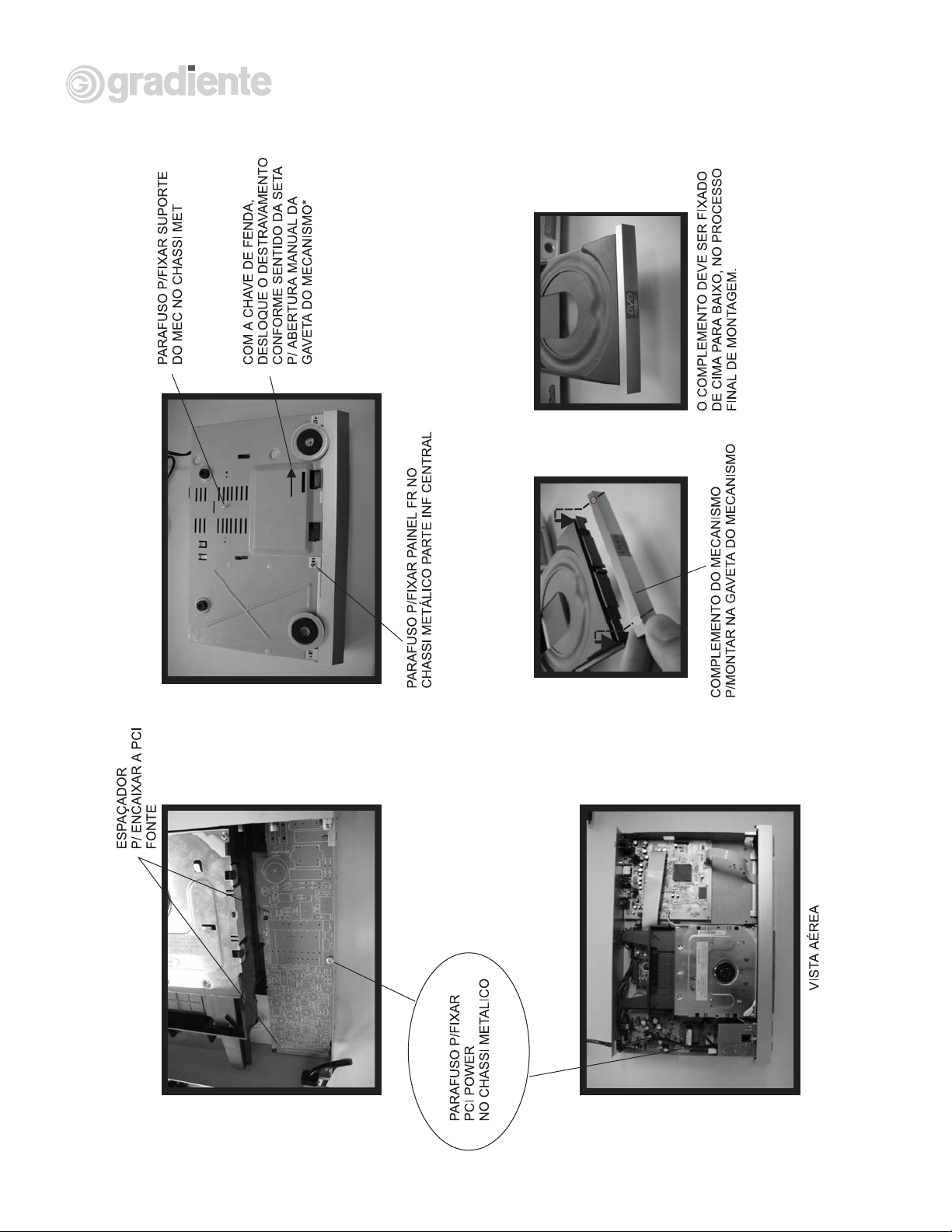

DESMONTAGEM DO CUBO

22 Manual de Serviço

Page 25

Manual de Serviço 23

Page 26

24 Manual de Serviço

Page 27

Manual de Serviço 25

Page 28

26 Manual de Serviço

Page 29

Manual de Serviço 27

Page 30

28 Manual de Serviço

Page 31

Manual de Serviço 29

Page 32

PROCEDIMENTOS: TESTE E VERIFICAÇÃO ELÉTRICA GERAL

1. Advertência

Esta especificação reflete as características do produto.

Os métodos de medição aqui descritos podem admitir

variações porém, não podem alterar as características

técnicas do produto.

2. Condições Gerais para Ensaio

- As medições especificadas foram obtidas com rede de

120VAC.

- A saída de vídeo deve estar carregada com 75

- A (s) saída(s) de áudio deve(m) estar carregada(s) com

Ω.

10k

- Em todas as medições efetuadas com osciloscópio, utilizar

pontas atenuados 10:1.

- 0 dBs = 0,775Vrms.

- 0 dBV= 1Vrms.

- 0 dBm= 1mW/600

- 0 dBµ = 1uV/75

- Valores com tolerância não especificada. Considerar +/10%.

- Os itens indicados com @. aplicam-se somente durante

o processo de fabricação (jigas) ou assistência técnica.

3. Características Técnicas

3.1 Gerais:

Ω.

Ω

Ω.

4. Procedimentos de testes

4.1 Equipamentos necessários

- MONITOR DE VÍDEO PAL-M/N/NTSC, COM ENTRADAS

S-VÍDEO / ÁUDIO E VÍDEO.

- AMPLIFICADOR DE ÁUDIO COM ENTRADA DIGITAL

COAXIAL.

- OSCILOSCÓPIO.

- DVD ZONA 1.

- DVD PAL* E NTSC.

- DVD DE TESTE DUPLA CAMADA.

- ABEX TEST TDV 525, ou equivalente

- ABEX TEST DVD-VIDEO TDV-540, ou equivalente

- ABEX TEST DVD-VIDEO TVD-541, ou equivalente

- ABEX TEST DVD-VIDEO TVD-545, ou equivalente

- DOLBY DVD DEMO AND TEST DISC, ou equivalente

- ABEX TEST CD TCD-725B, ou equivalente

- ABEX TEST CD TCD-785, ou equivalente

- ABEX TEST CD TCD-731, ou equivalente

- ABEX TEST CD TCD-712, ou equivalente

- MEDIDOR DE ISOLAÇÃO E RIGIDEZ DIELETRICA.

- MEDIDOR DE DISTORÇÃO

- MEDIDOR DE S/N

- MILIVOLTIMETRO AC.

- WATTIMETRO

- FREQUENCIMETRO

- VARIAC.

Obs.: DVD PAL* - Alternaltivo

- Alimentação: 90 ~250 VAC, 50/60Hz.

- Consumo de energia máximo: 27W.

- Peso:

- Dimensões em cm: L X A X P.

- Sistema de cor: NTSC / PAL-M/ PAL-N

- Temperatura operacional: 5º ~45º

- Faixa de umidade operacional: 10% a 75%

- Saída de Vídeo

Vídeo composto - 1,2 Vp-p (carga de 75

S-Vídeo - Sinal de luminânica 1,0

Vp-p (carga de 75

Sinal de cor 0,8 Vp-p

(carga de 75

(o,286 Vrms)

- Saída de áudio:

Analógica 0 ~2Vrms (1kHz)

Digital coaxial 2,0 Vp-p.

Ω

Ω

Ω

)

)

4.2 Preparação para ajuste:

Para verificação e teste deve-se adotar os limites

especificados abaixo:

- Tensão da rede: 90 Vac ~250 Vac.

5. Seção testes de segurança (esta seção deve ser

utilizada somente se for necessário e autorizado)

5.1 Teste da rigidez dielétrica

)

- Ajuste o medidor de isolação para: 1.200 VAC, FUNCTION

W, TIMER ON, 2 s, CUT-OFF 5mA, LOWER ON ( LOWER

REFERENCE: Ajustar aproximadamente na metade do

curso do potenciômetro).

- Conecte o polo positivo do medidor de isolação nos pinos

de força e o polo negativo no conector de saída de vídeo.

- Dispare o medidor e verifique o resultado da medição ( O

alarme não deve disparar).

- Teste o funcionamento geral do DVD player para confirmar

que não houve danos.

5.2 Teste de isolação

- Ajuste o medidor de isolação para: 500V DC, FUNCTION

I, TIMER ON, 2s, LOWER 1 M

Ω

, UPPER→JUDGE OFF.

30 Manual de Serviço

Page 33

- Conecte o polo positivo do medidor de isolação nos pinos

do cordão de força e o polo negativo no conector de saída

de RF.

- O valor medido deve ser > 1 M

disparar).

Ω

, (O alarme não deve

6. Seção fonte de alimentação

As medidas da fonte de alimentação do D-10/2 devem ser

feitas com as seguintes cargas de teste, para verificação

de conformidade. Conforme tabela abaixo:

Obs.: os testes 5.1 e 5.2 devem ser executados com o

aparelho fechado.

PINO TENSÃO DE SAÍDA CARGA DE TESTE COMENTÁRIOS

(OHMS) / WATTS

1 5VA 22R / 10W CARGA CONECTADA COM GND PIN-2

2 GND

3 NC*

4 12V 47R / 10W CARGA CONECTADA COM GND PIN- 6 e 7

5 -12V 1k2 / 0,5W CARGA CONECTADA COM GND PIN-6 e 7

6 GND

7 GND

8 5V 10R / 10W CARGA CONECTADA COM GND PIN - 6 e 7

9 3V3 10R / 10W CARGA CONECTADA COM GND PIN - 6 e 7

10 2V5 4R7 / 10W CARGA CONECTADA COM GND PIN - 6 e 7

11 GND

12 2,6 Vac 22R / 10W CARGA DEVE ESTAR ENTRE PINO 12 e 13

13 2,6 Vac A MEDIDA DEVE SER FEITA ENTRE

14 -23V 560R / 1W CARGA CONECTADA COM GND PIN - 11

NC* Não consta nenhuma ligação de saída.

@6.1 Tensão de 5VA Pino 1 Conector CN503

Obs.: as medidas de tensão da fonte não podem ser

executadas com o produto em funcionamento.

OS PINOS 12 e 13 ( na carga)

@6.4 Tensão de 5 V Pino 8 do Conector CN503

A tensão 5VA deve ser medida com o auxilio de um

voltímetro digital entre o pino 1 (5VA) e 2 (GND) do conector

CN 503. O valor encontrado deverá ser:

± ±

±

± ±

± ±

±

± ±

± ±

±

± ±

5%

5%

5%

5,15 Vdc

@6.2 Tensão 12 V Pino de 4 do Conector CN503

A tensão de 12VA deve ser medida com o auxilio de um

voltímetro digital entre o pino 4 (12VA) e pino 6,7 (GND)

do conector CN 503. O valor encontrado deverá ser:

12,6 Vdc

@6.3 Tensão de -12 V Pino 5 do Conector CN503

A tensão de -12VA deve ser medida com o auxilio de um

voltímetro digital entre o pino 5 (-12V) e pino 6,7 (GND) do

conector CN 503. O valor encontrado deverá ser:

-11,7

A tensão de 5V deve ser medida com o auxilio de um

voltímetro digital entre o pino 8 (5V) e pino 6,7 (GND) do

conector CN 503. O valor encontrado deverá ser:

5,1Vdc

@6.5 Tensão de 3,3V Pino 9 do Conector CN503

A tensão de 3,3V deve ser medida com o auxilio de um

voltímetro digital entre o pino 9 (3V3) e pino 6,7 (GND) do

conector CN 503. O valor encontrado deverá ser:

3,3Vdc

@6.6 Tensão de 2,5V Pino 10 do Conector CN503

A tensão de 2,5V deve ser medida com o auxilio de um

voltímetro digital entre o pino 10 (2V5) e pino 6,7 (GND)

do conector CN 503. O valor encontrado deverá ser:

2,5Vdc

± ±

±

± ±

+/− +/−

+/−

+/− +/−

± ±

±

± ±

5%

5%

5%

Manual de Serviço 31

Page 34

@6.7 Tensão de filamento (2,6 Vac) - Pino 12 (Fil1) e Pino

13 (Fil2) do conector CN503.

8.2 Saída de S-vídeo

A tensão de filamento (2,6Vac) deve ser medida com o

auxílio de um voltímetro digital AC entre os pinos 12 e 13

do conector CN503. O valor medido deverá ser de:

± ±

10%

2,6Vac

@6.8 Tensão de -23V Pino 14 do Conector CN503

A tensão de -23V deve ser medida com o auxilio de um

voltímetro digital entre o pino 14 (-23V) e pino 11 (GND)

do conector CN 503. O valor encontrado deverá ser:

-23Vdc

@6.9 Consumo do primário

Com um watimetro ligado a entrada de rede do produto e

com o aparelho ligado, deverá se obter:

< 30W (potência máxima)

< 15W (potência em Stand-By)

7. Seção DVD

7.1 Frequencia do Clock (27.000Mhz). (apenas verificação)

Com o auxilio de um frequencimetro medir a frequencia

do clock do sistema no R255. O valor encontrado deverá

ser de:

±

± ±

± ±

±

± ±

10%

Reproduzir um disco de DVD com padrão 100% full color

bar e com o auxilio de um osciloscópio medir o nível de

saída de luminânica (Y) e crominância (C) na saídaS-vídeo

com uma carga de 75

ser de:

9. Seção Áudio

9.1 Nível de sáida de áudio (R/L)

Inserir disco de teste TCD-785, selecionar TNO 1, com o

auxílio de um milivoltimetro ac medir o nível das saídas L

e R, que deverá ser de:

Ω.

Os valores encontrados deverão

Y: 1,0 Vp-p

C: 0,8 Vp-p

2,00V +/- 0,1V

± ±

±

0,1 Vp-p

± ±

± ±

±

0,1 Vp-p

± ±

26.9991MHz ~27.000810MHz

8. Seção Vídeo

8.1 Saída de vídeo composto

Reproduzir um disco de DVD com padrão 100% full color

bar e com o auxilio de um osciloscópio medir o nível de

saída de vídeo com uma carga de 75

deverá ser de:

± ±

1,2 Vpp

32 Manual de Serviço

±

± ±

Ω.

0,1 Vpp

O valor encontrado

9.2 Distorção nas saídas de Áudio (R/L)

Inserir disco de teste TCD-785, selecionar TNO 1, com o

auxílio de um medidor de distorção e filtros acionados,

medir a distorção nas saídas L e R que deverá ser de:

< 0,1%

9.3 Diferença entre as saídas R e L.

Inserir disco de teste TCD-785, selecionar TNO 1, com o

auxílio de um milivoltimetro ac medir A diferença entre os

níveis das saídas L e R, que deverá ser de:

< 0,5dB

9.4 Relação S/N

Inserir disco de teste TCD-785, selecionar TNO 1 e TNO

21, com o auxilio de um noise meter e filtros acionados

medir a relação S/N para as saídas L e R, que deverá ser

de:

> 8,5dB

Page 35

9.5 Separação Canal L.

Inserir disco de teste TCD-785, selecionar TNO 30, com o

auxilio de um milivoltimetro ac medir A diferença entre os

níveis das saídas L e R (nível residual), que deverá ser de:

> 80dB

9.6 Separação Canal R.

Inserir disco de teste TCD-785, selecionar TNO 35, com o

auxilio de um milivoltimetro ac medir A diferença entre os

níveis das saídas L (nível residual), que deverá ser de:

> 80dB

9.7 Resposta de freqüência (R/L)

Inserir disco de teste TCD-785, selecionar TNO 20, com o

auxilio de um milivoltimetro ac medir a resposta de

freqüência nas saídas L e R, que deverá ser de:

> 0,5dB

9.8 Saída de Áudio Digital

Inserir disco DOLBY DVD DEMO AND TEST DISC e

selecionar titulo 41 ou 30, com o axulio de um osciloscópio

medir o nível de saída, que deverá ser de:

> 1,6 Vpp

Obs.: os itens 9.1 à 9.7 devem ser executados com

uma carga de 10K

Ω.

10. Teste de reprodução

10.1 - Teste de black Dot e Finger Prints (TDV-525)

1- Colocar disco para reproduzir e fazer a verificação de

BLACK DOT no capitulo 9.

2- Inspeção audível: o som não deve ficar travando ou

pulando e não dever haver ruído.

3- Inspeção visual: verificar em um osciloscópio se o sinal

de áudio das saídas R e L não estão vibrando e com ruído.

4- Colocar no capitulo 13 e fazer o teste de FINGER

PRINTER.

5- Inspeção audível: o som não deve ficar travando ou

pulando e não deve haver ruído.

6- Inspeção visual: verificar em um osciloscópio se o sinal

de áudio das saídas R e L não estão vibrando e com ruído.

Manual de Serviço 33

Page 36

MECANISMO - PROCEDIMENTOS PARA VERIFICAÇÃO E MANUTENÇÃO (TVM502H / TVM502P*)

Obs.: consideramos que é praticamente nulaa possibilidade de uso desta versão de mecanismo (TVM-502P) para

DVD Player D-10/2

1. Instrução para manutenção do Mecanismo

Visando a melhoria do procedimento de manutenção e o

aprimoramento técnico dos SAGs estamos disponibilizado

a instrução de manutenção dos mecanismos TVM502H,

TVM502P.

O DVD Player D-10/2 utilizou 2 tipos de mecanismos que

são respectivamente os modelos, TVM502P e TVM502H

que podem ser identificados através da etiqueta de

descrição localizada na lateral esquerda do mecanismo,

conforme pode ser observado na figura.

ATENÇÃO:

Esta instrução não se aplica nos mecanismos de modelo

TVM502A, TVM502C, TVM502D. Para estes modelos, devese fazer o pedido do mecanismo inteiro utilizando o código

disponível no GBS.

As partes do mecanismo TVM502H, TVM502P não são

compatíveis, pedimos portanto atenção dobrada ao realizar

o pedido de alguma parte. Nas figuras abaixo pode ser

observada as diferenças na PCI Servo, Unidade Óptica, e

conector Unidade Óptica

TVM502H

Unidade

Óptica

Conector

Unidade

Óptica

Memória

EEPROM

somente no

TVM502P

2. Procedimento para a verificação do sinal de HF.

È necessário sempre verificar o nível do sinal de HF, antes

de realizar a troca da unidade óptica

Reproduzir o disco TDV-525 na trilha 1.

Monitorar a tensão no ponto de teste M2 RF (EYE

PATTERN).

A tensão deve ser 1,25Vpp com variação de 15% ( 1,0

vpp 1,4vpp ) para tensões menores de 1 vpp

recomendamos que a unidade óptica seja substituída.

Deve-se observar também se a forma de onda não

apresenta grande oscilações.

3. Procedimento para a verificação da corrente laser

Com o disco TDV-525 na trilha1 em play, medir a

tensão sobre o resistor RS16. O resistor está localizado

próximo ao cabo da unidade óptica.

O valor da tensão medido deve ser dividido pelo valor

do resistor RS16 10ohms, veja o exemplo abaixo.

TVM502P

34 Manual de Serviço

Unidade

Óptica

Conector

Unidade

Óptica

Memória

EEPROM

somente no

TVM502P

0,25 V

ΩΩ

10

Ω

ΩΩ

= 0,025 A = 25mA

O valor resultante corresponde ao valor da corrente

do diodo laser e pode ser utilizado como parâmetro para

determinar o grau de desgaste do componente. Verifique

se o valor medido/calculado corresponde ao valor nominal

da unidade óptica, o valor encontra-se impresso na

etiqueta que está no corpo da unidade óptica conforme

pode ser observado na figura.

Valor da corrente da Unidade Óptica

Caso o valor medido estiver 20%

acima do valor nominal a unidade

óptica deve ser substituida por outra

do mesmo modelo.

Obs.: em caso de dúvida consulte o Orientador Técnico.

Page 37

DESCRIÇÃO DOS PINOS DOS PRINCIPAIS CIRCUITOS INTEGRADOS

IC200 ( Microprocessador STI5519)

1. Microprocessador de DVD com características

otimizadas de Áudio.

1.1. DADOS PRELIMINARES

CPU integrada de 32-bits @ 60MHz

2 Kbytes de Icache, 2 Kbytes de Dcache, e 4 Kbytes de SRAM

configurável como Dcache.

Decodificador de áudio

Decodificação Dolby Digital

®

5.1 / MPEG-2 multi-canal, saídas

PMC 3 x 2 canais.

Saída digital IEC60958 -IEC61937

SRS

®

/ TrueSurround

®

Saída digital DTS® e decodificação MP3

Decodificador de vídeo

Suporta MPEG-2 MP @ ML

Zoom-in e Zoom-out totalmente programável

Conversão de NTSC para PAL

Decodificador de sub-imagem DVD e SVCD

Display na tela (OSD) de alto desempenho

Opções de OSD de 2 a 8 bits por pixel

Filtros anti-flicker, anti-flutter e anti-aliasing

Codificador PAL/NTSC/SECAM

Saídas RGB, CVBS, Y/C e YUV com DACs de 10 bits

Compatível com Macrovisionâ 7.01/6.1

O STi5519 é uma solução de back-end altamente integrada

para aplicações de DVD. Uma CPU gerencia a aplicação geral

(a interface de usuário e a navegação do DVD, CD-DA, VCD

e SVCD) e controla os drivers de periféricos inclusos. Os

periféricos inclusos incluem um processador de áudio,

decodificadores de vídeo e sub-imagem, OSD e um codificador

PAL/NTSC.

Devido à economia de memória, ao alto número de periféricos

internos e à plataforma de desenvolvimento e projeto de

referência aperfeiçoados, o STi5519 oferece uma solução de

excelente relação custo/benefício para aplicações DVD, com

curto tempo para ser entregue ao mercado.

O alto nível de integração em um único encapsulamento

PQFP208 torna o STi5519 ideal para aplicações de reprodutor

de DVD de baixo custo e grande volume.

Interface de memória SDRAM compartilhada

SDRAM de 125MHz de 1 ou 2x16-Mbit, ou 1x64Mbit

Interface de memória da CPU programável para SDRAM,

ROM, periféricos...

Interface de front-end

Compatível com DVD, VCD, SVCD e CD-DA

Interfaces serial, paralela e ATAPI

Filtragem do setor de hardware

Buffer de trilha e tradução de criptografia CSS integrados

Periféricos integrados

2 UARTs, controlador I2C, 3 saídas PWM, 3 temporizadores

de captura.

38 bits de I/O programável

Suporte à ferramentas profissionais

Compilador e bibliotecas C ANSI

Encapsulamento PQFP de 208 pinos

Manual de Serviço 35

Page 38

VISTA DA ARQUITETURA (DIAGRAMA DE BLOCO)

1. Visão geral da arquitetura

1.1. Introdução

A figura abaixo mostra a arquitetura do STi5519

Esse capítulo fornece uma breve visão geral de cada bloco

funcional do STi5519.

36 Manual de Serviço

Page 39

PINAGEM

Manual de Serviço 37

Page 40

DESCRIÇÃO DA PINAGEM

1. Pinos ordenados por número

Núm. do Pino Nome do pino Função principal Função alternativa Direção

Entrada Saída

Lado esquerdo

1 PIO2[5] PIO2[5] I/O

2 PIO2[6] PIO2[6] I/O

3 PIO2[7] PIO2[7] I/O

4 VDD3_3 3.3 V ALIMENTAÇÃO ALIMENTAÇÃO

5 VSS TERRA ALIMENTAÇÃO

6 PIO3[0] PIO3[0] PARA_DATA{0] I/O

7 PIO3[1] PIO3[1] PARA_DATA{1] I/O

8 PIO3[2] PIO3[2] PARA_DATA{2] I/O

9 PIO3[3] PIO3[3] CPAURE_INO I/O

PARA_DATA[3]

10 PIO3[4] PIO3[4] CAPTURE_IN1 UART1 RTS (RTS1) I/O

PARA_DATA[4]

11 PIO3[5] PIO3[5] CAPTURE_IN2 UART2 RTS (RTS2) I/O

PARA_DATA[5]

12 PIO3[6] PIO3[6] PARA_DATA[6] COMP_OUT1 I/O

UART1 CTS (CTS1)

13 PIO3[7] PIO3[7] PARA_DATA[7] COMP_OUT0 I/O

UART2 CTS (CTS2)

14 VDD2_5 2.5V ALIMENTAÇÃO ALIMENTAÇÃO

15 VSS TERRA ALIMENTAÇÃO

16 B_DATA 12S DATA SER_DATA I

17 B_BCLK 12S BIT CLOCK SER_BCLK I

18 B_FLAG 12S ERROR FLAG DVD SER_VALID I

19 B_SYNC 12S SECTOR/ABS TIME SER_SYNC I

20 Reservado B_WCLK I/O

2 and 6

1

I/O

I/O

NRSS_CLOCK

21 Reservado B_V4 NRSS_OUT

22 Reservado NRSS_IN

7

23 VDD_RGB VDDA_RGB=2.5V ALIMENTAÇÃO

24 VSS_RGB VSSA_RGB=GND ALIMENTAÇÃO

25 B_OUT B_OUT O

26 G_OUT G_OUT O

27 R_OUT R_OUT O

28 V_REF_RGB V_REF_DAC_RGB I

29 I_REF_RGB I_REF_DAC_RGB I

30 VDD_YCC VDDA_YCC=2.5V ALIMENTAÇÃO

31 VSS_YCC VSSA_YCC=GND ALIMENTAÇÃO

32 Y_OUT Y_OUT O

38 Manual de Serviço

Page 41

Núm. do Pino Nome do pino Função principal Função alternativa Direção

Entrada Saída

Lado esquerdo

33 C_OUT C_OUT O

34 CV_OUT CV_OUT O

35 V_REF_YCC V_REF_DAC_YCC I

36 I_REF_YCC I_REF_DAC_YCC I

37 VDD2_5 2.5V ALIMENTAÇÃO ALIMENTAÇÃO

38 VSS TERRA ALIMENTAÇÃO

39 PIO4[0] PIO4[0] YC[0] I/O

40 PIO4[1] PIO4[1] YC[1] I/O

41 PIO4[2] PIO4[2] YC[2] I/O

42 PIO4[3] PIO4[3] YC[3] I/O

43 PIO4[4] PIO4[4] YC[4] I/O

44 PIO4[5] PIO4[5] YC[5] I/O

45 PIO4[6] PIO4[6] YC[6] I/O

46 PIO4[7] PIO4[7] YC[7] I/O

47 VDD3_3 3.3 V ALIMENTAÇÃO ALIMENTAÇÃO

48 VDD_PCM VDD FREQ.SYNTH=2.5V ALIMENTAÇÃO

49 VSS_PCM VSS FREQ.SYNTH=GND ALIMENTAÇÃO

50 VSS TERRA ALIMENTAÇÃO

51 DAC_SCLK SAMPLING CLK EXT_AUD_CLK O

52 DAC_PCMOUT0 PCM_OUT0 EXT_AUD_DATA O

Lado inferior

53 DAC_PCMOUT1 PCM_OUT1 EXT_AUD_REQ I/O

54 DAC_PCMOUT2 PCM_OUT2 O

55 DAC_PCMCLK PCM_CLOCK I/O

56 DAC_LRCLK LEFT/RIGHT CLK EXT_AUD_WCLK O

57 SPDIF_OUT SPDIF_OUT O

58 SMI_ADR[4] Barramento de end. SDRAM O

59 SMI_ADR[5] Barramento de end. SDRAM O

60 SMI_ADR[6] Barramento de end. SDRAM O

61 SMI_ADR[7] Barramento de end. SDRAM O

62 SMI_ADR[8] Barramento de end. SDRAM O

63 SMI_ADR[9] Barramento de end. SDRAM O

64 VDD2_5 2.5V ALIMENTAÇÃO ALIMENTAÇÃO

65 VSS TERRA ALIMENTAÇÃO

66 SMI_ADR[3] Barramento de end. SDRAM O

67 SMI_ADR[2] Barramento de end. SDRAM O

68 SMI_ADR[1] Barramento de end. SDRAM O

69 SMI_ADR[0] Barramento de end. SDRAM O

70 SMI_ADR[10] Barramento de end. SDRAM O

71 SMI_ADR[11] Barramento de end. SDRAM O

Manual de Serviço 39

Page 42

Núm. do Pino Nome do pino Função principal Função alternativa Direção

Entrada Saída

72 SMI_ADR[12] Barramento de end. SDRAM O

73 SMI_ADR[13] Barramento de end. SDRAM O

74 SMI_CS[0] Chip select do banco 0 O

75 SMI_CS[1] Chip select do banco 1 O

76 SMI_RAS RAS SDRAM O

77 SMI_CAS CAS SDRAM O

78 SMI_WE Habilitação de escr. SDRAM O

79 SMI_DQML DQ MASK EN LOW O

80 SMI_DQMU DQ MASK EN UP O

81 VDD3_3 3.3 V ALIMENTAÇÃO ALIMENTAÇÃO

82 SMI_CLKIN Entrada de clock da SDRAM I

83 VSS TERRA ALIMENTAÇÃO

84 SMI_DATA[0] Barramento de dados SDRAM I/O

85 SMI_DATA[1] Barramento de dados SDRAM I/O

86 SMI_DATA[2] Barramento de dados SDRAM I/O

87 SMI_DATA[3] Barramento de dados SDRAM I/O

88 SMI_DATA[4] Barramento de dados SDRAM I/O

89 SMI_DATA[5] Barramento de dados SDRAM I/O

90 SMI_DATA[6] Barramento de dados SDRAM I/O

91 SMI_DATA[7] Barramento de dados SDRAM I/O

92 SMI_DATA[8] Barramento de dados SDRAM I/O

93 SMI_DATA[9] Barramento de dados SDRAM I/O

94 VDD2_5 2.5V ALIMENTAÇÃO ALIMENTAÇÃO

95 SMI_CLKOUT Saída de clock da SDRAM O

96 VSS TERRA ALIMENTAÇÃO

97 SMI_DATA[10] Barramento de dados SDRAM I/O

98 SMI_DATA[11] Barramento de dados SDRAM I/O

99 SMI_DATA[12] Barramento de dados SDRAM I/O

100 SMI_DATA[13] Barramento de dados SDRAM I/O

101 SMI_DATA[14] Barramento de dados SDRAM I/O

102 SMI_DATA[15] Barramento de dados SDRAM I/O

103 Reservado I/O

104 Reservado I/O

Lado direito

105 Reservado I/O

106 Reservado O

107 VDD3_3 3.3 V ALIMENTAÇÃO ALIMENTAÇÃO

108 VSS TERRA ALIMENTAÇÃO

109 TRST

3

Reset de teste I

110 TMS Seleção de modo de teste I

40 Manual de Serviço

Page 43

Núm. do Pino Nome do pino Função principal Função alternativa Direção

Entrada Saída

111 TDO Saída de dados de teste O

112 TDI Entrada de dados de teste I

113 TCK Clock de teste I

114 PWM2 Modulador por larg. de pulso 2 VSYNC I/O

115 PWM1 Modulardor por larg. de pulso 1 BOOT_FROM_ROM

4

I/O

116 PWM0 Modulador por larg. de pulso 0 HSYNC I/O

117 CPU_OE Habilitação da saída I/O

118 CPU_RAM_CLK SDRAM CLOCK O

119 VDD2_5 2.5V POWER SUPLLY ALIMENTAÇÃO

120 PIX_CLK Clock principal de 27 MHz I

121 VSS TERRA ALIMENTAÇÃO

122 VDD_PLL VDD PLL=2.5V ALIMENTAÇÃO

123 VSS_PLL GND PLL=GND ALIMENTAÇÃO

124 RESET RESET DO CHIP I

125 IRQ[2] IRQ[2] (MD_IRQ) I

126 IRQ[1] IRQ[1] (ATAPI IRQ) I

127 IRQ[0] IRQ[0] (SERVO_IRQ) I

128 CPU_BE[0] Habilitação do byte 0 DQM[0] O

129 CPU_BE[1] Habilitação do byte 1 DQM[1] O

130 CPU_RW Leitura não escrita NOT_SDRAM-WE O

131 CPU_WAIT Estado de espera I

132 CPU_CE[3] CHIP sel. banco 3 CS_SUB_BANK3 O

133 CPU_CE[2] CHIP sel. banco 2 O

134 CPU_CE[1] CHIP sel. banco 1 O

135 CPU_CE[0] DRAM_RAS0 SDRAM_RAS O

136 VDD3_3 3.3 V ALIMENTAÇÃO ALIMENTAÇÃO

137 VSS TERRA ALIMENTAÇÃO

138 CPU_RAS1 DRAM RAS NOT_SDRAM_CS1 I/O

139 CPU_CAS0 DRAM CAS0 SDRAM_CAS O

CPU_ADR[22]

140 CPU_CAS1 DRAM NOT_SDRAM_CS0 O

141 CPU_DATA[0] DATA[0] I/O

142 CPU_DATA[1] DATA[1] I/O

143 CPU_DATA[2] DATA[2] I/O

144 CPU_DATA[3] DATA[3] I/O

145 CPU_DATA[4] DATA[4] I/O

146 CPU_DATA[5] DATA[5] I/O

147 CPU_DATA[6] DATA[6] I/O

148 CPU_DATA[7] DATA[7] I/O

149 VDD2_5 2.5V ALIMENTAÇÃO ALIMENTAÇÃO

Manual de Serviço 41

Page 44

Núm. do Pino Nome do pino Função principal Função alternativa Direção

Entrada Saída

150 VSS TERRA ALIMENTAÇÃO

151 CPU_DATA[8] DATA[8] I/O

152 CPU_DATA[9] DATA[9] I/O

153 CPU_DATA[10] DATA[10] I/O

154 CPU_DATA[11] DATA[11] I/O

155 CPU_DATA[12] DATA[12] I/O

156 CPU_DATA[13] DATA[13] I/O

Lado superior

157 CPU_DATA[14] DATA[14] I/O

158 CPU_DATA[15] DATA[15] I/O

159 VDD3_3 3.3 V ALIMENTAÇÃO ALIMENTAÇÃO

160 VSS TERRA ALIMENTAÇÃO

161 CPU_ADR[1] ADR[1] O

162 CPU_ADR[2] ADR[2] O

163 CPU_ADR[3] ADR[3] O

164 CPU_ADR[4] ADR[4] O

165 CPU_ADR[5] ADR[5] O

166 CPU_ADR[6] ADR[6] O

167 CPU_ADR[7] ADR[7] O

168 CPU_ADR[8] ADR[8] O

169 CPU_ADR[9] ADR[9] O

170 CPU_ADR[10] ADR[10] O

171 VDD2_5 2.5V ALIMENTAÇÃO ALIMENTAÇÃO

172 VSS TERRA ALIMENTAÇÃO

173 CPU_ADR[11] ADR[11] O

174 CPU_ADR[12] ADR[12] O

175 CPU_ADR[13] ADR[13] O

176 CPU_ADR[14] ADR[14] O

177 CPU_ADR[15] ADR[15] O

178 CPU_ADR[16] ADR[16] O

179 CPU_ADR[17] ADR[17] O

180 CPU_ADR[18] ADR[18] O

181 CPU_ADR[19] ADR[19] O

182 CPU_ADR[20] ADR[20] O

183 CPU_ADR[21] ADR[21] O

184 VDD3_3 3.3 V ALIMENTAÇÃO ALIMENTAÇÃO

185 VSS TERRA ALIMENTAÇÃO

186 PIO0[0] PIO0[0] UARTO_DATA I/O

187 PIO0[1] PIO0[1] ATAPI_RD I/O

188 PIO0[2] PIO0[2] ATAPI_WR I/O

42 Manual de Serviço

Page 45

Núm. do Pino Nome do pino Função principal Função alternativa Direção

Entrada Saída

189 PIO0[3] PIO0[3] I/O

190 PIO0[4] PIO0[4] I/O

191 PIO0[5] PIO0[5] I/O

192 PIO0[6] PIO0[6] I/O

193 PIO0[7] PIO0[7] I/O

194 PIO1[0] PIO1[0] SSC0_DATA (MTSROut/MRSTin) I/O

195 PIO1[1] PIO1[1] SSC0_CLOCK I/O

196 PIO1[2] PIO1[2] PARA_DVALID I/O

197 PIO1[3] PIO1[3] UART2_TXD I/O

198 VDD2_5 2.5V ALIMENTAÇÃO ALIMENTAÇÃO

199 VSS TERRA ALIMENTAÇÃO

200 PIO1[4] PIO1[4] UART2_RXD I/O

201 PIO1[5] PIO1[5] PARA_SYNC UART1_TXD I/O

202 Entrada do disp. Entr. do disparador p/ DCU I/O

203 Saída do disp. Saída do disparador p/ DCU I/O

204 PIO2[0] PIO2[0] UART3_DATA I/O

205 PIO2[1] PIO2[1] UART1_RXD PARA_REQ I/O

206 PIO2[2] PIO2[2] PARA_STR I/O

207 PIO2[3] PIO2[3] I/O

208 PIO2[4] PIO2[4] I/O

Tabela 2, pinos ordenados por número

1. Bits 8 e 9 do FEI_CFG devem ser programados de acordo com a configuração NRSS requerida.

2. Os pinos NRSS_IN e NRSS_OUT são invertidos no STi5519 em comparação com o STi5508.

3. Mantenha em nível baixo quando a JTAG não for usada.

4. BOOTFROMROM fica ativo durante reset.

Manual de Serviço 43

Page 46

IC202 (CI M29F800AT MEMÓRIA FLASH)

1. Memória Flash de fonte simples de 8Mbit

(1Mb x8 ou 512Kb x16, Bloco de boot)

TENSÃO DE ALIMENTAÇÃO SIMPLES DE 5V±10%

PARA OPERAÇÕES DE PROGRAMAÇÃO,

APAGAMENTO E LEITURA

TEMPO DE ACESSO: 70ns

TEMPO DE PROGRAMAÇÃO

- 8us por byte/palavra típico

19 BLOCOS DE MEMÓRIA

- 1 bloco de boot (Localização

superior ou inferior)

- 2 blocos de parâmetro e 16 principais

CONTROLADOR DE PROGRAMAÇÃO/APAGAMENTO

- Incluso algoritmo de programação de

Byte/Palavra

- Incluso algoritmo de apagamento

de Multi-Bloco/Chip

- Registrador de estado

- Pino de saída pronto/ocupado

MODOS DE INTERROMPER / CONTINUAR

APAGAMENTO

- Lê e programa outro bloco durante

interrupção de apagamento

Figura 1. Diagrama Lógico

MODO DE DESPROTEGER BLOCO TEMPORARIAMENTE

BAIXO CONSUMO DE ENERGIA

- Standby e Standby automático

100.000 CICLOS DE PROGRAMAÇÃO

POR BLOCO

20 ANOS DE RETENÇÃO DE DADOS

- Defeitos abaixo 1 ppm/ano

ASSINATURA ELETRÔNICA

- Código do fabricante: 0020h

- Código do dispositivo M29F800AT: 00ECh

- Código do dispositivo M29F800AB: 0058h

44 Manual de Serviço

Page 47

Figura 2. Conexões do TSOP

2. Descrição Resumida

O M29F800A é uma memória não-volátil de 8Mbit (1Mb x8 ou

512Kb x16) que pode ser lida, apagada e reprogramada. Essas

operações podem ser realizadas usando uma única fonte de

5V. Ao ser ligada a memória entra em modo de leitura onde

pode ser lida da mesma forma que uma ROM ou EPROM.

A memória é dividida em blocos que podem ser apagados

independentemente portanto é possível preservar dados válidos

enquanto dados antigos são apagados. Cada bloco pode ser

protegido independentemente para evitar que comandos

acidentais de programação ou apagamento alterem a memória.

Comandos de apagamento/ programação são escritos na

Interface de Comando da memória. Um controlador no chip

simplifica o processo de programar ou apagar a memória

cuidando de todas as operações especiais que são requeridas

para atualizar o conteúdo da memória. O fim de uma operação

de programação ou apagamento pode ser detectado e qualquer

condição de erro identificada. O conjunto de comandos

requeridos para controlar a memória estão de acordo com os

padrões JEDEC.

Tabela 1. Nomes dos sinais

A0-A18 Entradas de endereço

DQ0-DQ7 Entradas/Saídas de Dados

DQ8-DQ14 Entradas/Saídas de Dados

DQ15A1 Entrada/Saída de Dados ou entrada de endereço

E Habilitação do chip

G Habilitação da saída

W Habilitação de escrita

RP Reset / Desproteger temporariamente bloco

RB Saída Pronto/Ocupado

BYTE Seleção de organização por byte/palavra

VCC Tensão de Alimentação

VSS Terra

NC Não conectado internamente

Manual de Serviço 45

Page 48

Tabela 2.Valores máximos absolutos (1)

Símbolo Parâmetro Valor Unidade

TA Temperatura ambiente de operação (Faixa de temperatura opção 1) 0 a 70 °C

Temperatura ambiente de operação (Faixa de temperatura opção 6) -40 a 85 °C

Temperatura ambiente de operação (Faixa de temperatura opção 3) -40 a 125 °C

TBIAS Temperatura sob polarização -50 a 125 °C

TSTG Temperatura de armazenamento -65 a 150 °C

VIO(2) Tensão de entrada ou saída -0.6 a 6 V

VCC Tensão de alimentação -0.6 a 6 V

VID Tensão de identificação -0.6 a 13.5 V

Nota:

1. Exceto pelo parâmetro Faixa de temperatura de operação, exceder os limites acima listados na tabela Valores máximos

absolutos pode causar dano permanente ao dispositivo. Esses são valores máximos e a operação do dispositivo sob essas

ou qualquer outra condição acima das indicadas na seção de Operação dessas especificações não é indicada. Exposição às

condições de Valores Máximos Absolutos por longos períodos pode afetar a confiabilidade do produto. Veja também o programa

SURE da STMicroeletronics e outros documentos relevantes de qualidade.

2. A Tensão mínima pode cair a -2V durante transição e por menos de 20ns durante transições.

Os blocos na memória são organizados de modo assimétrico,

veja tabelas 3 e 4, Blocos de endereços. Os primeiros ou últimos

64Kbytes foram divididos em quatro blocos adicionais.

O Bloco de Boot de 16Kbyte pode ser usado para um pequeno

código de inicialização para iniciar o microprocessador, os dois

Blocos de Parâmetros de 8Kbyte podem ser usados para

armazenamento de parâmetros e os 32Kbyte restantes formam

um pequeno Bloco Principal onde a aplicação pode ser

guardada.

Tabela 3. Endereços da Bloco de Boot

M29F800AT

# Tamanho Faixa de endereços Faixa de endereços

(Kbytes) (x8) (x16)

18 16 FC000h-FFFFFh 7E000h-7FFFFh

17 8 FA000h-FBFFFh 7D000h-7DFFFh

16 8 F8000h-F9FFFh 7C000h-7CFFFh

15 32 F0000h-F7FFFh 78000h-7BFFFh

14 64 E0000h-EFFFFh 70000h-77FFFh

13 64 D0000h-DFFFFh 68000h-6FFFFh

12 64 C0000h-CFFFFh 60000h-67FFFh

11 64 B0000h-BFFFFh 58000h-5FFFFh

10 64 A0000h-AFFFFh 50000h-57FFFh

9 64 90000h-9FFFFh 48000h-47FFFh

8 64 80000h-8FFFFh 40000h-47FFFh

7 64 70000h-7FFFFh 38000h-3FFFFh

6 64 60000h-6FFFFh 30000h-37FFFh

5 64 50000h-5FFFFh 28000h-2FFFFh

4 64 40000h-4FFFFh 20000h-27FFFh

3 64 30000h-3FFFFh 18000h-1FFFFh

2 64 20000h-2FFFFh 10000h-17FFFh

1 64 10000h-1FFFFh 08000h-0FFFFh

0 64 00000h-0FFFFh 00000h-07FFFh

Os sinais Chip Enable, Output Enable e Werite Enable

controlam a operação do barramento da memória. Eles

permitem conexão simples a maioria dos micro-processadores,

freqüentemente sem lógica adicional.

A memória é oferecida em encapsulamentos TSOP48 (12 x

20mm) e S044 e é fornecida com todos os bits apagados

(colocados em 1).

46 Manual de Serviço

Page 49

DESCRIÇÕES DOS SINAIS

Veja a figura 1, Diagrama Lógico e tabela 1, Nomes dos sinais,

para uma breve visão geral dos sinais conectados a este

dispositivo.

Entradas de Endereço (A0-A18).

As entradas de endereço selecionam as células na matriz de

memória para acesso durante operações de leitura do

barramento. Durante operações de escrita no barramento elas

controlam os comandos enviados à Interface de comando da

máquina de estados interna.

Entradas/Saídas de dados (DQ0-DQ7).

As entradas/ saídas de dados enviam os dados guardados no

endereço selecionado durante uma operação de leitura do

barramento. Durante operações de escrita do barramento elas

mostram os comandos

enviados à Interface de Comando da máquina de estados

interna.

Entradas/saídas de dados(DQ8-DQ14).

As entradas/ saídas de dados enviam os dados guardados no

endereço selecionado durante uma operação de leitura do

barramento quando BYTE está alto, Vih. Quando BYTE está

baixo, VIL, esses pinos não são usados estão em alta

impedância.

Durante operações de escrita do barramento o registrador de

comandos não usa esses bits.

Ao ler o Registrador de Estado esses bits devem ser ignorados.

Entrada/saída de dados ou Entrada de endereço (DQ15A-1).

Quando BYTE está alto, VIH, esse pino se comporta como um

pino de endereço. DQ15A-1 baixo irá selecionar o LSB da

palavra no outro endereço, DQ15A-1 alto irá selecionar

o MSB. No texto considere esse pino como entrada/saída de

dados quando BYTE está em alto e como entrada de endereço

quando BYTE está baixo exceto quando especificado o

contrário.

Chip Enable (E).

O Chip Enable, E, ativa a memória, permitindo operações de

leitura e escrita. Quando Chip Enable está alto, Vih, todos os

outros pinos são ignorados.

Output Enable (G).

O Output Enable, G, controla a operação de leitura de

barramento da memória.

Write Enable (W).

O Write Enable, W, controla a operação de Escrita no

Barramento da Interface de Comando da memória.

Características AC de Reset/Block Temporary Unprotect para

maisdetalhes.

Mantendo RP em Vid irá temporariamente desproteger os

blocos protegidos na memória. Operações de programação e

apagamento em todos os blocos tornam-se possíveis. A

transição de Vih para Vid deve ser menor que tPHPHH.

Ready/Bysy Output (RB).

O pino Ready/Busy (Pronto/Ocupado) é uma saída de dreno

aberto que pode ser usada para identificar quando a matriz de

memória pode ser lida. Esse pino é de alta impedância durante

o modo de leitura, modo de auto-seleção e modo de

apagamento interrompido.

Depois de um reset de hardware, operações de leitura e escrita

do barramento não podem começar até que esse pino esteja

em alta impedância. Veja a tabela 17 e a figura 11,

Características AC de Reset/Block Temporary Unprotect.

Durante operações de programação ou apagamento esse pino

está em nível baixo, Vol. Ele irá permanecer baixo durante

comandos de leitura/ reset ou resets de hardware até que a

memória esteja pronta para entrar no modo de leitura.

O uso de uma saída de dreno aberto permite que os pinos

Ready/busy de várias memórias sejam conectadas a um único

resistor de pull-up.

Um nível baixo indica que uma, ou mais, das memórias está

ocupada.

Seleção de organização Byte/Palavra (BYTE)

Esse pino é usado para comutar entre os modos de barramento

de 8 e 16 bits da memória. Quando o pino está em nível baixo,

Vil, a memória está em modo de 8 bits, quando está em nível

alto a memória está em modo de 16 bits.

Tensão de alimentação Vcc.

A tensão de alimentação Vcc fornece energia para todas as

operações (Leitura, Programação, Apagamento, etc.)

A interface de comando é desabilitada quando essa tensão é

menor que a tensão de lockout, Vlko. Isso evita que operações

de escrita acidentalmente danifiquem os dados quando a

energia está sendo ligada, desligada ou durante transientes

na alimentação. Se o controlador de programação/ apagamento

estiver programando ou apagando durante esse período a

operação é abortada e o conteúdo da memória sendo alterado

não irá ser válido.

Um capacitor de 0,1uF deve ser conectado entre o pino de

tensão de alimentação Vcc e o pino terra Vss para desacoplar

os transientes da fonte de alimentação.

A largura da trilha da placa de circuito impresso deve ser

suficiente para levar a corrente requerida durante operações

de programação e apagamento, Icc4.

Reset/Block Temporary Unprotect (RP).

O pino Reset/Block Temporary Unprotect pode ser usado para

aplicar um reset de hardware na memória ou temporariamente

desproteger todos os blocos que tenham sido protegidos.

Um reset de hardware é alcançado mantendo esse pino em

nível baixo, por pelo menos tPLPX. Depois que esse pino vai a

nível alto, a memória estará pronta para operações de leitura e

operações de escrita após tPHEL ou tRHEL, o que ocorrer por

último. Veja a seção Ready/Busy Output, tabela 17 e figura 11,

Terra Vss. Esse pino é a referência de tensão para todas as

medições.

OPERAÇÕES DE BARRAMENTO

Existem cinco operações padrão de barramento que controlam

o dispositivo. São elas Leitura do Barramento, Escrita do

Barramento, Output Disable, Standby e Standby Automático.

Operações de barramento, para um resumo. Tipicamente

pulsos de menos de 5ns nas linhas Chip Enable e Write Enable

são ignorados pela memória e não afetam as operações de

barramento.

Manual de Serviço 47

Page 50

Leitura do barramento.

Essas operações de barramento lêem os dados de células de

memória ou registradores específicos na Interface de Comando.

Uma operação válida de leitura de barramento envolve definir

o endereço desejado nas entradas de endereço, aplicar um

nível baixo aos pinos Chip Enable e Output Enable e manter

Write Enable em nível alto. As entradas/saídas de dados irão

mostrar o valor, Formas de Onda AC do modo de leitura e a

Características AC de leitura, para detalhes de quando a saída

se torna válida.

Escrita de barramento.

Essas operações escrevem pela Interface de Comando. Uma

operação de escrita de barramento válida começa definindo o

endereço desejado nas entradas de endereço. As entradas de

endereço são trancadas pela Interface de comando na borda

de descida do sinal Chip Enable ou Write Enable, o que ocorrer

por último.

As entradas/saídas de dados são trancadas pela Interface de

comando na borda de subida do sinal Chip Enable ou Write

Enable, o que ocorrer primeiro. O sinal Output Enable deve

ser mantido alto durante todo a operação de escrita. Formas

de onda AC de escrita, Características AC de escrita, para

detalhes dos requisitos de temporização.

Output Disable.

As entradas/saídas de dados estão em estado de alta

impedância quando este pino está em nível alto.

Standby.

Quando Chip Enable está em nível alto, os pinos de entrada/

saída de dados são colocados em estado de alta impedância

e a corrente de alimentação é reduzida ao nível de standby.

Quando Chip Enable está em nível alto a corrente de

alimentação é reduzida à Corrente de Alimentação de Standby

TTL, Icc2. Para reduzir adicionalmente a corrente de

Alimentação para Corrente de Alimentação de Standby CMOS,

Icc3, Chip Enable deve ser mantido dentro de Vcc ± 0.2V. Para

níveis de corrente de Standby veja a tabela 13, Características

DC.

Durante operações de programação ou apagamento a memória

irá continuar a usar a Corrente de Alimentação de programação/

apagamento, Icc4, até que a operação esteja completa.

Standby Automático.

Se os níveis CMOS (Vcc ± 0.2V) são usados para excitar

o barramento e este fica inativo por 150ns ou mais a memória

entra em Standby Automático, onde a corrente de alimentação

interna é reduzida à Corrente de Alimentação Standby CMOS,

Icc3. As entradas/saídas de dados continuarão a enviar dados

se uma operação de leitura estiver em andamento.

Operações especiais de barramento.

Operações adicionais de barramento podem ser executadas

para ler a Assinatura Eletrônica e também para aplicar e

remover Proteção de Blocos. Essas operações de barramento

são voltadas para uso por equipamentos de programação e

não são normalmente usadas em aplicações. Elas requerem

que VID seja aplicado a alguns pinos.

Assinatura eletrônica.

A memória tem dois códigos, o código do fabricante e o código

do dispositivo, que pode ser lido para identificar a memória.

Esses códigos podem ser lidos aplicando os sinais listados

nas tabelas 5 e 6, Operações de barramento.

Proteção de blocos e Desproteger blocos.

Cada bloco pode ser separadamente protegido contra

apagamento ou programação acidental. Blocos protegidos

podem ser desprotegidos para permitir mudança nos dados.

Essas operações somente devem ser executadas em

equipamentos de programação.

Para informações adicionais veja a Nota de Aplicação AN1122,

Protegendo e Desprotegendo a Flash Série M29.

INTERFACE DE COMANDO

Todas as operações de escrita no barramento são interpretadas

pela Interface de comando. Comandos consistem de uma ou

mais operações Sequenciais de Escrita de Barramento. Falhas

em observar uma seqüência válida de operações de escrita de

barramento irão resultar no retorno da memória ao modo de

leitura. Nesse caso, depois de 50ns, uma transição de endereço

ou um sinal Chip Enable em nível baixo é requerido antes

de ler os dados corretos. A longa seqüência de comandos é

imposta para maximizar a segurança de dados.

O endereço usado para os comandos depende se a memória

está em modo de 8 ou 16 bits. Veja a tabela 7 ou 8, dependendo

da configuração que está sendo usada, para um

resumo dos comandos.

Comando de leitura/reset.

O comando de leitura/reset retorna a memória ao seu modo de

leitura onde ela se comporta como uma ROM ou EPROM. Isso

também reseta os erros no registrador de estado. Uma ou três

operações de escrita no barramento podem ser usadas para

executar o comando de Leitura/reset.

Se o comando de leitura/reset é executado durante uma

operação de apagamento de bloco ou seguindo um erro de

programação ou apagamento a memória irá levar até 10us para

abortar. Durante esse período nenhum dado válido poderá ser

lido na memória. Executar um comando de leitura/reset durante

uma operação de apagamento de bloco irá deixar dados

inválidos na memória.

Comando de auto-seleção.

Esse comando é usado para ler o código do fabricante, o código

do dispositivo e o estado de proteção dos blocos. Três

operações consecutivas de Escrita no barramento são

requeridas para executar o comando de auto-seleção. Uma

vez que o comando tenha sido executado a memória

permanece em modo de auto-seleção até que outro comando

seja executado.

No modo de auto-seleção o código do fabricante pode ser lido

usando uma operação de leitura do barramento com A0 = VIL

e A1 = VIL. Os outros bits de endereço podem ser colocados

em VIL ou VIH. O código de fabricante para a

STMicroelectronics é 0020h.

48 Manual de Serviço

Page 51

O código do dispositivo pode ser lido usando uma operação

de leitura do barramento com A0 = VIH e A1 = VIL. Os outros

bits de endereço podem ser colocados em VIL ou VIH. O código

de dispositivo para o M29F800AT é 00ECh e para o

M29F800AB é 0058h.

O estado de proteção dos blocos de cada bloco pode ser lido

usando uma operação de Leitura de barramento com A0 =

VIL, A1 = VIH, e A12-A18 especificando o endereço do bloco.

Os outrosbits de endereço podem ser colocados em VIL ou

VIH. Se o bloco endereçado está protegido então 01h é enviado

para as saídas de dados DQ0-DQ7, caso contrário 00h é

enviado.

Comando de programação.

O comando de programação pode ser usado para programar

um valor para um endereço na matriz de memória por vez. O

comando requer quatro operações de escrita no barramento,

a operação final de escrita tranca o endereço e o dado na

máquina de estado interna e inicia o controlador

de programação/apagamento.

Se o endereço cai em um bloco protegido, o comando de

programação é ignorado, os dados permanecem inalterados.

O registrador de estado não é lido e nenhuma condição de

erro é dada. Durante a operação de programação a memória

irá ignorar todos os comandos. Não é possível executar

nenhum comando para abortar ou pausar a operação. Os

tempos de programação típicos são dados na Tabela 9.

Operações de leitura durante a operação de programação irão

colocar o Registrador de estado na Saídas de dados.

Veja a seção de Registrador de estado para mais detalhes.

Depois que a operação de programação foi concluída a

memória irá retornar ao modo de leitura, a menos que um erro

tenha ocorrido. Quando um erro ocorre a memória irá continuar

a enviar o Registrador de estado para a saída. Um comando

Leitura/ Reset deve ser executado para resetar a condição de

erro e retornar ao modo de leitura.

Note que o comando de programação não pode mudar um

conjunto de bits em 0 para 1 novamente. Um dos comandos

de apagamento deve ser usado para colocar todos os bits de

um bloco ou da memória inteira em 1.

Depois que a operação de apagamento de chip for concluída a

memória irá retornar para o modo de leitura, a menos que um

erro tenha ocorrido. Quando um erro ocorre a memória continua

a enviar o conteúdo do registrador de estado. Um comando

leitura/ reset deve ser executado para zerar a condição de erro

e retornar ao modo de leitura.

O comando de apagamento de chip coloca todos os bits dos

blocos desprotegidos da memória em 1. Todos os dados são

perdidos.

Comando de apagamento de bloco.

Esse comando pode ser executado para apagar uma lista de

um ou mais blocos. Seis operações de escrita são requeridas

para selecionar o primeiro bloco da lista. Cada bloco adicional

na lista pode ser selecionado repetindo a sexta operação de

escrita usando o endereço do bloco adicional. A operação de

apagamento de bloco inicia o controlador de programação/

apagamento cerca de 50us depois da última operação de escrita

no barramento. Uma vez que o controlador de programação/

apagamento tenha iniciado não é possível selecionar mais

blocos. Cada bloco adicional deve portanto ser selecionado

até 50us depois do último bloco. O temporizador de 50us reinicia

quando um bloco adicional é selecionado. O registrador de

estado pode ser lido depois da sexta operação de escrita no

barramento. Veja o registrador de estado para detalhes

sobre como identificar se o controlador de programação/

apagamento iniciou a operação de apagamento de bloco. Se

algum dos blocos selecionados estiver protegido, ele será

ignorado e todos os outros blocos serão apagados. Se todos

os blocos selecionados estiverem protegidos a operação de

apagamento de bloco parece iniciar mas termina em cerca de

100us, deixando os dados inalterados. Nenhuma condição de

erro é dada quando blocos protegidos são ignorados. Durante

a operação de apagamento de blocoa memória irá ignorar todos

os comandos exceto o comando de interrupção de apagamento

e o de leitura/reset. Tempos típicos de apagamento de bloco

são dados na tabela 9.

Todas as operações de leitura durante a operação de

apagamento de chip irão colocar o registrador de estado nas

saídas de dados. Veja a seção sobre o registrador de estado

para mais detalhes.

Comando de apagamento de chip.

O comando de apagamento de chip pode ser usado para

apagar o chip inteiro. Seis operações de escrita do barramento

são requeridas para executar esse comando e iniciar o

controlador de programação/apagamento. Se algum bloco

estiver protegido eles serão ignorados e todos os outros blocos

são apagados. Se todos os blocos estão protegidos a operação

de apagamento de chip não começa e termina em cerca de

100us, deixando os dados inalterados. Nenhuma condição de

erro é dada quando blocos protegidos são ignorados.

Durante a operação de apagamento a memória irá ignorar

todos os comandos. Não é possível executar nenhum comando

para abortar a operação.

Tempos típicos de apagamento de chip são dados na tabela

9. Todas as operações de leitura durante a operação de

apagamento de chip irão colocar o registrador de estado nas

saídas de dados. Veja a seção sobre o registrador de estado

para mais detalhes.

Depois que a operação de apagamento de chip for concluída a

memória irá retornar para o modo de leitura, a menos que um

erro tenha ocorrido. Quando um erro ocorre a memória continua

a enviar para a saída o conteúdo do registrador de estado.

Um comando leitura/reset deve ser executado para zerar a

condição de erro e retornar ao modo de leitura. O comando de

apagamento de bloco coloca todos os bits dos blocos

desprotegidos selecionados da memória em 1. Todos os dados

nos blocos selecionados são perdidos.

Comando de Interrupção de apagamento.

Esse comando pode ser usado para suspender

temporariamente uma operação de apagamento de bloco e

retornar a memória ao modo de leitura. Esse comando requer

uma operação de escrita no barramento. O controlador de

programação/apagamento irá suspender o apagamento em até

15us após o comando ter sido executado. Uma vez que o

controlador tenha parado a memória irá entrar em modo de

leitura e o apagamento será interrompido. Se o comando for

executado durante o período em que a memória

estáaguardando por um bloco adicional (antes do controlador

Manual de Serviço 49

Page 52

iniciar), o apagamento é suspenso imediatamente e irá iniciar

imediatamente quando o comando de continuação do

apagamento for executado. Não será possível selecionar

nenhum bloco adicional para apagamento após o reinicio do

apagamento.

Durante a fase de suspensão é possível ler e programar células

nos blocos que não estão sendo apagados; ambas as

operações comportam-se de modo normal nesses blocos.

Leituras dos blocos que estão sendo apagados resultam em

leitura dos dados do registrador de estado. Também é possível

entrar no modo de auto-seleção: a memória irá se comportar

como no modo de auto-seleção em todos os blocos até que

um comando de leitura/reset retorne a memória para o modo

de interrupção de apagamento.

Comando de continuação de apagamento.

Esse comando deve ser usado para reiniciar o controlador de

programação/apagamento de uma interrupção de apagamento.

Um apagamento pode ser interrompido e continuado mais de

uma vez.

REGISTRADOR DE ESTADO

Operações de leitura de qualquer endereço sempre lêem o

registrador de estado durante operações de programação e

apagamento. Ele também é lido durante interrupção do

apagamento quando um endereço dentro de um bloco sendo

apagado é acessado.

Bit de verificação de dados(DQ7).

Esse bit pode ser usado para identificar se o controlador de

programação/apagamento completou a operação com sucesso

ou se ele respondeu a um comando de interrupção de

apagamento. Esse bit sai pelo DQ7 quando o registrador de

estado é lido.

Durante operações de programação esse bit envia o

complemento do bit sendo programado para DQ7. Depois de

uma operação de programação completa com sucesso a

memória retorna para o modo de leitura e as operações de

leitura no endereço programado enviam DQ7, não seu

complemento.

Durante operações de apagamento o bit envia 0, o

complemento do estado apagado de DQ7. Depois que a

operação termina com sucesso, a memória retorna para o modo

de leitura.

No modo de interrupção de apagamento o bit envia 1 durante

uma operação de leitura em um bloco sendo apagado. o Bit

muda de 0 para 1 quando o controlador de apagamento/

programação suspende a operação de apagamento.

Figura 4. O fluxograma da verificação de dados dá um exemplo

de como usar esse bit. Um endereço válido é o endereço sendo

programado ou um endereço dentro do bloco sendo apagado.

Bit de comutação (DQ6).

Esse bit pode ser usado para identificar se uma operação foi

concluída com sucesso pelo controlador de programação/

apagamento ou se ele respondeu a um comando de interrupção

de apagamento. Ele sai em DQ6 quando o registrador de estado

é lido.

Durante operações de programação ou apagamento o bit muda

de 0 para 1, para 0, etc., com sucessivas operações de

leitura em qualquer endereço. Depois de completar com

sucesso a operação a memória volta para o modo de leitura.

Durante o modo de interrupção de apagamento o bit é enviado

quando uma célula dentro de um bloco sendo apagado é

acessada.

O bit pára de mudar quando o controlador de programação/

apagamento suspende a operação de apagamento.

Figura 5. O fluxograma do bit de comutação dá um exemplo de

como usar esse bit.

Bit de erro (DQ5).

Esse bit pode ser usado para identificar erros detectados pelo

controlador de programação/apagamento. O bit de erro é

colocado em 1 quando uma operação de programação,

apagamento de bloco ou de chip falha em escrever os

dados corretos na memória. O bit de erro sai em DQ5 quando

o registrador de dados é lido.

Note que o comando de programação não pode mudar um bit

0 de volta para 1 e tentar fazê-lo pode ou não colocar

DQ5 em 1. Em ambos os casos, uma operação de leitura em

seguida irá mostrar o bit ainda em 0. Um dos comandos de

apagamento deve ser usado para colocar todos os bits no

bloco ou na memória inteira de 0 para 1.

Bit de temporização de apagamento (DQ3).

Esse bit pode ser usado para identificar o início da operação

do controlador de apagamento/programação durante um

comando de apagamento de bloco. Uma vez que o controlador

começa o apagamento o bit é colocado em 1. Antes do

controlador de programação/apagamento começar o bit é

colocado em 0 e blocos adicionais serem apagados podem

ser escritos via a interface de comando. O Bit de temporização

de apagamento sai em DQ3 quando o registrador de estado é

lido.

Bit de comutação alternativo (DQ2).

Esse bit pode ser usado para monitorar o controlador de

programação/apagamento durante operações de apagamento.

Esse bit sai em DQ2 quando o registrador de estado é lido.

Durante apagamento de chip e apagamento de bloco o bit muda

de 0 para 1 para 0, etc., com sucessivas operações de leitura

de endereços dentro dos blocos sendo apagados. Uma vez

que a operação termine a memória retorna ao modo de

leitura.

Durante interrupção do apagamento o bit muda de 0 para 1

para 0, etc., com sucessivas operações de leitura de endereços

dentro dos blocos sendo apagados. Operações de leitura em

blocos que não estão sendo apagados retornam o conteúdo

da célula como no modo de leitura.

Depois de uma operação de apagamento que causa a ativação

do bit de erro esse bit pode ser usado para identificar

qual bloco o blocos causaram o erro. Ele muda de 0 para 1

para 0, etc., com sucessivas operações de leitura de endereços

dentro dos blocos que não foram apagados corretamente. Esse

bit não muda se o bloco endereçado foi apagado corretamente.

50 Manual de Serviço

Page 53

Tabela 18.

Exemplo:

Tipo de dispositivo

M29

Voltagem operacional

F = Vcc = 5V ± 10%

Função de dispositivo

800A = 8 Mbit (1Mb x 8 ou 512 Kb x 16), Bloco

Forma Matriz

T = Bota de Topo

B = Bota de Fundo

Velocidade

70 = 70 ns

90 = 90 ns

Pacote

N = TSOP48: 12 x 20mm

M = S044

Gama de temperatura

1=0 a 70 °C

3 = 40 a 125 °C

6 = 40 a 85 °C

M29F800AB

70 N 1 T

Opção

T = Tape & Reel Embalagem

Nota: Os últimos caracteres de uso do código de ordenação podem ser substituídos por um código de carta para preprogramação

separada, caso contrário são transportados dispositivos da fábrica com a memória contendo apagamento 1.

Para uma lista de opções disponíveis (Velocidade, Empacote, etc...) ou para informação adicional sobre qualquer aspecto deste

dispositivo, por favor contate um Depto Service.

Manual de Serviço 51

Page 54

Tabela 20.

Simbolo mm polegadas

tipo min. max. tipo min. max.

A 1.20 0.0472

A1 0.05 0.15 0.0020 0.0059

A2 0.95 1.05 0.0374 0.0413

B 0.17 0.27 0.0067 0.0106

C 0.10 0.21 0.0039 0.0083

D 19.80 20.20 0.7795 0.7953

D1 18.30 18.50 0.7205 0.7283

E 11.90 12.10 0.4685 0.4764

e 0.50 - - 0.0197 - L 0.50 0.70 0.0197 0.0279

α 0° 5° 0° 5°

N48 48

CP 0.10 0.0039

Figura 12.

52 Manual de Serviço

Page 55

IC206(CI NM24C02 MEMÓRIA EEPROM)

1. NM24C02 - EEPROM de 2 kbits de Interface Serial de

padrão 2-fios

Descrição geral

Os dispositivos NM24C02/03 são memórias CMOS de 2048

bits não voláteis de apagamento elétrico.

Esses dispositivos atendem a todas as especificações do

padrão de protocolo Standard IIC 2-Wire e são projetados

para minimizar o número de pinos e simplificar os requisitos de

layout da placa.

A metade superior (acima de 1Kbit) da memória do NM24C03

pode ser protegida contra gravação conectando-se o pino

WP ao Vcc. Essa seção da memória torna-se então inalterável

a menos que o pino WP seja ligado ao Vss.

Esse protocolo de comunicação usa as linhas CLOCK (SCL) e

DATA I/O (SDA) para transferir dados de modo síncrono (entre

o dispositivo mestre (por exemplo um microprocessador) e o

dispositivo EEPROM escravo.

O protocolo Standard IIC permite um máximo de 16K de

memória EEPROM que é suportada pela família Fairchild em

dispositivos de 2K,4K,8K e 16K, permitindo ao usuário

configurar a memória conforme a aplicação requer com

qualquer combinação de EEPROMs. Para implementar

densidades de memória EEPROM mais altas no barramento

IIC, o protocolo Extended IIC deve ser usado. (Veja os

datasheets do NM24C32 ou NM24C65 para mais informação.)

Características

Larga faixa de tensão de operação 2.7V - 5.5V

Freqüência de clock (F) de 400 KHz em 2.7V - 5.5V

Corrente de ativo típica de 200µA

Corrente de standby típica de 10µA

Corrente de standby típica(L) de 1µA

Corrente de standby típica(LZ) de 0,1µA

Interface compatível com IIC

Modo de escrita em página de dezesseis bytes

Ciclo de escrita auto-temporizado

Proteção de escrita por Hardware para a metade superior

(somente NM24C03)

Durabilidade: 1,000,000 de mudanças de dados

Retenção de dados maior que 40 anos.

Encapsulamentos disponíveis: 8 pinos DIP, 8 pinos SO, e 8

pinos TSSOP

Disponível em três faixas de temperatura

Provê protocolo de transferência de dados

bidirecional Entradas Schmitt trigger

Minimiza o tempo total de escrita por byte.

Típico tempo do ciclo de escrita de 6ms

°

- Comercial: 0

- Estendida (E): -40° a +85°C

- Automotiva (V): -40

a +70°C

°

a +125°C

As EEPROMs Fairchild são projetadas e testadas para

aplicações que requerem alta durabilidade, alta confiabilidade

e baixo consumo de energia.

Diagrama de Blocos

Manual de Serviço 53

Page 56

Diagrama de Conexão

Encapsulamento Dual - in - line (N), Encapsulamento SO (M8) e Esncapsulamento TSSOP (MT8)

Nome dos pinos

Especificações do produto

Valores máximos absolutos

Temperatura ambiente de armazenamento -65°C a +150°C

Todas as tensões de entrada ou saída

em relação ao terra 6.5V a -0.3V

Temperatura do terminal

(Soldagem, 10 segundos) +300

Resistência a ESD 2000V min.

°

C

54 Manual de Serviço

Condições de operação

Temperatura ambiente de operação

NM24C02/03 0

NM24C02E/03E -40

NM24C02V/03V -40

Alimentação positiva

NM24C02/03 4.5V a 5.5V

NM24C02L/03L 2.7V a 5.5V

NM24C02LZ/03LZ 2.7V a 5.5V

°

C a +70°C

°

C a +85°C

°

C a +125°C

Page 57

Manual de Serviço 55

Page 58

56 Manual de Serviço

Page 59

IC208(CI LM833D AMPLIFICADOR OPERACIONAL DE ÁUDIO DUPLO (BAIXO RUÍDO))

Descrição Geral

O LM833 é um amplificador operacional de uso geral projetado

com particular ênfase em desempenho em sistemas de áudio.

Esse CI amplificador duplo utiliza novo circuito e técnicas de

processamento para obter baixo ruído, alta velocidade e grande

largura de banda sem aumentar os componentes externos ou

diminuir a estabilidade. O LM833 é compensado internamente

para todos ganhos de loop fechado e é portanto otimizado para

todos estágios de pré-amplificador e de alto nível em sistemas

PCM e HiFi.

O LM833 é compatível pino-a-pino com os amplificadores

operacionais duplos padrão da indústria.

Diagrama Esquemático

Características

Larga faixa dinâmica................................ 140dB

Baixa tensão de ruído de entrada ........... 4.5nV/

Alta taxa de subida .................................. 7V/us (typ), 5Vus (min)

Largura de banda de alto ganho ................ 15MHz (typ); 10MHz (min)

Grande largura de banda de potência .... 120KHz

Baixa distorção ........................................ 0.002%

Baixa tensão de offset ............................. 0.3mV

Grande margem de fase .......................... 60

Disponível em encapsulamento

MSOP de 8 pinos.

✓

Hz

°

Diagrama de conexão

Número de pedido LM833M, LM833MX,LM833N,LM833MM ou LM833MMX

Veja número de encapsulamento NS M08A.

Manual de Serviço 57

Page 60

Valores máximos absolutos (nota 1)

Se dispositivos com especificação para uso militar/aeroespacial

forem necessários, por favor contate o escritório de vendas da

National Semiconductor / Distribuidores para disponibilidade e

especificações.

Tensão de alimentação Vcc-Vee .................................36V

Tensão de entrada diferencial(Nota 3) Vi ....................± 30V

Faixa de tensão de entrada (Nota 3) Vic .................... ± 15V

Dissipação de potência (Nota 4) PD ........................... 500 mW

Faixa de temperatura de operação Topr ..................... -40 - 85°C

Faixa de temperatura de armazenamento Tstg .......... -60 - 150°C

Informação de soldagem

Encapsulamento Dual-In-Line

Soldagem ..................................................................... 260°C

Encapsulamento Small Outline(SOIC e MSOP)

Fase de vapor (60 segundos) ......................................215°C

Infravermelho (15 segundos) .......................................220°C

Veja AN-450 Métodos de montagem em superfície e seus efeitos sobre

a confiabilidade do produto

Tolerância a ESD (Nota 5) ........................................... 1600V

58 Manual de Serviço

Page 61

Manual de Serviço 59

Page 62

IC209(CI LM393 AMPLIFICADOR OPERACIONAL )

Comparadores duplos de baixa potência e baixa tensão de

Offset

A série LM193 consiste de dois comparadores de tensão de

precisão independentes com uma especificação de tensão de

offset tão baixa quanto 2,0mV máximos para dois comparadores

que são projetados especificamente para operar em uma única

fonte de alimentação em uma larga faixa de tensões. Operação

com fontes de alimentação divididas é também possível e o

consumo de corrente de alimentação baixa é independente da

magnitude da tensão de alimentação. Esses comparadores têm

também uma característica única em que a faixa de tensão

modo-comum da entrada inclui terra, mesmo se operado em

uma fonte de alimentação simples.

Áreas de aplicação incluem comparadores de limite,

conversores simples de analógico para digital, geradores de

pulso, onda quadrada e tempo de atraso; VCO de faixa larga,

temporizadores de clock MOS; multivibradores e portas lógicas

digitais de tensão elevada. A série LM193 foi projetada para

fazer interface direta com TTL e CMOS. Quando operado com

fontes de alimentação positiva e negativa, a série LM193 faz

interface direta com lógica MOS onde o seu baixo consumo de

energia é uma vantagem sobre os comparadores padrão.

Vantagens

Comparadores de alta precisão

Reduzida variação de Vos com a temperatura

Elimina necessidade de fontes duplas

Permite sensibilidade próxima ao terra

Compatível com todas as formas de lógica

Consumo de energia adequado para operação com baterias

Características

Larga faixa de alimentação

- Faixa de tensão 2.0V a 36V

- fonte simples ou dupla ±1.0V a ±18V

Consumo de corrente

muito baixo (0,4mA) - independente da

tensão de

alimentação.

Baixa corrente de polarização

de entrada: 25nA

Baixa corrente de entrada de offset: ±5 nA

Máxima tensão de offset: ±3 mV

Faixa de tensão de modo-comum de

entrada inclui terra.

Faixa de tensão de entrada diferencial

igual à tensão de alimentação.

Baixa tensão de saturação de saída 250 mV em 4 mA

Tensão de saída compatível com sistemas de lógica TTL,DTL,

ECL, MOS e CMOS.

Diagramas de conexão e esquemático

60 Manual de Serviço

Encapsulamento Dual-In-Line

Número de pedido LM193J/883 *

LM193AJ/883, LM193AJ-QMLV**

LM393M, LM393MX, LM2903M,

LM2903MX, LM393N ou LM2903N

Veja número de encapsulamento NS J08A,

M08A ou N08E

Page 63

Valores máximos absolutos (nota 10)

Se dispositivos com especificação para uso militar/aeroespacial

forem necessários, por favor contate o escritório de vendas

da National Semiconductor / Distribuidores para disponibilidade

e especificações.

Tensão de alimentação, V+ 36V

Tensão de entrada diferencial (Nota 8) 36V

Tensão de entrada -0.3V a +36V

Corrente de entrada (Vin < -0,3V) (Nota 3) 50mA

Dissipação de potência (Nota 1)

Molded DIP 780mW

Metálico 660mW

Encap. Small Outline 510mW

Curto-circuito da saída para o terra (nota 2)

Faixa de temperatura de operação

LM393/LM393A 0°C a +70°C

LM293/LM293A -25°C a +85°C

LM193/LM193A -55°C a +125°C

LM2903 -40°C a +85°C

Faixa de temperatura de armazenagem -65°C a +150°C

Temperatura do terminal

(Soldagem, 10 segundos) +260°C

Informação de soldagem

Encapsulamento Dual-In-Line

(Soldagem (10 segundos) 215°C

Encapsulamento Small Outline

Fase de vapor (60 segundos)

Infravermelho (15 segundos) 220°C

Veja AN-450 Métodos de montagem em superfície e seus

efeitos sobre a confiabilidade do produto para outros métodos

de soldagem de dispositivos montados em superfície.

Tolerância a ESD

(1,5kohms em série com 100pF) 1300V

Manual de Serviço 61

Page 64

62 Manual de Serviço

Page 65

Dimensões físicas em polegadas (milímetros) a menos que especificado o contrário (continuação)

Manual de Serviço 63

Page 66

IC210(CI TL7702A SUPERIOR DE TENSÃO DE ALIMENTAÇÃO)

Gerador de power-on reset

Geração automática de reset após queda de tensão

Larga faixa de tensão de alimentação... 3V a 18V

Sensor de tensão de precisão

Referência de tensão com compensação de temperatura

Saídas de reset verdadeira e complementar

Largura do pulso ajustável externamente

Descrição

A série TL7700A são circuitos integrados monolíticos de

supervisão de tensão de alimentação especificamente

projetados para uso como controladores de reset em sistemas

de microcomputador e microprocessador. Durante a ativação

o dispositivo testa a tensão de alimentação e mantém as saídas

RESET e RESET ativas (alta e baixa, respectivamente)

enquanto a tensão de alimentação não tenha atingido seu

valor nominal de tensão. Manter RESIN em nível baixo tem o

mesmo efeito. Para assegurar que o sistema microprocessador

seja resetado, o TL7700A inicia então um tempo interno que

atrasa o retorno das saídas de reset ao estado de inativas. Já

que o atraso de tempo para a maioria dos microcomputadores

e microprocessadores é da ordem de alguns ciclos de máquina,

o tempo de atraso interno é determinado por um capacitor

externo conectado à entrada Ct (pino 3).

Diagrama de Blocos

= 1.3 x 104 x C

t

d

T

Onde: Ct é em Farads(F) E td em segundos(s). Adicionalmente,

quando a tensão cai abaixo do valor nominal, as saídas estarão

ativas até que ela retorne ao valor nominal. Um capacitor

externo (tipicamente 0,1uF) deve ser conectado à saída REF

(pino 1) para reduzir a influência de transientes rápidos na

tensão de alimentação.

A série TL7700AI é para operação de -25°C a 85°C; a série

TL7700AC é para operação de 0°C a 70°C.

64 Manual de Serviço

Page 67

Manual de Serviço 65

Page 68

66 Manual de Serviço

Page 69

Manual de Serviço 67

Page 70

IC212(CI LB1641 DIRVER MOTOR BIDIRECIONAL)

Driver de Motor Bidirecional

O LB1641 é um CI driver de motor bidirecional. Tendo circuitos

lógicos de 2 entradas e executando funções de acionamento

bidirecional e frenagem, ele é capaz de acionar diretamente

motores de 12V. A tensão de saída pode ser variada usando

um diodo zener externo.

Características

A lógica de 2 entradas pode ser usada para controle do

acionamento bidirecional e frenagem.

Elementos no chip para absorver a corrente de partida do

motor.

Entrada compatível com MOS LSI.

Tensão de saída variável pelo uso de um diodo zener externo

Valores máximos absolutos em Ta = 25°C unidade

Tensão máxima de alimentação VCCmax 18 V

Tensão de entrada Vin -0,3 a Vcc V

Corrente de saída Iout +-1,6 A

Dissipação de potência permitida Pdmax 1,2 W

Temperatura de operação Topr -25 a +75 °C

Temperatura de armazenagem Tstg -55 a +125 °C

Condições de operação permitidas em Ta=25 ° unidade

Tensão de Alimentação Vcc1 7 a 18 V

Vcc2 5 a 18 V

Características elétricas em Ta=25 ºC, Vcc=12V

Tensão limiar de entradA Vth RL= ¥ 1,1 1,3 1,5 V

Mínima corrente de entrada

em estado ligado: Iin RL= ¥ 10 15 uA

Tensão de saída Vo RL=60ohms,Vz=7,4V 6,6 7,2 7,4 V

Corrente de fuga de saída IOL Pinos 5,6 GND, RL= ¥ 0,01 1,0 mA

Dissipação de Corrente Icc Pinos 5,6 GND, RL= ¥ 3 6 10 mA

Tensão de saturação (mais alta) Vsat1 Vcc=12V,Iout=300mA 1,9 2,2 V

Tensão de saturação(mais baixa) Vsat1 Vcc=12V,Iout=300mA 0,25 0,5 V

Vsat1 Vcc=12V,Iout=500mA 1,9 2,3 V

Vsat1 Vcc=12V,Iout=500mA 0,4 0,65 V

mín. típ. máx. unidade

Dimensões do encapsulamento 3043A

(unidade: mm)

Diagrama de blocos do circuito equivalente

Predriver

Tabela verdade

Entrada Saída Operação

IN1 IN2 OUT1 OUT2

0 0 0 0 Frenagem

1 0 1 0 Acionamento para frente (para trás)

0 1 0 1 Acionamento para trás (para frente)

1 1 0 0 Frenagem

Nível de entrada 1: 2,0V ou maior

0: 0,7V ou menos

68 Manual de Serviço

Circuito Lógico de Entrada

Page 71

IC501( TDA16833 CONTROLADOR OFF-LINE COM SENSOR DE 600V )

Dados preliminares

Visão Geral

Características

Controlador PWM + sensor CoolMOS

anexados em um encapsulamento compacto.