Page 1

DIGITAL STORAGE

O~CILLOSCOPE

054000

Instruction Manual

-} GOULD

Telephone 01-5001000

Telegrams Attenuate Ilford

Telex 263785

Page 2

Contents

SECTION 1

SECTION 2 Specification

SECTION

SECTION

SECTION 5 Maintenance

SECTION 6

SECTION 7 Guarantee and Service Facilities

Introduction

Operating Instructions

3

3.1 Supplies

3.2 C.R.T. Controls

3.3 Y Channel Controls

3.4 Timebase Controls

3.5 Store Controls 7

3.6 Alias Effects

3.7 Additional Facil ities

3.8

Functional Checks

4

CIRCUIT DESCRIPTION 12

4.1 System Description

4.2 Power Supplies

Y Amplifier

4.3

Analogue-Digital Converter

4.4

4.5 Store and Control Logic

Mode Control

4.6

4.7 Trigger and Timebase

4.8 D-A Converter and Dot Joiner 34

4.9 Calibrator

5.1 General

5.2 Mechanical Assembly

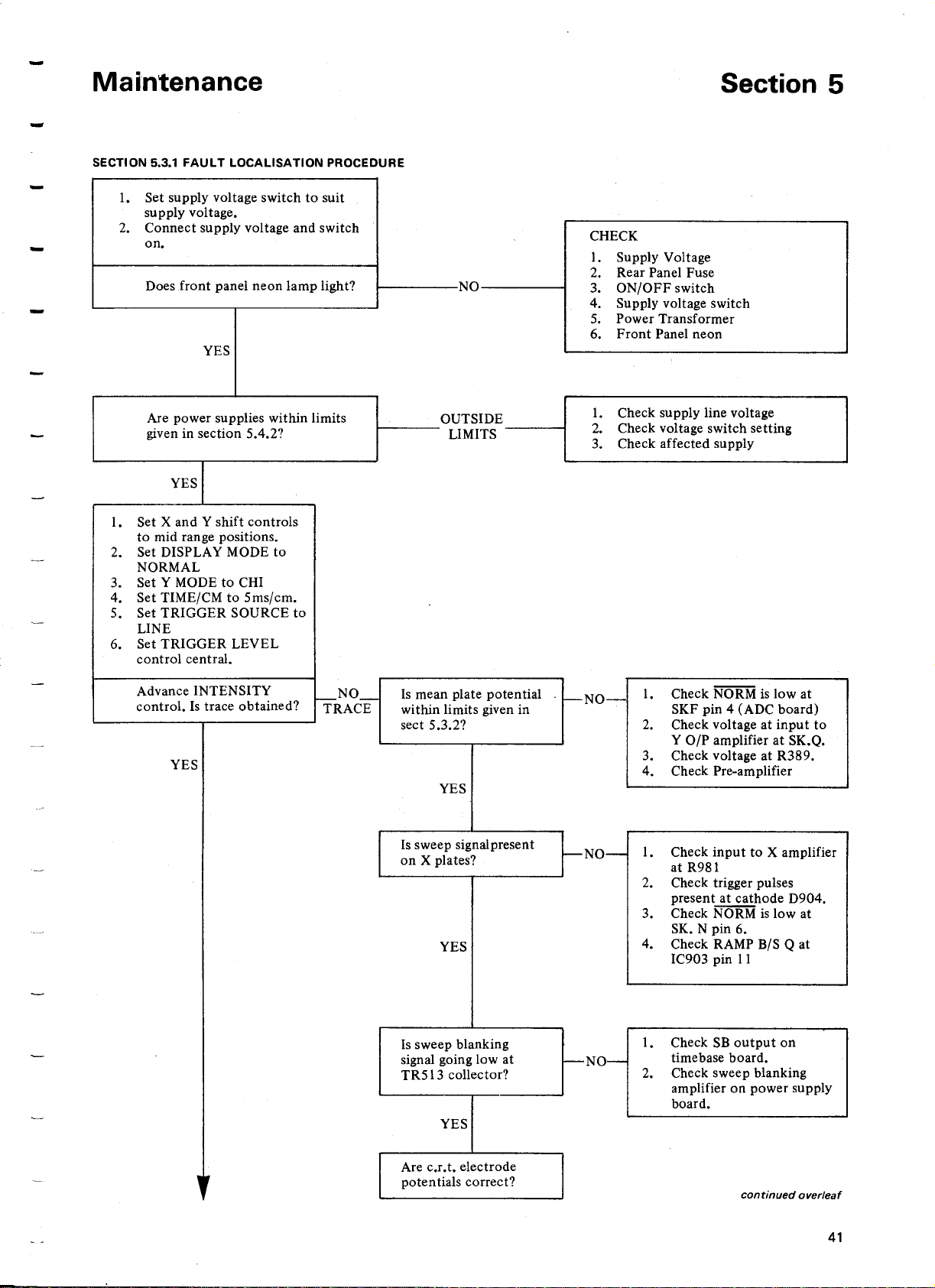

5.3 Fault Finding

5.4 Calibration Procedure

5.5 Wiring details for l00V operation

Circuit Diagrams and

Component Schedules 55

4

Fig. 1

5

6

6

6

6

6

8

9

9

12

13

14 Normal Mode

16

20

27

30 Position

35

36

36

36

39

52

52

79

Fig. 2 Block Diagram of Instrument

Fig.

Fig.

Fig. 5 Timing Signal Waveforms (ADC)

Fig.

Fig. 7 Logic Block Diagram:

Fig.

Fig. 9 Tim ing Diagram: Address

Fig. 10

Fig. 11

Fig. 12 Simplified Control Logic

Fig. 13

Fig. 14

Fig. 15

Fig. 16

Fig. 17

Fig. 18

Fig. 19

Fig. 20 Circuit Diagram: Power Supplies,

Fig. 21 Circuit Diagram: Pre-amplifiers

Fig. 22

Fig. 23

Fig. 24 Circuit Diagram: Timebase

Fig. 25 Circuit Diagram: D-A Converter

Fig. 26

Fig. 27

ILLUSTRATIONS

Alias Effects

3 Block Diagram of ADC

4

Typical Signal Waveforms (ADC)

Timing Chart (ADC)

6

Refreshed Mode

8 Tim ing Diagram: Refreshed

Mode

Sequence

Logic Block Diagram: Roll Mode 23

Timing Diagram: Roll Mode

Timebase Block Diagram:

Bottom View

Righthand View

Righthand View:

Control Condition Table

Data Faults

ADC Waveforms

Y Output and Blanking

Circuit Diagram: A-D Converter

Circuit Diagram: Timing and

Store Logic

and Dot Joiner

Interconnection Diagram 75

Mechanical Views

10

12

'16

17

18

19

20

21

22

24

28

30

37

37

Maintenance

38

40

50

51

57

59

63

69

71

73

77

Page 3

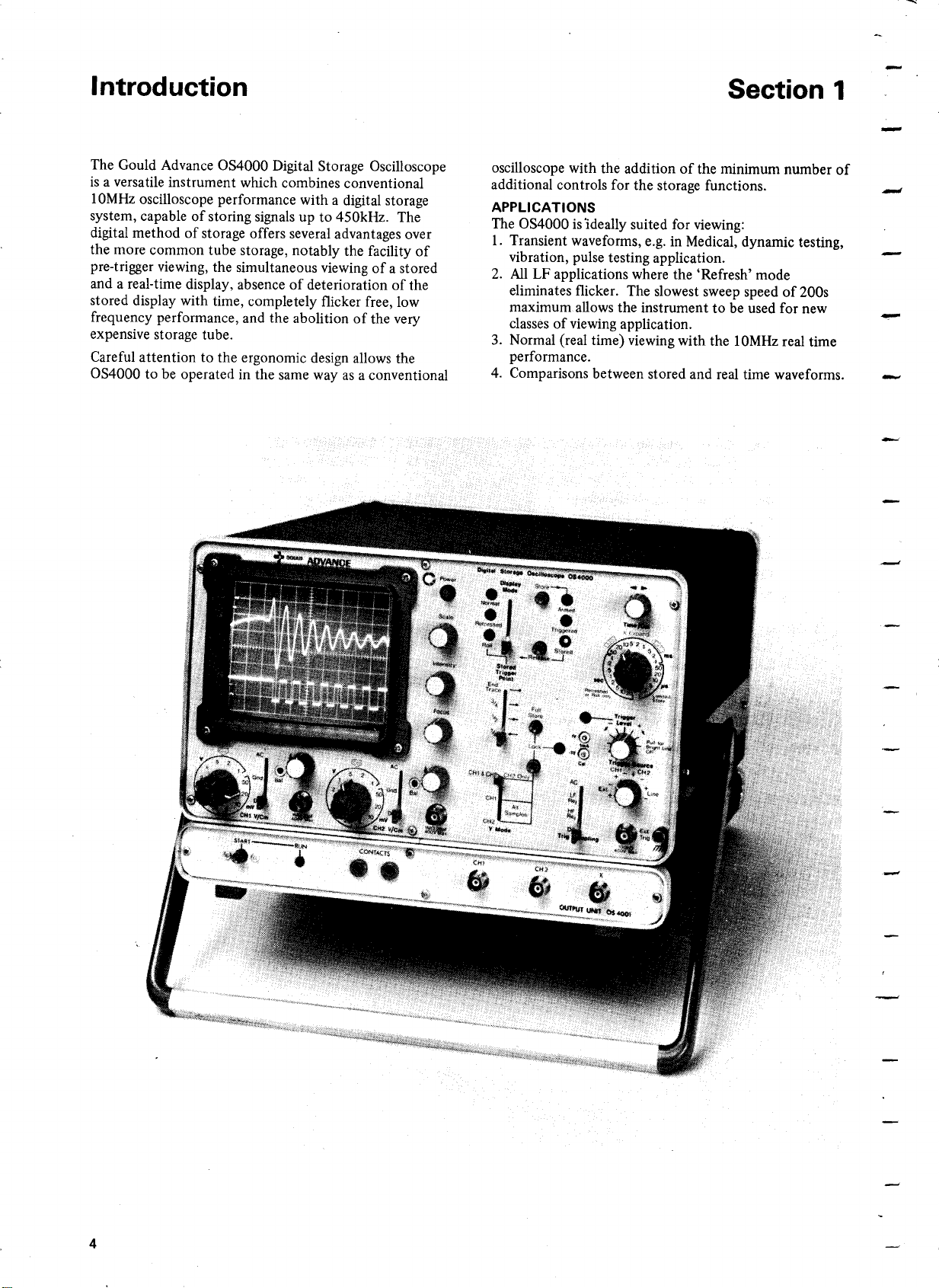

Section 1

The Gould Advance OS4000 Digital Storage Oscilloscope

is a versatile instrument which combines conventional

lOMHz oscilloscope performance with a digital storage

system, capable of storing signals up to 450kHz. The

digital method of storage offers several advantages over

the more common tube storage, notably the facility of

pre-trigger viewing, the simultaneous viewing of a stored

and a real-time display, absence of deterioration of the

stored display with time, completely flicker free, low

frequency performance, and the abolition of the very

expensive storage tube.

Careful attention to the ergonomic design allows the

OS4000 to be operated in the same way as a conventional

oscilloscope with the addition of the minimum number of

additional controls for the storage functions.

APPLICATIONS

The OS4000 is "ideallysuited for viewing:

1. Transient waveforms, e.g. in Medical, dynamic testing,

vibration, pulse testing application.

2. All LF applications where the 'Refresh' mode

eliminates flicker. The slowest sweep speed of 200s

maximum allows the instrument to be used for new

classes of viewing application.

3. Normal (real time) viewing with the 10MHz real time

performance.

4. Comparisons between stored and real time waveforms.

Page 4

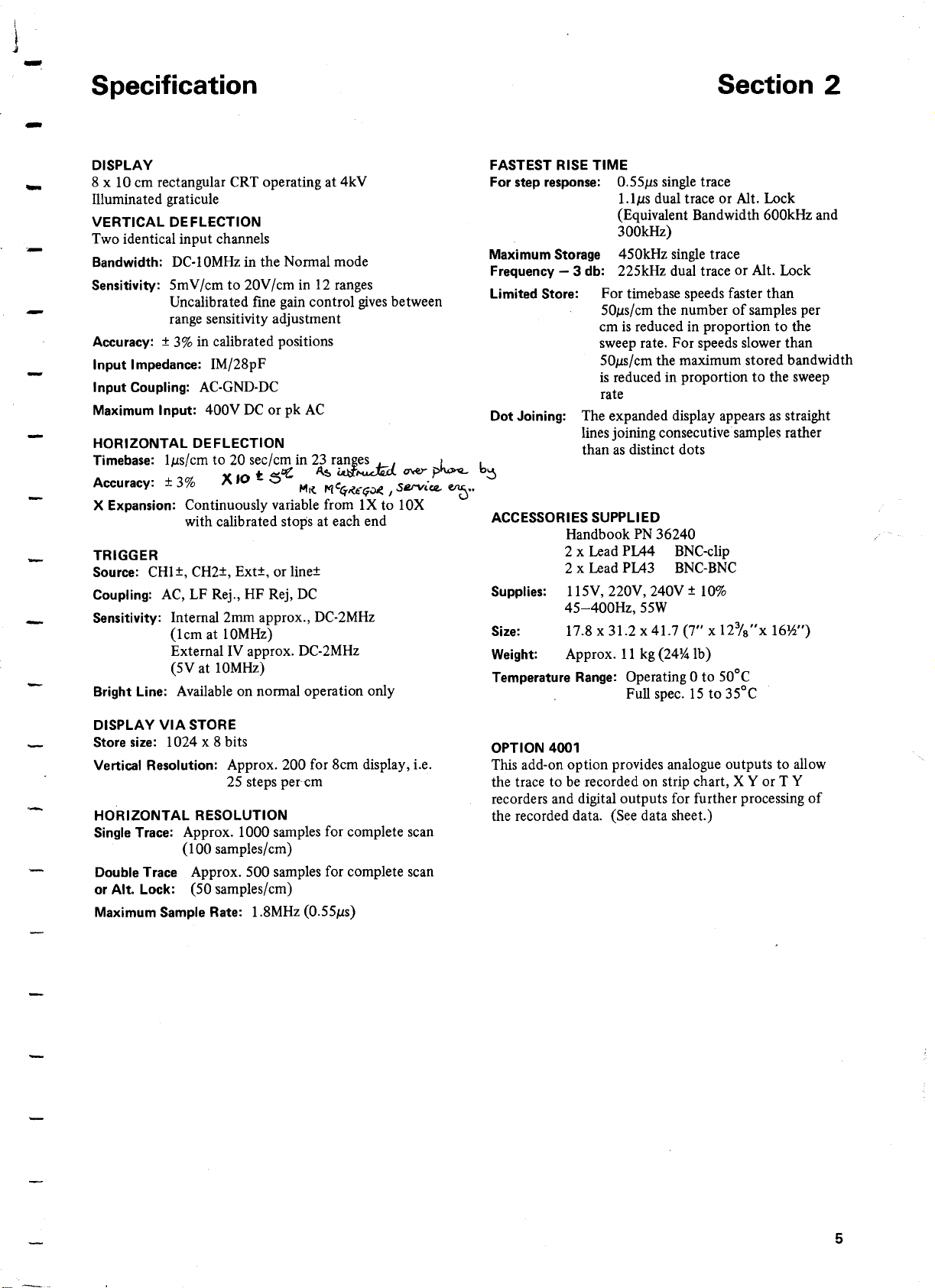

Specification

Section 2

DISPLAY

8 x 10 cm rectangular CRT operating at 4kV

Illuminated graticule

VERTICAL DEFLECTION

Two identical input channels

Bandwidth: DC-lOMHz in the Normal mode

Sensitivity: 5mV/cm to 20V/cm in 12 ranges

Uncalibrated fine gain control gives between

range sensitivity adjustment

Accuracy: ± 3% in calibrated positions

Input Impedance: IM/28pF

Input Coupling: AC-GND-DC

Maximum Input: 400V DC or pk AC

HORIZONTAL DEFLECTION

Timebase: Ills/cm to 20 sec/cm in 23 ranges

Accuracy. - 3%

X Expansion: Continuously variable from IX to 10X

TRIGGER

Source: CHl±, CH2±, Ext±, or line±

Coupling: AC, LF Rej., HF Rej, DC

Sensitivity: Internal 2mm approx., DC-2MHz

Bright Line: Available on normal operation only

. + XJO

with calibrated stops at each end

(lcm at 10MHz)

External IV approx. DC-2MHz

(5Vat 10MHz)

t.s~ ~

"'I{

MCcr~cc;~

iA$~

J-J

a'<er

I SIVV'C/L. ~ ••

k

b

f> ~

FASTEST RISE TIME

For step response:

Maximum Storage 450kHz single trace

Frequency - 3 db: 225kHz dual trace or Alt. Lock

Limited Store: For timebase speeds faster than

Dot Joining: The expanded display appears as straight

ACCESSORIES SUPPLIED

Handbook PN 36240

2 x Lead PL44 BNC-clip

2 x Lead PL43 BNC-BNC

Supplies: Il5V, 220V, 240V ± 10%

45-400Hz, 55W

Size: 17.8 x 31.2 x 41.7 (7" x 12% "x 16*")

Weight: Approx. 11 kg (24% Ib)

Temperature Range: Operating 0 to 50°C

0.551ls

single trace

I.Ills dual trace or Alt. Lock

(Equivalent Bandwidth 600kHz and

300kHz)

SOils/cm

cm is reduced in proportion to the

sweep rate. For speeds slower than

SOils/cm

is reduced in proportion to the sweep

rate

lines joining consecutive samples rather

than as distinct dots

the number of samples per

the maximum stored bandwidth

Full spec. 15 to 35° C

DISPLAY VIA STORE

Store size: 1024 x 8 bits

Vertical Resolution: Approx. 200 for 8cm display, Le.

25 steps per(;m

HORIZONTAL RESOLUTION

Single Trace: Approx. 1000 samples for complete scan

(lOO samples/cm)

Double Trace Approx. 500 samples for complete scan

or Alt. Lock: (50 samples/cm)

Maximum Sample Rate: 1.8MHz

(0.55Ils)

OPTION 4001

This add-on option provides analogue outputs to allow

the trace to be recorded on strip chart, X Y or T Y

recorders and digital outputs for further processing of

the recorded data. (See data sheet.)

Page 5

Operation

Section 3

3.1 SUPPLI ES

The instrument is normally despatched from the factory

with the supply range switch on the rear panel set to the

240V(±10%) range. Check that this is set correctly

before connecting to the supply. Note that the correct

fuse for the two high voltage ranges, 220V and 240V, is

500mA Slo-Blo (20mm) Advance Part No. 33685. If the

115V range is selected the fuse should be changed to a

lA Slo-Blo Advance Part No. 34790.

NOTE:

DO NOT CHANGE THE SUPPLY RANGE SWITCH

WITH THE INSTRUMENT CONNECTED TO THE

SUPPLY.

While the instrument does not rely on forced air

circulation, it should not be operated at elevated

temperatures if the natural connection cooling is

restricted, particularly at the rear of the instrument.

The instrument is switched on by pressing the POWER

button when the associated neon indicator should light.

The button is self locking and the instrument is switched

off by pressing the button agam.

3.2 C.R.T. CONTROLS

These controls are grouped to the right of the c.r.t.

display.

Intensity This is used to set optimum trace intensity

depending on ambient lighting conditions.

Focus Used to obtain finest possible trace width.

Scale The un-illuminated graticule is easily visible

under normal lighting conditions. Graticule

illumination is usually only reqUired under

low ambient light conditions or when photo-

graphically recording the display. The

intensity will depend on the film speed,

aperture and exposure time being used. The

graticule has 0, 10, 90,100% lines marked to

assist in rise time measurement.

3.3 Y CHANNEL CONTROLS

These controls are grouped beneath the c.r.t. display.

The input signal is applied to the CHI or CH2 BNC

input socket.

Coupling

For direct connection of the input signal, set the

associated AC-Ground-DC input iever switch to DC.

For capacitive coupling of the input signal through an

internal O.lpF 400V capacitor, set the lever switch to

AC.

NOTE:

When examining low amplitude a.c. signals super-

imposed on.a high d.c. level, the lever switch should be

set to AC and the sensitivity of the Y amplifier increased.

To locate the baseline, set the lever switch to the 'ground'

setting. At this setting, the input signal is open circuit

and the input of the amplifier is switched to ground.

Sensitivity

Set the VOLTS/CM switch to a suitable setting. To

minimise pick up at sensitive settings, it is essential to

ensure that the ground lead connection is near to the

signal point.

If necessary, adjust the concentric VARIABLE control.

NOTE:

The range of the VARIABLE control is approximately

3.1 so that its.full adjustment overlaps the adjacent

lower sensitivity range. Except at the CAL setting, the

VARIABLE control is uncalibrated. At the CAL setting,

the calibration corresponds to the setting of the VOLTS/

CM switch.

Shift

For vertical shift of the trace, adjust the Y shift controls

(identified with vertical arrows).

Ba!.

The preset balance should be adjusted to minimise

verticle movement of the CHI or CH2 traces when the

inputs are grounded and the attenuator switch is moved

between the 0.5V/cm position and the 0.2V/cm position:

This should only be done after a reasonable warm up

time of say 15 minutes and should only require

infrequent adjustment thereafter.

Y Mode

This three position switch allows single channel display

of the selected channel CHI or CH2, or dual channel

display when CHI&.CH2 is selected.

3.4 TIMEBASE AND TRIGGER

All control~ associated with the Timebase and Trigger

facilities are grouped together on the right hand side of

the panel.

Time/cm, Expand and Shift

The timebase sweep speed (i.e. the time scale of the

horizontal axis) is determined by the setting of the

TIME/CM switch.

X Expand

The time scale can be adjusted to any intermediate

setting by use of the concentric X EXPAND control.

This provides a calibrated sensitivity at the Xl and XIO

detent positions at the ends of travel with a fully

variable uncalibrated range between. The X shift

control, identified with horizontal arrows is used to

centre the display or locate any part of the trace in the

expanded condition. This is a dual action control,

providing fine adjustment over a small angle of rotation

and coarse adjustment over the full rotation.

Trigger

The TRIGGER SOURCE switch selects one of the four

signals, internal CHI, internal CH2, External or line.

The TRIG COUPLING selects wide band DC or AC

coupling.

The AC coupling cuts off at approx. 105Hz.

The L.F. reject position limits the trigger sensitivity

below approx. 15kHz while the HF reject is AC coupled

Page 6

Operation

Section 3

but limits sensitivity above approx. 34kHz. The source

switch also selects the slope, positive or negative going,

to cause trigger when the signal passes through the level

set by the TRIGGER LEVEL control.

The associated L.E.D. indicates when trigger signals are

present. This will flash at low repetition rates and

remain on at faster rates. However it may not indicate

trigger signals above SMHz.

In the Normal mode of operation, the timebase will free

run automatically in the absence of trigger signals.

This provides a "bright line" display to assist in trace

location. With this facility operating, false triggering

may occur if the trigger frequency is less than approx.

40Hz. It is disabled in the Refreshed or Roll modes and

can be disabled in the Normal Mode by pulling the

Trigger Level Knob.

3.5

STORE CONTROLS

All controls associated with the storage facility are

grouped together and distinguished with blue coding.

The DISPLAY MODE lever switch selects the three

modes of operation NORMAL, REFRESHED or

ROLL, the associated L.E.D. indicating the operating

mode.

Normal

In this mode the instrument operates as a conventional

oscilloscope and the store controls do not influence the

display. This mode of operation is available for all

medium and fast sweep rates, O.Ss/cm to IlJ.s/cm, but if

slower sweep rates are selected, the instrument operates

automatically in the Refreshed mode.

Refreshed

If the instrument is displaying a trace in the Normal

mode and the mode switch is moved to REFRESHED,

the display essentially will be unchanged. However in

this mode and in ROLL, the display is generated via the

digital signal path and a small amount of step structure

may be detected on the trace. This is visible in the form

of small vertical steps, less than j6 mm on slow rising or

falling traces. Also with the full X 10 expansion fast

rising or falling traces will appear as a series of sloping

lines (approx. IO/cm in the X direction) rather than as

a smooth curve.

The display is triggered as in the Normal mode but in

the absence of trigger the previously stored trace is

displayed continuously. This has the advantage of

providing a flicker-free display of signals with low

repetition or trigger rates even if a fast sweep is selected.

The display is updated or refreshed by each trigger

signal which would cause a sweep of trace in the Normal

mode. A further advantage over Normal operation is the

availability of very slow sweep rates with continuous

flicker-free display of the sweep as it is written or re-

written.

The Refreshed mode can be used over the full range of

sweep speeds but as the internal sampling rate is limited

to 2MHz, the horizontal sample density decreases in

proportion from the normal lOO/cm when operating at

sweep rates above SOlJ.s/cm.

Roll

Selection of this display mode provides a form of free

running time-base not found on a conventional oscillo-

scop~. Incoming data is fed continuously to the store so

that the display from the store at any instant is a back

history of duration determined by the time/cm speed

control. As the display is continuously updated from

the right, the trace appears to be moving or rolling to

the left similar to the view through a IOcm window of

a strip chart recorder trace.

This mode of display is most suited to direct display of

low frequency signals using comparatively slow sweep

speeds.

As with the Refreshed mode, the Roll mode can be used

on all sweep speed ranges but with limited horizontal

sample density at the faster sweep rates.

Store and Release

These buttons operate in the Refreshed and Roll modes.

Operation of the STORE button in the Refreshed mode

retains any current sweep or the next full triggered

sweep as a stored display, unaffected by subsequent

trigger signals. L.E.D. lamps indicate the single shot

sequence followed. The Armed lamp shows that the

circuitry has been primed by operation of the button.

This lamp goes off and the Triggered lamp comes on

during a sweep. Finally this indication is replaced by

the Stored lamp coming on when the stored sweep is

complete. The sequence and resultant display is similar

to operation of the single shot facility on a conventional

storage oscilloscope after erasing any previous trace. The

OS4000 has no need for an erase facility as the entry of

new data into the store automatically rejects previous

data.

Even in the Stored mode it is possible to use the X

EXPAND control with adjustment of the X shift control

for detailed examination of any part of the trace.

Subsequent operation of the Store button will repeat the

single shot storage cycle, updating the display as

required.

Operation of the Release button will return the

instrument to the Refreshed mode of operation.

Pre-Trigger Storage

The effect of operation of the STORE button in the

ROLL mode depends on the setting of the STORED

TRIGGER POINT SWITCH. With this switch in the top

(End Trace) position, the rolling trace will continue after

operation of the STORE button until a trigger is

received when the display will be frozen. Thus it shows

a full trace of signal prior to trigger, Le. trigger is at the

end of the trace, not at the beginning as on a convention-

al oscilloscope, storage type or otherwise.

Operation of the STORE button at the*trace setting of

the STORED TRIGGER POINT switch allows the

display to roll on for ~ of a sweep beyond the next

trigger. The resultant frozen display shows*of the

trace occuring before trigger and

The actual trigger point on the waveform,*from the

y,.

after trigger.

Page 7

Operation

left hand side of the screen, is shown by a bright-up spot.

It may be necessary to reduce the Intensity setting to

obtain contrast to see this spot.

Selection of thehor

Trigger Point allows the proportion of pre-trigger

display on subsequent storage cycles to be varied

accordingly.

The ability to display a trace of the incoming wave-

form prior to or about trigger, can be used up to sweep

speeds of

For this function, the Roll mode is advantageous on

fast changing signals and at fast sweep speeds. These

present a meaningless display which in the free running

Roll mode but are relevant when stored.

The X EXPAND facility can be used with the X shift

control in this Stored mode for detailed examination of

any part of the trace. It should be noted that the bright-

up dot actually occurs approx. 0.2% of trace before the

actual trigger point and this can be seen as a 2mm

difference on X 10 expand.

The Armed, Triggered and Stored lamps associated with

the STORE button, operate in the Roll mode similarly

to that described for Refreshed. At the End Trace

setting, the triggered state is omitted as the display is

held in the Stored Mode immediately upon receipt of

trigger.

After storage, operation of the RELEASE button will

return the function to Roll. Alternatively further

operation of the STORE button will return the function

to Roll but primed for another storage cycle. In either

case previously stored data has to roll out of the store as

new data is fed in. A new trigger signal will be accepted

only when this mixed display condition has cleared.

Lock Full Store

Operation of the LOCK FULL STORE button prevents

change of the data held in the store. It can be used

usefully in the Roll mode to freeze the display at once

if a feature of interest appears on the screen. Alternat-

ively the store can be locked in the Refreshed or Stored

modes. Subsequently the instrument can be used as a

conventional oscilloscope in the Normal mode but the

original locked display is recalled when returned to the

Refreshed mode. The Lock Full Store button latches

mechanically. To enable the instrument to update the

store as usual the button should be pressed again. An

LED indication warns that the Lock Full Store or Lock

Alternate Samples button is pressed. It should be noted

that movement of function switches after a display has

been locked in the Roll mode, can disturb the display,

particularly shifting the start point of the trace and the

bright up trigger marker spot if relevent. This disturb-

ance is not corrected when the function switch is

returned to Roll.

Lock Alternate Samples

All the store functions described above operate irrespec-

tive of the setting of the 'Y' Mode switch. This is, they

apply equally to the single trace display of CHI or CH2

and the dual trace display of CHI&CH2. This is not

SOJ.Ls/cm,

711

trace position of the Stored

irrespective of the trigger rate.

so for the LOCK ALT. SAMPLES button. When this

condition is applied in the Refreshed mode for single

trace displays (CHI or CH2), the effect is to produce a

dual trace display. One trace is stored and the other

free to follow updating signal inputs. This simultaneous

display of stored and the incoming signal can be used to

compare 'before' and 'now' traces or even to compare

traces taken at different sweep speeds, (once a trace is

stored its display is not altered by the setting of the

Time/cm switch except above

the LOCK ALT. SAMPLES in the dual trace, CHI &

CH2, mode has the effect of freezing the CH2 trace,

leaving CHI free to respond to current signals.

It should be noted that it is possible in this condition to

see a narrow vertical transient appearing on the CH2

trace at the point where the CHI trace is being refreshed.

This effect can be removed by switching from CHI and

CH2 to CHI once CH2 has been frozen.

Once the LOCK ALT. SAMPLES button is pressed, it is

possible still to go from Refreshed to Store and then to

Release to Refreshed with the free trace following the

mode selected, but the frozen trace remaining as when

that lock button was pressed. Operation of the LOCK

ALT. SAMPLES button in the ROLL mode is less

meaningful than in the Refreshed mode. Half of the

display is frozen as before, giving a dual trace effect to

single channel displays or locking CH2 only on dual

trace displays. However the trace continues to move

across the screen from right to left with data lost from

the left appearing at the right.

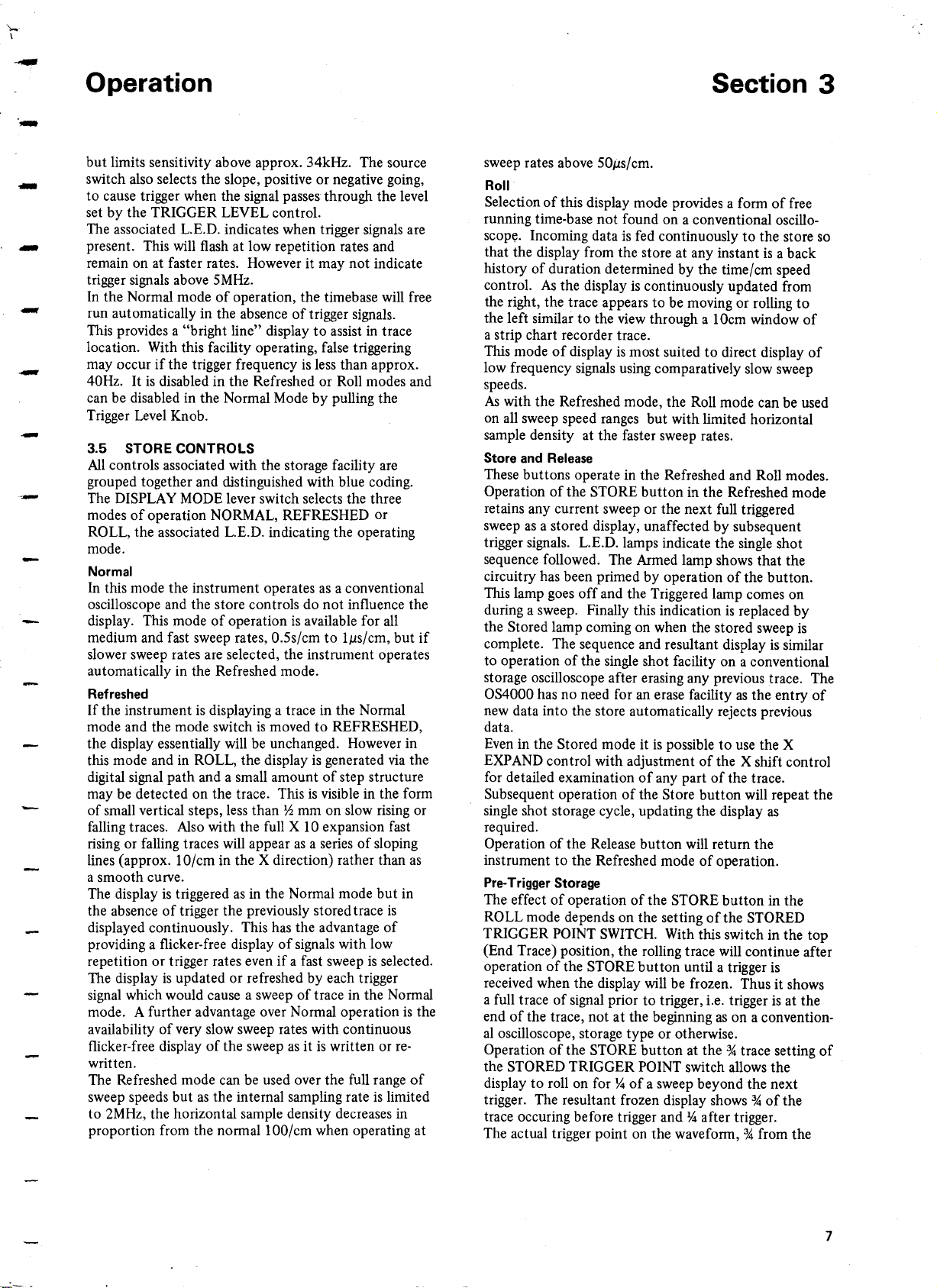

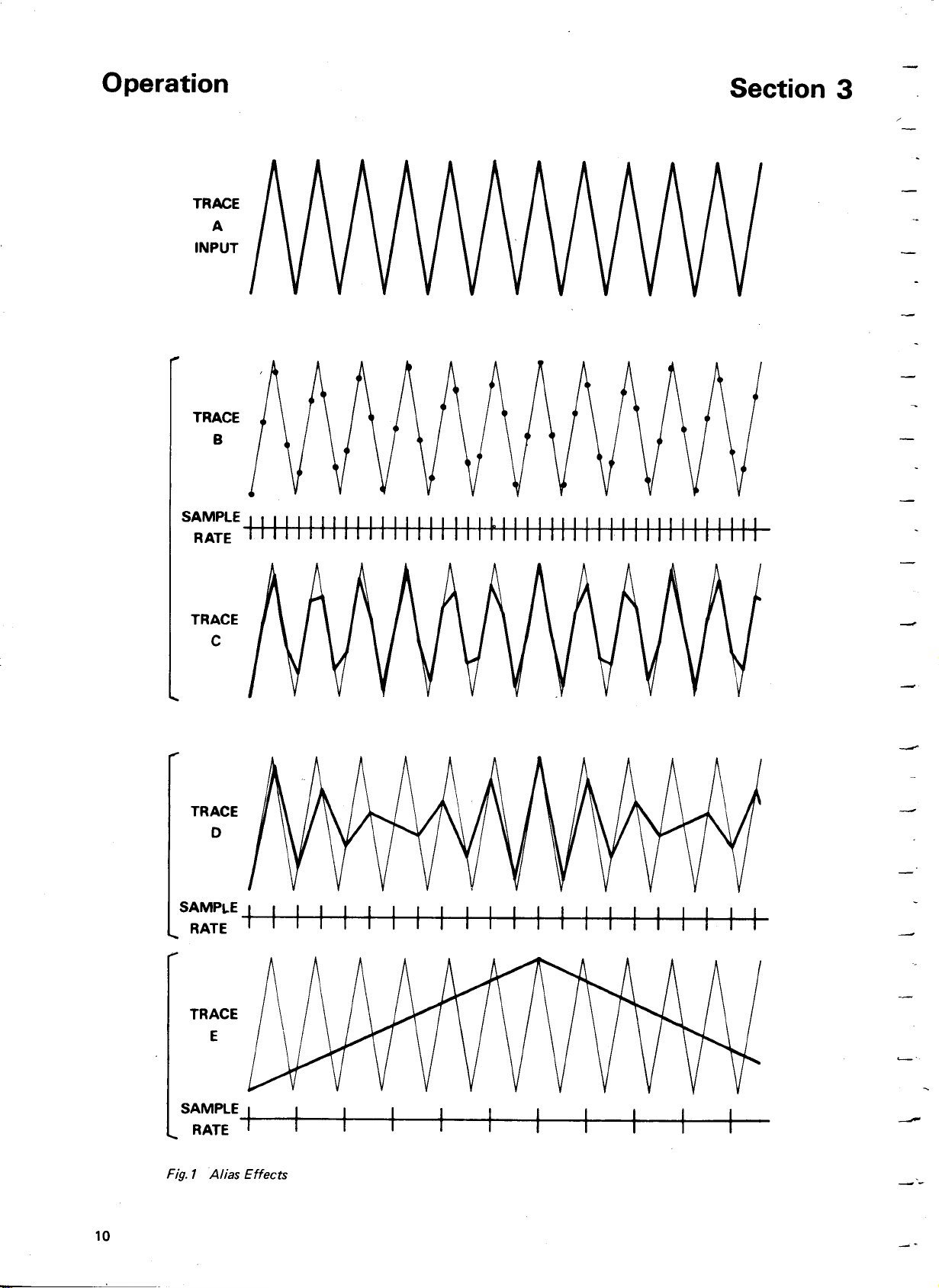

3.6 ALIAS EFFECTS

In the Refreshed and Roll modes, the instrument uses a

sampling system to examine the incoming waveform.

Any such system can give misleading results known as

alias effects if the input signal has a significant

component with a frequency approaching or above the

sampling frequency.

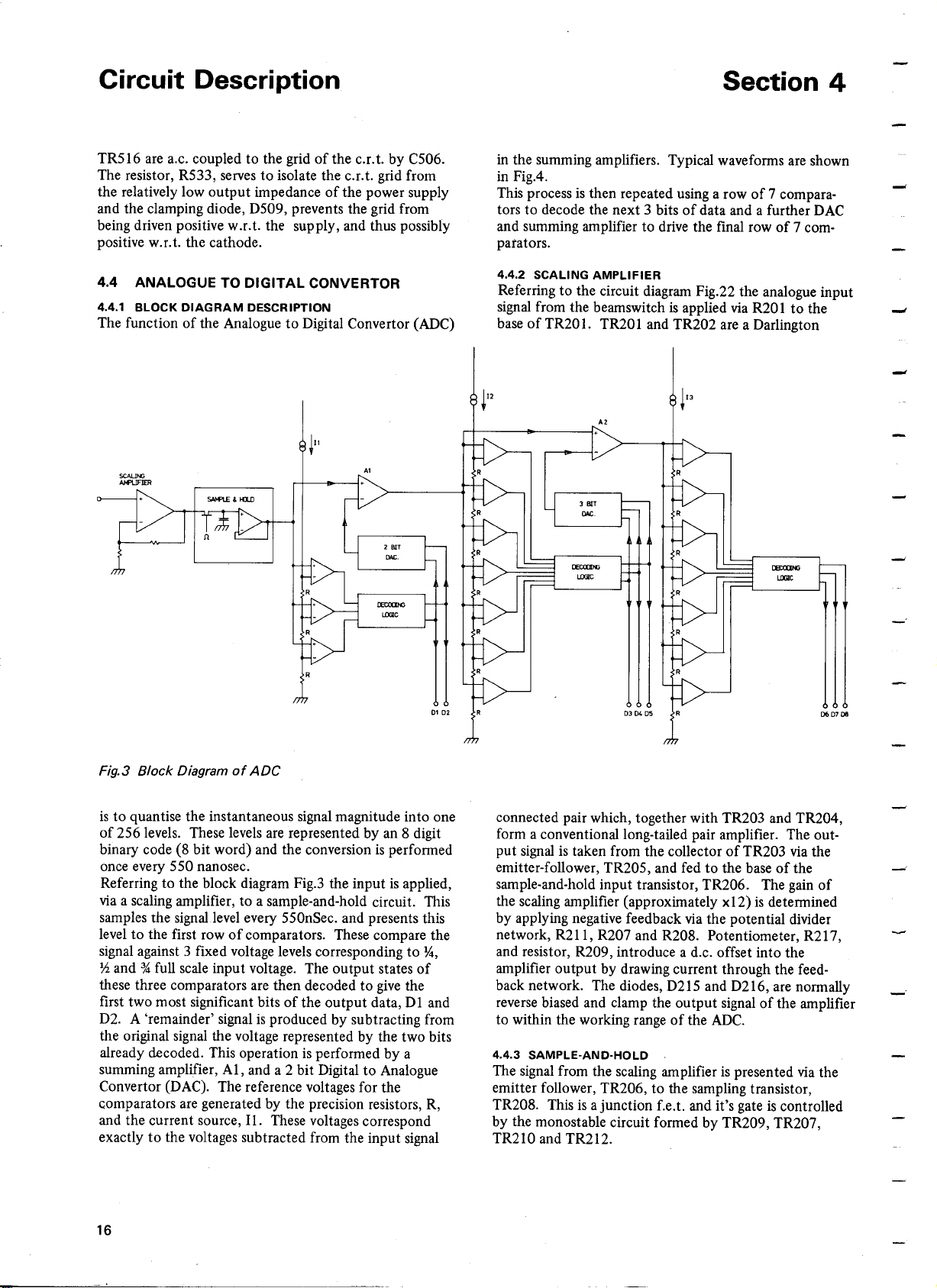

Fig. I shows the effect of the sampling process on a

triangular input waveform (trace A).

Trace B shows the effect of sampling at a frequency

close to four times that of the input if the display is

formed by a series of dots. It will be seen that this can

become a meaningless jumble. However trace C shows

the same sampled waveform reconstructed with the dot

joining system employed in the OS4000. Thus the

display is formed by a series of straight lines, joining the

successive sampled levels rather than a dot at each level,

usually used on reconstructed displays. The dot joining

approach is seen to retain the essential nature of the

input waveform without ambiguity. This is particularly

important as the horizontal dot density is much closer

than that shown on the diagram. However if the

sampling rate is reduced further, the essential nature of

the waveform will be lost. Trace D shows the effect of

a sampling rate close to half the input frequency and

Trace E the effect when the frequencies are nearly equal.

In the latter case the display appears as the input form

but at reduced frequency. The frequency division is the

SOJ.Ls/cm).

Operation of

Page 8

Operation

Section 3

principle on which sampling oscilloscopes operate, and

can cause confusion in this case.

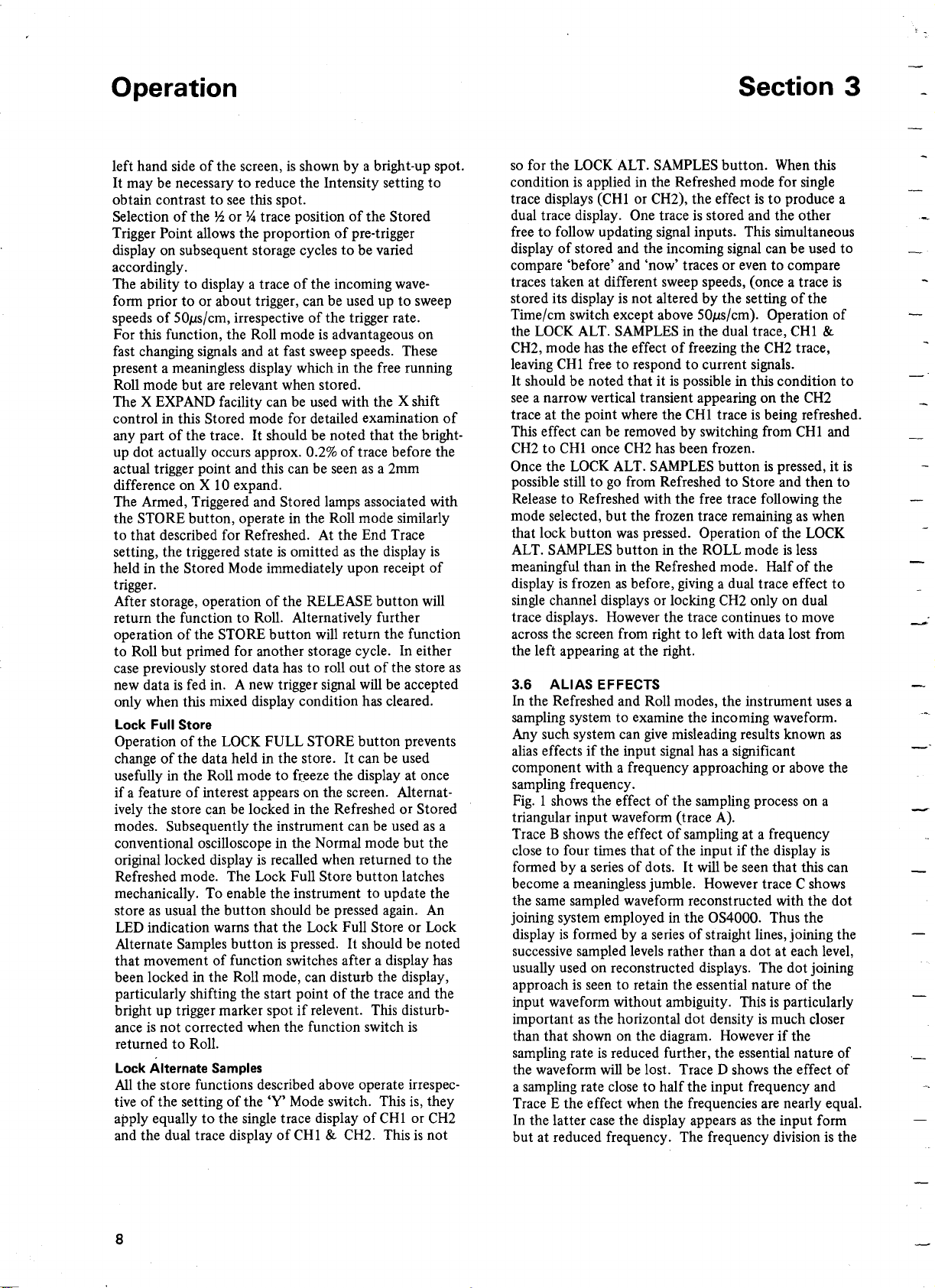

The OS4000 takes approx. 1000 samples per sweep.

These are shared between traces on dual channel or

alternate locked modes of operation. Assuming that the

sampling rate should exceed the input signal frequency

by a factor of between 4 or 5, the following table shows

the maximum frequency which can be viewed on each

range.

Dual Channel

Time/cm Range Single Channel or Alt. Locked

50 Ils/cm 400kHz 200kHz

O.lms/cm 200kHz 100kHz

0.2ms/cm 100kHz 50kHz

0.5ms/cm 40kHz 20kHz

1 ms/cm 20kHz 10kHz

2 ms/cm 10kHz 5kHz

5 ms/cm 4kHz 2kHz

10 ms/cm 2kHz 1kHz

20 ms/cm 1kHz 500Hz

50 ms/cm 400Hz 200Hz

0.1 s/cm 200Hz 100Hz

0.2 s/cm 100Hz 50Hz

0.5 s/cm 40Hz 20Hz

1 s/cm 20Hz 10Hz

2 s/cm 10Hz 50Hz

5 s/cm 4Hz 2Hz

10 s/cm 2Hz 1Hz

20 s/cm 1Hz 0.5Hz

At sweep speeds faster than SOils/cm the sampling rate

remains at 1.8MHz and the storage capability is reduced.

Thus the usable frequency remains at 400Hz or 200kHz.

In practice there is little advantage is using the storage

modes above SOils/cm.

The above table shows the order of frequency which can

cause mis-Ieading displays. The actual amount of

distortion depends on both the frequency and the wave-

shape involved. Individual peaks of sinusoidal signals

can be -3db at a frequency approx. 10% above those

shown above.

If alias effects are suspected, it is recommended that the

fastest possible sweep speed is selected. Repetitive

signals are best viewed in the normal mode if possible,

before comparison with a refreshed trace.

It should be noted also that the sampling system will

not detect narrow transients which occur between

samples.

3.7 ADDITIONAL FACILITIES

Cal

These pins provide d.c. coupled positive-going square

waves of 0.1V and 1V ± 2% amplitude at approximately

1kHz frequency for calibration checks, (2kHz when

Time/cm set SOils/cm or faster). Shorting between the

CAL pins will produce a square current wave-form of

ImA in the shorting link. This can be used for current

probe calibration.

Use of Optional PassiveProbe

A x 10 passive probe may be used to extend the voltage

range and increase the input impedance of the Yampli-

fiers. The input resistance of a Y channel is 1MD

shunted by approximately 28pF. The effective capacity

of the input lead must be added to this and the resultant

impedance will sometimes load the signal source. There-

fore it is advisable to use a lOMD, x 10 probe. This

reduces the input capacity and increases the input

resistance, at the expense of the sensitivity. The probe

contains a shunt RC network in series with the input,

and forms an attenuator with the input RC of the Y

channel. To obtain a flat frequency response it is

necessary to adjust the capacitance of the probe to

match the input capacity of the Y channel as follows:-

1. In the Normal Mode, set the Y channel VOLTS/CM

switch to 20mV/cm, and the TIME/CM switch to

.2ms/cm.

2. Connect the probe to the CAL 1V pin.

3. Set the adjustable capacitor in the probe tip or

termination with a small screwdriver for a level

response with no overshoot or undershoot visible

on the display.

3.8 FUNCTIONAL CHECKS

This section describes a test routine which checks that

the instrument is functioning correctly in its main modes

of operation, but it also provides examples of how to set

and use the instrument.

Normal Mode

Switch on, put Display Mode switch to normal.

Put timebase switch to Ims/cm; CHI and CH2

attenuators to 0.2V/cm; Trigger Lever Control knob

pushed in; CHI, CH2 and X shift controls central;

Y Mode switch to CHI

switches to GND; Trigger source switch to CHI; Trigger

Coupling to A.C.

Turn Intensity control to clockwise end. Adjust CHI

and CH2 shift controls to obtain two traces. Adjust

Intensity and Focus control to obtain finest possible

traces.

Rotation of the Trigger Level control through the

central position will cause trigger L.E.D. to flash once.

After about 15mins. warm up, check that on both

channels the vertical trace movement caused by turning

the attenuator switches from 0.2V/cm to 0.5V/cm is less

than 0.5cm. If not adjust the BAL. pre-set for that

channel. Set input coupling switch to DC.

Apply sine wave at approx. 1kHz to CHI and select

CHI as trigger source. Adjust CHI attenuator and/or

signal amplitude to give about 5cm Y deflection. Adjust

level control to obtain stationary trace - check trigger

L.E.D. is illuminated. Pull out Trigger level control to

disable Bright Line facility and turn until trigger is lost;

trace should disappear. Trace should re-appear free

running when Level control is pushed in. Reset Level

control for stationary trace.

&

CH2; Input coupling

Page 9

Operation

TRACE

INPUT

TRACE

SAMPLE

RATE

Section 3

A

B

TRACE

C

TRACE

o

SAMPL.E

RATE

TRACE

E

SAMPLE

RATE

Page 10

Operation

Section 3

Refreshed Mode

Apply approx. 1kHz with the timebase on the O.5ms/cm

range. Obtain a stable display. Switch the Display mode

to Refreshed. The Display is now being obtained from

the store. Removal of the signal by disconnecting the

input or switching the input coupling switch to the CND

will cause the last "sweep" to be preserved in the store

and displayed indefinitely. This sweep may include the

break of signal. Apply a 1 to 10Hz sine wave and adjust

the timebase range switch accordingly. Adjust the level

control to light the trigger L.E.D. The refreshing sweeps

through the store can be clearly seen as the time base

range is switched up or down.

Store

If the signal is removed and the Store button pressed, on

re-applying the signal the sequence-trigger-store can be

followed by watching the status indicators, and the store

will have been completely updated when the store

L.E.D. is lit. The sequence may be repeated by pressing

the Store button again.

Lock Full Store

Select CHI only, with CHI as trigger source. Apply

approximately 1kHz signal and adjust the Trigger Level

so that refreshing sweeps are occuring. Push Store

button and when the store L.E.D. is lit, push the Lock

Full Store button. On returning the Display mode

switch to the normal position, conventional oscilloscope

operation is possible - Le. the input attenuators and

time base range can be altered, another signal can be

observed, but on returning the mode switch to the

Refreshed position, the original stored display will be

obtained, irrespective of the current input and setting of

the sensitivity and sweep speed controls

slower). Release the Lock button.

Lock Alt. Samples

With the display mode switch in the refreshed position

again, apply the same signal as before and adjust trigger

level to obtained refresh sweeps. Store the trace then press

the Lock Alt. Samples button. On returning to the

refreshed mode (pushing Release button) it will be

found that operating the CHI shift control, results in

two traces being generated - one which responds to the

input signal, shift, attenuator and timebase controls, the

other a fixed display of the original store contents. On

uplatching the Lock ALT. Samples button a single trace

is again displayed.

(SOils/cm

or

Select CHI & CH2 (Dual trace), CHI trigger, and

apply approximately 1kHz signals to CHI and CH2.

Adjust trigger level so that refresh sweeps are occuring.

Push Store button and wait for store L.E.D. to light. If

the Lock Alt. Samples button is operated on returning

to the refreshed mode, one trace (CHI) will respond to

the CHI shift and input signal, the other trace (CH2) is

locked. Returning to the normal mode will not destroy

the CH2 information held in the store until the Lock

Alt. Samples button is un-latched.

Roll Mode

Switch display mode to Roll. Select a low sweep speed

such as 1 sec/cm. Select CHI only. Offset trigger level

to one end, and check Hold and store L.E.D.'s are off.

Movements of the CHI shift control will now be seen to

draw a trace on the screen similar to a strip chart

recorder, with the "pen" at the right hand side of the

screen, and the trace moving towards the lift at the

sweep speed selected. This movement can be arrested at

any time by pressing the Full Lock button.

Pre-trigger Storage

Apply a low frequency signal of approximately 1Hz and

with trigger coupling in the D.C. position adjust the

trigger level control until the trigger source L.E.D.

flashes continuously. The display will continue to move

to the left. Remove the signal and press the Store

button. On re-applying the signal the sequence,

triggered-stored will be followed resulting in a stationary

display. The length of time spent in the triggered

condition and therefore the final waveform position is

dependent upon the setting of the stored trigger point

switch, and can be changed from zero to three quarters

of the full sweep time. At normal to low settings of the

brilliance control a bright dot can be observed marking

the point of trigger (it is displaced approximately 0.2 cm

on XIO expansion to the left of the true trigger point).

After a stationary display has been obtained, if the signal

is not removed, but its frequency is changed by say 2: 1,

on pressing the store button again, the sequence,

triggered-stored will be followed, resulting in a stationary

display again. It will be found that the new display

contains none of the "old" frequency, because the

store will automatically take in just enough new

information before becoming sensitive to trigger such

that the next stored waveform consists of new

information entirely.

Page 11

Circuit Description

Section 4

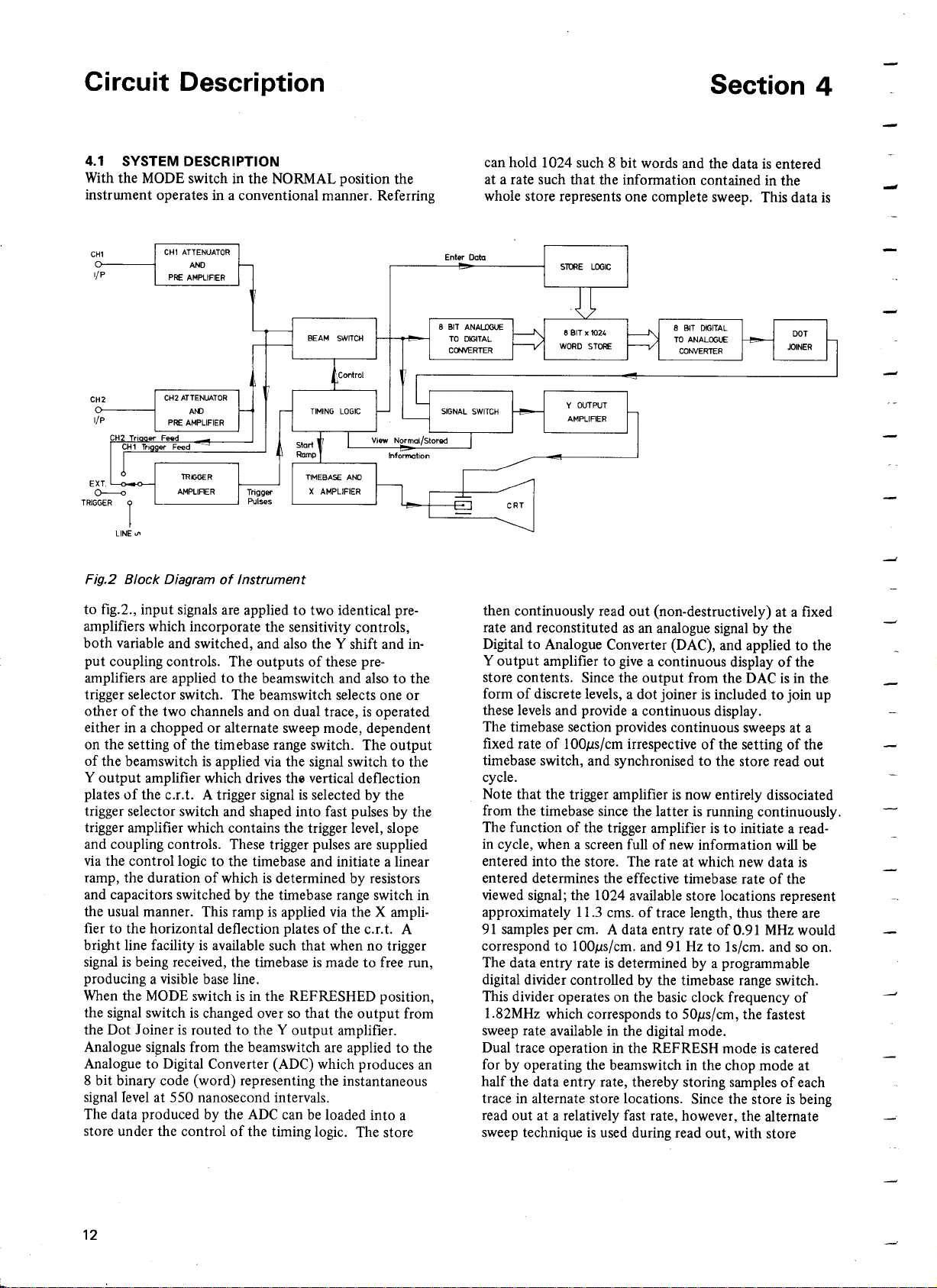

4.1 SYSTEM DESCRIPTION

With the MODE switch in the NORMAL position the

instnnnent operates in a conventional manner. Referring

CH' CH' ATTENUATQR

'ip PRE AMPLIFIER

CH2 CH2 ATTENUATOR

!/p

AND

AND

PRE AMPLIFIER

TRGGER

AMPLlRER

can hold 1024 such 8 bit words and the data is entered

at a rate such that the information contained in the

whole store represents one complete sweep. This data is

to fig.2., input signals are applied to two identical pre-

amplifiers which incorporate the sensitivity controls,

both variable and switched, and also the Y shift and in-

put coupling controls. The outputs of these pre-

amplifiers are applied to the beamswitch and also to the

trigger selector switch. The beamswitch selects one or

other of the two channels and on dual trace, is operated

either in a chopped or alternate sweep mode, dependent

on the setting of the timebase range switch. The output

of the beamswitch is applied via the signal switch to the

Y output amplifier which drives the vertical deflection

plates of the C.r.1. A trigger signal is selected by the

trigger selector switch and shaped into fast pulses by the

trigger amplifier which contains the trigger level, slope

and coupling controls. These trigger pulses are supplied

via the control logic to the time base and initiate a linear

ramp, the duration of which is determined by resistors

and capacitors switched by the time base range switch in

the usual manner. This ramp is applied via the X ampli-

fier to the horizontal deflection plates of the c.r.t. A

bright line facility is available such that when no trigger

signal is being received, the timebase is made to free run,

producing a visible base line.

When the MODE switch is in the REFRESHED position,

the signal switch is changed over so that the output from

the Dot Joiner is routed to the Y output amplifier.

Analogue signals from the beamswitch are applied to the

Analogue to Digital Converter (ADC) which produces an

8 bit binary code (word) representing the instantaneous

signal level at 550 nanosecond intervals.

The data produced by the ADC can be loaded into a

store under the control of the timing logic. The store

then continuously read out (non-destructively) at a fixed

rate and reconstituted as an analogue signal by the

Digital to Analogue Converter (DAC), and applied to the

Y output amplifier to give a continuous display of the

store contents. Since the output from the DAC is in the

form of discrete levels, a dot joiner is included to join up

these levels and provide a continuous display.

The time base section provides continuous sweeps at a

fixed rate of lOOlls/cm irrespective of the setting of the

timebase switch, and synchronised to the store read out

cycle.

Note that the trigger amplifier is now entirely dissociated

from the timebase since the latter is running continuously.

The function of the trigger amplifier is to initiate a read-

in cycle, when a screen full of new information will be

entered into the store. The rate at which new data is

entered determines the effective time base rate of the

viewed signal; the 1024 available store locations represent

approximately 11.3 cms. of trace length, thus there are

91 samples per cm. A data entry rate of 0.91 MHz would

correspond to 100Ils/cm. and 91 Hz to Is/cm. and so on.

The data entry rate is determined by a programmable

digital divider controlled by the time base range switch.

This divider operates on the basic clock frequency of

1.82MHz which corresponds to SOils/cm, the fastest

sweep rate available in the digital mode.

Dual trace operation in the REFRESH mode is catered

for by operating the beamswitch in the chop mode at

half the data entry rate, thereby storing samples of each

trace in alternate store locations. Since the store is being

read out at a relatively fast rate, however, the alternate

sweep technique is used during read out, with store

Page 12

Circuit Description

Section 4

locations relevant to one trace being read out on one

sweep, and the remaining location on the next sweep.

The STORE control provides a conventional single shot

facility to enter one triggered sweep of data into the store,

while the LOCK STORE controls inhibit immediately

the entry of any new data.

The ROLL mode of operation is similar to the

REFRESHED mode except in the way in which new

data is entered into the store. Instead of waiting for a

trigger pulse to initiate a new data input cycle, data is

continuously entered into the store. Thus, if data entry

is made to stop on receipt of a trigger pulse, the contents

of the store will be information stored before the trigger

pulse, rather than after it as in a conventional trigger

sequence. To expand this facility, which operates only

in conjunction with the single shot store controls, a

switched delay is incorporated marked STORED

TRIGGER POINT which allows the input of new data

to continue after a trigger is received, for a time corres-

ponding to ~, ~ or%of the store length. This allows the

amount of pre-trigger and post trigger information

retained in the store to be varied to suit the application.

Circuit References

Each component in the instrument is specified by a

circuit reference consisting of a letter prefix and a

number. The number also indicates which printed

circuit board assembly the component is mounted on

as shown below:-

Circuit Reference No.

o -

99 Main Frame Components

100 - 399 Analogue to Digital Converter

Assembly

400 - 499

500 - 599

600 -699

700 - 799

800 - 899

900 - 1099 Timebase Board.

The location of the various assemblies is shown in

Figs.14, 15 and 16.

4.2.1

GENERAL

Referring to Fig.20 all the power supplies for the

instrument are derived from the transformer, TS1. Two

tapped primary windings are switched by SS2 to allow

for three supply voltage ranges and fuse FSS1 provides

fault protection. The supply indicator neon, NE 51, is

supplied via limiting resistor RS8 from the 115 volt tap

on the transformer.

4.2.2

LOW VOLTAGE SUPPLIES

Five separate secondary windings supply bridge rectifiers,

BRS1-BRSS, mounted on the transformer and provide

unregulated supplies of +170V, +26V, -26V, +18V,

-lOV and +8V across the reservoir capacitors, CS09A,

E.H.T. Board

Power Supply Board

Store Logic Board

Timing Logic Board

Output Unit 4001 - Fitted as

an option. See separate handbook

for details.

CS10, CS11, CS12, CS02 and CS1 , respectively. Note

that the -10V and +8V supplies are floating with respect

to ground due to the action of the regulators. The +170V

supply is further smoothed by RS40 and CS09B and

protected by fuse, FSS01. The + 26V, -26V, + 18V and

-10V supplies are fed to high performance integrated

circuit regulators, ICS03, ICS04, ICS01 and ICS02

respectively to provide stabilised lines of +20V, -20V,

.+12Vand -6V. These devices contain all the circuitry

necessary for a conventional series regulator, together

with current limiting and thermal shutdown facilities to

protect the device against overloads arising from short

circuits, etc. Note that the two 20V lines are in fact

provided by lSV regulators in conjunction with zener

diodes, DS03 and DS04.

The +8V supply feeds a discrete series regulator com-

prising transistors, TRSOS-TRS10, and associated

components, to provide a stabilised +SV line. The long

tailed pair, TRSOS and TRS06, compares the output

voltage with the voltage across the zener diode, DSOS,

and provides an error signal which is passed via the

emitter follower, TRS09, to the series pass transistor,

TRS10. A second long tailed pair, TRS07 and TRS08,

senses the voltage drop across the current sensing

resistor, RS22, and if the supply current rises above

3 amps will shut down the regulator by reducing the

reference voltage at the base of TRSOS. The resistor

network, RS18, RS17 and RS20, determines the

limiting current and also provides a 'foldback' limiting

characteristic by reducing the permissible output current

of the regulator as the output voltage falls. This prevents

excess dissipation in the series pass transistor under short

circuit conditions. The zener diode, DS06, prevents the

output voltage of the regulator rising excessively high

under fault conditions and thus protects from damage

the integrated circuits supplied from this line.

4.2.3 E.H.T.

The two remaining secondary windings are associated

with the cathode ray tube (c.r.t.) supplies. The 6.3V

winding feeds the c.r.t. heater and the 850 volt winding

provides the -lkV and the +3kV supplies. Stabilisation

of both lines against supply voltage variations is achieved

as follows. One end of the 8S0V winding feeds the

rectifier diodes in the normal manner, the other end

passes to ground via a bridge rectifier, BR401. The alter-

nating current in the winding passes through R406 and

TR402 as direct current developing a steady voltage

across C402. This voltage, controlled by the conduction

of TR402, is effectively subtracted from the peak voltage

available at the 'hot' end of the winding and thus by

varying the base-emitter voltage of TR402, the rectified

high voltage supplies can be controlled. The average value

of the base-emitter voltage of TR402 is established by the

voltage at TR403 emitter. This in turn is controlled by

the voltage at TR403 base set by the feedback resistor, R411,

from the -lkV supply line and the combination of R409

and R41O, thus establishing a closed feedback loop. A

small current also flows from the base of TR403 via R407

SUPPLIES

Page 13

Circuit Description

Section 4

to the unregulated -26V supply. Since this voltage

changes with the line voltage, this trims out any remaining

fluctuations in the E.H.T. supplies due to supply variations.

The -lkV supply is derived by the diodes, D404, D405

and D406, feeding the reservoir capacitors, C404, C407

aqd C406. The voltage is smoothed by R413, R414 and

C405, C408 and C409 and applied to the grid of the c.r.t.

The cathode potential of the tube is held positive w.r.t.

the grid as determined by the brilliance control, R419,

and the second anode potential is set by R416 to opti-

mise the focus. Small positive voltages set by R417 and

R408 are applied to the third anode and interplate shield

to minimise raster distortion.

4.2.4

GRATICUlE IllUMINATION

The graticule is illuminated by two lamps, ILPI and ILP2.

The supply for these lamps is derived from the emitter

follower, TR401, and controlled by the potentiometer,

R402. This circuit is supplied from the 8 volt winding

of the transformer via diodes, D53 and D54.

4.2.5

THE TRACE ROTATION COil

A coil, L51, fitted round the neck of the C.r.t. inside the

magnetic shield, is used to align the trace with the

horizontal graticule lines. The current for this coil is

taken from the pre-set potentiometer, R529, through

R530 on the power supply board. The direction of

rotation can be reversed by interchanging the coil

connections at the power supply board.

4.3.1

THE Y PRE-AMPLlFIER

The attenuator and pre-amplifier in Channel I are

identical to those in Channel 2. Accordingly only

Channel I will be described. Referring to Fig.21 the

input signal is applied to the front panel socket, SKY,

and then to the 3 position lever switch, SI, via R22.

This switch selects AC or DC inpuLcoupling by including

or by-passing C20 in the signal path. On the middle

position of the switch, the input socket is disconnected

and the input to the amplifier is connected to ground.

Input sensitivity selection is performed in two stages; the

six lowest ranges, 5-200mV/cm, are obtained by switch-

ing the gain of the amplifier as described later. The 0.5-

20V/cm ranges are provided by switching in a -;.-100

attenuator section before the amplifier and repeating the

gain switching. This attenuator is formed by R24 and

R351 with C305 to set the hJ. response. C303 is adjusted

to maintain the total input capacitance of the highest

ranges equal to the lower ranges. Diodes, D301 and D302,

limit the peak signal voltage at the amplifier input to

approximately 8 volts and in conjunction with R26,

protect the instrument against damage from inputs of up

to 400 volts peak.

The input stage consists of the field effect transistor,

TR30 I, connected as a source follower driving the emitter

follower, TR305, via R303. The operating current of

TR30 I is defined by TR302 which is an identical transis-

tor mounted in a common package with TR301 to ensure

close matching and good thermal tracking. TR302 is self

biased such that the operating current will develop a

voltage across R308 equal to the gate-source potential.

Since this same current flows in TR301 and R303 is

identical to R308, the voltage at the base of TR305 is

equal to the gate voltage of TR30 1. The drain-source

voltage of TR301 is maintained constant by 'boots-

rapping' with TR304 and D303. The drain-source

voltage of TR302 is also maintained constant by the

cascode transistor, TR303. Diode, D304, prevents the

base-emitter junction of TR305 becoming reverse biased

under overdrive conditions. The voltage at the gate of

TR302 can be varied by R373 to balance out small

variations in matching characteristics.

The signal at the emitter of TR305 is applied via the

switched resistor network, R28/34, and the common

base stage, TR306, to the shunt feedback amplifier

formed by TR307, R312 and R311. This can be

regarded as a 'virtual earth' amplifier with R311 as the

feedback resistor and the R28/R34 network as the input

resistor. Thus, the overall gain of the stage is selected by

S3B to provide the six basic input sensitivities of the

instrument. The common base transistor, TR306, is

interposed to balance the d.c. offset voltage introduced

into the signal path by TR305. Diode D305 is fitted to

protect TR306 from reverse base-emitter voltages. The

output from the collector of TR307 is taken via R315 to

the base of TR309, which, together with TR31O, forms

a long-tailed pair. Transistors, TR315 and TR308, are

connected in a similar fashion to TR306 and TR307 and

provide a balancing d.c. voltage at the base of TR31O.

The mutual conductance of the long-tailed pair is deter-

mined by series combination of R319, R320 and R3.

Resistor, R3, is the variable sensitivity control and is

shorted by S13 when in the 'CAL' position. The preset

potentiometer, R319, sets the overall gain of the pre-

amplifier and C309 provides h.f. compensation.

Movement of the displayed trace will occur when the

variable sensitivity control, R3, is operated unless the

voltages at the emitters of TR309 and TR31 0 are equal

(except for the input signal) and this balance is set up

using potentiometer, R369. The collector current of

TR309 feeds into a load resistor on the time base board

to provide an internal trigger signal.

4.3.2

BEAM SWITCH

The collector current from TR310 is passed through a

cascode transistor, TR317, to the emitter of the beam

switch transistor, TR319. A d.c. current determined by'

the shift control potentiometer, RI, and the series resistor,

R387, is injected at the emitter of TR317 to provide a

shift range of ±12 cms. If the base of TR319 is held high

(approx. 3.3 volts) the signal current will pass through the

forward biased diodes, D313, D315 and D316, to the load

resistor, R389. If the base voltage of TR319 is low

(approx. 0.4 volts) the signal current will flow through

TR319 to ground and D313 will become reverse biased

isolating Channel I from the common load resistor, R389.

An identical beam switch circuit controls the output of

Page 14

Circuit Description

the Channel 2 pre-amplifier but the drive to transistor,

TR320, is the complement of that to TR319.

For dual trace operation the beam switching technique

employed depends upon the main operating mode switch.

In the NORMAL mode the channels are switched on

alternate sweeps when the time base range switch is set

to 2 msec./cm. or faster. On the lower timebase ranges

the beam is chopped at a 225kHz rate. In the

REFRESHED and ROLL modes the channels are always

chopped at a rate dependent on the setting of the time-

base range switch. On the 50p.sec./cm ranges and above,

the chopping rate is 0.9MHz; below this the chopping

rate decreases pro rata Le. at 5msec./cm, it is 9kHz and

at 5 seconds/cm. it is 9Hz.

4.3.3

SIGNAL SWITCH

The combined input from both channels appears across

R389 at a level of approximately 37mV/cm. This signal

is taken via R201 to the Analogue to Digital convertor

(section 4.4) and also via emitter follower, TR321, to

the signal switch formed by diodes, D317 to D320.

This determines whether the signal passed to the Y out-

put stage is the direct signal from the pre-amplifiers

(NORMAL mode) or the stored signal from the Digital

to Analogue convertor (REFRESHED and ROLL modes).

In the NORMAL mode, transistor TR324 is turned off

and its collector is at a high level thus turning TR325

fully on. The voltage at the junction of diodes D319

and D320 will be low and both diodes will be reverse

biased. The two diodes, D31 7 and D318, will be forward

biased and conducting however, and a signal at the

emitter of TR321 will be transferred to the junction of

D318 and D319, and via R379 to the Y output stage.

When a high level is applied via R362 to the base of

TR324, this transistor is turned on, TR325 becomes cut

off and the situation is reversed with D317 and D318

reverse biased and the signal from TR322 emitter trans-

ferred to the output stage. The stored signal from the

Digital to Analogue convertor is applied via R355 to the

base ofTR322. To compensate for the dc level shift

introduced into the signal path by the emitter followers,

TR321- TR322, a bias supply is provided for the output

stage by transistor, TR323, which is operating under

quiscent conditions identical to transistors, TR321 and

TR322. The collectors of all these three transistors are

supplied via R391 and clamped by D321 to approximately

-0.7V in order to reduce dissipation in the devices.

4.3.4 Y

OUTPUT AMPLIFIER

The Y output amplifier shown in Fig.20 is a conventional

two stage differential amplifier. Input signals from the

signal switch are applied via SK.U to the base of TR409

and a bias signal at the same d.c. level (approx. +0.6 volt)

is fed to the base of TR408. These two transistors form

a long-tailed pair with the gain determined by the resistor

combination, R437 and R438, in conjunction with the

collector load resistors, R441 and R442. The two

resistor-capacitor combinations, R443, C424, C426 and

R448, C430 provide pulse response correction. The

zener diodes in the collectors, D411 and D412, set the

collector-emitter voltage across each transistor so that

variations in-power dissipation (and hence junction

temperature) of the transistor with signal amplitude, are

minimised. The output signal from this stage is applied

to the bases of a second long-tailed pair, TR406 and

TR407, which are connected in cascode configuration

with TR404 and TR405, respectively.

The c.r.t. deflection plates are driven from the collectors

ofTR404 and TR405 with inductors,

UOl

and

U02,

providing shunt compensation. The networks, C419,

C420, R425 and C421, R427 across the gain setting

resistors, R426 and R435, provide h.f. compensation to

ensure good pulse response.

4.3.5

BLANKING AMPLIFIERS

There are two separate blanking amplifiers producing

intensity modulation of the c.r.t. display and these

operate with three separate input signals viz:

i) The Sweep Blanking signal. This cuts off the beam

except when a time base sweep is in progress.

ii) Chop Blanking. This is a short duration blanking

pulse applied in the NORMAL mode only when the

beamswitch is being switched from one channel to

the other at the fast chopping rate.

iii) Trigger Point Bright-Up. This is a short duration

bright-up pulse applied once per sweep when a

trace has been stored in the ROLL mode of

operation.

The Sweep Blanking signal is amplified by a d.c. coupled

amplifier comprising TR513 and associated components.

The sweep blanking signal is derived from a TTL. logic

gate (IC902a) in the timebase via R971 (see Fig.24).

When no sw.eep is in progress the sweep blanking signal

is at a low level «0.4 volt) and transistor TR513 is cut

off. The collector voltage in this condition is determined

by the resistor chain, R526, R527 and R528, at approx.

90 volts. This voltage is applied to the second grid elec-

trode (blanking electrode) of the c.r. t. and the beam is

cut off.

When a sweep is initiated the sweep blanking input from

the timebase rises to a high logic level (approx. 4 volts)

turning on transistor TR513. The base drive to this

transistor is limited by D507 becoming forward biased

to avoid saturating the transistor and the collector

voltage falls to 4 volts, thus unblanking the C.r.t. beam.

The remaining two input signals are amplified by the

circuit comprising TR514, TR515 and TR516. Both

the Chop Blanking (CB) and Trigger Bright-Up (TBU)

signals are produced by TTL logic devices situated on

the Timing Logic board and the Store Logic board

respectively (see Fig.23). For detailed information on

the timing of these signals see section 4.5

The Trigger Bright-Up signal is inverted by the common

emitter stage, TR514, and applied to the base ofTR515

via R508. The Chop Blanking signals are applied directly

to the base of TR515 via R507 and the speed-up capacitor,

C505. The signal at the collector ofTR515 is fed to the

base of TR516 via the d.c. level-shifting network, D508

and C519. The pulses occurring at the collector of

Page 15

Circuit Description

Section 4

TR516 are a.c. coupled to the grid of the C.r.t. by C506.

The resistor, R533, serves to isolate the c.r.t. grid from

the relatively low output impedance of the power supply

and the clamping diode, D509, prevents the grid from

being driven positive w.r. 1. the supply, and thus possibly

positive W.r.t. the cathode.

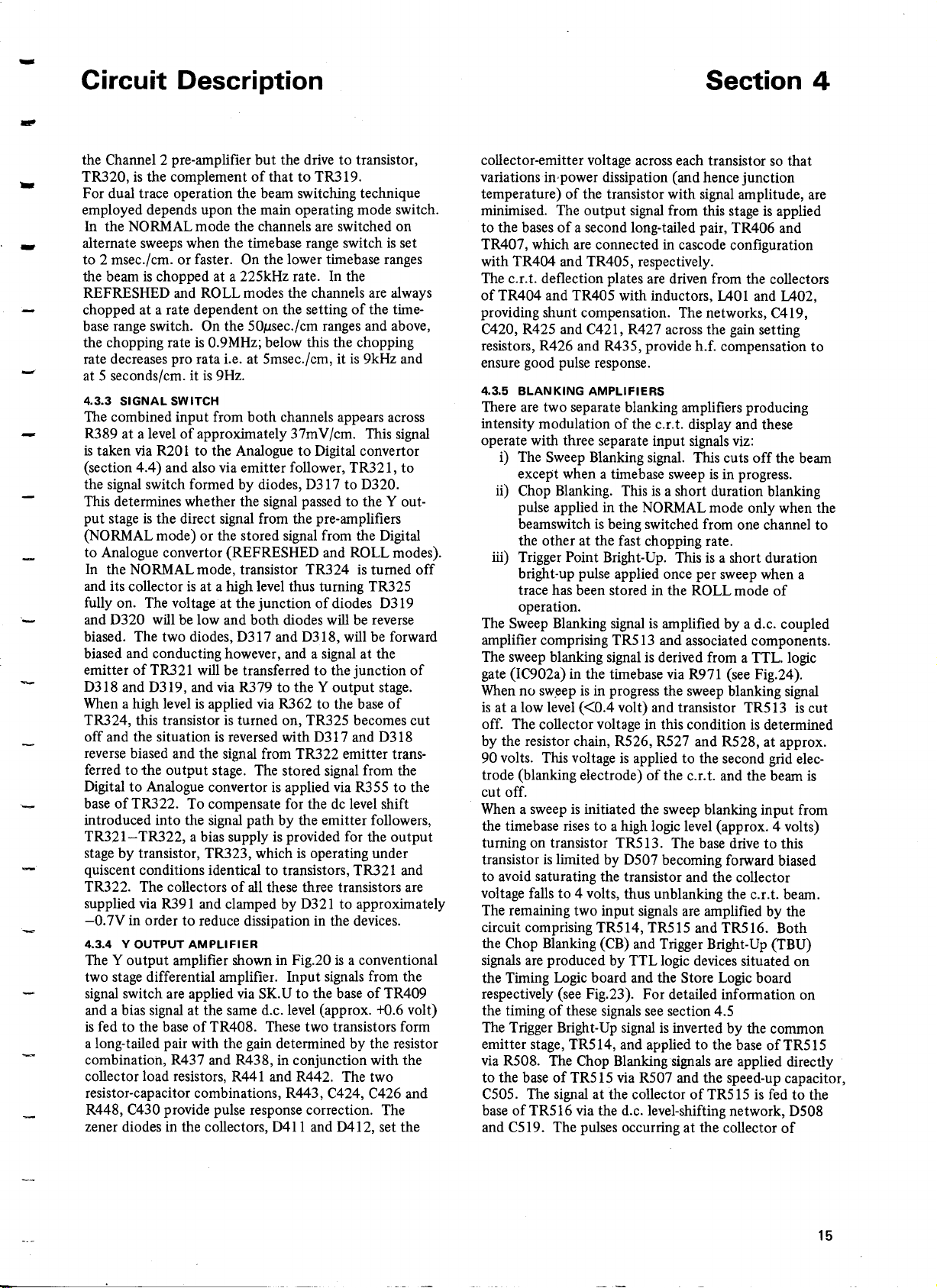

4.4.1

BLOCK DIAGRAM DESCRIPTION

The function of the Analogue to Digital Convertor (ADC)

in the summing amplifiers. Typical waveforms are shown

in Fig.4.

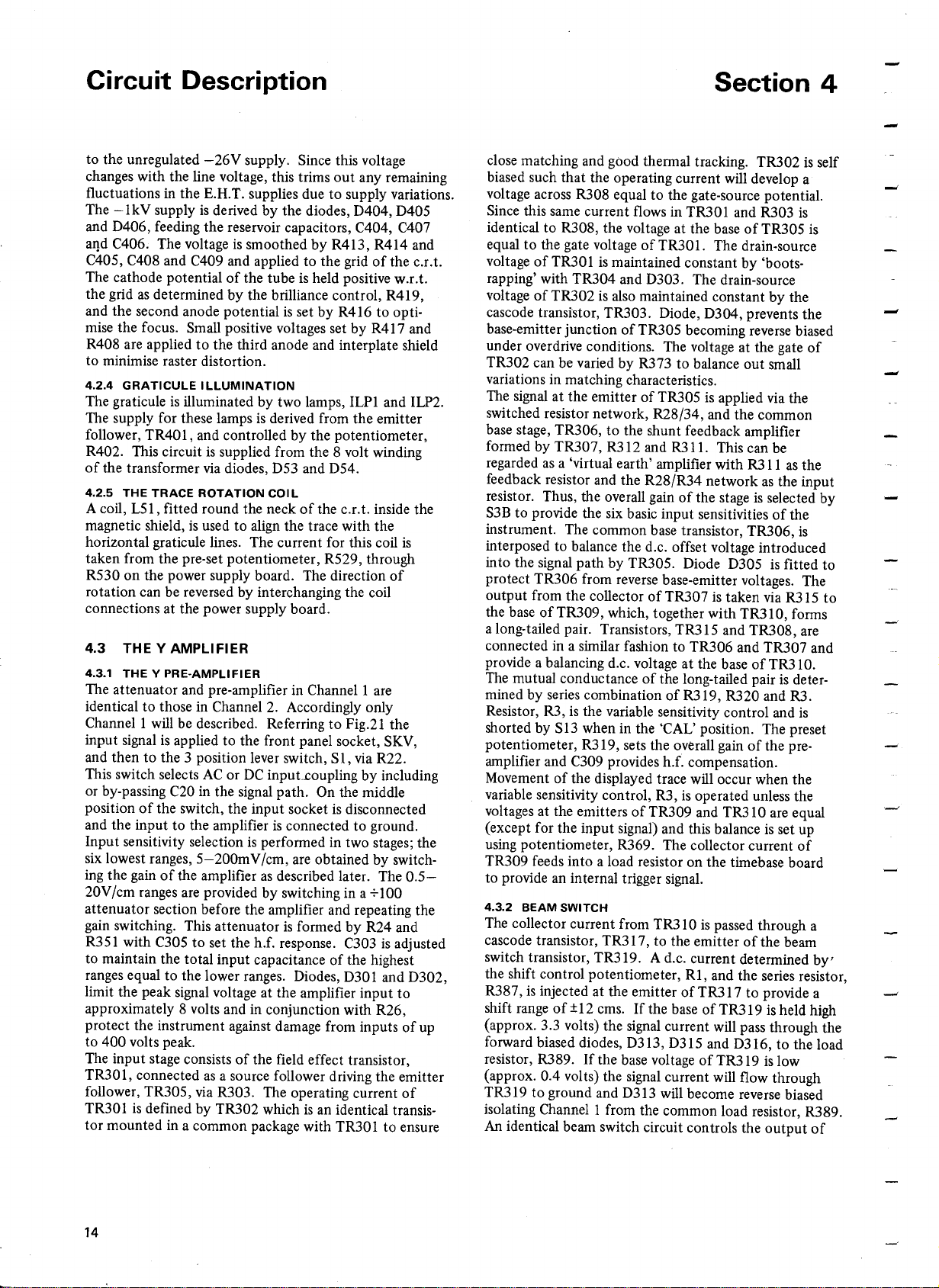

This process is then repeated using a row of 7 compara-

tors to decode the next 3 bits of data and a further DAC

and summing amplifier to drive the final row of 7 corn-

patators.

4.4.2

SCALING AMPLIFIER

Referring to the circuit diagram Fig.22 the analogue input

signal from the beamswitch is applied via R20 I to the

base of TR201. TR201 and TR202 are a Darlington

is to quantise the instantaneous signal magnitude into one

of 256 levels. These levels are represented by an 8 digit

binary code (8 bit word) and the conversion is performed

once every 550 nanosec.

Referring to the block diagram Fig.3 the input is applied,

via a scaling amplifier, to a sample-and-hold circuit. This

samples the signal level every 550nSec. and presents this

level to the first row of comparators. These compare the

signal against 3 fixed voltage levels corresponding to Y<!,

%

and*full scale input voltage. The output states of

these three comparators are then decoded to give the

first two most significant bits of the output data, DI and

D2. A 'remainder' signal is produced by subtracting from

the original signal the voltage represented by the two bits

already decoded. This operation is performed by a

summing amplifier, AI, and a 2 bit Digital to Analogue

Convertor (DAC). The reference volt ages for the

comparators are generated by the precision resistors, R,

and the current source,

exactly to the voltages subtracted from the input signal

n.

These voltages correspond

connected pair which, together with TR203 and TR204,

form a conventional long-tailed pair amplifier. The out-

put signal is taken from the collector of TR203 via the

emitter-follower, TR205, and fed to the base of the

sample-and-hold input transistor, TR206. The gain of

the scaling amplifier (approximately x12) is determined

by applying negative feedback via the potential divider

network, R2II, R207 and R208. Potentiometer, R217,

and resistor, R209, introduce a d.c. offset into the

amplifier output by drawing current through the feed-

back network. The diodes, D215 and D216, are normally

reverse biased and clamp the output signal of the amplifier

to within the working range of the ADC.

4.4.3

SAMPLE·AND·HOLD

The signal from the scaling amplifier is presented via the

emitter follower, TR206, to the sampling transistor,

TR208. This is a junction f.e.t. and it's gate is controlled

by the monostable circuit formed by TR209, TR207,

TR210 and TR212.

Page 16

Circuit Description

INPUT

SIGNAL

Section 4

I

I

I

I

I I

----------------~--------~

I

I I

I I

I I

I I I

I

1st.ROW

COMPARATOR

LEVELS

--+----------------t--------~-

I

FIRST

TWO

DATA

BITS

,

I

_n _

I

I

I

I

I

OUTPUT

FROM

FIRST

SUMMING

AMPLIFIER

The sample-and-hold cycle is initiated by a timing pulse

from the ADC logic board applied to the base of emitter

follower, TR226. This is amplified by the common

emitter amplifier, TR227, and differentiated by C214.

The negative going edge of this pulse appears at base of

TR209 and turns off the transistor. The collector

voltage of this transistor rises and turns on TR21 0 via

emitter follower, TR207, and the potential divider,

R222, R226. The negative-going signal at the collector

of TR21 0 is fed back via emitter follower, TR212, D207

and C212 to the base of TR209 thus maintaining the

L

I

I

I

I

I

I

- 2nd.1UN

- COMPARATOR

-}

- LEVELS

circuit in this state until C212 charges up via R218, and

TR209 turns on again.

In this way a large positive-going pulse, approximately

lOOnSec. long, appears at the gate of TR208. During

this time TR208 conducts and charges C210 to the input

signal voltage present at the emitter of TR206. The

injection effect of the gate-drain capacitance in TR208

is compensated by driving TR211 gate with the inverse

of the signal fed to TR208 gate. Similarly the drain-

source capacitance of TR208 is balanced by an antiphase

signal applied via C206. The voltage stored across C210

Page 17

Circuit Description

is buffered by a voltage follower comprising TR213,

TR214 and TR215. TR213 is a source follower driving

the emitter follower, TR215. The operating current of

TR213 is defined by an identical transistor, TR214,

operating in a manner similar to the Y Pre-Amplifier in-

put stage as described in section 4.3. The low impedance

output at the emitter of TR215 is fed to the first row of

comparators, ICIII and ICII2, and also to the first

summing amplifier, ICI02a.

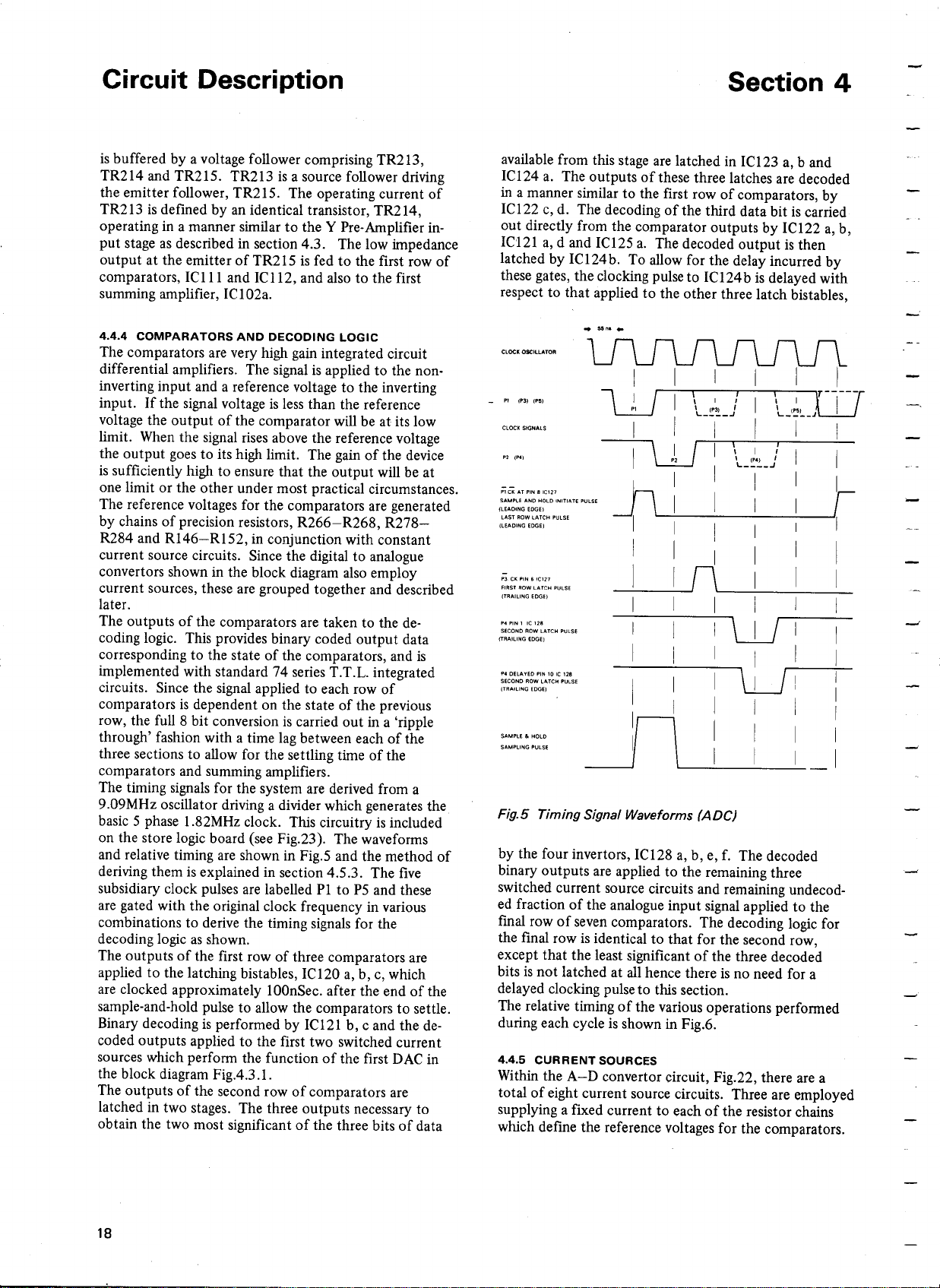

4.4.4 COMPARATORS AND DECODING LOGIC

The comparators are very high gain integrated circuit

differential amplifiers. The signal is applied to the non-

inverting input and a reference voltage to the inverting

input. If the signal voltage is less than the reference

voltage the output of the comparator will be at its low

limit. When the signal rises above the reference voltage

the output goes to its high limit. The gain of the device

is sufficiently high to ensure that the output will be at

one limit or the other under most practical circumstances.

The reference voltages for the comparators are generated

by chains of precision resistors, R266-R268, R278-

R284 and RI46-RI52, in conjunction with constant

current source circuits. Since the digital to analogue

convertors shown in the block diagram also employ

current sources, these are grouped together and described

later.

The outputs of the comparators are taken to the de-

coding logic. This provides binary coded output data

corresponding to the state of the comparators, and is

implemented with standard 74 series T.T.L. integrated

circuits. Since the signal applied to each row of

comparators is dependent on the state of the previous

row, the full 8 bit conversion is carried out in a 'ripple

through' fashion with a time lag between each of the

three sections to allow for the settling time of the

comparators and summing amplifiers.

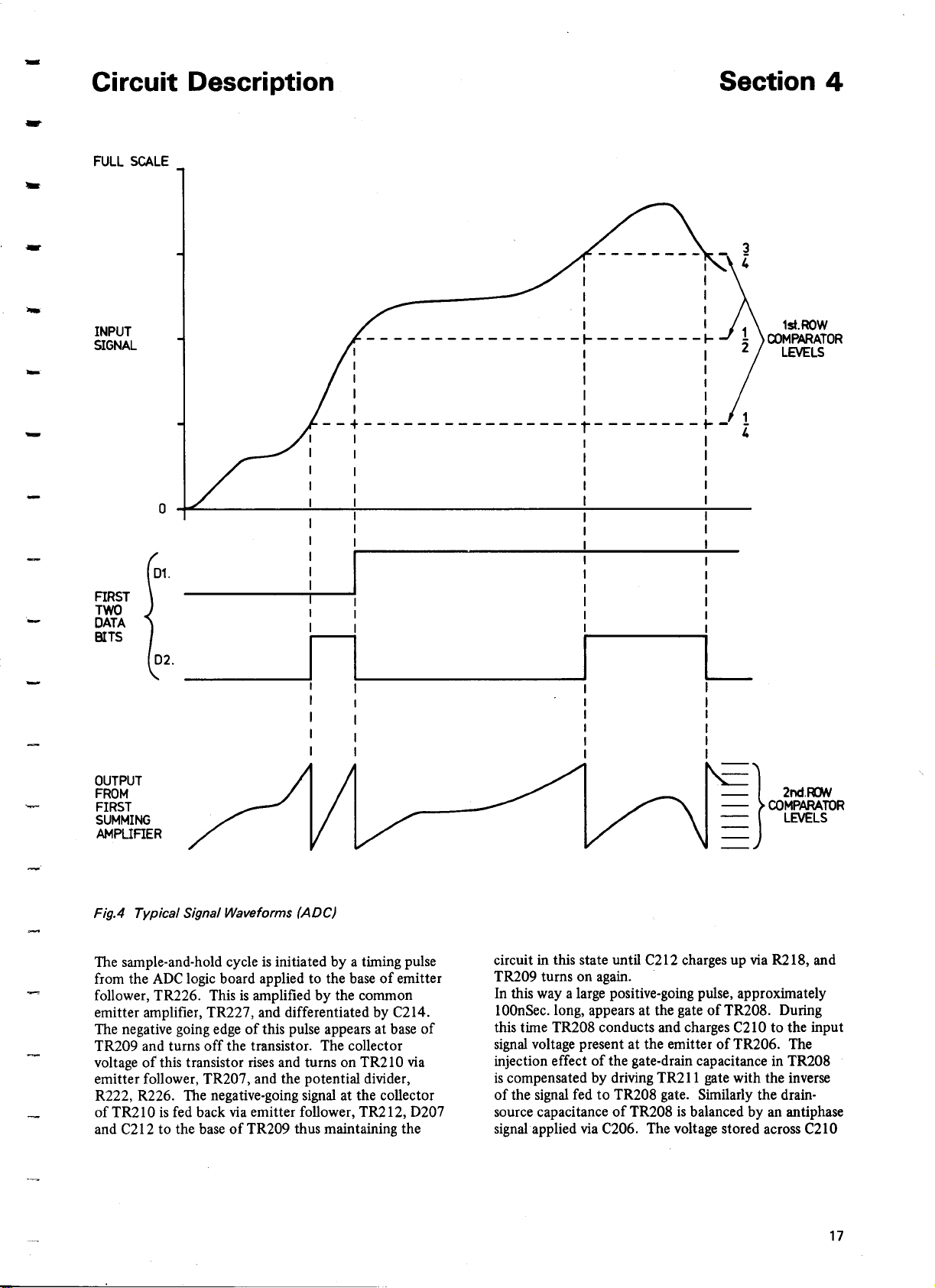

The timing signals for the system are derived from a

9.09MHz oscillator driving a divider which generates the

basic 5 phase I.82MHz clock. This circuitry is included

on the store logic board (see Fig.23). The waveforms

and relative timing are shown in Fig.5 and the method of

deriving them is explained in section 4.5.3. The five

subsidiary clock pulses are labelled PI to PS and these

are gated with the original clock frequency in various

combinations to derive the timing signals for the

decoding logic as shown.

The outputs of the first row of three comparators are

applied to the latching bistables, ICI20 a, b, c, which

are clocked approximately lOOnSec. after the end of the

sample-and-hold pulse to allow the comparators to settle.

Binary decoding is performed by ICI21 b, c and the de-

coded outputs applied to the first two switched current

sources which perform the function of the first DAC in

the block diagram Fig.4.3.I.

The outputs of the second row of comparators are

latched in two stages. The three outputs necessary to

obtain the two most significant of the three bits of data

available from this stage are latched in ICI23 a, band

ICI24 a. The outputs of these three latches are decoded

in a manner similar to the first row of comparators, by

IC122 c, d. The decoding of the third data bit is carried

out directly from the comparator outputs by ICI22 a, b,

ICI21 a, d and ICI25 a. The decoded output is then

latched by IC124b. To allow for the delay incurred by

these gates, the clocking pulse to IC 124 b is delayed with

respect to that applied to the other three latch bistables,

I

I

I I

IW

PiC;:

AT PIN 8 IC127

SAMPLE AND HOLD INITIATE PULSE

(LEADING EDGE)

LAST ROW LATCH PULSE

(LEADING EDGE)

Jl:

I I

I I

P30;PIN61C127

FIRST ROW LATCH PULSE

(TRAILING EDGE)

P4 PIN 1,e128

SECOND ROW LATCH PULse

(TRAILING EDGE)

I I

I I

I I

I I

I I

I I

n

by the four invertors, ICI28 a, b, e, f. The decoded

binary outputs are applied to the remaining three

switched current source circuits and remaining undecod-

ed fraction of the analogue input signal applied to the

final row of seven comparators. The decoding logic for

the final row is identical to that for the second row,

except that the least significant of the three decoded

bits is not latched at all hence there is no need for a

delayed clocking pulse to this section.

The relative timing of the various operations performed

during each cycle is shown in Fig.6.

4.4.5 CURRENT SOURCES

Within the A-D convertor circuit, Fig.22, there are a

total of eight current source circuits. Three are employed

supplying a fixed current to each of the resistor chains

which define the reference voltages for the comparators.

n

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

W

I

LLJ

I

I

I

r-

I

I

I

I

I

I

I

I

I

I

I

I

I

Page 18

Circuit Description

NOTE

ACTUALTIMES ARE SHOWN.

DETAILS OF S PHASE CLOCK

GENERATION ,PROPAGATION

TIMES ETC. NOT SHOWN.

t

LATCH PREVIOUS

DATA INTO STORE

CAl.CU.ATE

FIRST ROW COMPARATORS FIRST SUMMINGAMPLlFIE SAMPLE PERIOD

SECOND RDW COMPARATORS. SECOi'{) SUMMINGAMPLIFIER

SETTLE SETTLE

DS THIRD ROWCllMFr.RATms

LATCH LATCH DATA

D6.D7.D8 INTO STORE

+

The remaining five are switched by the data outputs from

the decoding logic. A common reference voltage is

supplied to all of the current source circuits by the

voltage regulator, ICIOl. The bases of the p.n.p. current

source transistors, TRl32, TRl36, TR139, TR141,

TR144, TR147, TRlS0 and TRlSl, are connected to

this reference line and precision resistors in the emitter

circuit define the collector current in each transistor.

The regulator, ICI0l, establishes the common reference

line by comparing the voltage across RI07, R266, R267

and R268 which is proportional to the output current of

the first current source, with its own internal stable

voltage reference. This internal reference, which is

available at pin 4 of ICI0l, is attenuated to a suitable

level by the potential divider chain, RI04, RI0S and

RI06, and applied to one input of the error amplifier,

pin 2. The other input of the error amplifier on pin 3

senses the voltage across the resistor chain mentioned.

In this way the regulator compensates for the effects of

supply line drift, temperature sensitive transistor

characteristics, etc. A current limit facility is provided

by the regulator: When the voltage drop across the series

resistor, RI03, exceeds one forward base emitter drop

(approximately 0.6 volt), the regulator is shut down

preventing overdissipation.

Two of the current sources, TRl32 and TR141, feed

buffer transistors, TRl33 and TR140, respectively, in

order to supply the relatively high currents required by

the first two comparator voltage reference chains.

The switched current sources are all identical with regard

to circuit operation. Taking TRl36 as an example, the

base of TR134 is driven by the most significant bit data

output at standard T.T.L. logic levels. A high level at

this point causes collector current to flow through the

load resistor, RIl3, and the catching diode, D101,

turning off TRl3S. The current source transistor,

TR136, then operates in the normal manner with it's

emitter current defined by R114 and RllS. A low level

at TR134 base turns off the transistor and R113 pulls

TRl3S base positive, turning this transistor fully on and

robbing TR136 of it's emitter current.

The currents of the first two switched current source

transistors, TRl36 and TR139, flow into a low impedance

mode in the first summing amplifier and the remaining

sources, TRI44, TR147 and TRlS0, into a similar point

in the second summing amplifier.

4.4.6

SUMMING AMPLIFIERS

The two summing amplifiers employed in Fig.22 are

identical except for the value of the feedback resistor

fitted. The component references mentioned in the

following description apply to the first amplifier which

drives the second row of comparators. ICI02 is an

integrated circuit array of five closely matched transis-

tors, two of these forming a long-tailed pair differential

input stage with a third acting as a current sink for this

stage. A p.n.p. common emitter stage, TR219, amplifies

the signal developed across the collector load resistors,

R237 and,R246, and an emitter follower, TR221,

provides a low output impedance. These stages form a

high bandwidth, differential input amplifier with

negative feedback applied via R249 to the inverting

input at the base of ICI02 b. The analogue input signal

from the sample-and-hold output transistor, TR21S, is

applied to the non-inverting input at the base of

ICI02 a, and appears at the output of the amplifier at

the emitter of TR221 by virtue of the unity voltage

gain feedback arrangement. However, the current from

the switched current sources is injected into the invert-

ing input of the amplifier at the base of ICI02 band

flows through the feedback resistor R249 developing a

negative offset voltage at the output, proportional to

the total current injected. Thus the output signal from

the amplifier represents the analogue input signal minus

the first two bits of data already detected, which

correspond to ~, h or ~ of the full scale input. The

signal fed to the second row of comparators and the

second summing amplifier input, ranges from zero to

one quarter full scale.

The second summing amplifier operates in an identical

manner except that the feedback resistor, R2S6, is one

quarter of the value of R249. This affects only the

magnitude of the injected currents which represent the

three bits of data detected by the second row of

comparators, that is

Y32to'1

full scale.

32

Page 19

Circuit Description

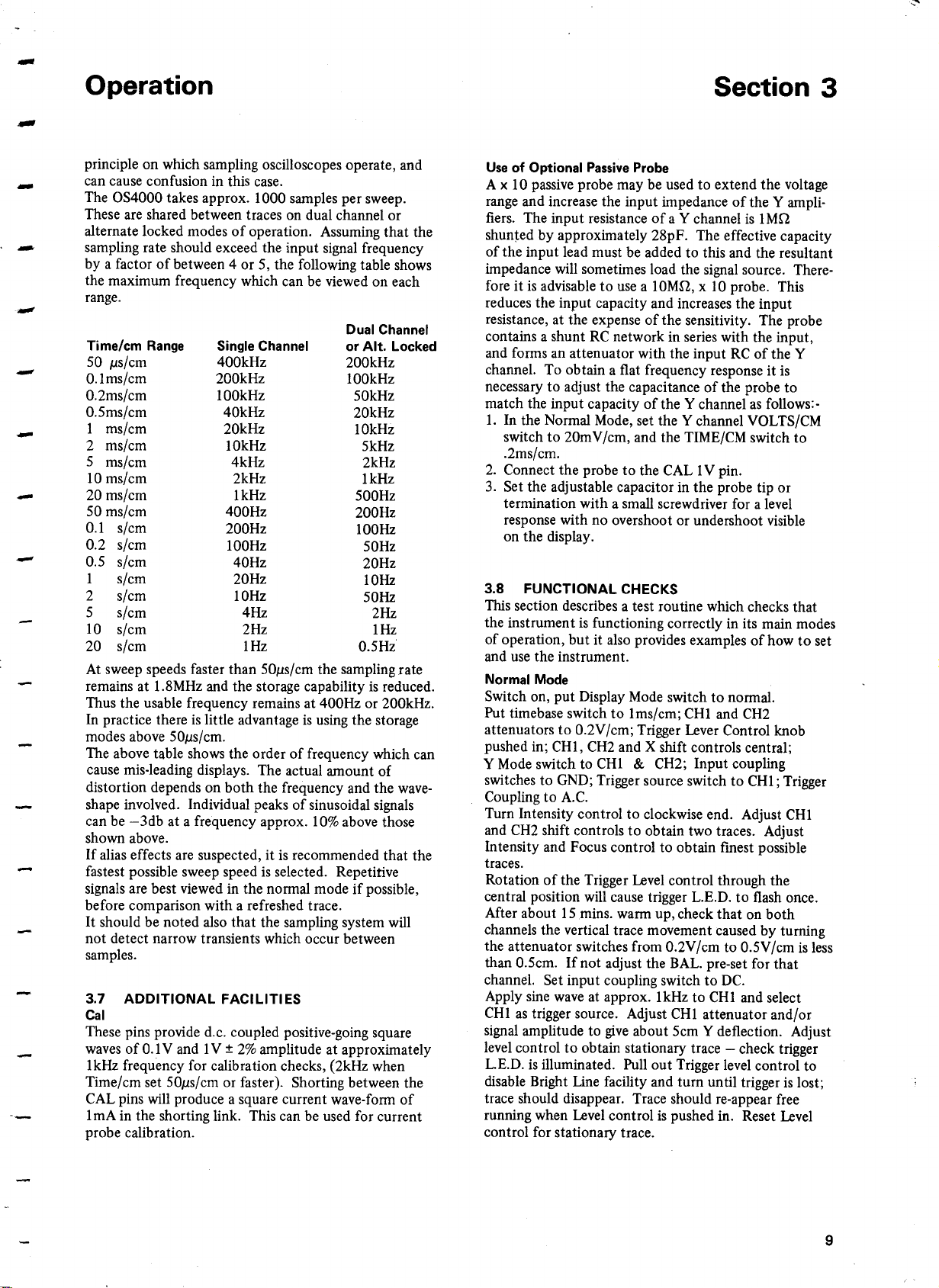

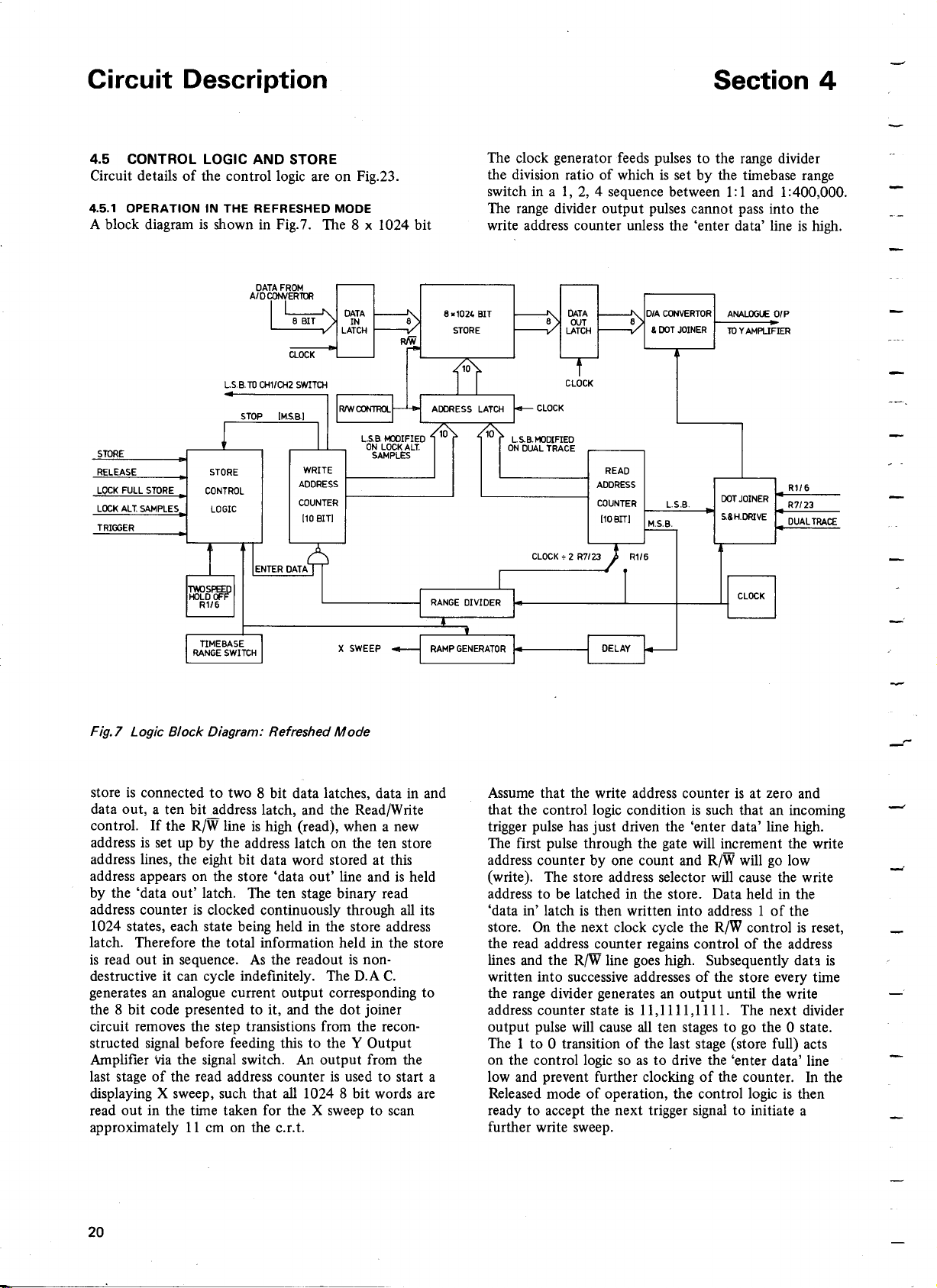

4.5 CONTROL LOGIC AND STORE

Circuit details of the control logic are on Fig.23.

4.5.1

OPERATION IN THE REFRESHED MODE

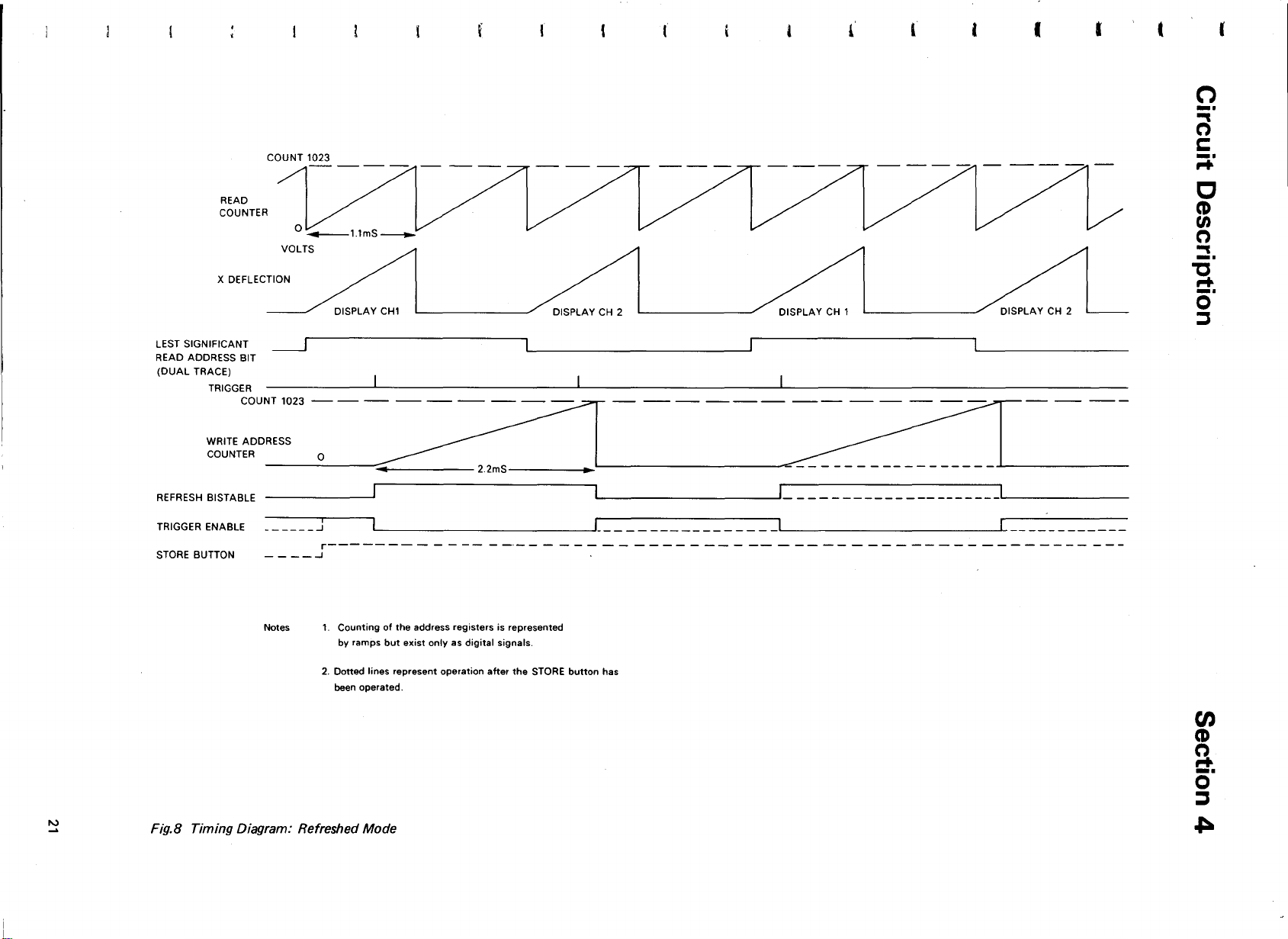

A block diagram is shown in Fig.7. The 8 x 1024 bit

STORE

RELEASE

LOCK FULL STORE

LOCK ALT. SAMPLES

TRIGGER

STORE

CONTROL

LOGIC

WRITE

ADDRESS

COUNTER

110 BIT]

The clock generator feeds pulses to the range divider

the division ratio of which is set by the time base range

switch in aI, 2, 4 sequence between 1: 1 and 1:400,000.

The range divider output pulses cannot pass into the

write address counter unless the 'enter data' line is high.

DIA CONVERTOR ANALOGl£ OIP

8

& DOT JOINER TOYAMPUFIER

READ

ADDRESS

COUNTER

110BlT]

M.s.B.

L.s.B.

DOT JOINER

S&H.DRIVE

R116

R7123

DUAL TRACE

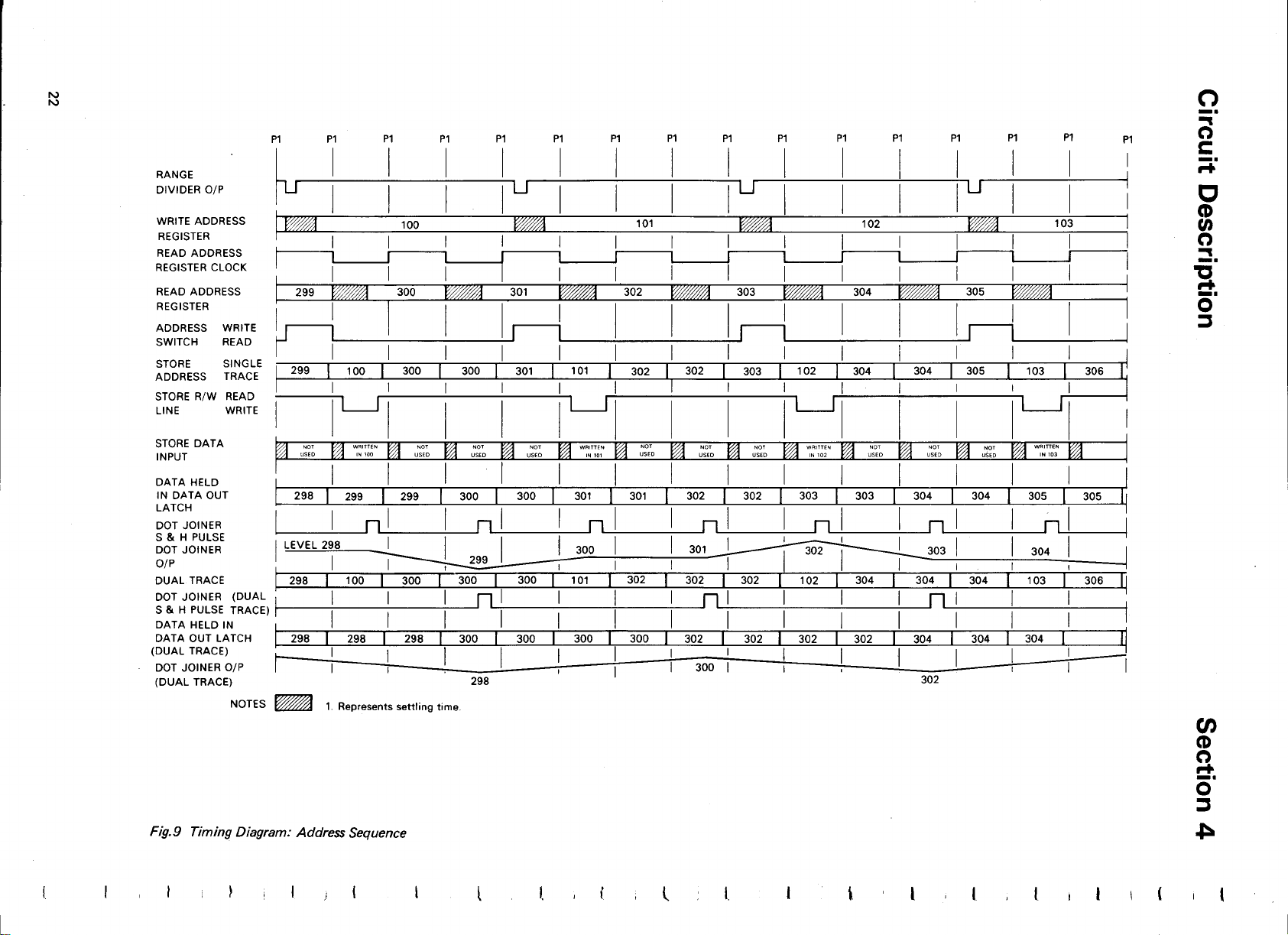

store is connected to two 8 bit data latches, data in and

data out, a ten bit address latch, and the Read/Write

control. If the R/W line is high (read), when a new

address is set up by the address latch on the ten store

address lines, the eight bit data word stored at this

address appears on the store 'data out' line and is held

by the 'data out' latch. The ten stage binary read

address counter is clocked continuously through all its

1024 states, each state being held in the store address

latch. Therefore the total information held in the store

is read out in sequence. As the readout is non·

destructive it can cycle indefinitely. The D.A C.

generates an analogue current output corresponding to

the 8 bit code presented to it, and the dot joiner

circuit removes the step transistions from the recon·

structed signal before feeding this to the Y Output

Amplifier Via the signal switch. An output from the

last stage of the read address counter is used to start a

displaying X sweep, such that all 1024 8 bit words are

read out in the time taken for the X sweep to scan

approximately 11 cm on the c.r.t.

Assume that the write address counter is at zero and

that the control logic condition is such that an incoming

trigger pulse has just driven the 'enter data' line high.

The first pulse through the gate will increment the write

address counter by one count and R/W will go low

(write). The store address selector will cause the write

address to be latched in the store. Data held in the

'data in' latch is then written into address 1 of the

store. On the next clock cycle the R/W control is reset,

the read address counter regains control of the address

lines and the R/W line goes high. Subsequently dah is