GMT G571SZ, G571S1 Datasheet

Global Mixed-mode Technology Inc.

G571

Single-Slot PCMCIA/CardBus Power Controllers

Features

Fully Integrated VCC and VPP Switching for Sin-

gle-Slot PC Card

Low r

Switch)

Compatible With Controllers From Cirrus, Ri-

coh, O

3.3V Low-Voltage Mode

Meets PC Card Standards

12V Supply Can Be Disabled Except During

12V Flash Programming

Short Circuit and Thermal Protection

Space-Saving 16 Pin SSOP

Compatible With 3.3V, 5V, and 12V PC Cards

Break-Before-Make Switching

Application

Notebook PC

Electronic Dictionary

Personal Digital Assistance

Digital still Camera

TM

Interface

(180-m

DS(on)

Micro, Intel, and Texas Instruments

2

5V VCC Switch and 3.3V VCC

ΩΩΩΩ

Description

The G571 PC Card power-interface switch provides an

integrated power-management solution for a single PC

Cards. All of the discrete power MOSFETs, a logic

section, current limiting, and thermal protection for PC

Card control are combined on a single integrated circuit. The circuit allows the distribution of 3.3V, 5V,

and/or 12V card power, and is compatible with many

PCMCIA controllers. The current-limiting feature

eliminates the need for fuses, which reduces component count and improves reliability. Current-limit reporting can help the user isolate a system fault to the

PC Card.

The G571 features a 3.3V low voltage mode that allows for 3.3V switching without the need for 5V. Bias

power can be derived from either the 3.3V or 5V inputs.

This facilitates low-power system designs such as

sleep mode and pager mode where only 3.3V is

available.

End equipment for the G571 includes notebook computers, desktop computers, personal digital assistants

(PDAs), digital cameras and bar-code scanners.

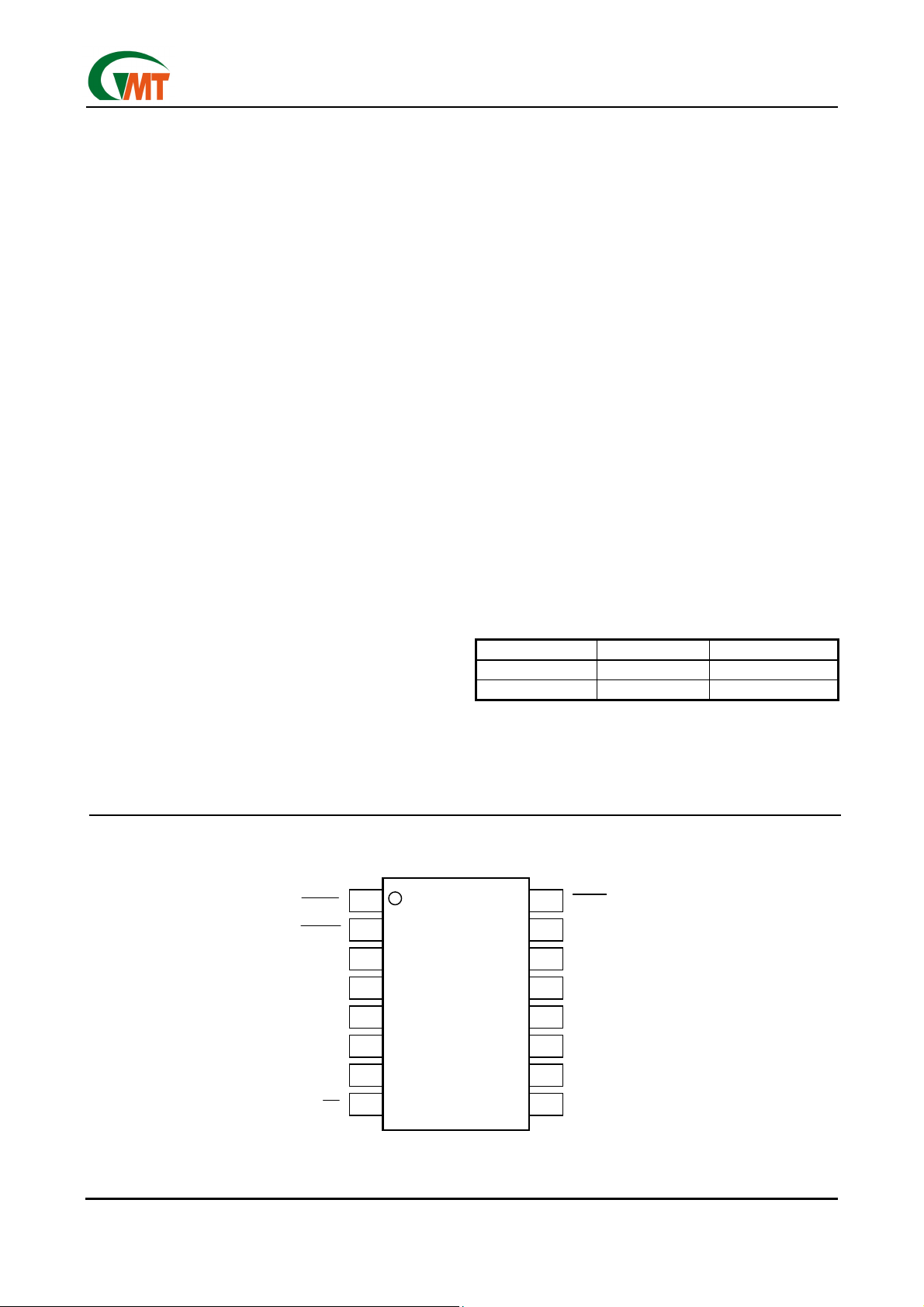

Pin Configuration

VCCD0

VCCD1

3.3V

3.3V

5V

5V

GND

Ordering Information

PART NUMBER TEMP. RANGE PACKAGE

G571SZ -40°C to +85°C SSOP-16L (150mil)

G571S1 -40°C to +85°C SSOP-16L (209mil)

G571

1

2

3

4

5

6

7

16

15

14

13

12

11

10

SHDN

VPPD0

VPPD1

AVCC

AVCC

AVCC

AVPP

Ver: 1.3

Feb 18, 2003

OC

9

8

12V

16Pin SSOP

1

TEL: 886-3-5788833

http://www.gmt.com.tw

Global Mixed-mode Technology Inc.

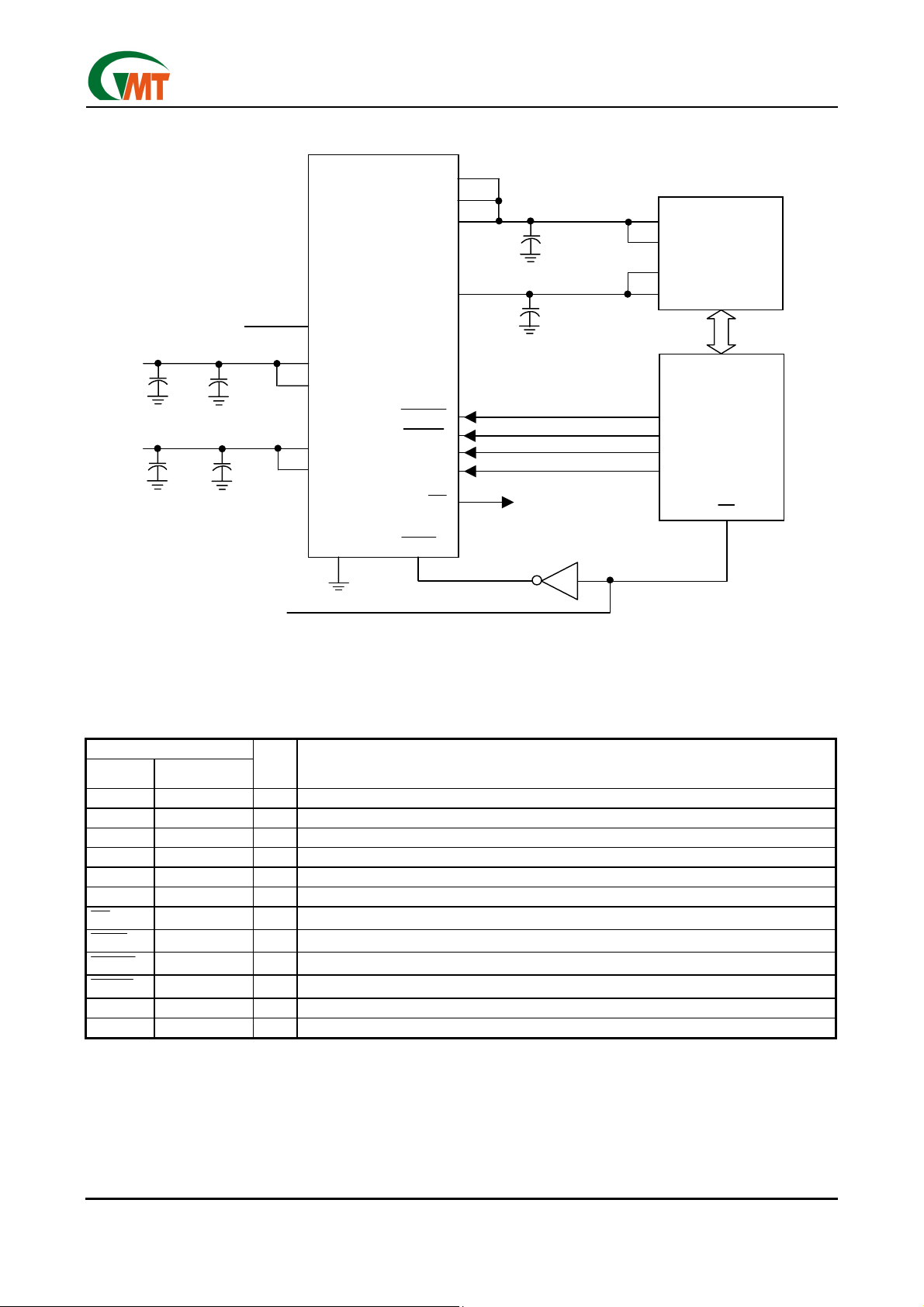

Typical PC-card Power-distribution application

AVCC

AVCC

AVCC

AVPP

12V

5V

5V

3.3V

3.3V

GND

G571

VCCD0

VCCD1

VPPD0

VPPD1

OC

SHDN

5V

3.3V

0.1µF

0.1µF

12V

1µF

1µF

0.1µF

0.1µF

To CPU

V

CC1

V

PC Card

CC2

Connector

V

PP1

V

PP2

PCMCIA

Controller

VCC_EN0

VCC_EN1

VPP_EN0

VPP_EN1

G571

CS

Shutdown Signal From CPU

Terminal Functions

TERMINAL

NAME NO.

3.3V 3,4 I 3.3V VCC input for card power and/or chip power if 5V is not present

5V 5,6 I 5V VCC input for card power and/or chip power

12V 9 I 12V VPP input card power

AVCC 11,12,13 O Switched output that delivers 0V, 3.3V, 5V, or high impedance to card

AVPP 10 O Switched output that delivers 0V, 3.3V, 5V, 12V or high impedance to card

GND 7 Ground

OC

SHDN

0VCCD

1VCCD

VPPD0 15 I Logic input that controls voltage of AVPP (see control-logic table)

VPPD1 14 I Logic input that controls voltage of AVPP (see control-logic table)

8 O Logic-level overcurrent reporting output that goes low when an overcurrent condition exists

16 I Logic input that shuts down the G571 and sets all power outputs to high-impedance state

1 I Logic input that controls voltage of AVCC (see control-logic table)

2 I

I/O DESCRIPTION

Logic input that controls voltage of AVCC (see control-logic table)

Ver: 1.3

Feb 18, 2003

2

TEL: 886-3-5788833

http://www.gmt.com.tw

Global Mixed-mode Technology Inc.

Absolute Maximum Ratings Over Operating

Free-Air Temperature

Input voltage range for card power:

V

..........................................………..…….-0.3V to 7V

I(5V)

V

..........…...........................…….……... -0.3V to 7V

I(3.3V)

V

..........................................……..…….-0.3V to 14V

I(12V)

Logic input voltage....................…...........…….-0.3V to 7V

Output current (each card):I

I

Operating virtual junction temperature range, T

.........…..............…………..…….………-40°C to 150°C

Operating free-air temperature range,.T

*

Stresses beyond those listed under "absolute maximum ratings”may cause permanent damage to the device. These are stress

rating only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions”is not implied. Exposure to absolute–maximum-rated conditions for extended periods may affect device reliability.

Note 1: ESD (electrostatic discharge) sensitive device. Proper ESD precautions are recommended to avoid performance degradation or

less of functionality.

(unless other-wise noted)*

...……internally limited

O (VCC).

............internally limited

O(VPP)

J.

A

………………………………………………………………………….

Storage temperature range, T

………………………...........….....……...-55°C to 150°C

STG

Lead temperature 1.6 mm (1/16 inch) from case for

10 seconds.……..……………………………….….260°C

Thermal resistance

θ

JA

SSOP-16L (150mil)…..…….……….…………178°C/W

SSOP-16L (209mil)…..….…………….………161°C/W

Power dissipation P

D

(T

+25°C)

≤

A

SSOP-16L (150mil)……………………………..700mW

SSOP-16L (209mil)..……………………………775mW

ESD…………………………..………………..……Note1

G571

-40°C to 85°C

Recommended Operating Conditions

V

0 5.25 V

I(5V)

Input voltage, VI

Output current

Operating virtual junction temperature, TJ -40 125

V

0 5.25 V

I(3.3V)

V

0 13.5 V

I(12V)

I

1.0 A

O(AVCC)

I

150 mA

O(AVPP)

MIN MAX UNIT

°C

(TA=25°C)

Electrical Characteristics

Power Switch

PARAMETER TEST CONDITIONS* MIN TYP MAX UNIT

5V to AVCC V

3.3V to AVCC V

Switch resistance

3.3V to AVCC V

5V to AVPP TJ = 25°C 6

3.3V to AVPP TJ = 25°C 6

12V to AVPP T

V

Clamp low voltage IPP at 10mA 0.8 V

O(AVPP)

V

Clamp low voltage ICC at 10mA 0.8 V

O(AVCC)

I

Leakage current

IKG

I

Input current

I

IPP high-impedance State TA = 25°C 1 10

I

high-impedance State TA = 25°C 1 10

CC

V

= 5V V

I(5V)

V

I(5V)

= 0V, V

= 3.3V V

I(3.3V)

Shutdown mode V

I

Short-circuit Output-

OS

current Limit

*Pulse-testing techniques maintain junction temperature close to ambient temperatures; thermal effects must be taken into account separately.

O(AVCC)

I

O(AVPP)

0.8 2.2 A I

= 5V 130 180

I(5V)

= 5V, V

I(5V)

= 0V, V

I(5V)

= 25°C 6

J

=5V,V

O(AVCC)

=3.3V,V

O(AVCC)

O(AVCC)=VO(AVPP)

=3.3V 130 180

I(3.3V)

=3.3V 130 180

I(3.3V)

=12V 75 150

O(AVPP)

= 12V 75 150

O(AVPP)

= Hi-Z 1 3

output powered into a short to GND

120 400 mA

mΩ

Ω

µA

µA

Ver: 1.3

Feb 18, 2003

3

TEL: 886-3-5788833

http://www.gmt.com.tw

Global Mixed-mode Technology Inc.

G571

Logic Section

PARAMETER TEST CONDITION* MIN MAX UNIT

Logic input current 1 µA

Logic input high level 2 V

Logic input low level 0.8 V

Logic output high level

= 5V, IO=1mA V

I(5V)

V

=0V,IO= 1mA,V

I(5V)

= 3.3V V

I(3.3V)

- 0.4

I(5V)

- 0.4

I(3.3V)

V

V

Logic output low level IO = 1mA 0.4 V

*Pulse-testing techniques maintain junction temperature close to ambient temperatures; thermal effects must be taken into account separately.

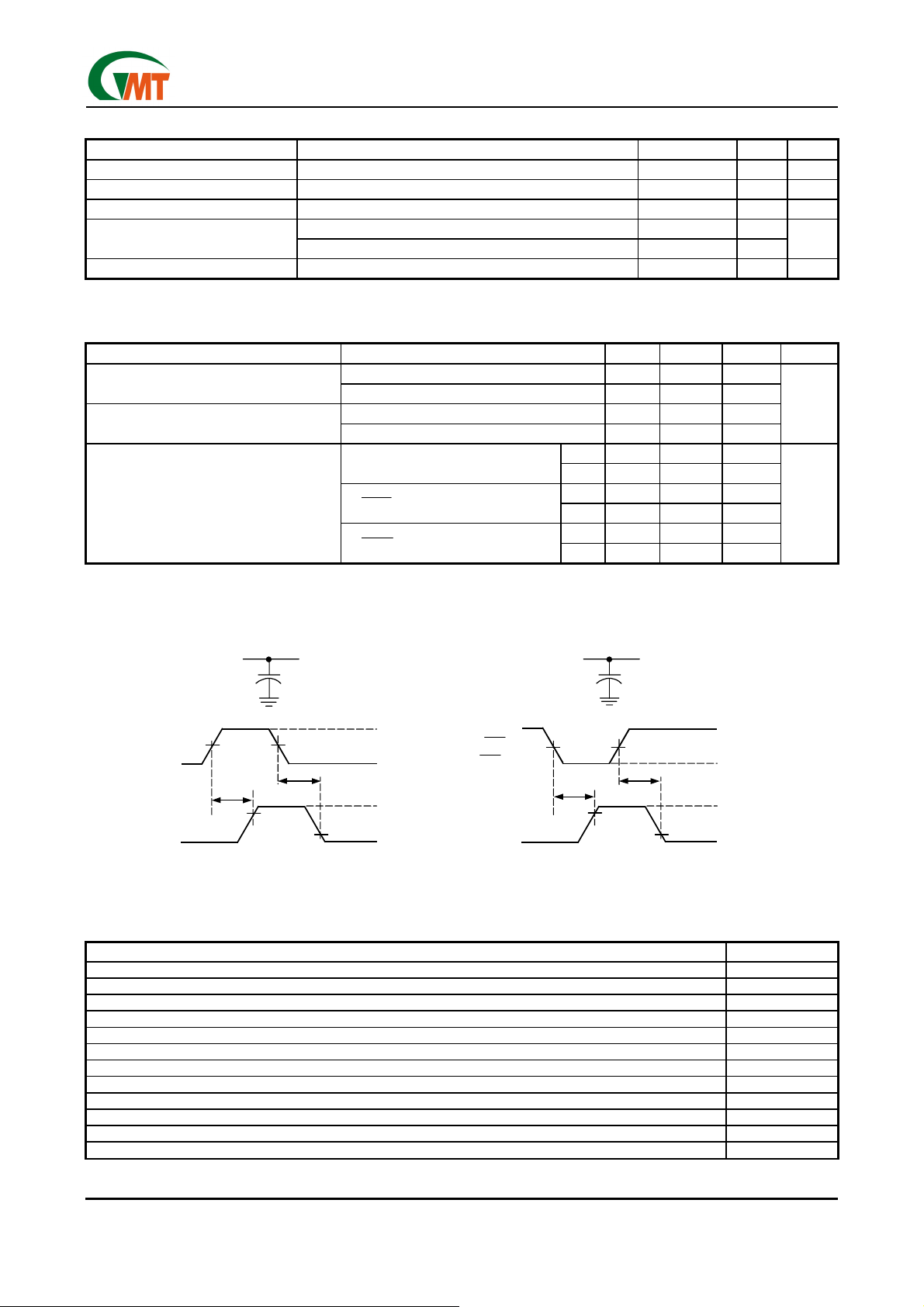

Switching Characteristics **

PARAMETER TEST CONDITION MIN TYP MAX UNIT

t

Rise times, output

r

t

Fall times, output

f

V

V

V

V

VI(

t

Propagation delay

pd

(see Figure 1)

VI(

V

**Switching Characteristics are with CL = 147µF.

§ Refer to Parameter Measurement Information

2.6

O (AVCC)

10

O (AVPP)

7.5

O (AVCC)

38

O (AVPP)

VPPD0

(

I

) to V

1VCCD

) to V

0VCCD

) to V

O(AVPP)

O(AVCC)

O(AVCC)

(3.3V)

(5V)

ton 14

t

44

off

ton 3.2

17

t

off

ton 4.4

20

t

off

ms

ms

Parameter Measurement Information

AVPP

C

L

(V

V

I(VPPD1)

V

I(VPPD0)

O(AVPP)

=0V)

LOAD CIRCUIT

50%

t

on

VOLTAGE WAVEFORMS

90%

50%

t

off

10%

V

DD

GND

V

GND

I(12V)

V

I(VCCD1)

(V

I(VCCD0)=VDD

V

O(AVCC)

Figure 1. Test Circuits and Voltage Waveforms

Table of Timing Diagrams

AVCC Propagation Delay and Rise Time With 1µF Load, 3.3V Switch 2

AVCC Propagation Delay and Fall Time With 1µF Load, 3.3V Switch 3

AVCC Propagation Delay and Rise Time With 147µF Load, 3.3V Switch 4

AVCC Propagation Delay and Fall Time With 147µF Load, 3.3V Switch 5

AVCC Propagation Delay and Rise Time With 1µF Load, 5V Switch 6

AVCC Propagation Delay and Fall Time With 1µF Load, 5V Switch 7

AVCC Propagation Delay and Rise Time With 147µF Load, 5V Switch 8

AVCC Propagation Delay and Fall Time With 147µF Load, 5V Switch 9

AVPP Propagation Delay and Rise Time With 1µF Load, 12V Switch 10

AVPP Propagation Delay and Fall Time With 1µF Load, 12V Switch 11

AVPP Propagation Delay and Rise Time W ith 147µF Load, 12V Switch 12

AVPP Propagation Delay and Fall Time With 147µF Load, 12V Switch 13

AVCC

LOAD CIRCUIT

50%

)

t

on

VOLTAGE WAVEFORMS

90%

C

50%

L

V

DD

t

off

10%

GND

V

I(3.3V)

GND

FIGURE

Ver: 1.3

Feb 18, 2003

4

TEL: 886-3-5788833

http://www.gmt.com.tw

Loading...

Loading...