G-LINK

RAS

CAS

RAS

512K X 8 CMOS DYNAMIC RAM WITH FAST PAGE MODE

Features : Description :

GLT44108

Preliminary Aug 1999 (Rev.2.1)

∗ 524,288 words by 8 bits organization.

∗ Fast access time and cycle time.

∗ Low power dissipation.

Operating Current-150mA max.

TTL Standby Current-2mA max.

∗ Read-Modify-Write,

-Before-

Refresh, Hidden

-Only Refresh,

Refresh and Test Mode Capability.

∗ 1024 refresh cycles/16ms.

∗ Available in 28pin 400 mil SOJ

∗ Single +5.0V±10% Power Supply.

∗ All inputs and Outputs are TTL-

compatible.

∗ Fast Page Mode supports sustained data

rates up to 50MHZ.

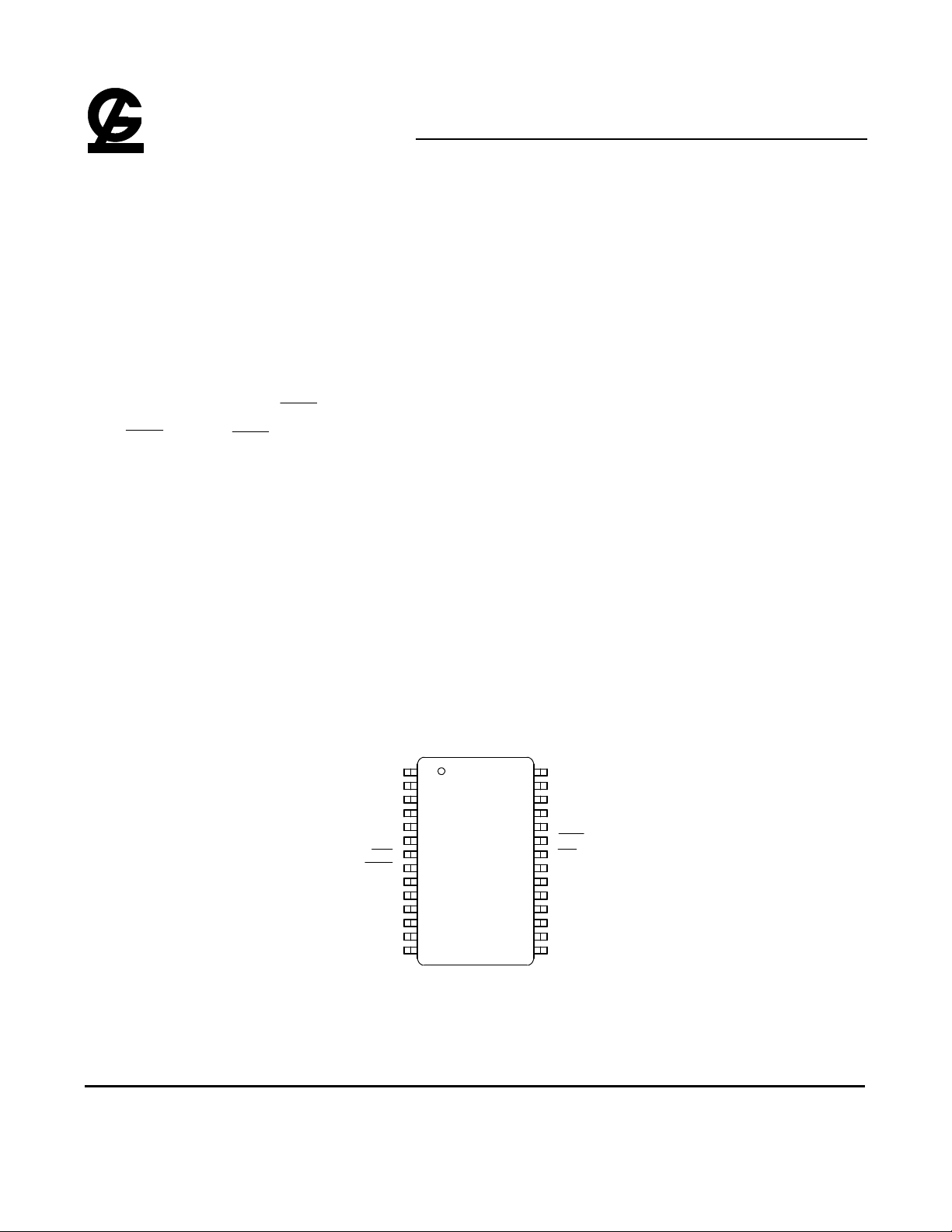

PIN CONFIGURATION :

The GLT44108 is a 524,288 x 8 bit highperformance CMOS dynamic random access

memory. The GLT44108 offers Fast Page mode with

asymmetric address and accepts 512-cycle refresh in

8ms interval.

All inputs are TTL compatible. Fast Page Mode

operation allows random access up to 512 x 8 bits

within a page, with cycle times as short as 22ns.

The GLT44108 is best suited for graphics, digital

signal processing and high performance peripherals.

GLT44108

28 Lead SOJ

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

Vcc

DQ0

DQ1

DQ2

DQ3

NC

WE

RAS

A9

A0

A1

A2

A3

VCC

1

2

3

4

5

6

7

8

9

10

11

12

13

- 1 -

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VSS

DQ

7

DQ6

DQ5

DQ4

CAS

OE

NC

A8

A7

A6

A5

A

4

VSS14

G-Link Technology Corporation,Taiwan

6F, No.24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

G-LINK

RAS

CAS

RAS

CAS

WE

OE

.

I/O0

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

GLT44108

512K X 8 CMOS DYNAMIC RAM WITH FAST PAGE MODE

Preliminary Aug 1999 (Rev.2.1)

HIGH PERFORMANCE -40 -50 -60

Max.

Access Time, (t

RAC

)

40 ns 50 ns 60 ns

Max. Column Address Access Time, (tAA) 20 ns 25 ns 30 ns

Min. Fast Page Mode Cycle Time, (tPC) 22 ns 31 ns 40 ns

Min. Read/Write Cycle Time, (tRC) 75 ns 90 ns 110 ns

Max.

Access Time (t

CAC

)

12 ns 13 ns 15 ns

Pin Descriptions:

Name Function

A0 – A

9

Address Inputs

Row Address Strobe

Column Address Strobe

Write Enable

Output Enable

DQ0 - DQ

V

CC

V

SS

7

Data Inputs / Outputs

+5V Power Supply

Ground

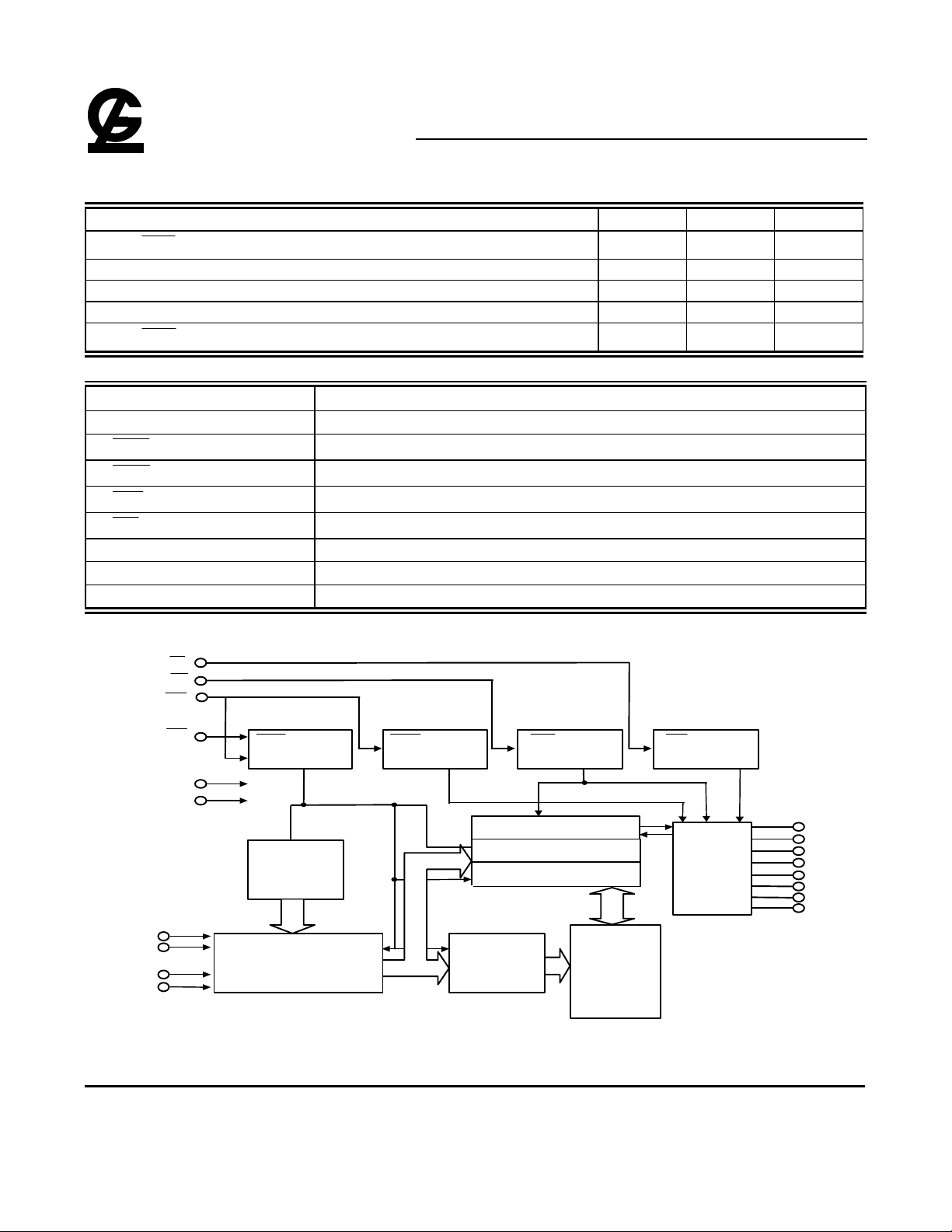

Block Diagram:

OE

WE

CAS

RAS

V

CC

V

SS

A

0

A

1

.

A

8

A

9

RAS

CLOCK

GENERATOR

REFRESH

COUNTER

9

ADDRESS BUFFERS

AND PREDECODERS

CAS

CLOCK

GENERATOR

Y0 - Y

8

DECODERS

X0 - x

9

WE

CLOCK

GENERATOR

Data I/O BUS

COLUMN DECODERS

SENSE AMPLIFIERS

1024

ROW

MEMORY

ARRAY

OE

GENERATOR

512×8

CLOCK

I/O

BUFFER

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No.24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 2 -

G-LINK

RAS

CAS

WE ,OE

CAS

RAS

RAS

512K X 8 CMOS DYNAMIC RAM WITH FAST PAGE MODE

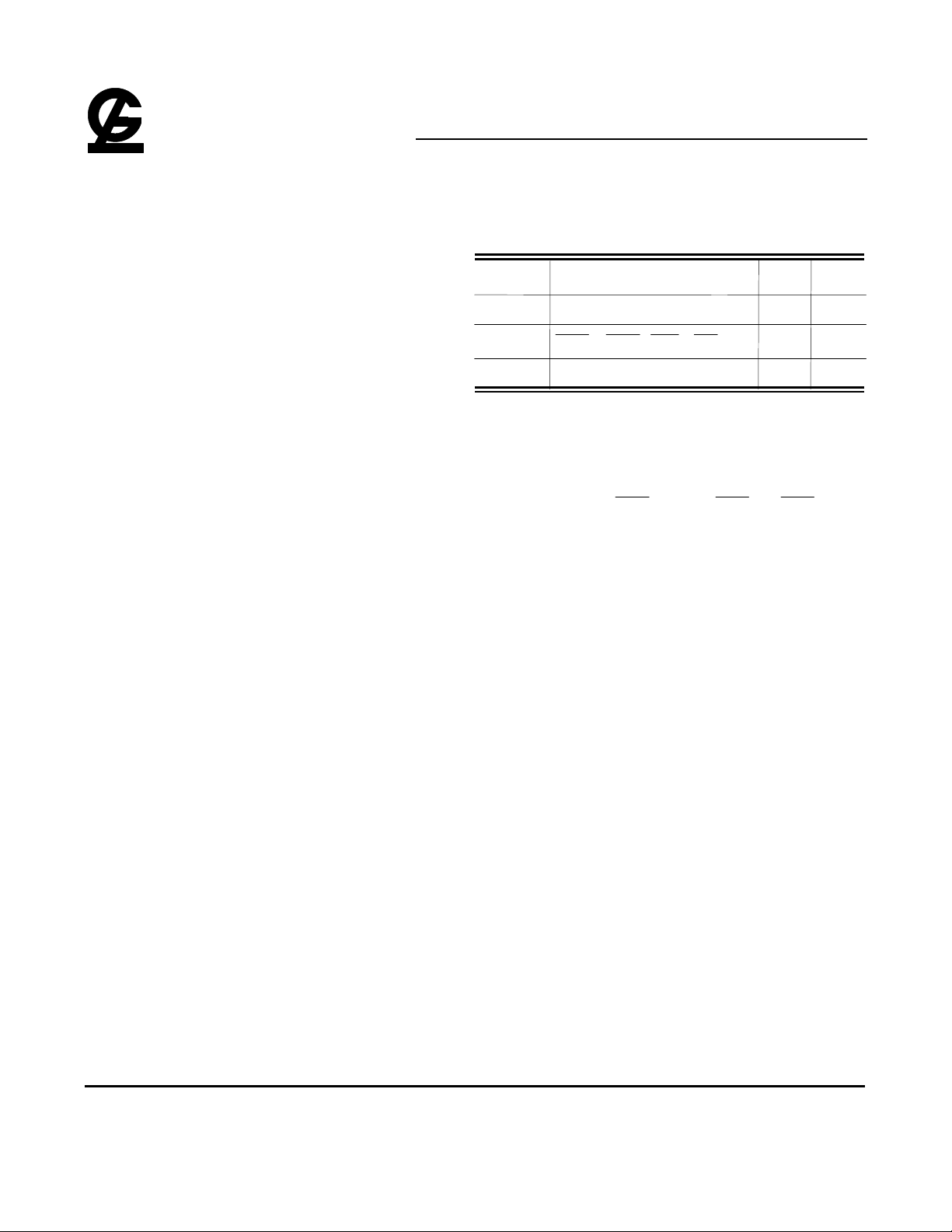

Absolute Maximum Ratings* Capacitance*

TA=25°C, VCC=5V±10%, VSS=0V

GLT44108

Preliminary Aug 1999 (Rev.2.1)

Operating Temperature, TA (ambient)

Symbol

......................................-10°C to +80°C

C

Storage Temperature(plastic)....-55°C to +150°C

Voltage Relative to VSS...............-1.0V to + 7.0V

IN1

C

IN2

Short Circuit Output Current......................50mA

C

Power Dissipation......................................1.0W

*Note:Operation above Absolute Maximum Ratings can

adversely affect device reliability.

OUT

*Note: Capacitance is sampled and not 100% tested

Electrical Specifications

l All voltages are referenced to GND.

l After power up, wait more than 200µs and then, execute eight

refresh cycles as dummy cycles to initialize internal circuit.

Parameter

Address Input

,

,

Data Input/Output

before

or

Max.

5

7

7

Unit

pF

pF

pF

only

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No.24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 3 -

G-LINK

RAC

RAC

RAC

RAS

CAS

RAS

RAS

CAS

RAC

RAC

RAC

RAS

CAS

RAC

RAC

RAC

CAS

RAS

RAS

CAS

RAC

RAC

RAC

RAS

CAS

512K X 8 CMOS DYNAMIC RAM WITH FAST PAGE MODE

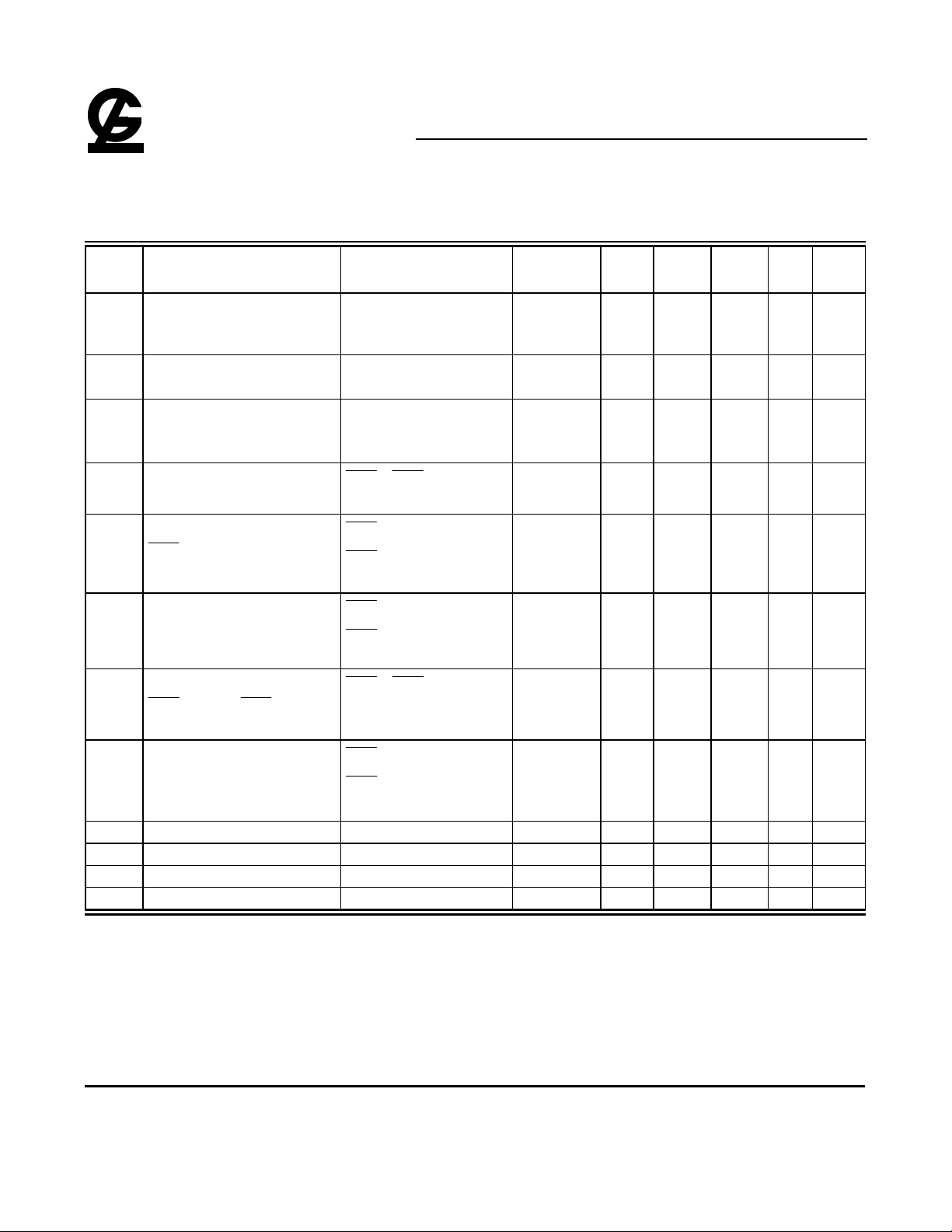

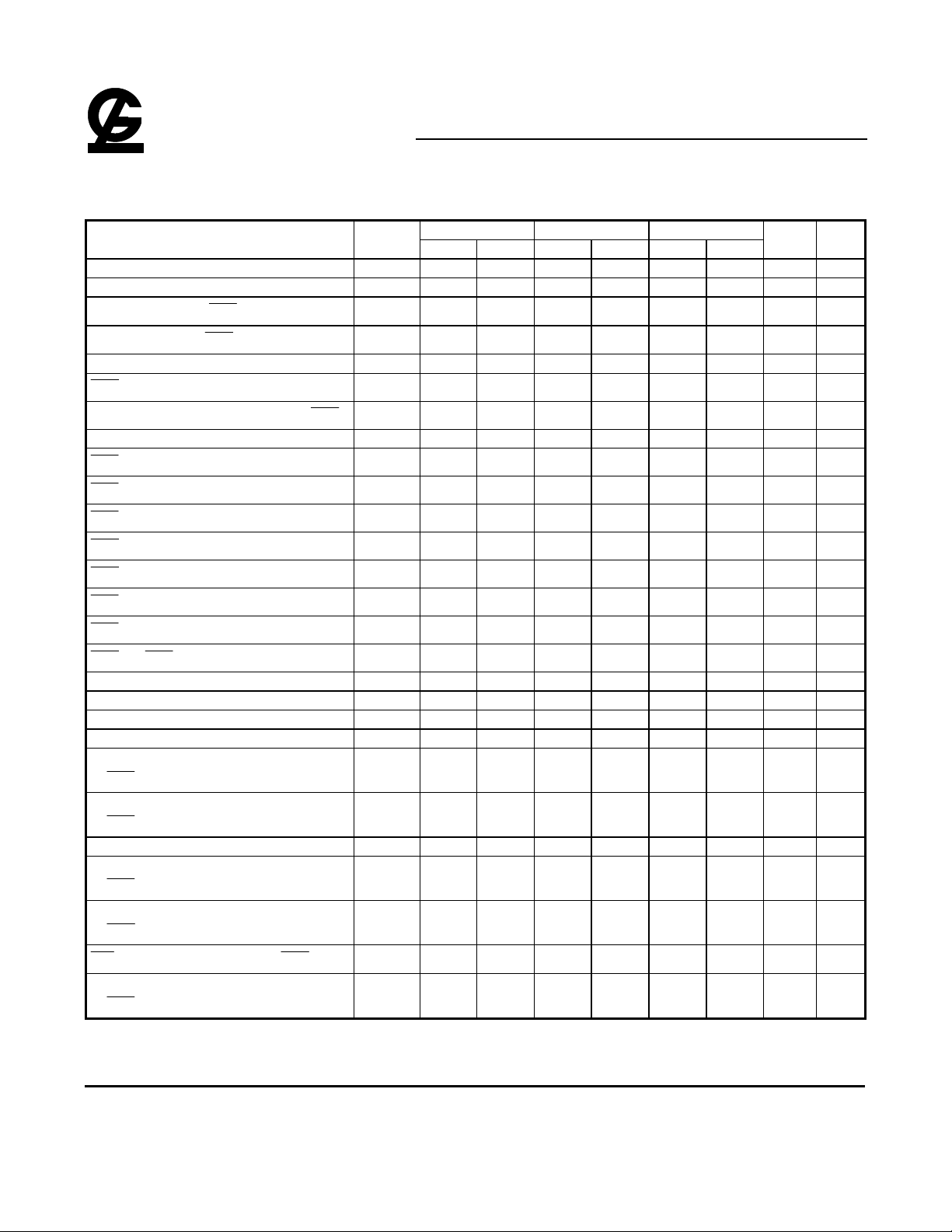

DC and Operating Characteristics (1-2)

TA = 0°C to 70°C, VCC=5V±10%, VSS=0V, unless otherwise specified.

GLT44108

Preliminary Aug 1999 (Rev.2.1)

Sym. Parameter Test Conditions Access

Min. Typ Max. Unit Notes

Time

I

I

I

I

I

I

I

I

V

V

V

V

Notes:

1.ICC is dependent on output loading when the device output is selected. Specified I

2.ICC is dependent upon the number of address transitions specified. I

3. Specified V

Input Leakage Current

LI

(any input pin)

0V ≤ VIN ≤ 5.5V

(All other pins not under

-10 +10

test=0V)

Output Leakage Current

LO

(for High-Z State)

Operating Current,

CC1

0V ≤ V

Output is disabled (Hiz)

Random READ/WRITE tRC = tRC (min.)

Standby Current,(TTL)

CC2

other inputs ≥ V

Refresh Current,

CC3

-Only

≤ 5.5V

out

,

cycling,

at V

IH

, at V

SS

t

= 40ns

t

= 50ns

t

= 60ns

IH

t

= 40ns

t

= 50ns

t

= 60ns

-10 +10

tRC = tRC (min.)

Operating Current,

CC4

FAST Page Mode

Refresh Current,

CC5

Before

Standby Current, (CMOS)

CC6

at V

,

IL

,address

cycling:tPC=tPC(min.)

,

,

address cycling:

tRC=tRC(min.)

≥ VCC-0.2V,

t

t

t

t

t

t

= 40ns

= 50ns

= 60ns

= 40ns

= 50ns

= 60ns

≥ VCC-0.2V,

All other inputs ≥V

Input Low Voltage -1 +0.8 V 3

IL

Input High Voltage 2.4 VCC+1 V 3

IH

Output Low Voltage IOL = 4.2mA 0.4 V

OL

Output High Voltage IOH = -5mA 2.4 V

OH

open.

per address cycle in random Read/Write and Fast Page Mode.

is steady state operation. During transitions, V

IL(min.)

not to exceed 20ns.All AC parameters are measured with V

SS

IL(min.)

IL(min.)≥Vss

is measured with a maximum of one transition

CC(max.)

may undershoot to -1.0V for a period

and V

IH(max.)≤Vcc

150

140

120

2 mA

150

140

120

150

140

120

150

140

120

1 mA

is measured with the output

CC(max.)

.

µA

µA

mA 1,2

mA 2

mA 1,2

mA 1

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No.24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 4 -

G-LINK

RAS

CAS

CAS

CAS

RAS

RAS

RAS

CAS

CAS

RAS

RAS

CAS

RAS

RAS

RAS

RAS

CAS

WE

CAS

RAS

512K X 8 CMOS DYNAMIC RAM WITH FAST PAGE MODE

AC Characteristics (0°°C≤≤TA≤≤70°°C,See note 1,2)

Test condition:VCC=5.0V±10%, VIH/VIL=2.4V/0.8V,VOH/VOL=2.0V/0.8V

Parameter 40 ns 50 ns 60 ns

Symbol MIN. MAX. MIN. MAX. MIN. MAX. Unit Notes

Read/Write Cycle Time t

Read Midify Write Cycle Time t

Access Time from

Access Time from

Access Time from Column Address t

to Output in Low-Z

Output Buffer Turn-off Delay from

Transition Time(Rise and Fall) t

Precharge Time

Pulse Width

Hold Time

Hold Time

Pulse Width

to CAS Delay Time

to Column Address Delay Time

to

Precharge Time

Row Address Setup Time t

Row Address Hold Time t

Column Address Setup Time t

Column Address Hold Time t

Column Address Hold Time Referenced

to

Column Address Lead Time Referenced

to

Read Command Setup Time t

Read Command Hold Time Referenced

to

Read Command Hold Time Referenced

to

Hold Time Referenced to

Write Command Hold Time Referenced

to

RC

RWC

t

RAC

t

CAC

AA

t

CLZ

t

OFF

T

t

RP

t

RAS

t

RSH

t

CSH

t

CAS

t

RCD

t

RAD

t

CRP

ASR

RAH

ASC

CAH

t

AR

t

RAL

RCS

t

RRH

t

RCH

t

WCH

t

WCR

75 - 90 - 110 - ns

120 - 140 - 160 - ns

- 40 - 50 - 60 ns 3,4

- 12 - 13 - 15 ns 3,4

- 20 - 25 - 30 ns 3,4

0 - 0 - 0 - ns 3

0 8

3 50

25 40 10000

12 40 12 10000

16 30

11 22

5 0 -

6 0 6 -

30 -

20 -

0 0 -

0 -

6 -

30 -

Preliminary Aug 1999 (Rev.2.1)

0 10 0 13

3 50 3 50

30 - 40 50 10000 60 10000

13 - 15 50 - 60 13 10000 15 10000

18 37 20 45

13 25 15 30

5 - 5 0 - 0 -

8 - 10 0 - 0 8 - 10 -

40 - 45 -

25 - 30 -

0 - 0 0 - 0 -

0 - 0 -

7 - 10 -

40 - 45 -

GLT44108

ns 7

ns 2

ns

ns

ns

ns

ns

ns 4

ns 4

ns 8

ns

ns

ns

ns

ns

ns

ns

ns 9

ns 9

ns 10

ns 5

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No.24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 5 -

Loading...

Loading...