G-LINK GLT4160M04E-60TC, GLT4160M04E-60J3, GLT4160M04-70TC, GLT4160M04-70J3, GLT4160M04-60TC Datasheet

...

G-LINK

GLT4160M04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Jan 2000 (Rev. 1.3)

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 1 -

Features : Description :

∗ 4,194,304 words by 4 bits organization.

∗ Fast access time and cycle time

∗ Low power dissipation.

∗ Read-Modify-Write,

RAS

-Only Refresh,

CAS

-Before-

RAS

Refresh, Hidden Refresh.

∗ 2,048 refresh cycles per 32ms.

∗ Available in 300 mil 26(24) SOJ and TSOPII.

∗ 2.5V±0.2V Vcc Power Supply voltage.

∗ All inputs and Outputs are LVTTL

compatible.

∗ Extended Data-Out (EDO) Page access

cycle.

∗ Self-refresh Capability. (S-Version).

The GLT4160M04 is a highperformance CMOS dynamic random access

memory containing 16,777,216 bits

organized in a x4 configuration. The

GLT4160M04 offers page cycle access with

Extended Data Output. The GLT4160M04

has 11 row- and 11 column-addresses, and

accepts 2048-cycle refresh in 32 ms.

The GLT4160M04 provides EDO PAGE

MODE operation which allows for fast data

access within a row-address defined

boundary, up to 2048 x 4 bits with cycle

times as short as 25ns.

HIGH PERFORMANCE 60 70

Max.

RAS

Access Time, (t

RAC

)

60 ns 70 ns

Max. Column Address Access Time, (tAA) 30 ns 35 ns

Min. Extended Data Out Page Mode Cycle Time, (tPC) 25 ns 30 ns

Min. Read/Write Cycle Time, (tRC) 104 ns 124 ns

Max.

CAS

Access Time (t

CAC

)

15 ns 20 ns

G-LINK

GLT4160M04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Jan 2000 (Rev. 1.3)

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 2 -

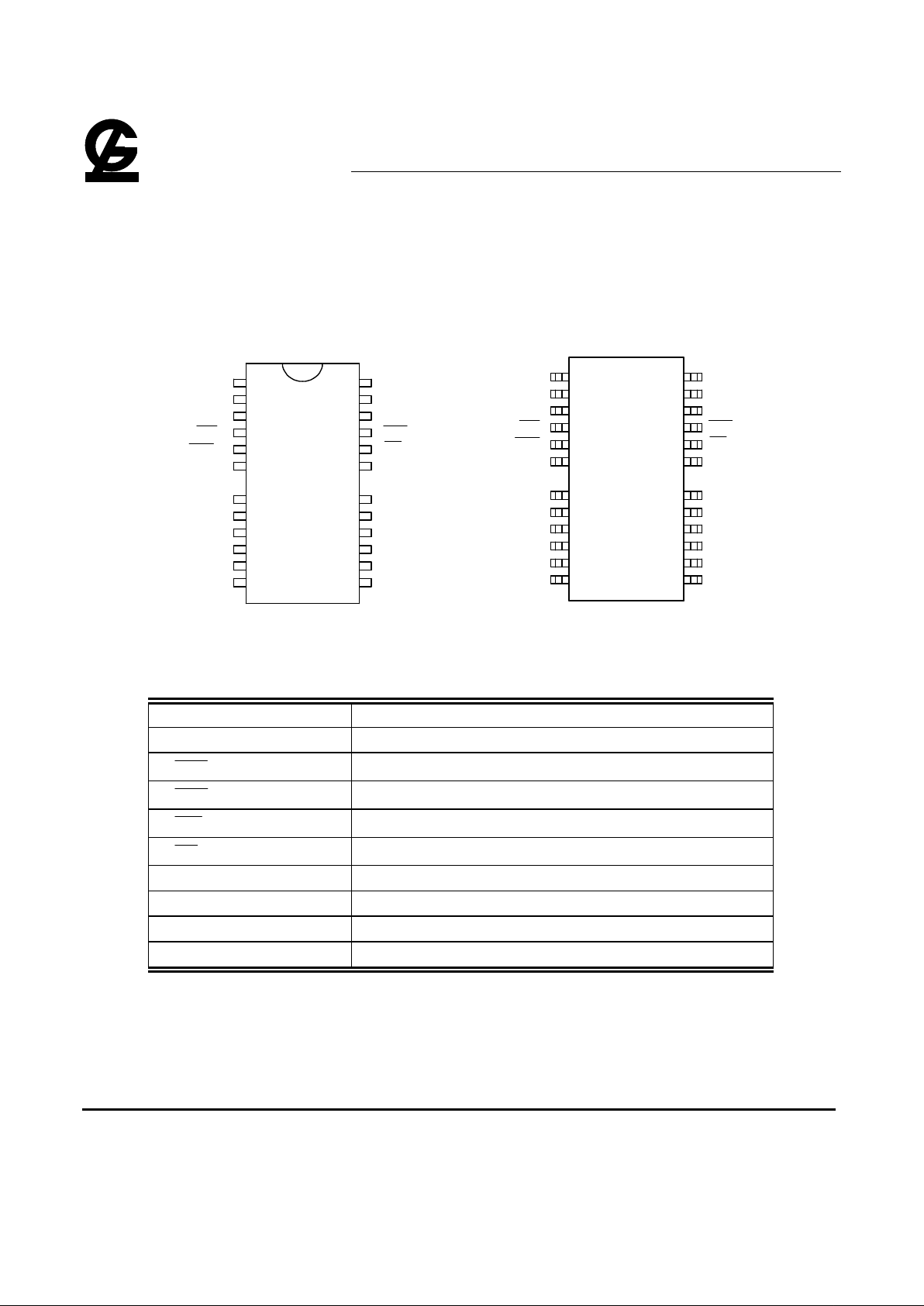

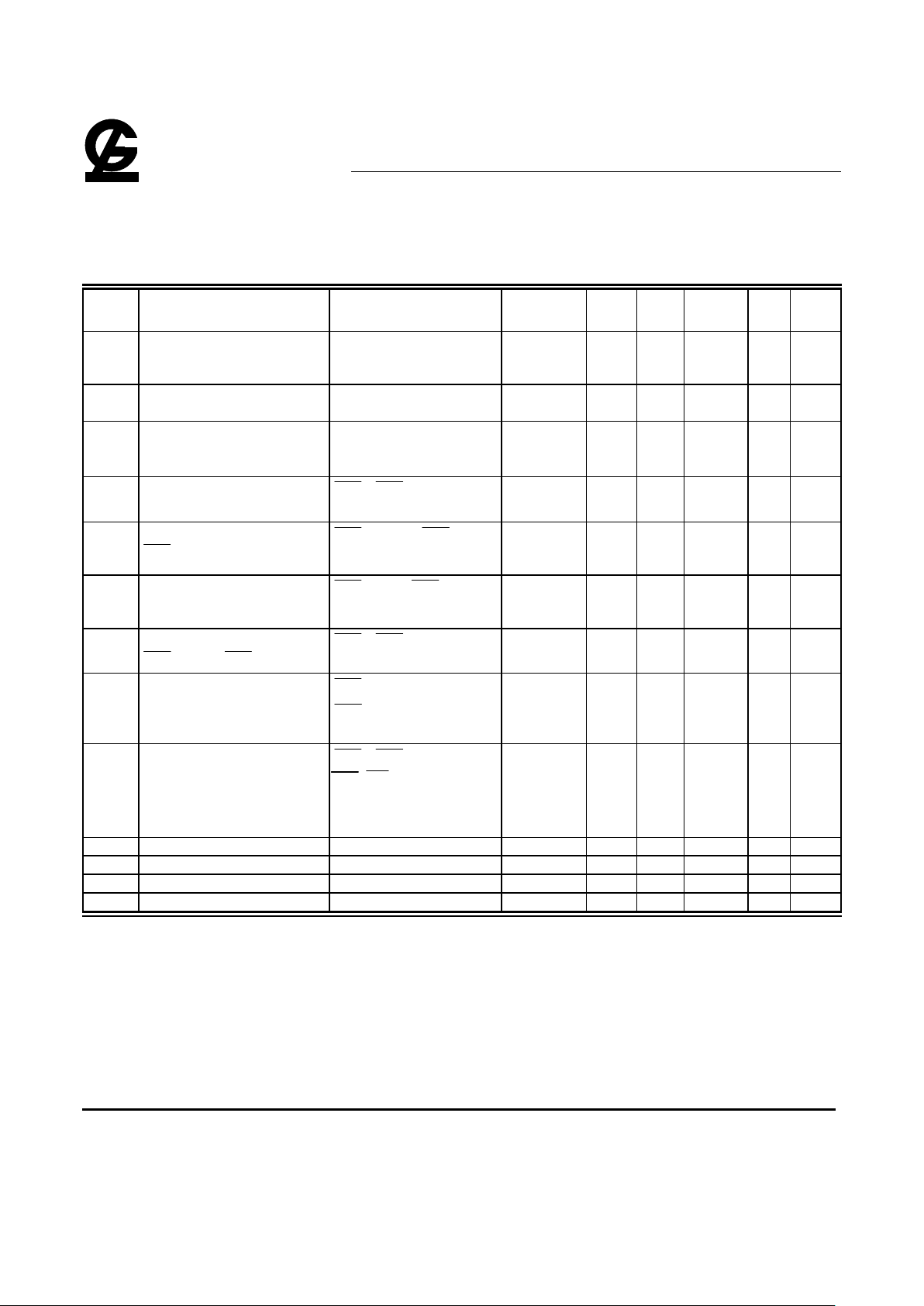

Pin Configuration :

Vcc

DQ0

A

0

A1

A2

A

3

1

2

3

4

5

6

8

9

10

11

12

13

22

21

19

18

17

16

15

14

26

25

24

23

A9

A

8

A7

A6

OE

CAS

VSS

DQ3

DQ1

WE

RAS

NC

VCC

DQ2

A5

A

4

VSS

A

10

Vcc

DQ0

A10

A0

A1

A2

A3

1

2

3

4

5

6

8

9

10

11

12

13

22

21

19

18

17

16

15

14

26

25

24

23

A9

A8

A7

A6

OE

CAS

VSS

DQ3

DQ1

WE

RAS

NC

VCC

DQ2

A5

A4

VSS

Pin Descriptions:

Name Function

A0 - A

10

Address Inputs

RAS

Row Address Strobe

CAS

Column Address Strobe

WE

Write Enable

OE

Output Enable

DQ0 - DQ

3

Data Inputs / Outputs

V

CC

+2.5V Power Supply

V

SS

Ground

NC No Connection

GLT4160M04

300mil 26(24) TSOPII

GLT4160M04

300mil 26(24) SOJ

G-LINK

GLT4160M04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Jan 2000 (Rev. 1.3)

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 3 -

Absolute Maximum Ratings* Capacitance*

TA=25°C, VCC=2.5V±0.2V, VSS=0V

Operating Temperature, TA (ambient)

.............................................….0°C to

+70°C

For Extended Temperature……………..-20°C to 85°C

Storage Temperature(plastic)............-55°C to +150°C

Voltage Relative to VSS........................-0.5V to + 4.6V

Short Circuit Output Current...............................20mA

Power Dissipation...............................................1.0W

Symbol

C

IN1

C

IN2

C

OUT

Parameter

Address Input

RAS, CAS, WE, OE

Data Input/Output

Max.

5

7

7

Unit

pF

pF

pF

*Note: Operation above Absolute Maximum Ratings can

aversely affect device reliability.

*Note: Capacitance is sampled and not 100% tested

Electrical Specifications

l All voltages are referenced to GND.

l After power up, wait more than 200µs and then, execute eight

CAS

-before-

RAS

or

RAS

-only

refresh cycles as dummy cycles to initialize internal circuit.

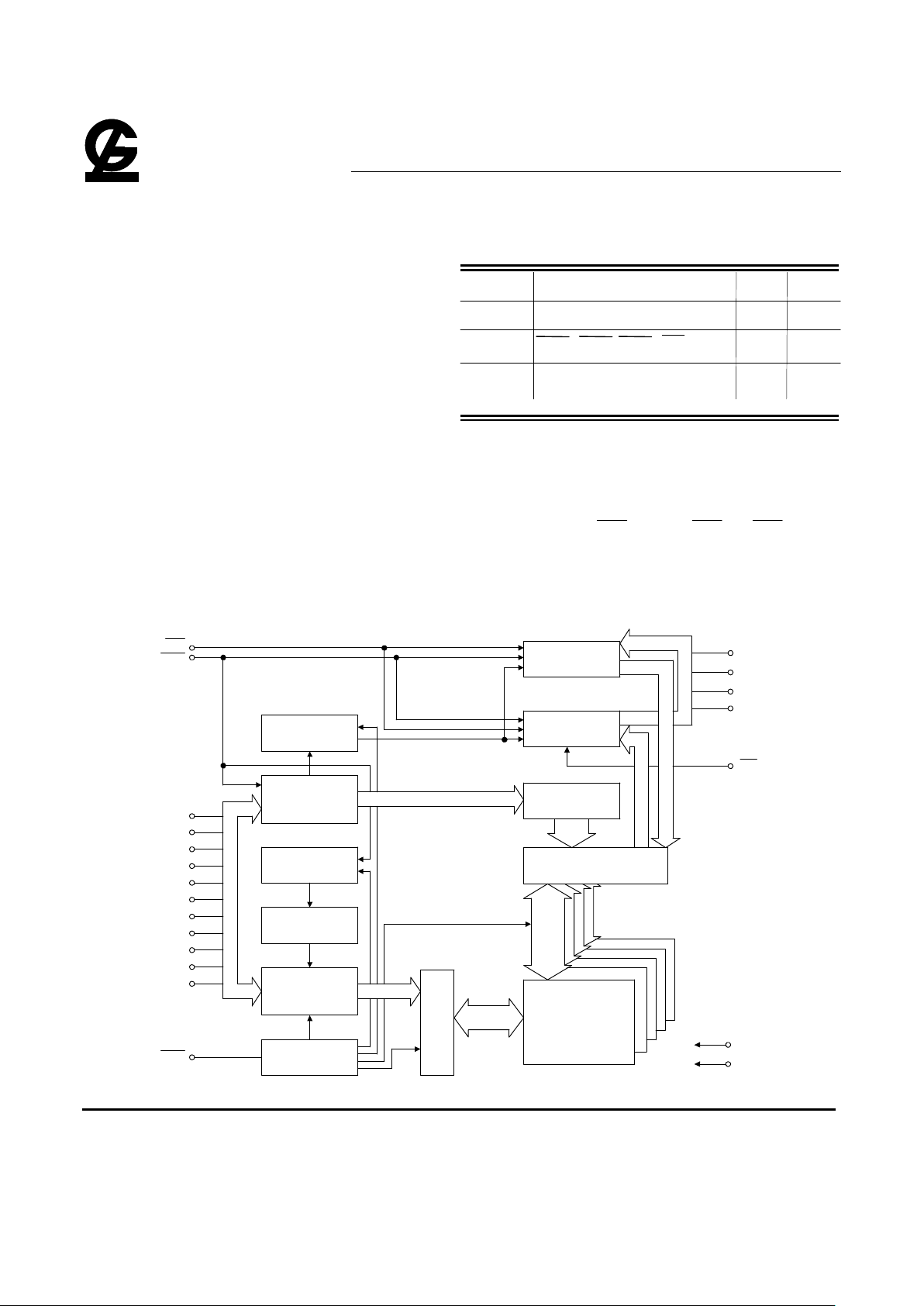

Block Diagram :

NO.2 CLOCK

GENERATOR

COLUMN-

ADDRESS

BUFFER(11)

REFRESH

CONTROLLER

REFRESH

COUNTER

ROW

ADDRESS

BUFFERS(11)

NO.1 CLOCK

GENERATOR

11

11

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

RAS

11

11

COLUMN

DECODER

DATA-OUT

BUFFER

DATA-IN

BUFFER

SENSE AMPLIFIERS

I/O GATING

2048 x 1024 x 4

MEMORY

ARRAY

2048

2048

4

4

4

4

WE

CAS

DQ0

DQ1

DQ2

DQ3

OE

VDD

VSS

ROW DECODER

2048

A0

G-LINK

GLT4160M04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Jan 2000 (Rev. 1.3)

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 4 -

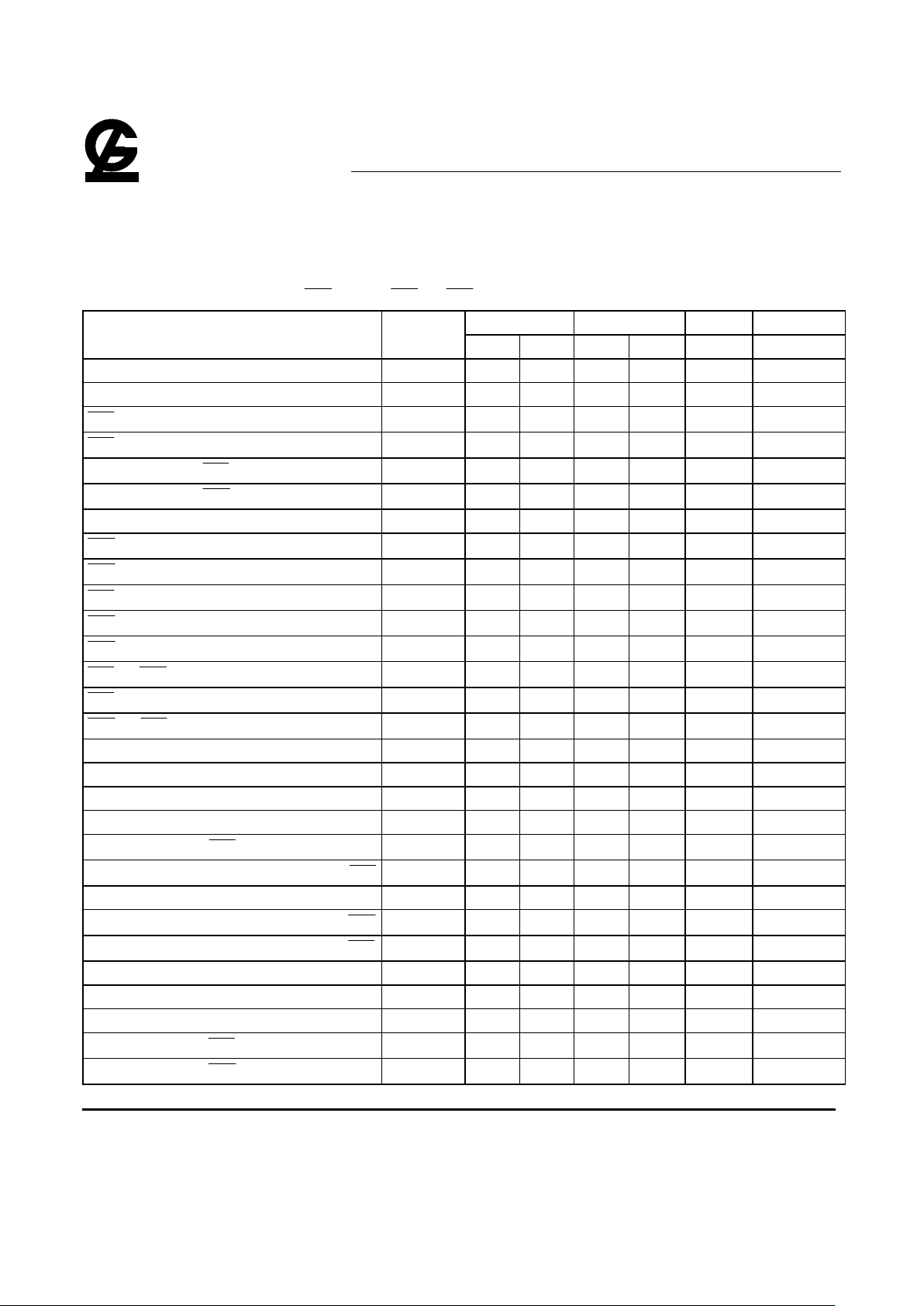

Truth Table:

Function

RAS

CAS

WE

OE

ADDRESS DATA-IN/OUT

t

R

t

C

DQ1-DQ4

Standby H

H→X

X X X X High-Z

READ L L H L ROW COL Data-Out

EARLY WRITE L L L X ROW COL Data-In

READ WRITE L L

H→L L→H

ROW COL Data-Out,Data-In

EDO-PAGE-MODE 1st Cycle L

H→L

H L ROW COL Data-Out

READ 2nd cycle L

H→L

H L n/a COL Data-Out

EDO-PAGE-MODE 1st Cycle L

H→L

L X ROW COL Data-In

EARLY-WRITE 2nd cycle L

H→L

L X n/a COL Data-In

EDO-PAGE-MODE 1st Cycle L

H→L H→L L→H

ROW COL Data-Out,Data-In

READ-WRITE 2nd cycle L

H→L H→L L→H

n/a COL Data-Out,Data-In

RAS

-ONLY REFRESH

L H X X ROW n/a High-Z

HIDDEN REFRESH READ

L→H→L

L H L ROW COL Data-Out

WRITE

L→H→L

L L X ROW COL Data-In

CBR REFRESH

H→L

L H X X X High-Z

SELF REFRESH

H→L

L H X X X High-Z

G-LINK

GLT4160M04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Jan 2000 (Rev. 1.3)

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 5 -

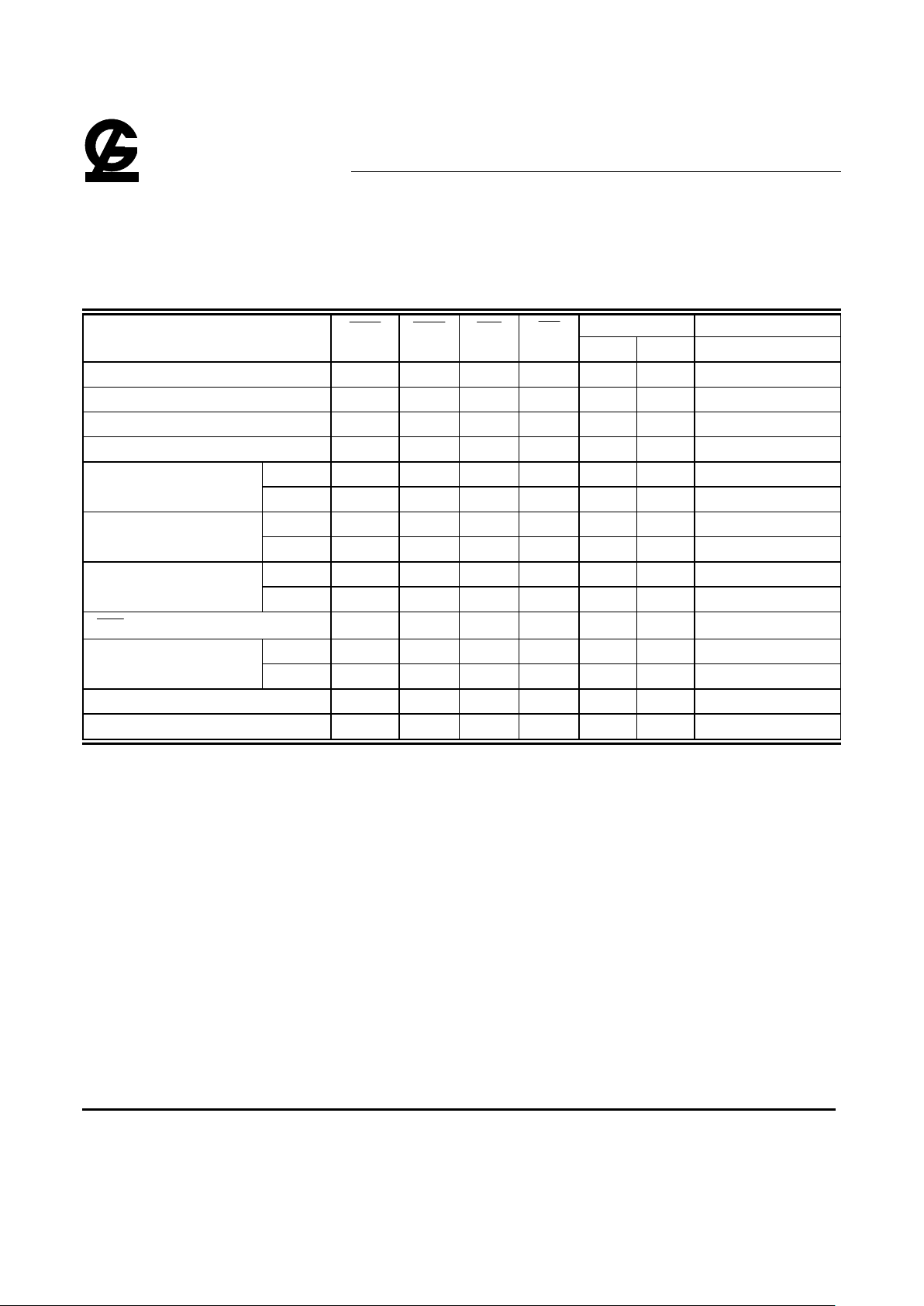

DC and Operating Characteristics (1-2)

TA = 0°C to 70°C, -20°C to 85°C VCC=2.5V±0.2V, VSS=0V, unless otherwise specified.

Sym. Parameter Test Conditions Access

Time

Min. Typ Max. Unit Notes

I

LI

Input Leakage Current

(any input pin)

0V ≤ V

IN

≤ VCC+0.3V

(All other pins not under

test=0V)

-5 +5

µA

I

LO

Output Leakage Current

(for High-Z State)

0V ≤ V

out

≤ V

CC

Output is disabled (Hiz)

-5 +5

µA

I

CC1

Operating Current,

Random READ/WRITE

tRC = tRC (min.) t

RAC

= 60ns

t

RAC

= 70ns

80

70 mA

1,2

I

CC2

Standby Current, (TTL)

RAS, CAS

at V

IH

other inputs ≥V

SS

1 mA

I

CC3

Refresh Current,

RAS

-Only

RAS

cycling,

CAS

at V

IH

tRC = tRC (min.)

t

RAC

= 60ns

t

RAC

= 70ns

80

70 mA

2

I

CC4

Operating Current,

EDO Page Mode

RAS

at VIL,

CAS

address

cycling:tPC=tPC(min.)

t

RAC

= 60ns

t

RAC

= 70ns

80

70 mA

1,2

I

CC5

Refresh Current,

CAS

Before

RAS

RAS, CAS

address

cycling: tRC=tRC (min.)

t

RAC

= 60ns

t

RAC

= 70ns

80

70

mA 1

I

CC6

Standby Current, (CMOS)

RAS

≥VCC-0.2V,

CAS

≥VCC-0.2V,

All other inputs V

SS

200

µA

1

I

CC7

Self refresh Current

RAS=CAS

=0.2V,

WE = OE = A0~A10=VCC-

0.2V or 0.2V

DQ0~DQ3=VCC-0.2V,0.2V

or Open

200

µA

V

IL

Input Low Voltage -0.3 +0.8 V 3

V

IH

Input High Voltage 2.0 VCC+0.3 V 4

V

OL

Output Low Voltage IOL = 2mA 0.4 V

V

OH

Output High Voltage IOH = -2mA 1.8 V

Notes:

1. ICC is dependent on output loading when the device output is selected. Specified ICC(max.) is measured with the output

open.

2. ICC is dependent upon the number of address transitions specified ICC(max.) is measured with a maximum of one

transition per address cycle in random Read/Write and EDO Fast Page Mode.

3. Specified VIL(min.) is steady state operation. During transitions VIL(min.) may undershoot to –0.9V for a period not to

exceed 10ns. All AC parameters are measured with VIL(min.)≥VSS and VIH(max.)≤VCC.

4. Specified VIH(max.) is steady state operation . During transitions VIH(max.) may overshoot to VCC+0.9V for a period not

to exceed 10ns. All AC parameters are measured with VIL(min.) ≥ VSS and VIH(max.) ≤ VCC .

G-LINK

GLT4160M04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Jan 2000 (Rev. 1.3)

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 6 -

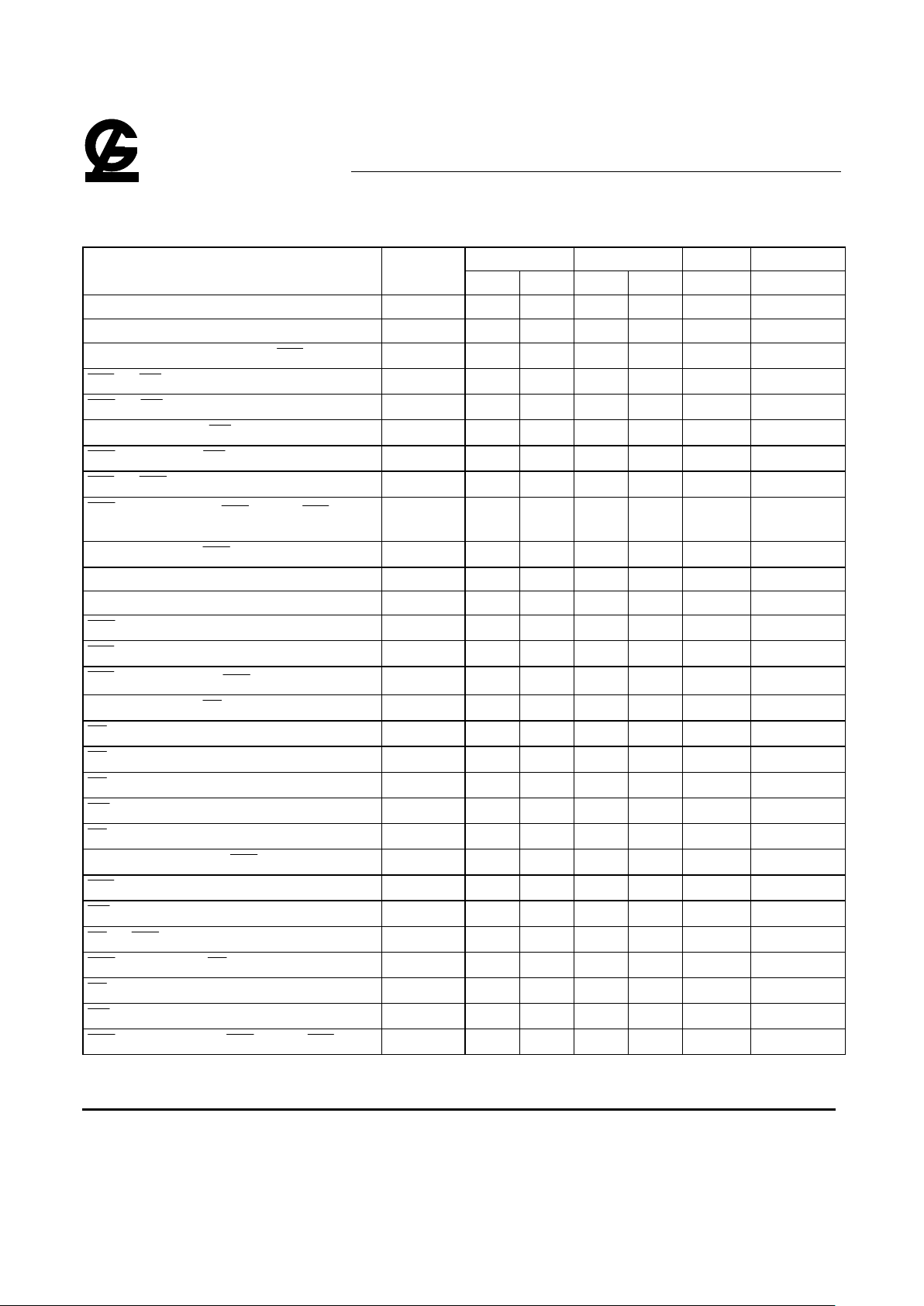

AC Characteristics

TA = 0°C to 70°C , -20°C to 85°C VCC = 2.5 V ± 0.2V, VIH/VIL = 2.0/0.8 V, VOH/VOL = 1.6/0.6V

An initial pause of 200 µs and 8

CAS

-before-

RAS

or

RAS

-only refresh cycles are required after power-up.

60 70

Parameter Symbol Min. Max. Min. Max. Unit Notes

Read or Write Cycle Time

t

RC

104 124 ns

Read Modify Write Cycle Time

t

RWC

140 170 ns

RAS

Precharge Time

t

RP

40 50 ns

RAS

Pulse Width

t

RAS

60 10k 70 10k ns

Access Time from

RAS

t

RAC

60 70 ns 1, 2, 3

Access Time from

CAS

t

CAC

15 20 ns 1, 5, 10

Access Time from Column Address

t

AA

30 35 ns 1, 5, 6

CAS

to Output Low-Z

t

CLZ

3 3 ns

CAS

to Output High-Z

t

CEZ

3 15 3 20 ns

RAS

Hold Time

t

RSH

15 20 ns

CAS

Hold Time

t

CSH

45 50 ns

CAS

Pulse Width

t

CAS

10 10k 15 10k ns

RAS

to

CAS

Delay Time

t

RCD

20 45 20 50 ns

RAS

to Column Address Delay Time

t

RAD

15 30 15 35 ns 7

CAS

to

RAS

Precharge Time

t

CRP

5 5 ns

Row Address Set-Up Time

t

ASR

0 0 ns

Row Address Hold Time

t

RAH

10 10 ns

Column Address Set-Up Time

t

ASC

0 0 ns

Column Address Hold Time

t

CAH

10 15 ns

Column Address to

RAS

Lead Time

t

RAL

30 35 ns

Column Address Hold Time Referenced to

RAS

t

AR

45 50 ns

Read Command Set-Up Time

t

RCS

0 0 ns

Read Command Hold Time Referenced to

CAS

t

RCH

0 0 ns 4

Read Command Hold Time Referenced to

RAS

t

RRH

0 0 ns 4

Write Command Set-Up Time

t

WCS

0 0 ns 8, 9

Write Command Hold Time

t

WCH

10 15 ns

Write Command Pulse Width

t

WP

10 15 ns

Write Command to

RAS

Lead Time

t

RWL

15 30 ns

Write Command to

CAS

Lead Time

t

CWL

10 15

ns

G-LINK

GLT4160M04

4M X 4 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Jan 2000 (Rev. 1.3)

G-Link Technology

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation,Taiwan

6F, No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 7 -

AC Characteristics

60 70

Parameter Symbol Min. Max. Min. Max. Unit Notes

Data Set-Up Time

t

DS

0 0 ns

Data Hold Time

t

DH

10 15 ns

Data Hold Time Referenced to

RAS

t

DHR

45 50 ns

RAS

to WE Delay Time

t

RWD

79 94 ns

CAS

to WE Delay Time

t

CWD

34 44 ns

Column Address to WE Delay Time

t

AWD

49 59 ns

CAS

Precharge to

WE

Delay

t

CPWD

54 64 ns

RAS

to

CAS

Precharge Time

t

RPC

5 5 ns

CAS

precharge time

(

CAS

Before

RAS

counter test cycle)

t

CPT

20 25 ns

Access Time from

CAS

Precharge

t

CPA

35 40 ns

EDO Page Mode Cycle Time

t

PC

25 30 ns

EDO Page Mode Read-Modify-Write Cycle Time

t

PRWC

56 71 ns

CAS

Precharge Time (EDO Page Mode)

t

CP

10 10 ns

RAS

Pulse Width (EDO Page Mode Only)

t

RASP

60 100k 70 100k ns

RAS

Hold Time from

CAS

precharge

t

RHCP

35 40 ns

Access Time from

OE

t

OEA

15 0 20 ns 8

OE

to Data Delay Time

t

OED

15 20 ns

OE

to Output Low-Z

t

OLZ

0 0 ns

OE

to Output High-Z

t

OEZ

3 15 3 20 ns

WE

to Data Delay

t

WED

15 20 ns

OE

Command Hold Time

t

OEH

15 20 ns

Data Output Hold after

CAS

low

t

DOH

5 5 ns

RAS

to Output High-Z

t

REZ

3 15 3 20 ns

WE

to Output High-Z

t

WEZ

3 15 3 20 ns

OE

to

CAS

Hold Time

t

OCH

5 5 ns

CAS

Hold Time to

OE

t

CHO

5 5 ns

OE

Precharge Time

t

OEP

5 5 ns

WE

Puts width (EDO mixed read write cycle)

t

WPE

5 5 ns

CAS

Set-Up Time for

CAS

-before-

RAS

Cycle

t

CSR

5 5 ns

Loading...

Loading...