G-LINK GLT41216-45TC, GLT41216-45J4, GLT41216-40TC, GLT41216-40J4, GLT41216-35TC Datasheet

...

G-LINK

GLT41216

64K X 16 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Aug 1999 (Rev.2.1)

G-Link Technology Corporation

2701Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

2F, No.12, R&D Rd. II, Science-Based Industrial Park,

Hsin Chu, Taiwan, R.O.C.

- 1 -

Features : Description :

∗ 65,536 words by 16 bits organization.

∗ Fast access time and cycle time.

∗ Dual

WE

Input.

∗ Low power dissipation.

∗ Read-Modify-Write,

RAS

-Only Refresh,

CAS

-Before-

RAS

Refresh, Hidden

Refresh and Test Mode Capability.

∗ 256 refresh cycles per 4ms.

∗ Available in 40-pin 400 mil SOJ,and 40/44

pin TSOP(II).

∗ Single 5.0V±10% Power Supply, Except

5V+5%,-10% for 30ns TSOPII Package.

∗ All inputs and Outputs are TTL

compatible.

∗ Extended Data-Out(EDO) Page Mode

operation.

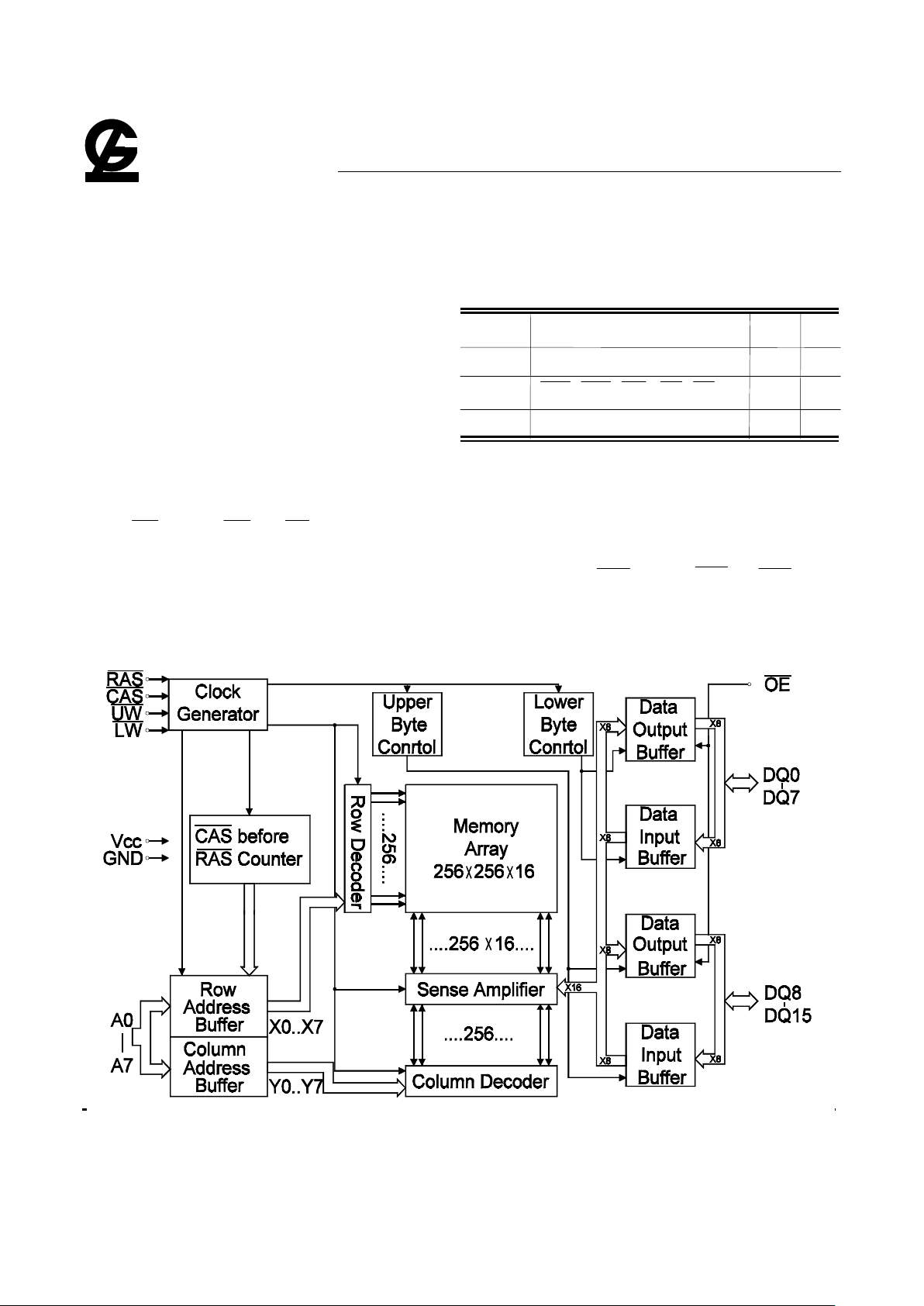

The GLT41216 is a 65,536 x 16 bit highperformance CMOS dynamic random access

memory. The GLT41216 offers Fast Page

mode with Extended Data Output, and has

both BYTE WRITE and WORD WRITE

access cycles via two WE pins. The

GLT41216 accepts 256-cycle refresh in 4ms

interval.

All inputs are TTL compatible. EDO

Page Mode operation allows random access

up to 256 x 16 bits, within a page, with cycle

times as short as 12ns.

The GLT41216 is best suited for

graphics, and DSP applications requiring

high performance memories.

HIGH PERFORMANCE 30 35 40 45

Max.

RAS

Access Time, (t

RAC

)

30 ns 35 ns 40 ns 45 ns

Max. Column Address Access Time, (tAA) 15 ns 18 ns 20 ns 22 ns

Min. Extended Data Out Page Mode Cycle Time, (tPC) 12 ns 13 ns 15 ns 18 ns

Min. Read/Write Cycle Time, (tRC) 65 ns 70 ns 75 ns 80 ns

Max.

CAS

Access Time (t

CAC

)

10 ns 11 ns 12 ns 12 ns

G-LINK

GLT41216

64K X 16 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Aug 1999 (Rev.2.1)

G-Link Technology Corporation

2701Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

2F, No.12, R&D Rd. II, Science-Based Industrial Park,

Hsin Chu, Taiwan, R.O.C.

- 2 -

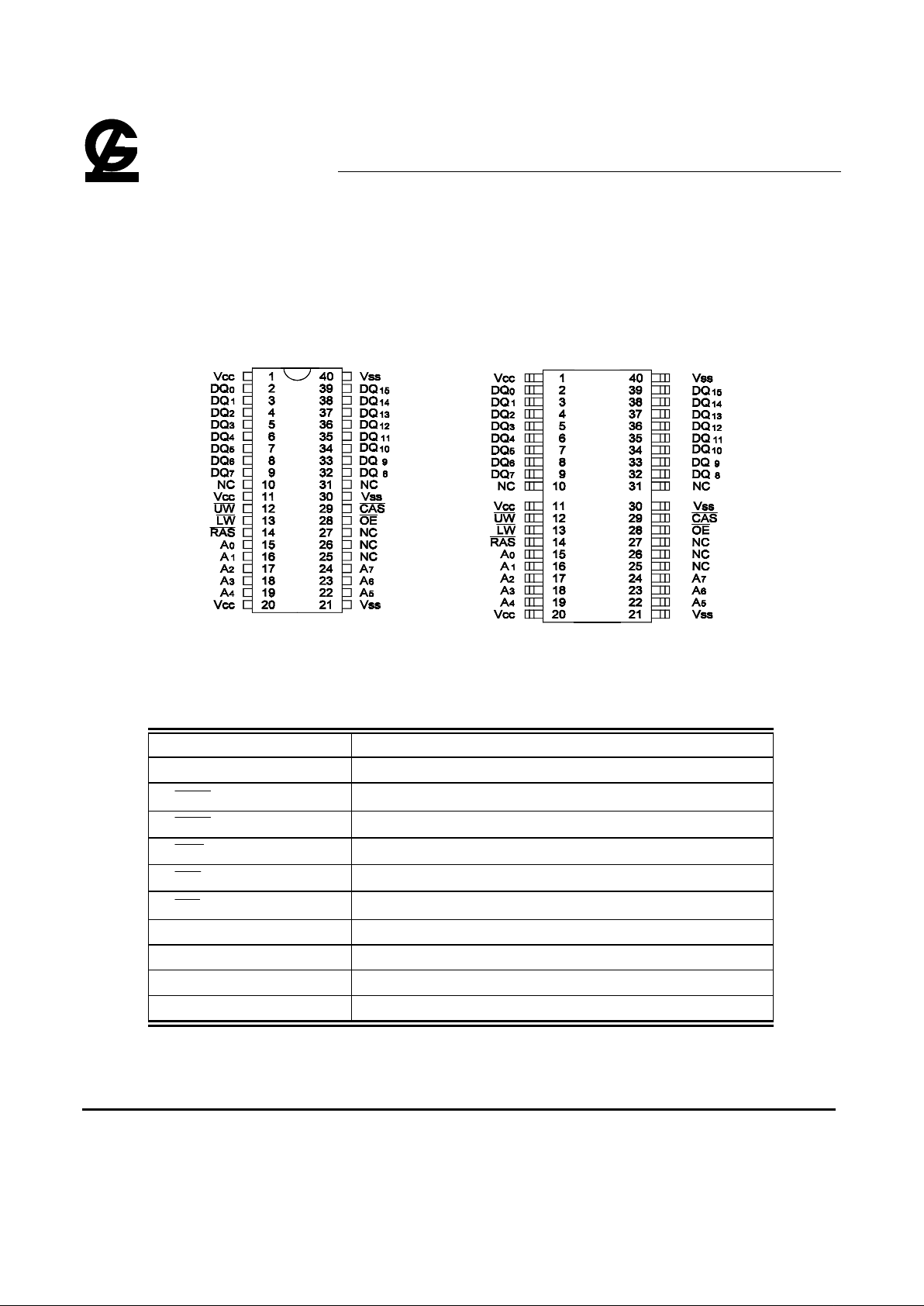

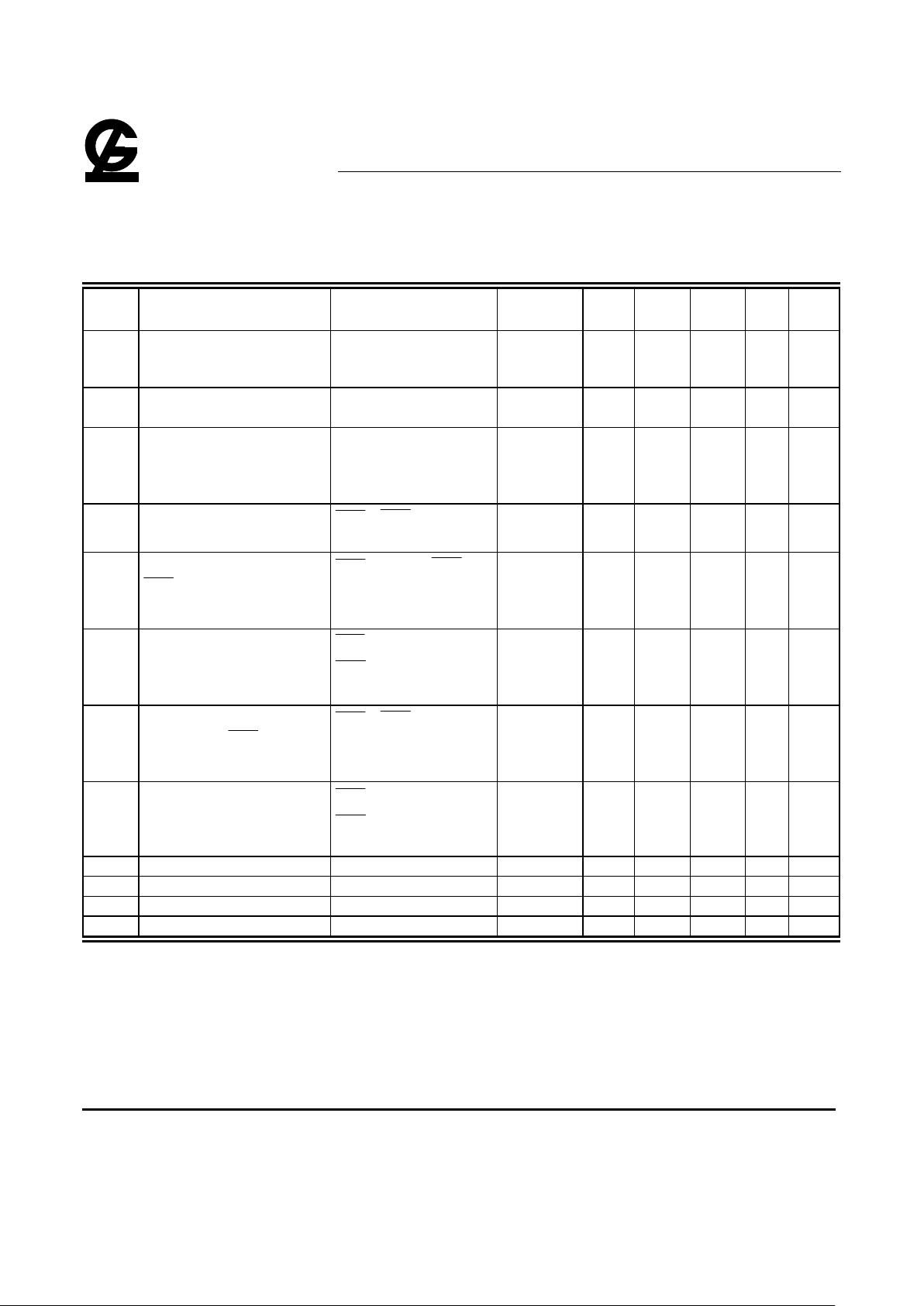

Pin Configuration :

Pin Descriptions:

Name Function

A0 - A

7

Address Inputs

RAS

Row Address Strobe

CAS

Column Address Strobe

UW

Read/Upper Byte Write Enable

LW

Read/Lower Byte Write Enable

OE

Output Enable

DQ0 - DQ

15

Data Inputs / Outputs

V

CC

+5V Power Supply

V

SS

Ground

NC No Connection

GLT41216

SOJ Top View

TSOP(Type II)

Top View

G-LINK

GLT41216

64K X 16 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Aug 1999 (Rev.2.1)

G-Link Technology Corporation

2701Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

2F, No.12, R&D Rd. II, Science-Based Industrial Park,

Hsin Chu, Taiwan, R.O.C.

- 3 -

Absolute Maximum Ratings* Capacitance*

TA=25°C, VCC=5V±10%, VSS=0V

Operating Temperature, TA (ambient)

.......................................-0°C to +70°C

Storage Temperature(plastic)....-55°C to +150°C

Voltage Relative to VSS...............-1.0V to + 7.0V

Short Circuit Output Current......................50mA

Power Dissipation......................................1.0W

Symbol

C

IN1

C

IN2

C

OUT

Parameter

Address Input

RAS

,

CAS,UW, LW,OE

Data Input/ Output

Max.

5

7

7

Unit

pF

pF

pF

*Note: Operation above Absolute Maximum Ratings

can adversely affect device reliability.

*Note: Capacitance is sampled and not 100% tested

Electrical Specifications

l

WE

means

UW

andLW.

l All voltages are referenced to GND.

l After power up, wait more than 100µs and then, execute eight

CAS

-before-

RAS

or

RAS

-only

refresh cycles as dummy cycles to initialize internal circuit.

Block Diagram :

G-LINK

GLT41216

64K X 16 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Aug 1999 (Rev.2.1)

G-Link Technology Corporation

2701Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

2F, No.12, R&D Rd. II, Science-Based Industrial Park,

Hsin Chu, Taiwan, R.O.C.

- 4 -

Extended Data Output (EDO) Page Mode

The EDO page mode is a kind of page mode with enhanced features. The two major features

of the EDO page mode are as follows.

1. Data output time is extended.

In the EDO page mode, the output data is held to the next

CAS

cycle‘s falling edge,

instead of the rising edge. For this reason, valid data output time in the EDO page mode is

extended compared with the fast page mode (=data extend function). In the fast page mode,

the data output time becomes shorter as the

CAS

cycle time becomes shorter. Therefore, in

the EDO page mode, the timing margin in read cycle is larger than of the fast page mode

even if the

CAS

cycle time becomes shorter.

2. The

CAS

cycle time in the EDO page mode is shorter than that in the fast page mode.

In the EDO page mode, due to the data extend function, the

CAS

cycle time can be

shorter than in the fast page mode if the timing margin is the same.

Taking a device whose t

RAC

is 60ns as an example, the

CAS

cycle time in the EDO page

mode is 25ns while that in the fast page mode is 40ns.

In the EDO page mode, read (data out) and write (data in) cycles can be executed

repeatedly during one

RAS

cycle. The EDO page mode allows both read and write

operations during one cycle, but the performance is equivalent to that of the fast page mode

in that case.

G-LINK

GLT41216

64K X 16 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Aug 1999 (Rev.2.1)

G-Link Technology Corporation

2701Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

2F, No.12, R&D Rd. II, Science-Based Industrial Park,

Hsin Chu, Taiwan, R.O.C.

- 5 -

Truth Table: GLT41216

Function

RAS

CAS

UWLWOE

ADDRESS DQs Note

s

Standby H

H→X

X X X High-Z

Read: Word L L H H L ROW/COL Data Out

Write: Word(Early Write) L L L L X ROW/COL Data-In

Write: Lower Byte (Early) L L H L X ROW/COL Lower Byte,Data-In

Upper Byte,High-Z

Write: Upper Byte (Early) L L L H X ROW/COL Lower Byte,High-Z

Upper Byte,Data-In

Read Write L L

H→L H→L L→H

ROW/COL Data-Out,Data-In 1,2

EDO-Page- 1st Cycle L

H→L

H H L ROW/COL Data-Out 1

Mode Read 2nd Cycle L

H→L

H H L COL Data-Out 1

EDO-Page- 1st Cycle L

H→L

L L X ROW/COL Data-In 2

Mode Write

2nd Cycle L

H→L

L L X COL Data-In 2

EDO-Page-

1st Cycle L

H→L H→L H→L L→H

ROW/COL Data-Out,Data-In 1,2

Mode ReadWrite

2st Cycle L

H→L H→L H→L L→H

COL Data-Out,Data-In 1,2

Hidden Read

L→H→L

L H H L ROW/COL Data-Out 1

Refresh Write

L→H→L

L L L X ROW/COL Data-In 2,3

RAS

-Only Refresh

L H X X X ROW High-Z

CBR Refresh

H→L

L X X X High-Z

Notes:

1. These READ cycles are always WORD READ cycles.

2. These WRITE cycles may also be BYTE READ cycles (either

UW

or LW active).

3. EARLY WRITE only.

G-LINK

GLT41216

64K X 16 CMOS DYNAMIC RAM WITH EXTENDED DATA OUTPUT

Aug 1999 (Rev.2.1)

G-Link Technology Corporation

2701Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

2F, No.12, R&D Rd. II, Science-Based Industrial Park,

Hsin Chu, Taiwan, R.O.C.

- 6 -

DC and Operating Characteristics (1-2)

TA = 0°C to 70°C, VCC=5V±10%, VSS=0V, unless otherwise specified.

Sym. Parameter Test Conditions Access

Time

Min. Typ Max. Unit Notes

I

LI

Input Leakage Current

(any input pin)

0V ≤ V

IN

≤ 5.5V

(All other pins not under

test=0V)

-10 +10

µA

I

LO

Output Leakage Current

(for High-Z State)

0V ≤ V

out

≤ 5.5V

Output is disabled (Hiz)

-10 +10

µA

I

CC1

Operating Current,

Random READ/WRITE tRC = tRC (min.)

t

RAC

= 30ns

t

RAC

= 35ns

t

RAC

= 40ns

t

RAC

= 45ns

180

170

160

150

mA 1,2

I

CC2

Standby Current,(TTL)

RAS

,

CAS

, at V

IH

other inputs ≥V

SS

2 mA

I

CC3

Refresh Current,

RAS

-Only

RAS

cycling,

CAS

, at

V

IH

tRC = tRC (min.)

t

RAC

= 30ns

t

RAC

= 35ns

t

RAC

= 40ns

t

RAC

= 45ns

180

170

160

150

mA 2

I

CC4

Operating Current,

EDO Page Mode

RAS

at VIL,

CAS

address cycling:

t

PC

= tPC(min.)

t

RAC

= 30ns

t

RAC

= 35ns

t

RAC

= 40ns

t

RAC

= 45ns

180

170

160

150

mA 1,2

I

CC5

Refresh Current,

CAS Before

RAS

RAS

,

CAS

,

address cycling:

t

RC

= tRC (min.)

t

RAC

= 30ns

t

RAC

= 35ns

t

RAC

= 40ns

t

RAC

= 45ns

180

170

160

150

mA 1

I

CC6

Standby Current, (CMOS)

RAS

≥VCC-0.2V,

CAS

≥VCC-0.2V,

All other inputs V

SS

1 mA

V

IL

Input Low Voltage -1 +0.8 V 3

V

IH

Input High Voltage 2.4 VCC+1 V 3

V

OL

Output Low Voltage IOL = 4.2mA 0.4 V

V

OH

Output High Voltage IOH = -5mA 2.4 V

Notes:

1. I

CC

is dependent on output loading when the device output is selected. Specified ICC(max.) is measured with

the output open.

2. ICC is dependent upon the number of address transitions specified ICC(max.) is measured with a maximum of

one transition per address cycle in random Read/Write and EDO Fast Page Mode.

3.Specified VIL(min.) is steady state operation. During transitions VIL(min.) may undershoot to -1.0V for a period

not to exceed 20ns. All AC parameters are measured with VIL(min.)≥VSS and VIH(max.)≤VCC.

Loading...

Loading...