Page 1

GD32VF103 User Manual

GigaDevice Semiconductor Inc.

GD32VF103

RISC-V 32-bit MCU

User Manual

Revision 1.0

( Jun. 2019 )

1

Page 2

GD32VF103 User Manual

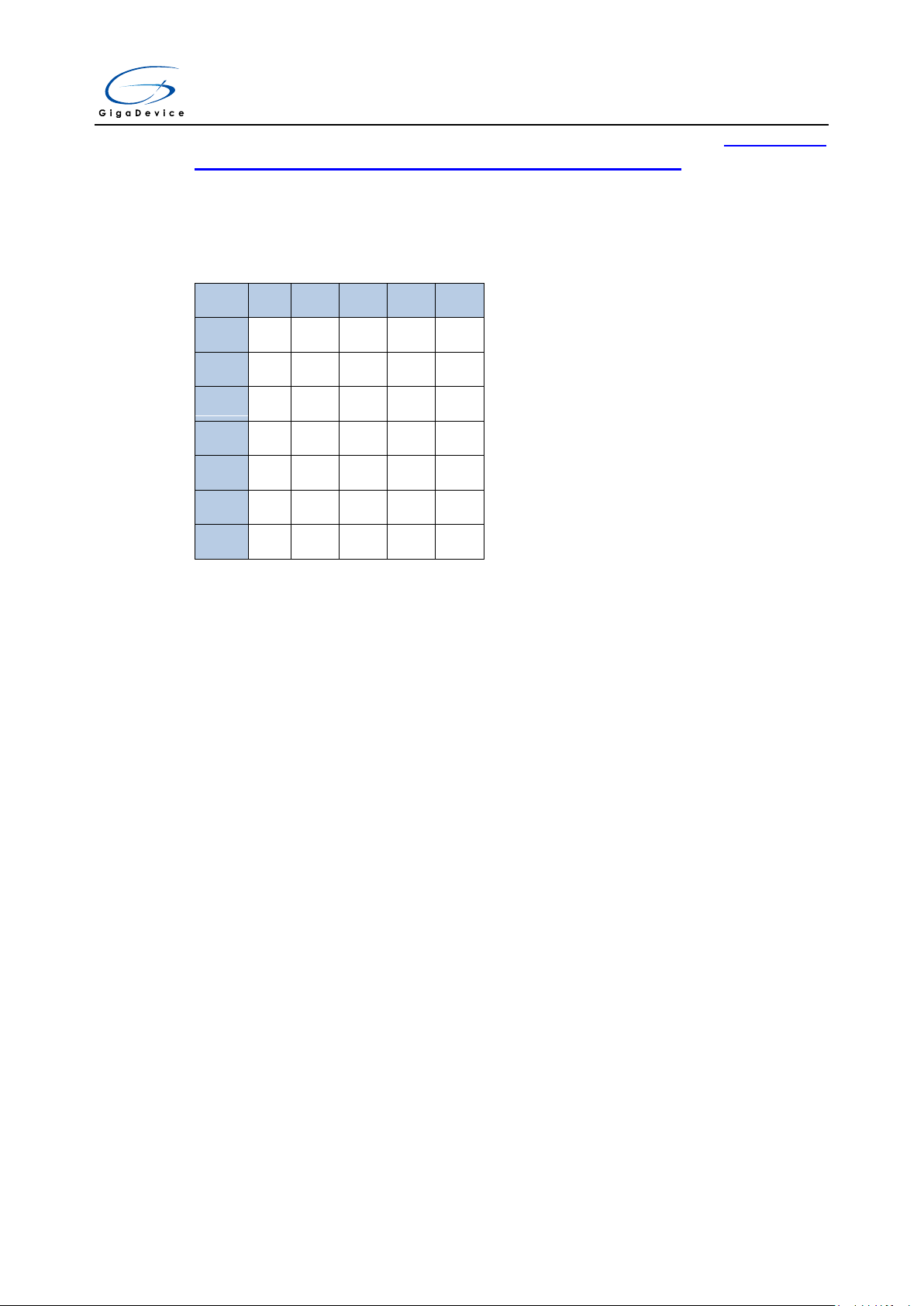

Table of Contents

Table of Contents ............................................................................................................... 2

List of Figures ................................................................................................................... 14

List of Tables ..................................................................................................................... 20

1. System and memory architecture ........................................................................... 22

1.1. RISC-V CPU ......................................................................................................................... 22

1.2. System architecture ............................................................................................................ 22

1.3. Memory map ..................................................................................................................... 24

1.3.1. On-chip SRAM memory ................................................................................................................... 28

1.3.2. On-chip flash memory overview ..................................................................................................... 28

1.4. Boot configuration ............................................................................................................. 29

1.5. Device electronic signature ................................................................................................. 29

1.5.1. Memory density information ............................................................................................................ 30

1.5.2. Unique device ID (96 bits) ............................................................................................................... 30

2. Flash memory controller (FMC) ............................................................................... 32

2.1. Overview ........................................................................................................................... 32

2.2. Characteristics .................................................................................................................... 32

2.3. Function overview .............................................................................................................. 32

2.3.1. Flash memory architecture .............................................................................................................. 32

2.3.2. Read operations ................................................................................................................................ 33

2.3.3. Unlock the FMC_CTL registers ...................................................................................................... 33

2.3.4. Page erase ........................................................................................................................................ 33

2.3.5. Mass erase ........................................................................................................................................ 34

2.3.6. Main flash programming .................................................................................................................. 35

2.3.7. Option bytes Erase ........................................................................................................................... 37

2.3.8. Option bytes modify .......................................................................................................................... 38

2.3.9. Option bytes description .................................................................................................................. 38

2.3.10. Page erase/program protection ...................................................................................................... 39

2.3.11. Security protection ............................................................................................................................ 40

2.4. Register definition .............................................................................................................. 41

2.4.1. Wait state register (FMC_WS) ........................................................................................................ 41

2.4.2. Unlock key register (FMC_KEY)..................................................................................................... 41

2.4.3. Option byte unlock key register (FMC_OBKEY) .......................................................................... 42

2.4.4. Status register (FMC_STAT) ........................................................................................................... 42

2.4.5. Control register (FMC_CTL) ............................................................................................................ 43

2.4.6. Address register (FMC_ADDR) ...................................................................................................... 44

2

Page 3

GD32VF103 User Manual

2.4.7. Option byte status register (FMC_OBSTAT) ................................................................................. 45

2.4.8. Erase/Program Protection register (FMC_WP) ............................................................................ 45

2.4.9. Product ID register (FMC_PID) ...................................................................................................... 46

3. Power management unit (PMU) ............................................................................... 47

3.1. Overview ........................................................................................................................... 47

3.2. Characteristics .................................................................................................................... 47

3.3. Function overview .............................................................................................................. 47

3.3.1. Battery backup domain .................................................................................................................... 48

3.3.2. VDD/V

3.3.3. 1.2V power domain ........................................................................................................................... 51

3.3.4. Power saving modes ........................................................................................................................ 51

power domain ................................................................................................................... 49

DDA

3.4. Register definition .............................................................................................................. 54

3.4.1. Control register (PMU_CTL) ........................................................................................................... 54

3.4.2. Control and status register (PMU_CS) .......................................................................................... 55

4. Backup registers (BKP) ............................................................................................ 57

4.1. Overview ........................................................................................................................... 57

4.2. Characteristics .................................................................................................................... 57

4.3. Function overview .............................................................................................................. 57

4.3.1. RTC clock calibration ....................................................................................................................... 57

4.3.2. Tamper detection .............................................................................................................................. 58

4.4. Register definition .............................................................................................................. 59

4.4.1. Backup data register x (BKP_DATAx) (x= 0..41) ......................................................................... 59

4.4.2. RTC signal output control register (BKP_OCTL) ......................................................................... 59

4.4.3. Tamper pin control register (BKP_TPCTL) ................................................................................... 60

4.4.4. Tamper control and status register (BKP_TPCS) ........................................................................ 60

5. Reset and clock unit (RCU) ...................................................................................... 62

5.1. Reset control unit (RCTL) .................................................................................................... 62

5.1.1. Overview ............................................................................................................................................ 62

5.1.2. Function overview ............................................................................................................................. 62

5.2. Clock control unit (CCTL) ..................................................................................................... 63

5.2.1. Overview ............................................................................................................................................ 63

5.2.2. Characteristics................................................................................................................................... 65

5.2.3. Function overview ............................................................................................................................. 65

5.3. Register definition .............................................................................................................. 69

5.3.1. Control register (RCU_CTL) ............................................................................................................ 69

5.3.2. Clock configuration register 0 (RCU_CFG0) ................................................................................ 71

5.3.3. Clock interrupt register (RCU_INT) ................................................................................................ 74

5.3.4. APB2 reset register (RCU_APB2RST) .......................................................................................... 77

3

Page 4

GD32VF103 User Manual

5.3.5. APB1 reset register (RCU_APB1RST) .......................................................................................... 79

5.3.6. AHB enable register (RCU_AHBEN) ............................................................................................. 82

5.3.7. APB2 enable register (RCU_APB2EN) ......................................................................................... 83

5.3.8. APB1 enable register (RCU_APB1EN) ......................................................................................... 85

5.3.9. Backup domain control register (RCU_BDCTL) .......................................................................... 87

5.3.10. Reset source/clock register (RCU_RSTSCK) .............................................................................. 88

5.3.11. AHB reset register (RCU_AHBRST) .............................................................................................. 90

5.3.12. Clock configuration register 1 (RCU_CFG1) ................................................................................ 91

5.3.13. Deep-sleep mode voltage register (RCU_DSV) .......................................................................... 93

6. Interrupt/event controller (EXTI) .............................................................................. 94

6.1. Overview ........................................................................................................................... 94

6.2. Characteristics .................................................................................................................... 94

6.3. Function overview .............................................................................................................. 94

6.4. External interrupt and event (EXTI) block diagram ............................................................... 97

6.5. External Interrupt and Event function overview .................................................................. 97

6.6. Register definition .............................................................................................................. 99

6.6.1. Interrupt enable register (EXTI_INTEN) ........................................................................................ 99

6.6.2. Event enable register (EXTI_EVEN) .............................................................................................. 99

6.6.3. Rising edge trigger enable register (EXTI_RTEN) ..................................................................... 100

6.6.4. Falling edge trigger enable register (EXTI_FTEN) .................................................................... 100

6.6.5. Software interrupt event register (EXTI_SWIEV) ....................................................................... 101

6.6.6. Pending register (EXTI_PD) .......................................................................................................... 101

7. General-purpose and alternate-function I/Os (GPIO and AFIO) ........................ 102

7.1. Overview ......................................................................................................................... 102

7.2. Characteristics .................................................................................................................. 102

7.3. Function overview ............................................................................................................ 102

7.3.1. GPIO pin configuration ................................................................................................................... 103

7.3.2. External interrupt/event lines ........................................................................................................ 104

7.3.3. Alternate functions (AF) ................................................................................................................. 104

7.3.4. Input configuration .......................................................................................................................... 104

7.3.5. Output configuration ....................................................................................................................... 105

7.3.6. Analog configuration ....................................................................................................................... 106

7.3.7. Alternate function (AF) configuration ........................................................................................... 106

7.3.8. IO pin function selection ................................................................................................................ 107

7.3.9. GPIO locking function .................................................................................................................... 107

7.4. Remapping function I/O and debug configuration ............................................................. 108

7.4.1. Introduction ...................................................................................................................................... 108

7.4.2. Main features ................................................................................................................................... 108

7.4.3. JTAG alternate function remapping ............................................................................................. 108

4

Page 5

GD32VF103 User Manual

7.4.4. TIMER AF remapping ..................................................................................................................... 109

7.4.5. USART AF remapping .................................................................................................................... 110

7.4.6. I2C0 AF remapping ......................................................................................................................... 110

7.4.7. SPI0 AF remapping ........................................................................................................................ 111

7.4.8. SPI2/I2S2 AF remapping ............................................................................................................... 111

7.4.9. CAN0 AF remapping ...................................................................................................................... 111

7.4.10. CAN1 AF remapping ...................................................................................................................... 111

7.4.11. CLK pins AF remapping ................................................................................................................. 112

7.5. Register definition ............................................................................................................ 113

7.5.1. Port control register 0 (GPIOx_CTL0, x=A..E) ........................................................................... 113

7.5.2. Port control register 1 (GPIOx_CTL1, x=A..E) ........................................................................... 115

7.5.3. Port input status register (GPIOx_ISTAT, x=A..E) ...................................................................... 116

7.5.4. Port output control register (GPIOx_OCTL, x=A..E) .................................................................. 117

7.5.5. Port bit operate register (GPIOx_BOP, x=A..E).......................................................................... 117

7.5.6. Port bit clear register (GPIOx_BC, x=A..E) ................................................................................. 118

7.5.7. Port configuration lock register (GPIOx_LOCK, x=A..E) .......................................................... 118

7.5.8. Event control register (AFIO_EC)................................................................................................. 119

7.5.9. AFIO port configuration register 0 (AFIO_PCF0) ....................................................................... 120

7.5.10. EXTI sources selection register 0 (AFIO_EXTISS0) ................................................................. 123

7.5.11. EXTI sources selection register 1 (AFIO_EXTISS1) ................................................................. 124

7.5.12. EXTI sources selection register 2 (AFIO_EXTISS2) ................................................................. 125

7.5.13. EXTI sources selection register 3 (AFIO_EXTISS3) ................................................................. 126

7.5.14. AFIO port configuration register 1 (AFIO_PCF1) ....................................................................... 127

8. CRC calculation unit (CRC) .................................................................................... 129

8.1. Overview ......................................................................................................................... 129

8.2. Characteristics .................................................................................................................. 129

8.3. Function overview ............................................................................................................ 130

8.4. Register definition ............................................................................................................ 131

8.4.1. Data register (CRC_DATA) ........................................................................................................... 131

8.4.2. Free data register (CRC_FDATA) ................................................................................................ 131

8.4.3. Control register (CRC_CTL) .......................................................................................................... 132

9. Direct memory access controller (DMA) .............................................................. 133

9.1. Overview ......................................................................................................................... 133

9.2. Characteristics .................................................................................................................. 133

9.3. Block diagram .................................................................................................................. 134

9.4. Function overview ............................................................................................................ 134

9.4.1. DMA operation................................................................................................................................. 134

9.4.2. Peripheral handshake .................................................................................................................... 136

9.4.3. Arbitration ......................................................................................................................................... 136

9.4.4. Address generation ........................................................................................................................ 137

5

Page 6

GD32VF103 User Manual

9.4.5. Circular mode .................................................................................................................................. 137

9.4.6. Memory to memory mode .............................................................................................................. 137

9.4.7. Channel configuration .................................................................................................................... 137

9.4.8. Interrupt ............................................................................................................................................ 138

9.4.9. DMA request mapping ................................................................................................................... 139

9.5. Register definition ............................................................................................................ 142

9.5.1. Interrupt flag register (DMA_INTF) ............................................................................................... 142

9.5.2. Interrupt flag clear register (DMA_INTC) .................................................................................... 143

9.5.3. Channel x control register (DMA_CHxCTL)................................................................................ 143

9.5.4. Channel x counter register (DMA_CHxCNT) .............................................................................. 145

9.5.5. Channel x peripheral base address register (DMA_CHxPADDR) ........................................... 146

9.5.6. Channel x memory base address register (DMA_CHxMADDR) ............................................. 146

10. Debug (DBG) ......................................................................................................... 148

10.1. Overview ...................................................................................................................... 148

10.2. JTAG function overview................................................................................................. 148

10.2.1. Pin assignment ................................................................................................................................ 148

10.2.2. JTAG daisy chained structure ....................................................................................................... 148

10.2.3. Debug reset ..................................................................................................................................... 149

10.3. Debug hold function overview ...................................................................................... 149

10.3.1. Debug support for power saving mode ....................................................................................... 149

10.3.2. Debug support for TIMER, I2C, WWDGT, FWDGT and CAN .................................................. 149

10.4. Register definition ........................................................................................................ 150

10.4.1. ID code register (DBG_ID) ............................................................................................................ 150

10.4.2. Control register (DBG_CTL) .......................................................................................................... 150

11. Analog-to-digital converter (ADC) ...................................................................... 153

11.1. Introduction ................................................................................................................. 153

11.2. Main features ............................................................................................................... 153

11.3. Pins and internal signals ................................................................................................ 154

11.4. Functional description .................................................................................................. 154

11.4.1. Calibration (CLB) ............................................................................................................................ 155

11.4.2. ADC clock ........................................................................................................................................ 156

11.4.3. ADCON switch ................................................................................................................................ 156

11.4.4. Regular and inserted channel groups .......................................................................................... 156

11.4.5. Conversion modes .......................................................................................................................... 156

11.4.6. Inserted channel management ..................................................................................................... 160

11.4.7. Data alignment ................................................................................................................................ 161

11.4.8. Programmable sample time .......................................................................................................... 162

11.4.9. External trigger ................................................................................................................................ 163

11.4.10. DMA request ................................................................................................................................ 163

11.4.11. Temperature sensor, and internal reference voltage V

................................................ 163

REFINT

6

Page 7

GD32VF103 User Manual

11.4.12. Programmable resolution (DRES) - fast conversion mode .................................................. 164

11.4.13. On-chip hardware oversampling .............................................................................................. 165

11.5. ADC sync mode ............................................................................................................. 166

11.6. Free mode .................................................................................................................... 167

11.6.1. Regular parallel mode .................................................................................................................... 168

11.6.2. Inserted parallel mode ................................................................................................................... 168

11.6.3. Follow-up fast mode ....................................................................................................................... 169

11.6.4. Follow-up slow mode ..................................................................................................................... 169

11.6.5. Trigger rotation mode ..................................................................................................................... 170

11.6.6. Combined regular parallel & inserted parallel mode ................................................................. 171

11.6.7. Combined regular parallel & trigger rotation mode .................................................................... 171

11.6.8. Combined inserted parallel & follow-up mode ............................................................................ 172

11.7. ADC interrupts .............................................................................................................. 173

11.8. ADC registers ................................................................................................................ 174

11.8.1. Status register (ADC_STAT) ......................................................................................................... 174

11.8.2. Control register 0 (ADC_CTL0) .................................................................................................... 175

11.8.3. Control register 1 (ADC_CTL1) .................................................................................................... 177

11.8.4. Sample time register 0 (ADC_SAMPT0) ..................................................................................... 179

11.8.5. Sample time register 1 (ADC_SAMPT1) ..................................................................................... 180

11.8.6. Inserted channel data offset register x (ADC_IOFFx) (x=0..3) ................................................ 181

11.8.7. Watchdog high threshold register (ADC_WDHT) ...................................................................... 181

11.8.8. Watchdog low threshold register (ADC_WDLT) ......................................................................... 182

11.8.9. Regular sequence register 0 (ADC_RSQ0) ................................................................................ 182

11.8.10. Regular sequence register 1 (ADC_RSQ1) ............................................................................ 183

11.8.11. Regular sequence register 2 (ADC_RSQ2) ............................................................................ 183

11.8.12. Inserted sequence register (ADC_ISQ) .................................................................................. 184

11.8.13. Inserted data register x (ADC_IDATAx) (x= 0..3) ................................................................... 185

11.8.14. Regular data register (ADC_RDATA) ...................................................................................... 185

11.8.15. Oversample control register (ADC_OVSAMPCTL) ............................................................... 186

12. Digital-to-analog converter (DAC) ...................................................................... 188

12.1. Overview ...................................................................................................................... 188

12.2. Characteristics .............................................................................................................. 188

12.3. Function overview ........................................................................................................ 189

12.3.1. DAC enable ..................................................................................................................................... 189

12.3.2. DAC output buffer ........................................................................................................................... 190

12.3.3. DAC data configuration .................................................................................................................. 190

12.3.4. DAC trigger ...................................................................................................................................... 190

12.3.5. DAC conversion .............................................................................................................................. 190

12.3.6. DAC noise wave ............................................................................................................................. 191

12.3.7. DAC output voltage ........................................................................................................................ 192

12.3.8. DMA request .................................................................................................................................... 192

7

Page 8

GD32VF103 User Manual

12.3.9. DAC concurrent conversion .......................................................................................................... 192

12.4. Register definition ........................................................................................................ 193

12.4.1. Control register (DAC_CTL) .......................................................................................................... 193

12.4.2. Software trigger register (DAC_SWT) ......................................................................................... 195

12.4.3. DAC0 12-bit right-aligned data holding register (DAC0_R12DH) ............................................ 196

12.4.4. DAC0 12-bit left-aligned data holding register (DAC0_L12DH) ............................................... 196

12.4.5. DAC0 8-bit right-aligned data holding register (DAC0_R8DH) ................................................ 197

12.4.6. DAC1 12-bit right-aligned data holding register (DAC1_R12DH) ............................................ 197

12.4.7. DAC1 12-bit left-aligned data holding register (DAC1_L12DH) ............................................... 198

12.4.8. DAC1 8-bit right-aligned data holding register (DAC1_R8DH) ................................................ 198

12.4.9. DAC concurrent mode 12-bit right-aligned data holding register (DACC_R12DH) .............. 199

12.4.10. DAC concurrent mode 12-bit left-aligned data holding register (DACC_L12DH) ............. 199

12.4.11. DAC concurrent mode 8-bit right-aligned data holding register (DACC_R8DH) .............. 200

12.4.12. DAC0 data output register (DAC0_DO) .................................................................................. 200

12.4.13. DAC1 data output register (DAC1_DO) .................................................................................. 201

13. Watchdog timer (WDGT) ...................................................................................... 202

13.1. Free watchdog timer (FWDGT) ...................................................................................... 202

13.1.1. Overview .......................................................................................................................................... 202

13.1.2. Characteristics................................................................................................................................. 202

13.1.3. Function overview ........................................................................................................................... 202

13.1.4. Register definition ........................................................................................................................... 205

13.2. Window watchdog timer (WWDGT) .............................................................................. 208

13.2.1. Overview .......................................................................................................................................... 208

13.2.2. Characteristics................................................................................................................................. 208

13.2.3. Function overview ........................................................................................................................... 208

13.2.4. Register definition ........................................................................................................................... 211

14. Real-time Clock (RTC) .......................................................................................... 213

14.1. Overview ...................................................................................................................... 213

14.2. Characteristics .............................................................................................................. 213

14.3. Function overview ........................................................................................................ 213

14.3.1. RTC reset ......................................................................................................................................... 214

14.3.2. RTC reading .................................................................................................................................... 214

14.3.3. RTC configuration ........................................................................................................................... 215

14.3.4. RTC flag assertion .......................................................................................................................... 215

14.4. Register definition ........................................................................................................ 217

14.4.1. RTC interrupt enable register(RTC_INTEN) ............................................................................... 217

14.4.2. RTC control register(RTC_CTL) ................................................................................................... 217

14.4.3. RTC prescaler high register (RTC_PSCH) ................................................................................. 218

14.4.4. RTC prescaler low register (RTC_PSCL) ................................................................................... 219

14.4.5. RTC divider high register (RTC_DIVH) ....................................................................................... 219

8

Page 9

GD32VF103 User Manual

14.4.6. RTC divider low register (RTC_DIVL) .......................................................................................... 219

14.4.7. RTC counter high register (RTC_CNTH) .................................................................................... 220

14.4.8. RTC counter low register (RTC_CNTL)....................................................................................... 220

14.4.9. RTC alarm high register (RTC_ALRMH) ..................................................................................... 221

14.4.10. RTC alarm low register (RTC_ALRML) ................................................................................... 221

15. Timer(TIMERx) ...................................................................................................... 222

15.1. Advanced timer (TIMERx, x=0) ...................................................................................... 223

15.1.1. Overview .......................................................................................................................................... 223

15.1.2. Characteristics................................................................................................................................. 223

15.1.3. Block diagram .................................................................................................................................. 224

15.1.4. Function overview ........................................................................................................................... 224

15.1.5. TIMERx registers(x=0) ................................................................................................................... 254

15.2. General level0 timer (TIMERx, x=1, 2, 3, 4) ..................................................................... 279

15.2.1. Overview .......................................................................................................................................... 279

15.2.2. Characteristics................................................................................................................................. 279

15.2.3. Block diagram .................................................................................................................................. 279

15.2.4. Function overview ........................................................................................................................... 280

15.2.5. TIMERx registers(x=1,2,3,4) ......................................................................................................... 297

15.3. Basic timer (TIMERx, x=5, 6) .......................................................................................... 318

15.3.1. Overview .......................................................................................................................................... 318

15.3.2. Characteristics................................................................................................................................. 318

15.3.3. Block diagram .................................................................................................................................. 318

15.3.4. Function overview ........................................................................................................................... 318

15.3.5. TIMERx registers(x=5,6) ................................................................................................................ 323

16. Universal synchronous/asynchronous receiver /transmitter (USART) ........ 328

16.1. Overview ...................................................................................................................... 328

16.2. Characteristics .............................................................................................................. 328

16.3. Function overview ........................................................................................................ 329

16.3.1. USART frame format ...................................................................................................................... 330

16.3.2. Baud rate generation ...................................................................................................................... 331

16.3.3. USART transmitter .......................................................................................................................... 331

16.3.4. USART receiver .............................................................................................................................. 333

16.3.5. Use DMA for data buffer access ................................................................................................... 334

16.3.6. Hardware flow control .................................................................................................................... 335

16.3.7. Multi-processor communication .................................................................................................... 336

16.3.8. LIN mode .......................................................................................................................................... 337

16.3.9. Synchronous mode ......................................................................................................................... 338

16.3.10. IrDA SIR ENDEC mode ............................................................................................................. 339

16.3.11. Half-duplex communication mode ............................................................................................ 341

16.3.12. Smartcard (ISO7816-3) mode .................................................................................................. 341

16.3.13. USART interrupts ........................................................................................................................ 342

9

Page 10

GD32VF103 User Manual

16.4. Register definition ........................................................................................................ 344

16.4.1. Status register (USART_STAT) .................................................................................................... 344

16.4.2. Data register (USART_DATA) ....................................................................................................... 346

16.4.3. Baud rate register (USART_BAUD) ............................................................................................. 346

16.4.4. Control register 0 (USART_CTL0) ............................................................................................... 347

16.4.5. Control register 1 (USART_CTL1) ............................................................................................... 349

16.4.6. Control register 2 (USART_CTL2) ............................................................................................... 350

16.4.7. Guard time and prescaler register (USART_GP) ....................................................................... 352

17. Inter-integrated circuit interface (I2C) ............................................................... 354

17.1. Overview ...................................................................................................................... 354

17.2. Characteristics .............................................................................................................. 354

17.3. Function overview ........................................................................................................ 354

17.3.1. SDA and SCL lines ......................................................................................................................... 355

17.3.2. Data validation................................................................................................................................. 356

17.3.3. START and STOP condition .......................................................................................................... 356

17.3.4. Clock synchronization .................................................................................................................... 356

17.3.5. Arbitration ......................................................................................................................................... 357

17.3.6. I2C communication flow ................................................................................................................. 357

17.3.7. Programming model ....................................................................................................................... 358

17.3.8. SCL line stretching .......................................................................................................................... 367

17.3.9. Use DMA for data transfer ............................................................................................................. 368

17.3.10. Packet error checking ................................................................................................................ 368

17.3.11. SMBus support ........................................................................................................................... 368

17.3.12. Status, errors and interrupts ..................................................................................................... 370

17.4. Register definition ........................................................................................................ 371

17.4.1. Control register 0 (I2C_CTL0)....................................................................................................... 371

17.4.2. Control register 1 (I2C_CTL1)....................................................................................................... 373

17.4.3. Slave address register 0 (I2C_SADDR0) .................................................................................... 374

17.4.4. Slave address register 1 (I2C_SADDR1) .................................................................................... 374

17.4.5. Transfer buffer register (I2C_DATA)............................................................................................. 375

17.4.6. Transfer status register 0 (I2C_STAT0) ....................................................................................... 375

17.4.7. Transfer status register 1 (I2C_STAT1) ....................................................................................... 377

17.4.8. Clock configure register (I2C_CKCFG) ....................................................................................... 378

17.4.9. Rise time register (I2C_RT)........................................................................................................... 379

18. Serial peripheral interface/Inter-IC sound (SPI/I2S) ......................................... 380

18.1. Overview ...................................................................................................................... 380

18.2. Characteristics .............................................................................................................. 380

18.2.1. SPI characteristics .......................................................................................................................... 380

18.2.2. I2S characteristics .......................................................................................................................... 380

18.3. SPI block diagram ......................................................................................................... 381

10

Page 11

GD32VF103 User Manual

18.4. SPI signal description .................................................................................................... 381

18.4.1. Normal configuration ...................................................................................................................... 381

18.5. SPI function overview ................................................................................................... 382

18.5.1. SPI clock timing and data format .................................................................................................. 382

18.5.2. NSS function .................................................................................................................................... 382

18.5.3. SPI operating modes ...................................................................................................................... 383

18.5.4. DMA function ................................................................................................................................... 389

18.5.5. CRC function ................................................................................................................................... 389

18.6. SPI interrupts ............................................................................................................... 389

18.6.1. Status flags ...................................................................................................................................... 389

18.6.2. Error flags ........................................................................................................................................ 390

18.7. I2S block diagram ......................................................................................................... 391

18.8. I2S signal description .................................................................................................... 391

18.9. I2S function overview ................................................................................................... 392

18.9.1. I2S audio standards ....................................................................................................................... 392

18.9.2. I2S clock ........................................................................................................................................... 400

18.9.3. Operation ......................................................................................................................................... 401

18.9.4. DMA function ................................................................................................................................... 403

18.10. I2S interrupts................................................................................................................ 404

18.10.1. Status flags .................................................................................................................................. 404

18.10.2. Error flags .................................................................................................................................... 404

18.11. Register definition ........................................................................................................ 406

18.11.1. Control register 0 (SPI_CTL0) .................................................................................................. 406

18.11.2. Control register 1 (SPI_CTL1) .................................................................................................. 408

18.11.3. Status register (SPI_STAT) ....................................................................................................... 409

18.11.4. Data register (SPI_DATA).......................................................................................................... 410

18.11.5. CRC polynomial register (SPI_CRCPOLY) ............................................................................ 411

18.11.6. RX CRC register (SPI_RCRC) ................................................................................................. 411

18.11.7. TX CRC register (SPI_TCRC) .................................................................................................. 412

18.11.8. I2S control register (SPI_I2SCTL) ........................................................................................... 413

18.11.9. I2S clock prescaler register (SPI_I2SPSC) ............................................................................ 414

19. External memory controller (EXMC) .................................................................. 416

19.1. Overview .................................................................................................................... 416

19.2. Characteristics .......................................................................................................... 416

19.3. Function overview .................................................................................................... 416

19.3.1. Block diagram .................................................................................................................................. 416

19.3.2. Basic regulation of EXMC access ................................................................................................ 417

19.3.3. External device address mapping ................................................................................................ 418

19.3.4. NOR/PSRAM controller ................................................................................................................. 418

11

Page 12

GD32VF103 User Manual

19.4. Register definition .................................................................................................... 424

19.4.1. NOR/PSRAM controller registers ................................................................................................. 424

20. Controller area network (CAN) ........................................................................... 427

20.1. Overview .................................................................................................................... 427

20.2. Characteristics .......................................................................................................... 427

20.3. Function overview .................................................................................................... 428

20.3.1. Working mode ................................................................................................................................. 428

20.3.2. Communication modes .................................................................................................................. 429

20.3.3. Data transmission ........................................................................................................................... 430

20.3.4. Data reception ................................................................................................................................. 432

20.3.5. Filtering function .............................................................................................................................. 433

20.3.6. Time-triggered communication ..................................................................................................... 436

20.3.7. Communication parameters .......................................................................................................... 437

20.3.8. Error flags ........................................................................................................................................ 438

20.3.9. CAN interrupts ................................................................................................................................. 439

20.4. Register definition .................................................................................................... 441

20.4.1. Control register (CAN_CTL) .......................................................................................................... 441

20.4.2. Status register (CAN_STAT) ......................................................................................................... 442

20.4.3. Transmit status register (CAN_TSTAT) ....................................................................................... 444

20.4.4. Receive message FIFO0 register (CAN_RFIFO0) .................................................................... 447

20.4.5. Receive message FIFO1 register (CAN_RFIFO1) .................................................................... 447

20.4.6. Interrupt enable register (CAN_INTEN) ...................................................................................... 448

20.4.7. Error register (CAN_ERR) ............................................................................................................. 450

20.4.8. Bit timing register (CAN_BT) ......................................................................................................... 451

20.4.9. Transmit mailbox identifier register (CAN_TMIx) (x=0..2) ........................................................ 452

20.4.10. Transmit mailbox property register (CAN_TMPx) (x=0..2) ................................................... 453

20.4.11. Transmit mailbox data0 register (CAN_TMDATA0x) (x=0..2) .............................................. 453

20.4.12. Transmit mailbox data1 register (CAN_TMDATA1x) (x=0..2) .............................................. 454

20.4.13. Receive FIFO mailbox identifier register (CAN_RFIFOMIx) (x=0,1) ................................... 454

20.4.14. Receive FIFO mailbox property register (CAN_RFIFOMPx) (x=0,1) .................................. 455

20.4.15. Receive FIFO mailbox data0 register (CAN_RFIFOMDATA0x) (x=0,1) ............................. 456

20.4.16. Receive FIFO mailbox data1 register (CAN_RFIFOMDATA1x) (x=0,1) ............................. 456

20.4.17. Filter control register (CAN_FCTL) .......................................................................................... 457

20.4.18. Filter mode configuration register (CAN_FMCFG) ................................................................ 457

20.4.19. Filter scale configuration register (CAN_FSCFG) ................................................................. 458

20.4.20. Filter associated FIFO register (CAN_FAFIFO) ..................................................................... 458

20.4.21. Filter working register (CAN_FW) ............................................................................................ 459

20.4.22. Filter x data y register (CAN_FxDATAy) (x=0..27, y=0,1) ..................................................... 459

21. Universal serial bus full-speed interface (USBFS) .......................................... 461

21.1. Overview ...................................................................................................................... 461

21.2. Characteristics .............................................................................................................. 461

12

Page 13

GD32VF103 User Manual

21.3. Block diagram ............................................................................................................... 462

21.4. Signal description ......................................................................................................... 462

21.5. Function overview ........................................................................................................ 462

21.5.1. USBFS clocks and working modes .............................................................................................. 462

21.5.2. USB host function ........................................................................................................................... 464

21.5.3. USB device function ....................................................................................................................... 466

21.5.4. OTG function overview .................................................................................................................. 467

21.5.5. Data FIFO ........................................................................................................................................ 468

21.5.6. Operation guide............................................................................................................................... 471

21.6. Interrupts ..................................................................................................................... 475

21.7. Register definition ........................................................................................................ 477

21.7.1. Global control and status registers ............................................................................................... 477

21.7.2. Host control and status registers .................................................................................................. 498

21.7.3. Device control and status registers .............................................................................................. 510

21.7.4. Power and clock control register (USBFS_PWRCLKCTL) ....................................................... 534

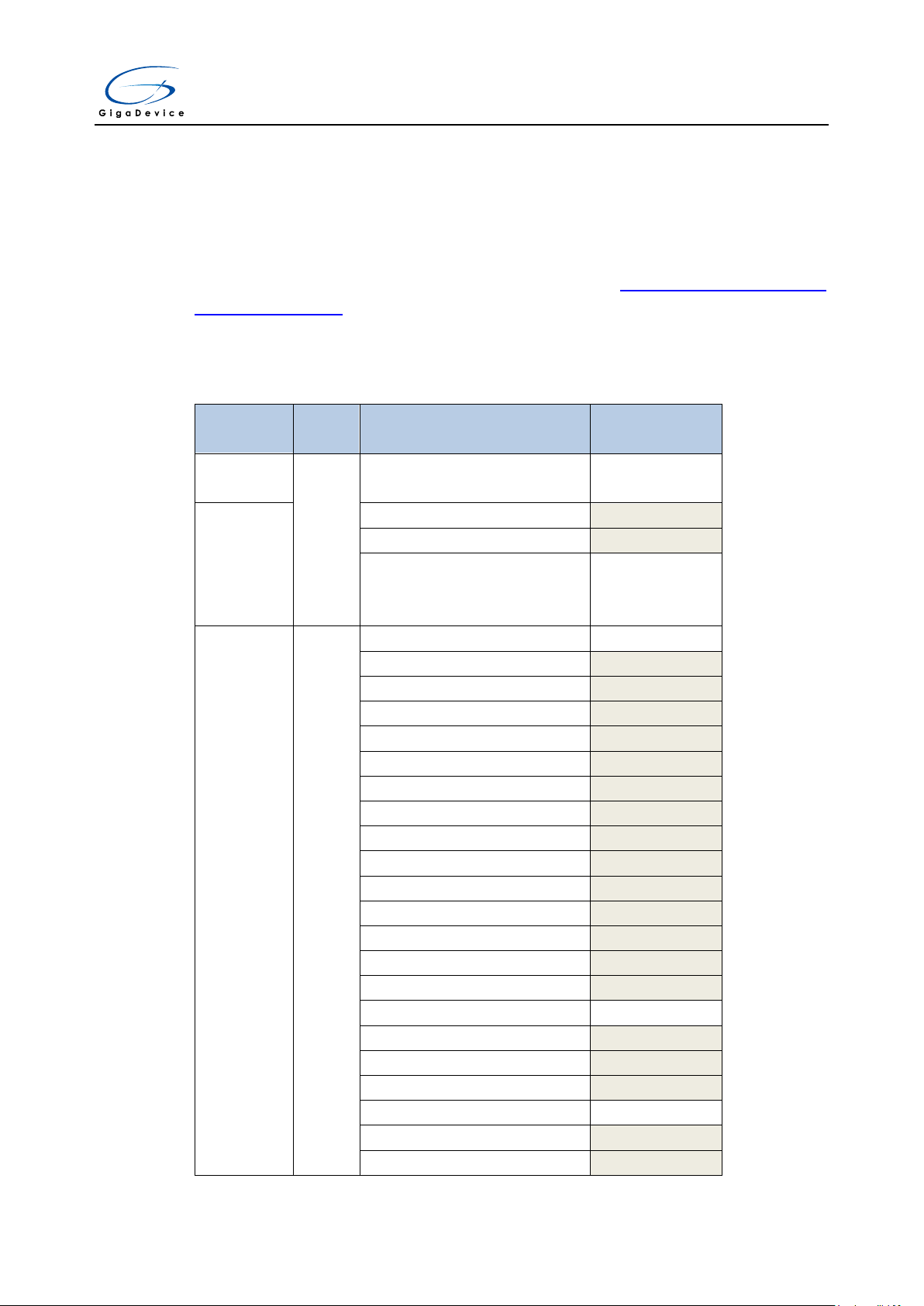

22. Revision history .................................................................................................... 535

13

Page 14

GD32VF103 User Manual

List of Figures

Figure 1-1. GD32VF103 system architecture ............................................................................................... 24

Figure 2-1. Process of page erase operation .............................................................................................. 34

Figure 2-2. Process of mass erase operation ............................................................................................. 35

Figure 2-3. Process of word program operation ........................................................................................ 37

Figure 3-1. Power supply overview ............................................................................................................... 48

Figure 3-2. Waveform of the POR/PDR ......................................................................................................... 50

Figure 3-3. Waveform of the LVD threshold ................................................................................................ 50

Figure 5-1. The system reset circuit ............................................................................................................. 63

Figure 5-2. Clock tree ...................................................................................................................................... 64

Figure 5-3. HXTAL clock source .................................................................................................................... 65

Figure 6-1. Block diagram of EXTI ................................................................................................................ 97

Figure 7.1. Basic structure of a standard I/O port bit .............................................................................. 103

Figure 7.2. Input configuration .................................................................................................................... 104

Figure 7.3. Output configuration ................................................................................................................. 105

Figure 7.4. Analog configuration ................................................................................................................. 106

Figure 7.5. Alternate function configuration ............................................................................................. 106

Figure 8-1. Block diagram of CRC calculation unit .................................................................................. 129

Figure 9-1. Block diagram of DMA .............................................................................................................. 134

Figure 9-2. Handshake mechanism ............................................................................................................. 136

Figure 9-3. DMA interrupt logic .................................................................................................................... 138

Figure 9-4. DMA0 request mapping ............................................................................................................ 139

Figure 9-5. DMA1 request mapping ............................................................................................................ 140

Figure 11-1. ADC module block diagram ................................................................................................... 154

Figure 11-2. Single conversion mode ......................................................................................................... 156

Figure 11-3. Continuous conversion mode ............................................................................................... 157

Figure 11-4. Scan conversion mode, continuous disable ...................................................................... 158

Figure 11-5. Scan conversion mode, continuous enable ....................................................................... 159

Figure 11-6. Discontinuous conversion mode .......................................................................................... 160

Figure 11-7. Auto-insertion, CNT = 1 .......................................................................................................... 161

Figure 11-8. Triggered insertion .................................................................................................................. 161

Figure 11-9. 12-bit Data alignment .............................................................................................................. 162

Figure 11-10. 6-bit Data alignment .............................................................................................................. 162

Figure 11-11. 20-bit to 16-bit result truncation .......................................................................................... 165

Figure 11-12. Numerical example with 5-bits shift and rounding .......................................................... 166

Figure 11-13. ADC sync block diagram ...................................................................................................... 167

Figure 11-14. Regular parallel mode on 16 channels............................................................................... 168

Figure 11-15. Inserted parallel mode on 4 channels ................................................................................ 169

Figure 11-16. Follow-up fast mode on 1 channel in continuous conversion mode ........................... 169

Figure 11-17. Follow-up slow mode on 1 channel .................................................................................... 170

Figure 11-18. Trigger rotation: inserted channel group .......................................................................... 171

14

Page 15

GD32VF103 User Manual

Figure 11-19. Trigger rotation: inserted channels in discontinuous mode ......................................... 171

Figure 11-20. Regular parallel & trigger rotation mode ........................................................................... 172

Figure 11-21. Trigger occurs during inserted conversion ...................................................................... 172

Figure 11-22 Follow-up single channel with inserted sequence CH1, CH2 ......................................... 173

Figure 12-1. DAC block diagram .................................................................................................................. 189

Figure 12-2. DAC LFSR algorithm ............................................................................................................... 191

Figure 12-3. DAC triangle noise wave ........................................................................................................ 191

Figure 13.1. Free watchdog block diagram ............................................................................................... 203

Figure 13.2. Window watchdog timer block diagram .............................................................................. 209

Figure 13.3. Window watchdog timing diagram ....................................................................................... 210

Figure 14.1. Block diagram of RTC ............................................................................................................. 214

Figure 14.2. RTC second and alarm waveform example (RTC_PSC = 3, RTC_ALRM = 2) ................ 215

Figure 14.3. RTC second and overflow waveform example (RTC_PSC= 3) ......................................... 216

Figure 15-1. Advanced timer block diagram ............................................................................................. 224

Figure 15-2. Normal mode, internal clock divided by 1 ........................................................................... 225

Figure 15-3. Counter timing diagram with prescaler division change from 1 to 2 ............................. 226

Figure 15-4. Timing chart of up counting mode, PSC=0/1 ...................................................................... 227

Figure 15-5. Timing chart of up counting mode, change TIMERx_CAR ongoing ............................... 228

Figure 15-6. Timing chart of down counting mode, PSC=0/1 ................................................................. 229

Figure 15-7. Timing chart of down counting mode, change TIMERx_CAR ongoing ......................... 230

Figure 15-8. Timing chart of center-aligned counting mode .................................................................. 231

Figure 15-9. Repetition counter timing chart of center-aligned counting mode ................................. 232

Figure 15-10. Repetition counter timing chart of up counting mode .................................................... 232

Figure 15-11. Repetition counter timing chart of down counting mode ............................................... 233

Figure 15-12. Input capture logic ................................................................................................................. 234

Figure 15-13. Output compare logic (with complementary output, x=0,1,2) ....................................... 235

Figure 15-14. Output compare logic (CH3_O) ........................................................................................... 235

Figure 15-15. Output-compare in three modes ......................................................................................... 237

Figure 15-16. Timing chart of EAPWM ........................................................................................................ 238

Figure 15-17. Timing chart of CAPWM ....................................................................................................... 238

Figure 15-18. Complementary output with dead time insertion ............................................................. 241

Figure 15-19. Output behavior of the channel in response to a break (the break high active) ........ 242

Figure 15-20. Example of counter operation in encoder interface mode ............................................. 243

Figure 15-21. Example of encoder interface mode with CI0FE0 polarity inverted ............................. 243

Figure 15-22. Hall sensor is used to BLDC motor .................................................................................... 244

Figure 15-23. Hall sensor timing between two timers ............................................................................. 245

Figure 15-24. Restart mode .......................................................................................................................... 246

Figure 15-25. Pause mode ............................................................................................................................ 246

Figure 15-26. Event mode ............................................................................................................................. 247

Figure 15-27. Single pulse mode TIMERx_CHxCV=0x04, TIMERx_CAR=0x60.................................... 248

Figure 15-28. TIMER0 Master/Slave mode timer example ....................................................................... 248

Figure 15-29. Triggering TIMER0 with enable signal of TIMER2 ............................................................ 249

Figure 15-30. Triggering TIMER0 with update signal of TIMER2 ........................................................... 250

Figure 15-31. Pause TIMER0 with enable signal of TIMER2 ................................................................... 251

15

Page 16

GD32VF103 User Manual

Figure 15-32. Pause TIMER0 with O0CPREF signal of Timer2 ............................................................... 251

Figure 15-33. Triggering TIMER0 and TIMER2 with TIMER2’s CI0 input .............................................. 252

Figure 15-34. General Level 0 timer block diagram ................................................................................. 280

Figure 15-35. Normal mode, internal clock divided by 1 ......................................................................... 281

Figure 15-36. Counter timing diagram with prescaler division change from 1 to 2 ........................... 282

Figure 15-37. Timing chart of up counting mode, PSC=0/1 .................................................................... 283

Figure 15-38. Timing chart of up counting mode, change TIMERx_CAR ongoing ............................. 284

Figure 15-39. Timing chart of down counting mode, PSC=0/1 ............................................................... 285

Figure 15-40. Timing chart of down counting mode, change TIMERx_CAR. ...................................... 286

Figure 15-41. Timing chart of center-aligned counting mode ................................................................ 287

Figure 15-42. Input capture logic ................................................................................................................. 288

Figure 15-43. Output-compare in three modes ......................................................................................... 290