Page 1

1

www.bufanxiu.com

2

3

4

5

6

7

8

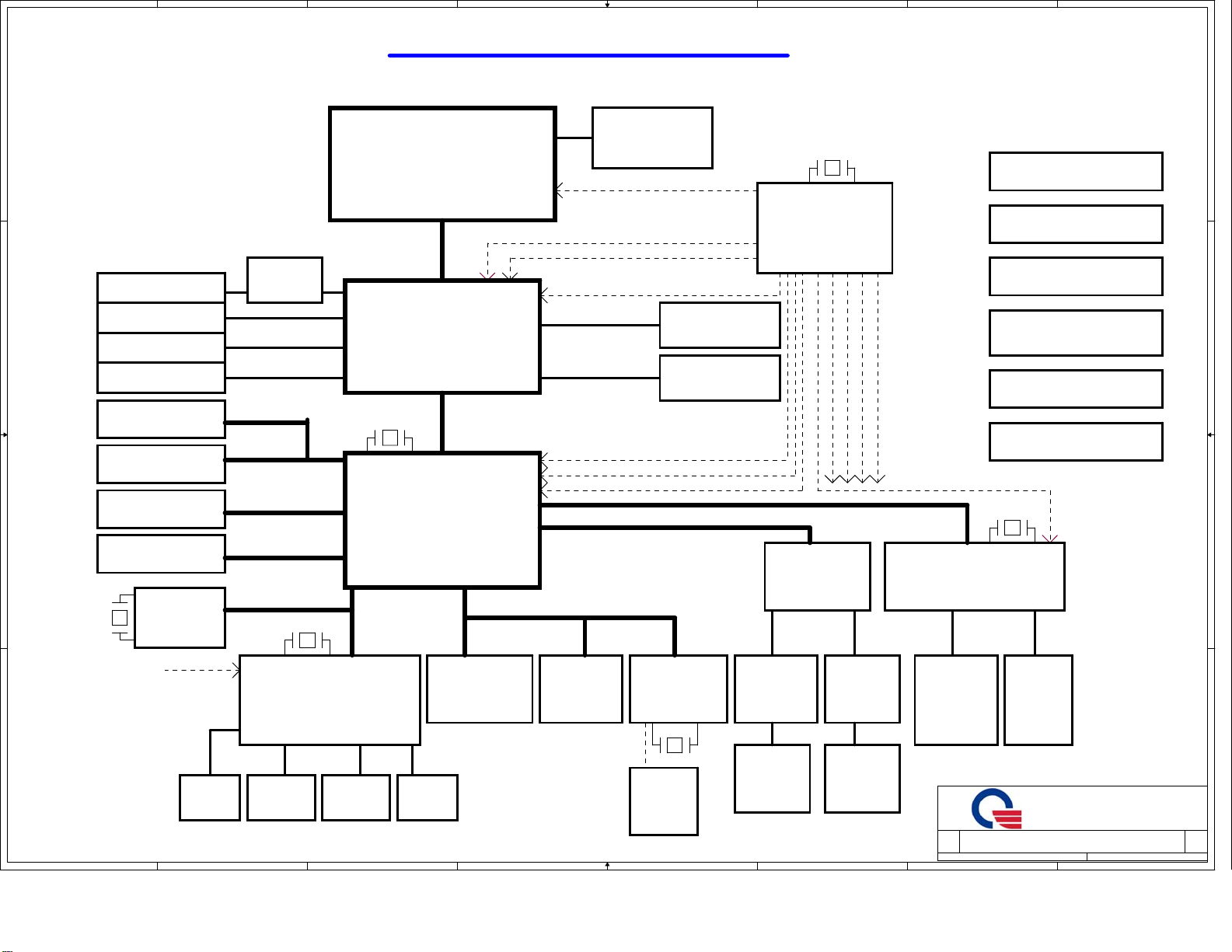

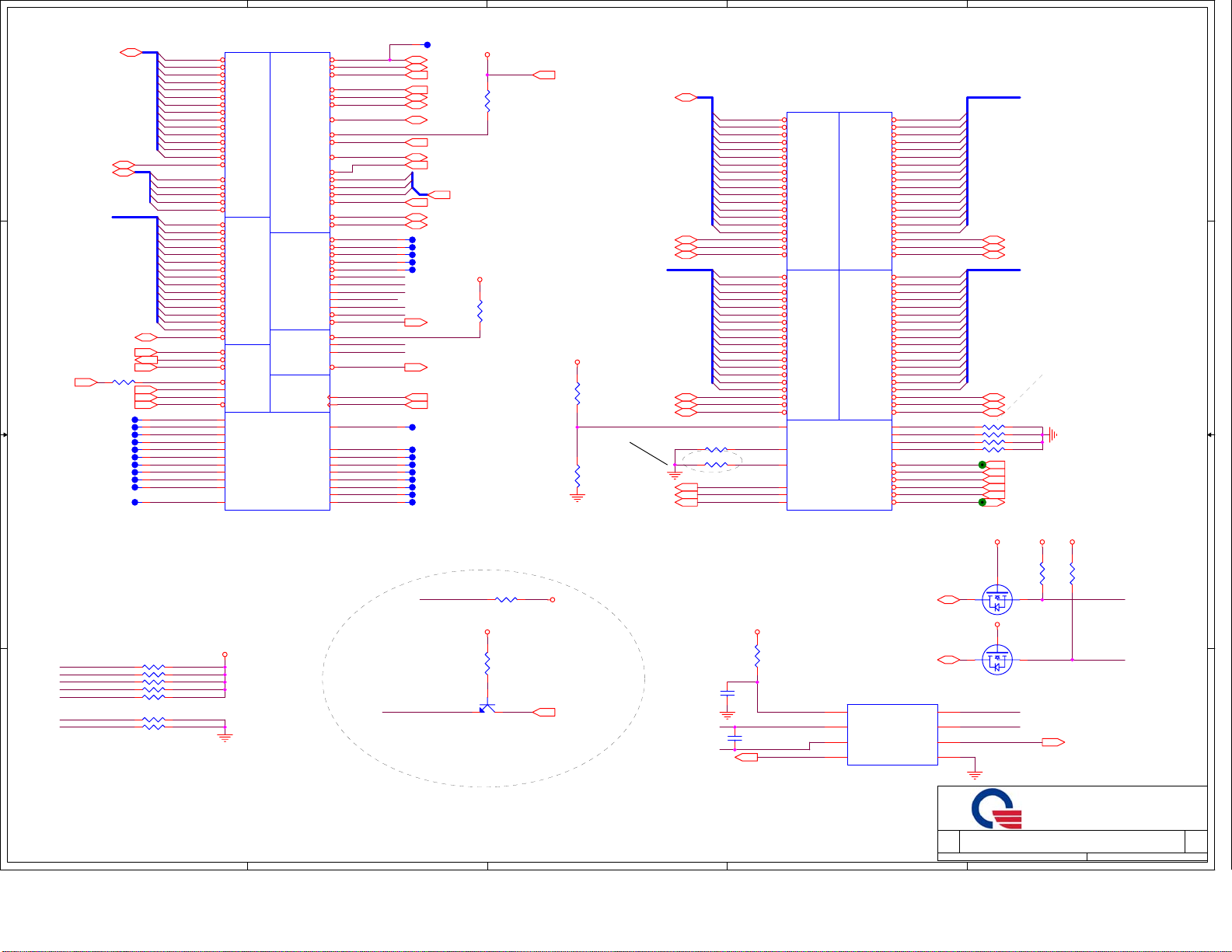

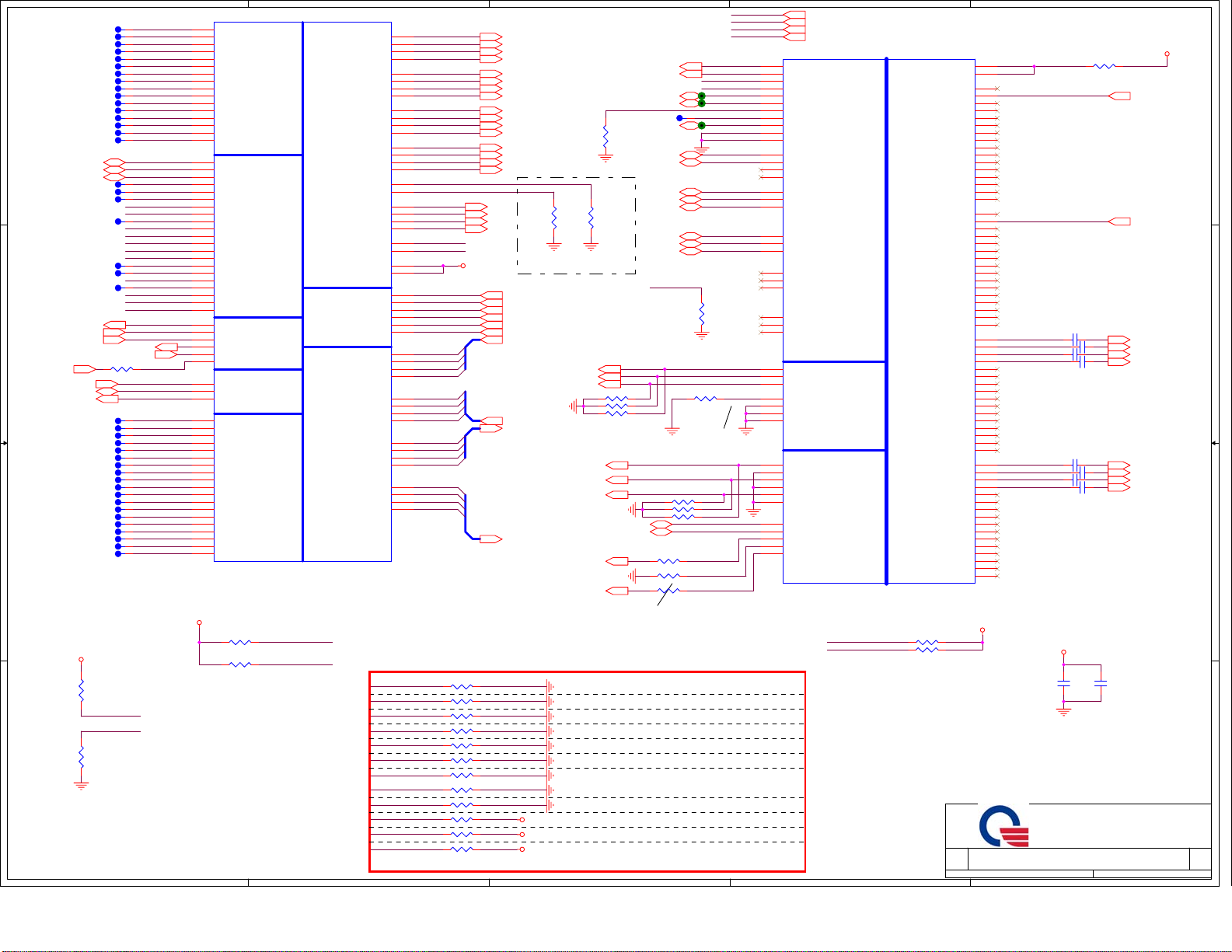

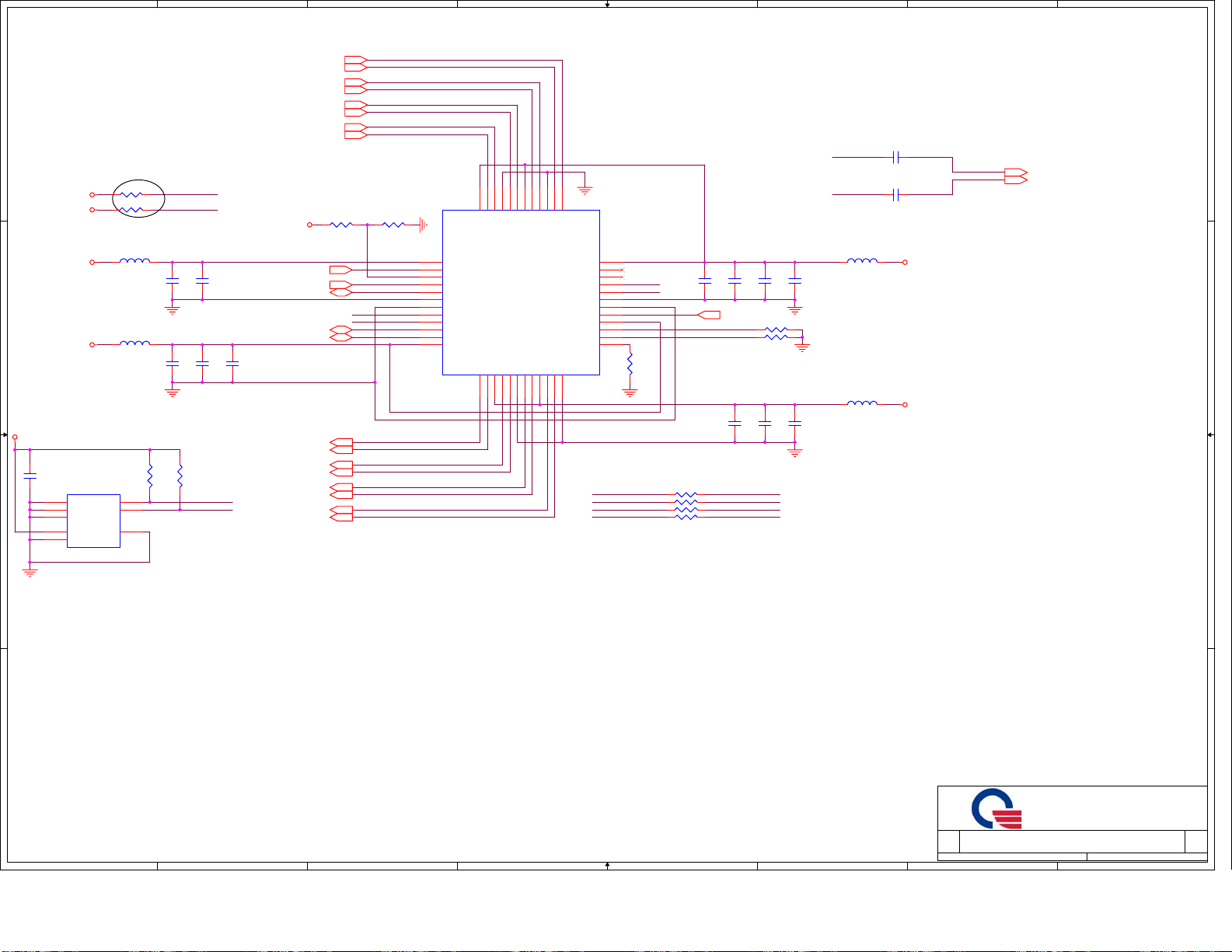

DW1 BLOCK DIAGRAM

Yonah / Calistoga / ICH7-M

A A

CPU Yonah/Merom

478P (uPGA)

PG 5,6

32.768KHz

Keyboard

HOST BUS

NORTH BRIDGE

Calistoga

1466P BGA

INTEGRADED VGA FUNCTION

PG 7,8,9,10,11,12

DMI LINK

PCI-E 4X

SOUTH BRIDGE

ICH7-M

652P BGA

PG 16,17,18,19

Express Card x1

NEW CARD

PG 30

FLASH

PG 30

3

DDRII 533,667 MHz

DDRII 533,667 MHz DDRII-SODIMM2

PCI-Express

4

DVI Bridge

DVI

B B

S-VIDEO

LCD Panel

CRT

PG 35

PG 35

PG 20

PG 32

CH7307

PG 13

S-VIDEO

LVDS X1

CRT

USB PORT 0,1,2,3

PG 23

USB PORT 4,5,6,7

Camera,Bluetooth,Mini

Card,New Card

SATA - HDD

C C

IDE - CDROM

PG 23

PG 33

USB 2.0

SATA 150MB

PATA 66/100/133

PG 33

3.3V LPC, 33MHz

32.768KHz

32.768KHz

TPM (1.2)

PG 35

PCLK_541

PC87541V

TQFP 176

D D

FAN

PG 32 PG 31PG 31

1

Touchpad

2

CPU THERMAL

SENSOR

MAX6657

CPUCLK, CPUCLK#

CLK_MCH_BCLK, CLK_MCH_BCLK#

DREFSSCLK, DREFSSCLK#

DREFCLK, DREFCLK#

CLK_PCIE_3GPLL, CLK_PCIE_3GPLL#

PG 5

DDRII-SODIMM1

PCLK_ICH

14M_ICH

SBLINKCLK, SBLINKCLK#

33MHZ, 3.3V PCI

Azalia

MINI-Card

PG 34PG 34

GigaLAN

Intel

82573E

PG 27,28

25MHz

RJ45

JACK

PG 27

5

PG 14,15

PG 14,15

SMARTDAA

MODEM,

CX20548

RJ11

14.318MHz

CLOCK GEN

ICS954206AG

56pins

Azalia

CX20549

DIB_DATAN

DIB_DATAP

PG 26

PG 26

CLK_PCIE_NEW_C, CLK_PCIE_NEW_C#

PG 24

AMP

TPA0312

GMT1427

AUDIO

JACK

6

PG 4

PCLK_TPM

PCLK_541

CLK_PCIE_MINI, CLK_PCIE_MINI#

PCLK_5C832

CARDREADER / IEEE 1394

CONTROLLER/CF

RICOH 5C832

3 IN 1

CARD READER

SD/MMC,MS

PG 24

MS-PRO

PG 23

PG 25

Size Document Number Rev

Date: Sheet

SYSTEM POWER MAX8743

PG 39

CPU CORE MAX8771

PG 41

SYSTEM MAX8734

POWER(3/5V)

PG 38

SYSTEM POWER MAX8632

(1.8VSUS/0.9V SMDDR_VREF)

PG 40

BATT CHARGER

MAX8724

PG 37

DISCHARGE

PG 36

24.576MHz

PG 21,22,23

1394

CONN

PG 22

PROJECT : DW1

Quanta Computer Inc.

BLOCK DIAGRAM

7

142Tuesday, January 03, 2006

8

1ACustom

of

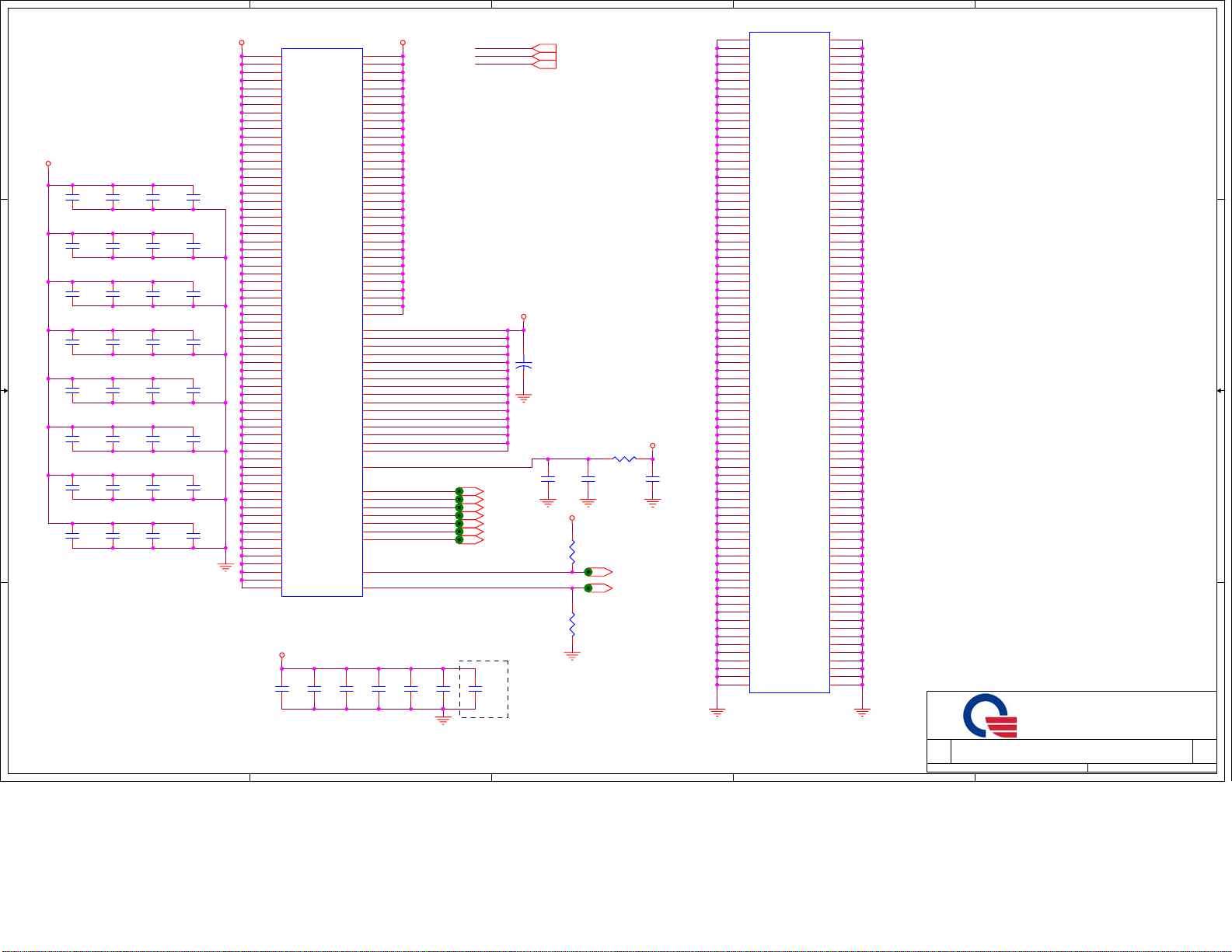

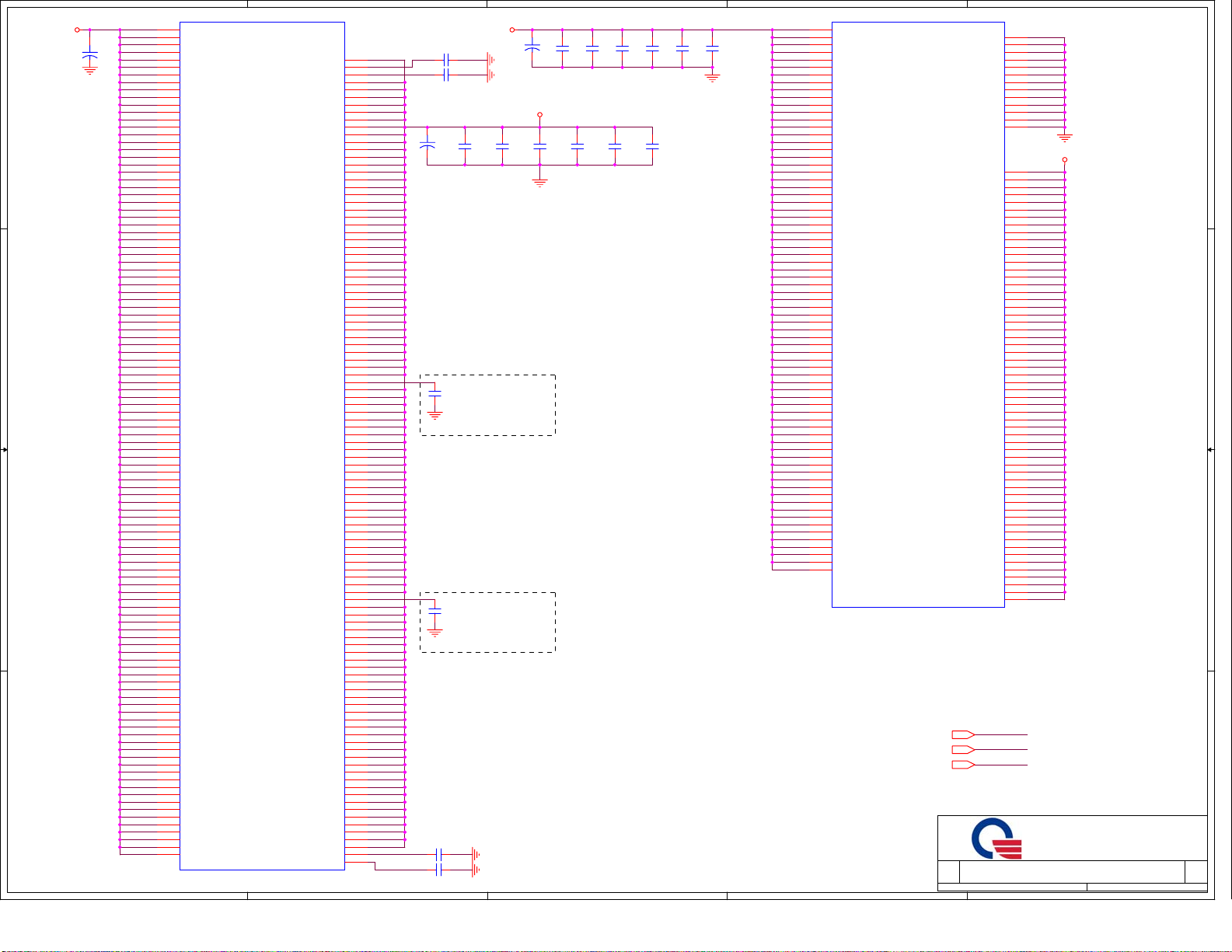

Page 2

5

www.bufanxiu.com

4

3

2

1

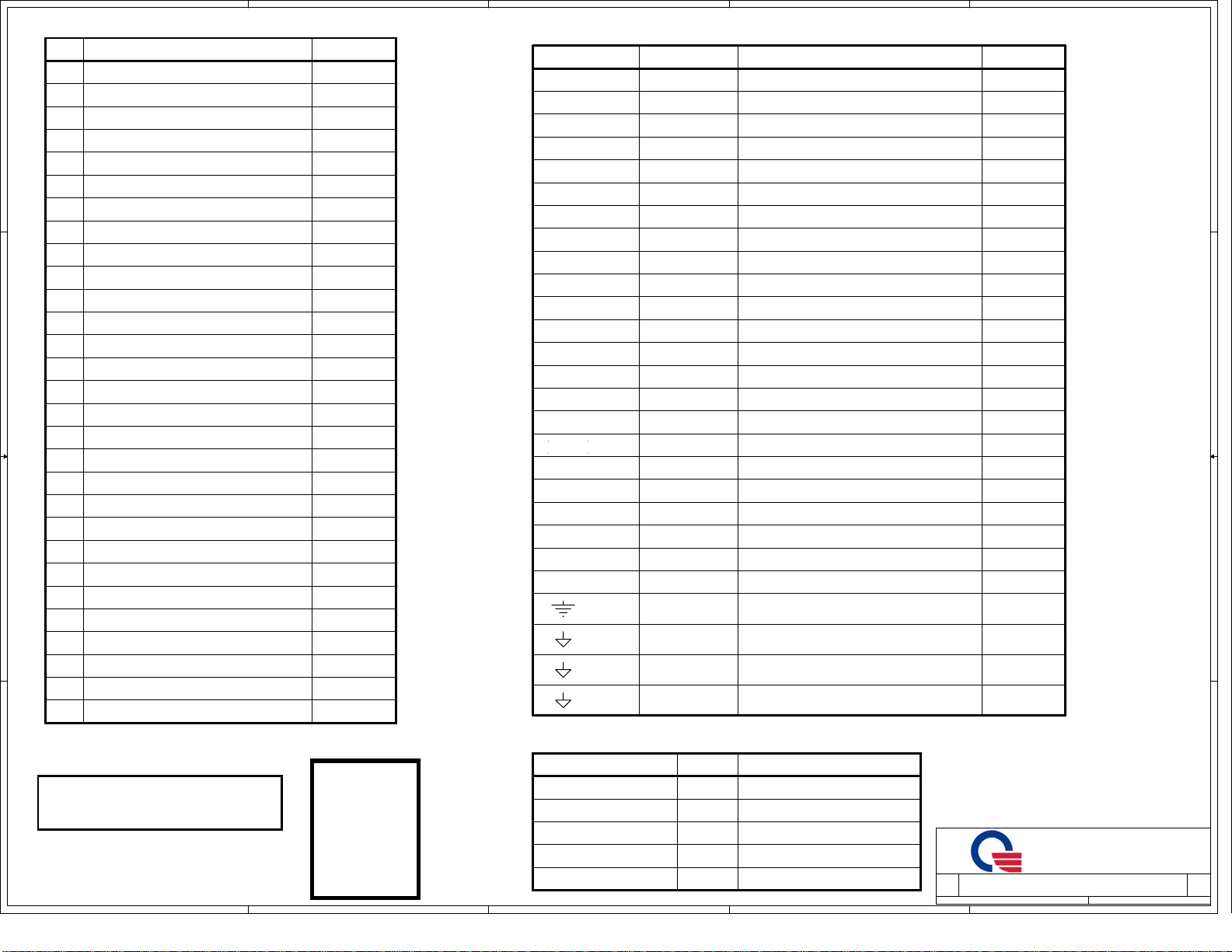

INDEX

Description

1

Schematic Block Diagram

2

System Information

D D

C C

B B

3

System Power Block Diagram

4

CLOCK GENERATOR

5-6

Intel Yonah CPU

7-12

Calistoga-GM

13

DVI Bridge

14-15

DDR II SO-DIMM

16-19

ICH7-M

20

LCD CONNECTOR / LCD PWR

21-22

CARD Reader(R5C832)

23

CARD Reader/USB Port

24-25

AUDIO CODEC / AUDIO JACK

26

MODEM(DAA)

27-28

GIGA-LAN 82573E

29

LED/Switch

30

KBC

31

Bluetooth/Touch Pad/Key board

32

FAN/CRT Port

33

SATA HDD / CD-ROM

34

NEW CARD/MINI CARD

35

TPM/DVI Port /S-Video

36

DISCHARGE

37

CHARGE

38

SYSTEM POWER(3V/5V)

39

SYSTEM POWER(1.05V/1.5V)

40

SYSTEM POWER(1.8V/0.9V)

41

CPU POWER(ISL6260/6280)

42

CPU Operation State

NOTEPg#

Power & Ground

Label

VIN

MBAT

VCCRTC

+15V

CPU_CORE

+1.05V

+3V

3VSUS

3V_S5 S5_ONS0, S3, S4, S5

3VPCU

+5V

5VSUS

5VPCU

+1.5V S0

1.5V_S5

1.8VSUS

+2.5V MAINONS0

SMDDR_VREF

VDDA

GND

AGND

T-GND

6260AGND

ACTIVE

S0, S3, S4, S5

S0, S3, S4, S5

S0, S3, S4, S5

S0, S3, S4, S5

S0

S0

S0

S0, S3

S0, S3, S4, S5

S0

S0, S3

S0, S3, S4, S5

S0, S3, S4, S5 S5_ON

S0, S3 SUSON

S0

S0, S3

S0 MAINON

ALL PAGES

Description

AC ADAPTER (19V)

MAIN BATTERY + (10~17V)

RTC & KBC POWER

+15V

CPU CORE POWER (1.25/1.15V)

FSB POWER (1.05V)

ALWAYS POWER (3V)

ALWAYS POWER (5V)

DDR CORE POWER

DDR COMMAND & CONTROL PULL UP POWER

DDR REF POWER

AUDIO ANALOG POWER (5V)

DIGITAL GROUND

AUDIO GND

AUDIO JACK GND

CPU ANALOG GROUND

(3_3V)

Control

Signal

VRON

VRON

MAIND

SUSON

MAIND

SUSON

S5_ONS0, S3, S4, S55V_S5

MAIND

MAINONSMDDR_VTERM

SUSON

PCI DEVICES IRQ ROUTING

A A

Ricoh 5C832 E,FAD25

5

PCI_INTDEVICE REQ/GNT #IDSEL #

0

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : GND

LAYER 6 : IN3

LAYER 7 : VCC

LAYER 8 : BOT

4

PCB STACK UP

SM BUS

DEVICE

CLOCK GENERATOR

DDR II

3

ADDRESS

D2H

A0H

TBD

16H

98H

BUS

PCLK_SMB, PCLK_SMB(ICH6)

(ICH6)PCLK_SMB, PCLK_SMB

GMCHLCD EDID

MBDATA,MBCLK

(KBC)CHARGER

MBDATA,MBCLK

(KBC)CPU THERMAL SENSOR

2

PROJECT : DW1

Size Document Number Rev

Date: Sheet

Quanta Computer Inc.

System Information

1

of

242Tuesday, January 03, 2006

1ACustom

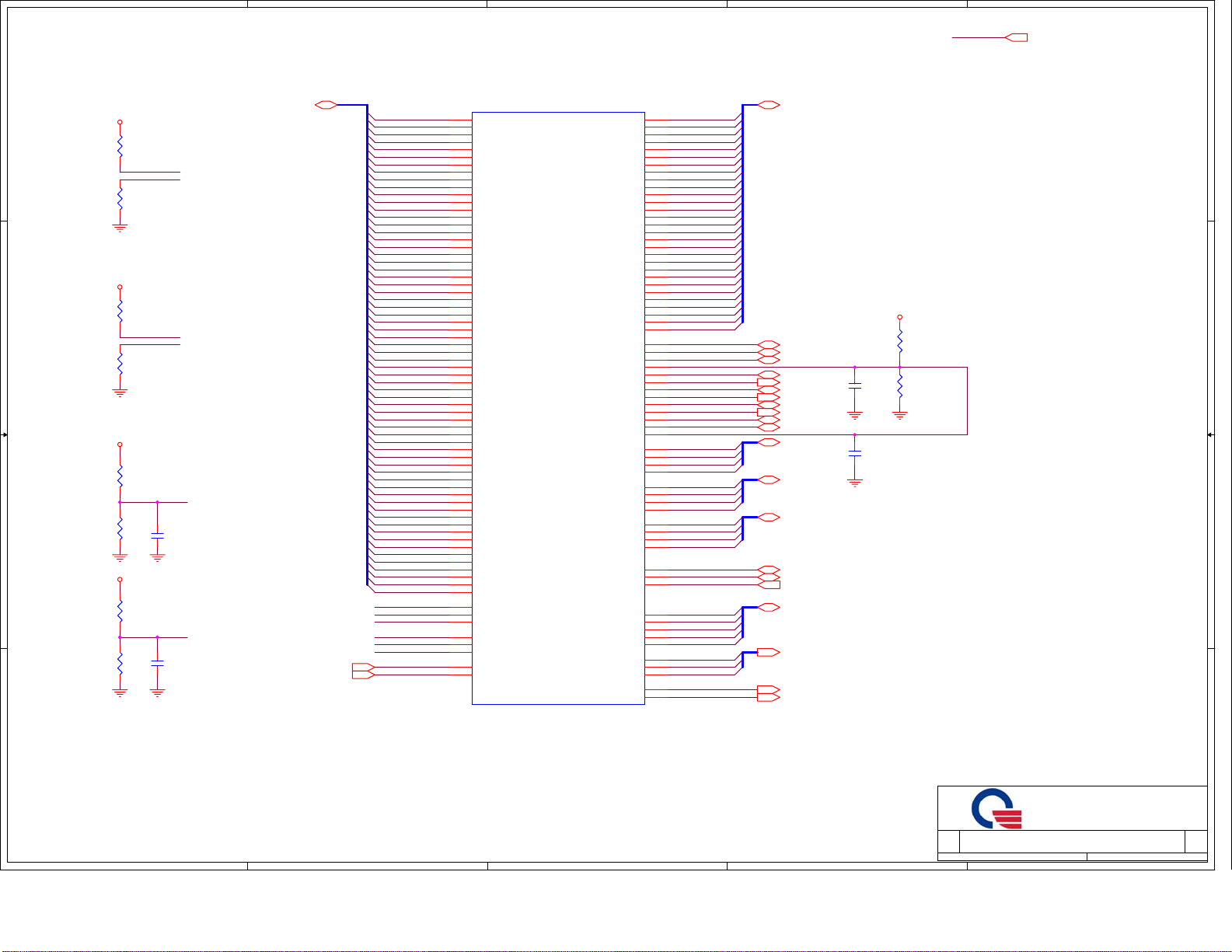

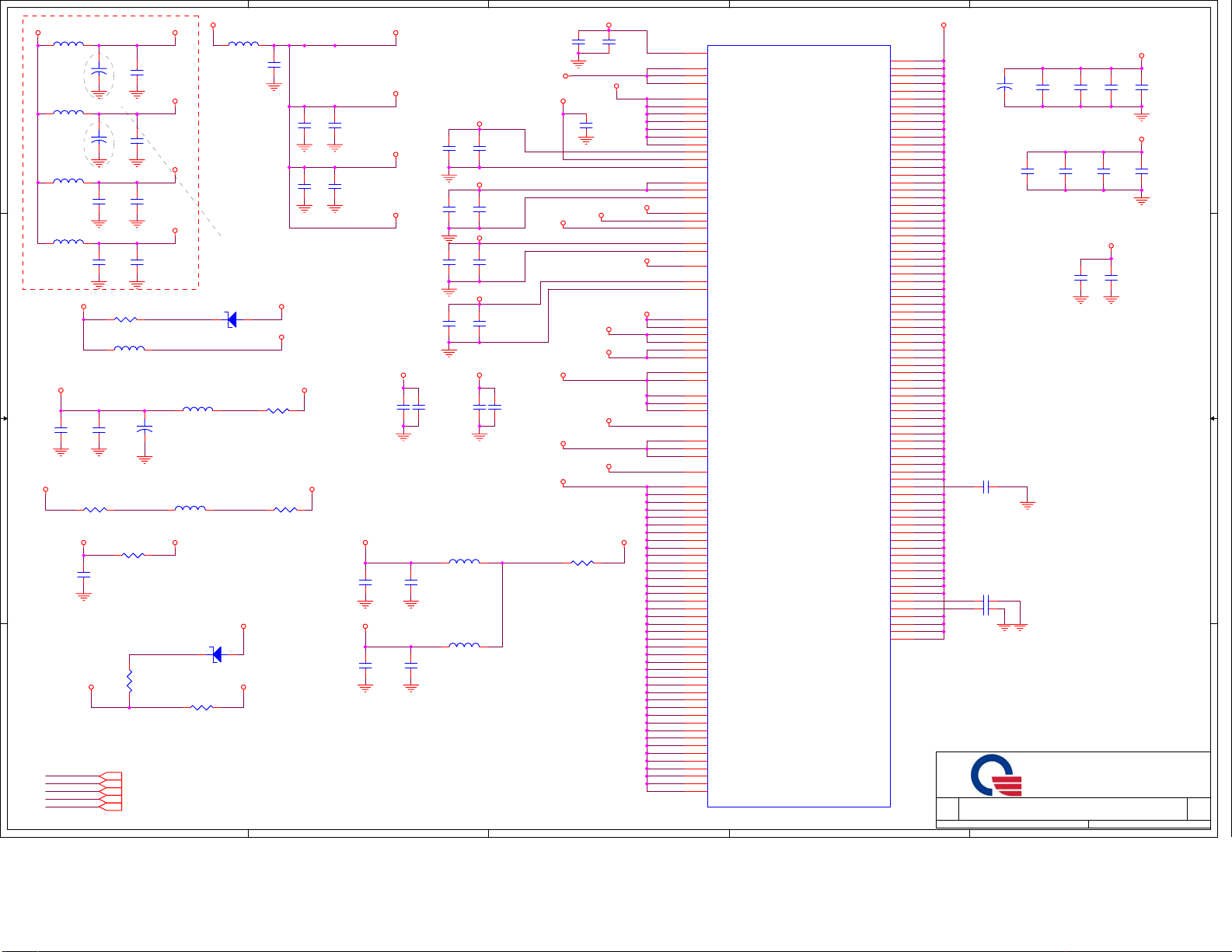

Page 3

5

www.bufanxiu.com

4

3

S5_ON

2

1

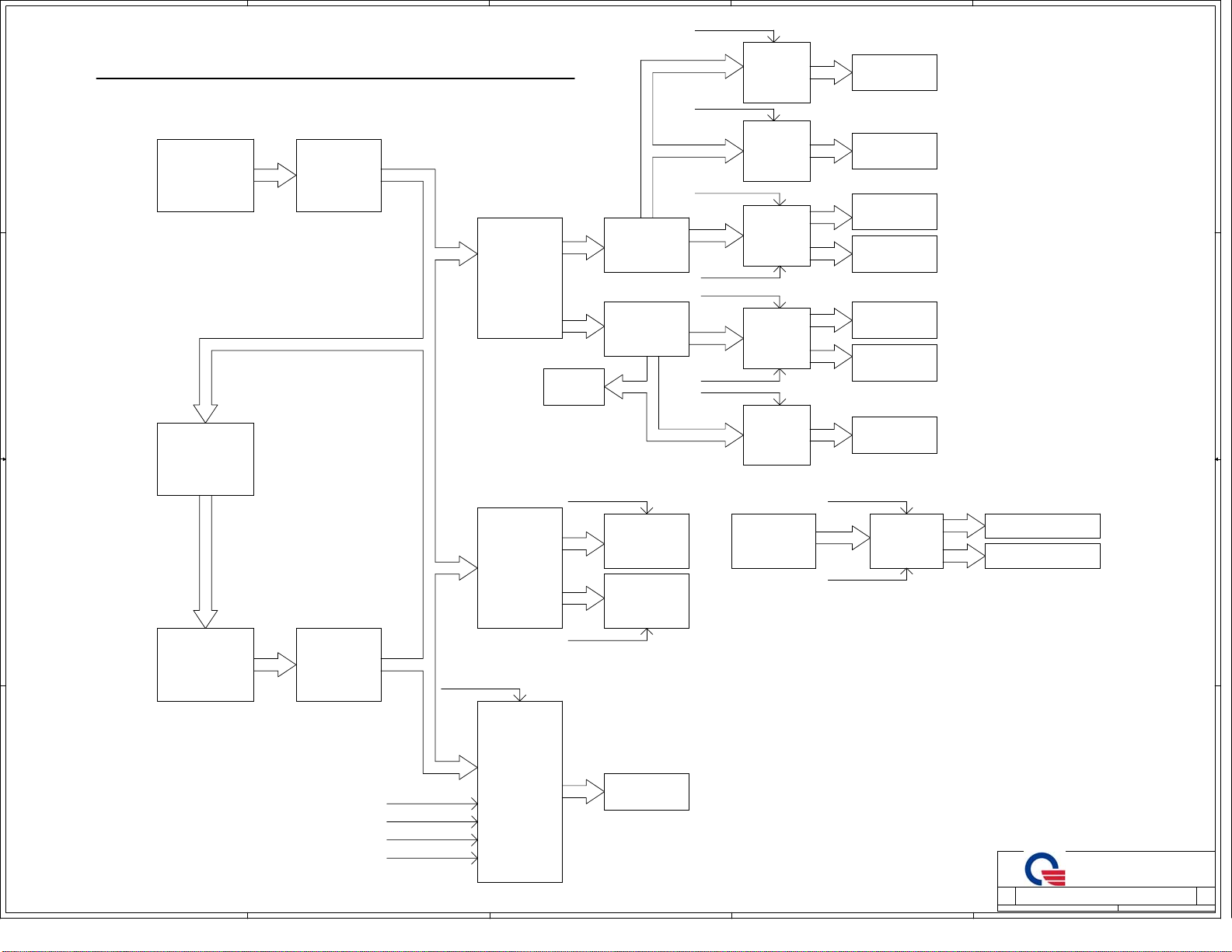

SYSTEM POWER BLOCK DIAGRAM

MAINON

D D

S.W

Adaptor

C C

VIN

MOS-FET

VIN

MAX8734

+15V

3VPCU

ALWAYS

5VPCU

ALWAYS

MAIND

SUSD

MAIND

SUSD

S5_ON

S.W

MOS-FET

S.W

MOS-FET

S.W

MOS-FET

3V_S5

+2.5VSC4215

+3V

3VSUS

+5V

5VSUS

S.W

CHARGER

MOS-FET

3V_S5

MAX8724

MAINON

MAINON

1.05V

B B

VIN

MAX1540

5VPCU

MAX8632

SUSON

SMDDR_VTERM

1.8VSUS

+1.5V

MAINON

BATTERY

A A

S.W

MOS-FET

VIN

CPU_VID[0..5]

HWPG

DPRSLPVR

STP_CPU#

VRON

MAX8771

CPU_CORE

PROJECT : DW1

Size Docum e n t N u mb er Re v

5

4

3

2

Date: Sheet

Quanta Computer Inc.

System Power block diagram

1

342Tuesday, J anu ary 03, 2006

1AC

of

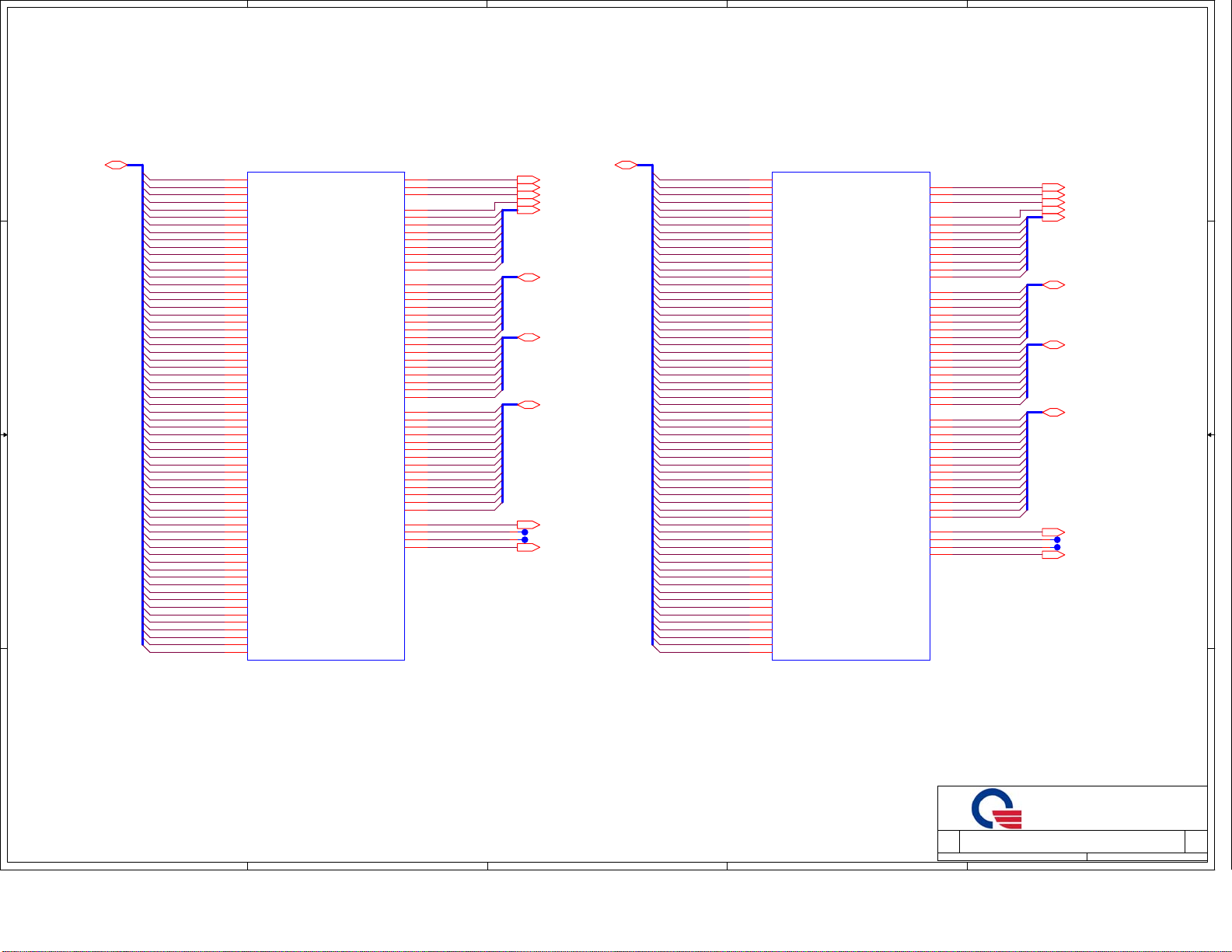

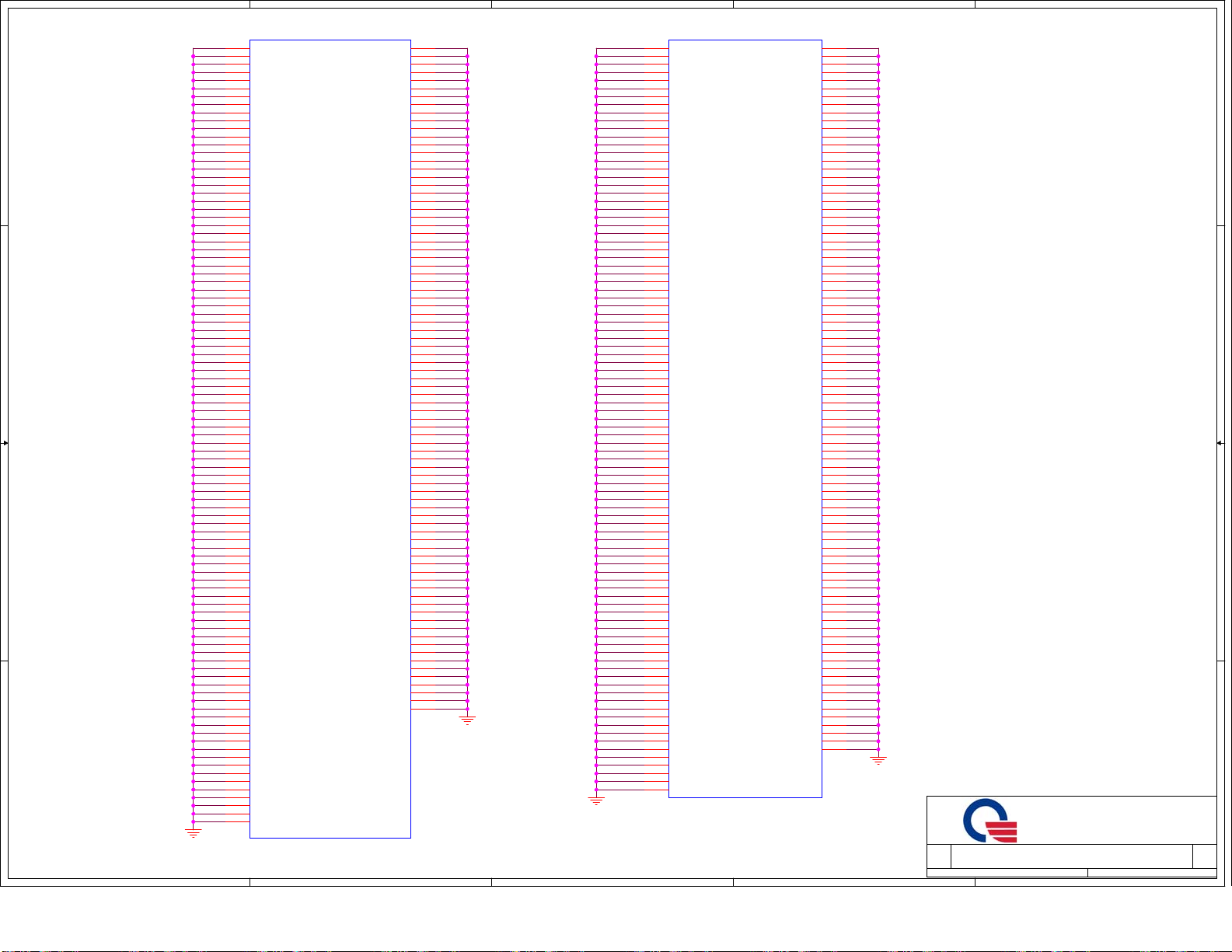

Page 4

A

www.bufanxiu.com

B

C

D

E

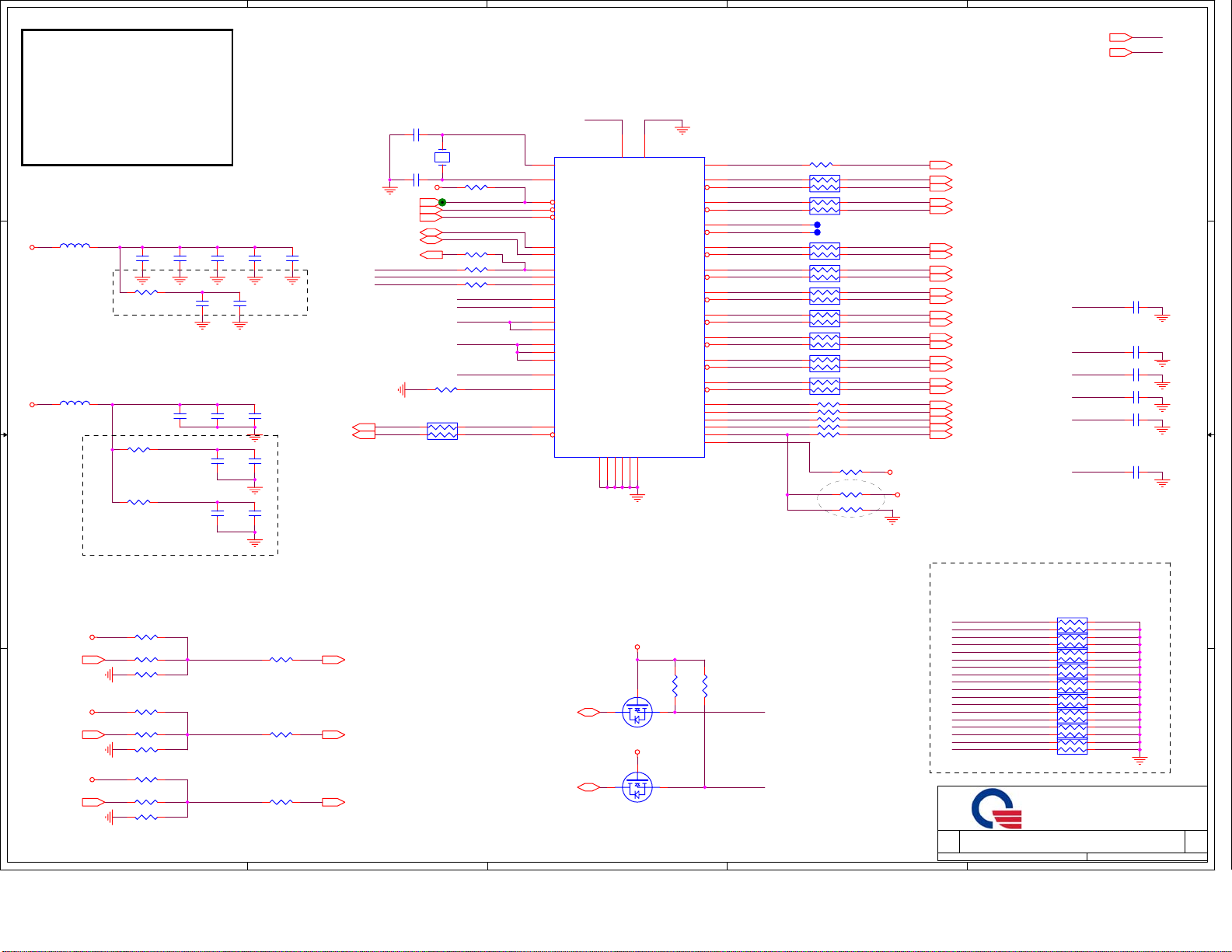

FSC FSB FSA CPU SRC PCI

1 0 1 100 100 33

0 0 1 133 100 33

+3V(5,9,11,13, 1 4 ,15,16,17,18,19,20,24,29,30,31,32,33,34,35,36,38)

+1.05V(5,6,7,10,1 1 ,16,19,36,39)

Default

+3V

+1.05V

0 1 1 166 100 33

0 1 0 200 100 33

0 0 0 266 100 33

4 4

1 0 0 333 100 33

1 1 0 400 100 33

1 1 1 200 100 33

VR_PWRGD_CK410#(18,41)

PM_STPPCI#(18)

L15

1T2012-121JT

+3V

120 ohms@100Mhz

3 3

L14

1T2012-121JT

+3V

120 ohms@100Mhz

2 2

VDD_SRC_CPU

C257

0.1U

R216 2.2/F

VDD_PCI

R158 2.2/F

R179 1

C264

0.1U

VDD_A

25 mils

C240

0.1U

VDD_48

VDD_REF

25 mils

C260

0.1U

C256

0.1U

C226

0.1U

C246

0.1U

C248

0.1U

C258

10U

C252

0.1U

C230

10U

C233

10U

C244

10U

C267

10U

DREFCLK(9)

DREFCLK#(9)

PM_STPCPU#(18)

CGCLK_SMB(14,15,34)

CGDAT_SMB(14,15,34)

CLKUSB_48(18)

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

Iref=5mA,

Ioh=4*Iref

DREFCLK R_DOT96

DREFCLK#

Close to IC <500mils

C228 33P

21

C227 33P

+3V

R200 475/F

RP37

1

3

33X2

CG_XIN

CL=20 - 22P

Y2

14.318MHZ

CG_XOUT RHCLK_CPU

R187 *10K

VR_PWRGD_CK410#

PM_STPPCI#

PM_STPCPU#

CGCLK_SMB

CGDAT_SMB

R186 33

R191 2.2K

R162 4.7K

VDD_REF

VDD_SRC_CPU

VDD_PCI

VDD_SRC_CPU

VDD_48

IREF

2

R_DOT96#

4

50

49

10

55

54

46

47

12

16

53

48

42

1

7

21

28

34

11

39

14

15

SMbus address D2 /IDT

U9

XTAL_IN

XTAL_OUT

Vtt_PwrGd#/PD

PCI/SRC_STOP#

CPU_STOP#

SCLK

SDATA

FSA/USB_48MHz

FSB/TEST_MODE

FSC/REF1

VDD_REF

VDD_CPU

VDD_PCI_1

VDD_PCI_2

VDD_SRC0

VDD_SRC1

VDD_SRC2

VDD_48

IREF

DOT96MHz

DOT96MHz#

ICS954206AG-T

VDD_A

CK-410M

GND_REF

GND_48

2

51

13

38

37

VDDA

GNDA

CPU2_ITP/SRC7

CPU2#_ITP/SRC7#

SRC0/DREFSSCLK

SRC0#/DREFSSCLK#

PCIF1/100_96M#

PCIF0/ITP_EN

GND_PCI_26GND_SRC29GND_CPU

GND_PCI_1

45

REF0

CPU0

CPU0#

CPU1

CPU1#

SRC6

SRC6#

SRC5

SRC5#

SRC4_SATA

SRC4#_SATA

SRC3

SRC3#

SRC2

SRC2#

SRC1

SRC1#

PCI5

PCI4

PCI3

PCI2

Place thes e t e r mination to close CK410M.

52

44

43

41

40

36

35

33

32

31

30

26

27

24

25

22

23

19

20

17

18

R_PCLK_541

5

R_PCLK_5C832

4

R_PCLK_TPM

3

R_PCLK_DBP

56

R_PCLK_ICH

9

R_PCLK_SIO

8

14M_REF

RHCLK_CPU#

RHCLK_MCH

RHCLK_MCH#

RSRC_MINI

RSRC_MINI#

RSRC_MCH

RSRC_MCH#

RSRC_SATA

RSRC_SATA#

RSRC_NEW

RSRC_NEW#

RSRC_ICH

RSRC_ICH#

RSRC_LAN

RSRC_LAN#

RDREFSSCLK

RDREFSSCLK#

R173 33

RP38

1

3

RP42

1

3

T194

T195

RP47

1

3

RP51

1

3

RP53

3

1

RP49

3

1

RP46

3

1

RP44

3

1

RP41

3

1

R176 33

R171 33

R159 33

R155 33

R183 33

R184 10K

R185 *10K

R175 10K

DREFSSCLK Frequency Select.

"0" : 96MHz

"1" : 100MHz

33X2

2

4

33X2

2

4

33X2

2

4

33X2

2

4

33X2

4

2

33X2

4

2

33X2

4

2

33X2

4

2

33X2

4

2

14M_ICH (18)

CLK_CPU_BCLK (5)

CLK_CPU_BCLK# (5)

CLK_MCH_BCLK (7)

CLK_MCH_BCLK# (7)

CLK_PCIE_MINI (34)

CLK_PCIE_MINI# (34)

CLK_PCIE_3GPLL (9)

CLK_PCIE_3GPLL# (9)

CLK_PCIE_SATA (16)

CLK_PCIE_SATA# (16)

CLK_PCIE_NEW (34)

CLK_PCIE_NEW# (34)

CLK_PCIE_ICH (17)

CLK_PCIE_ICH# (17)

CLK_PCIE_LAN (27)

CLK_PCIE_LAN# (27)

DREFSSCLK (9)

DREFSSCLK# (9)

PCLK_541 (30)

PCLK_5C832 (21)

PCLK_TPM (35)

PCLK_DBP (34)

PCLK_ICH (17)

EMI

48MHZ

CLKUSB_48

33MHZ

PCLK_541

PCLK_5C832

PCLK_TPM

PCLK_ICH

C245 *10P

C232 *10P

C225 *10P

C223 *10P

C239 *10P

14.318MHZ

14M_ICH

+3V

+3V

To check intel re ference circuit default setting.

100MHZ? or 96MHZ?

EMI problem?

C241 *10P

FSB frequency will be selected by CPU internal.

+1.05V

CPU_BSEL0(5)

+1.05V

CPU_BSEL1(5)

1 1

+1.05V

CPU_BSEL2(5) MCH_BSEL2 (9)

R206 56/F

R194 *0

R196 *1K

R211 *1K

R214 0

R207 *0

R154 *1K

R172 0

R177 *0

A

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

R202 1K

R212 1K

R160 1K

MCH_BSEL0 (9)

MCH_BSEL1 (9)

B

B Stage:

Change Q9,Q10 footprint.

PDAT_SMB(18,27,34)

PCLK_SMB(18,27,34)

+3V

R192

R188

2

3

3

C

1

Q9

2N7002E

+3V

2

1

Q10

2N7002E

10K

10K

CGDAT_SMB

CGCLK_SMB

D

Place thes e t e r mination to close CK410M.

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

CLK_PCIE_SATA#

CLK_PCIE_SATA

CLK_PCIE_MINI

CLK_PCIE_MINI#

CLK_PCIE_ICH#

CLK_PCIE_ICH

CLK_PCIE_NEW_C

CLK_PCIE_NEW_C#

DREFSSCLK#

DREFSSCLK

DREFCLK#

DREFCLK

RP39 49.9/FX2

RP43 49.9/FX2

RP54 49.9/FX2

RP52 49.9/FX2

RP50 49.9/FX2

RP45 49.9/FX2

RP48 49.9/FX2

RP40 49.9/FX2

RP36 49.9/FX2

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

PROJECT : DW1

Size Document Number Rev

Date: Sheet

Quanta Computer Inc.

CLOCK GENERATOR

442Tuesday, January 03, 2006

E

of

1ACustom

Page 5

5

www.bufanxiu.com

H_A#[31:3](7)

D D

H_ADSTB#0(7)

H_REQ#[4:0](7)

H_A#[31:3]

C C

H_STPCLK#(16)

B B

H_ADSTB#1(7)

H_A20M#(16)

H_FERR#(16)

H_IGNNE#(16)

R99 0

H_INTR(16)

H_NMI(16)

H_SMI#(16)

T170

T9

T171

T11

T15

T22

T16

T12

T177

T19

T192

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK_R#

H_INTR

H_NMI

H_SMI#

TP_A32#

TP_A33#

TP_A34#

TP_A35#

TP_A36#

TP_A37#

TP_A38#

TP_A39#

TP_APM0#

TP_APM1#

TP_HFPLL

U28A

J4

A[3]#

L4

A[4]#

M3

A[5]#

K5

A[6]#

M1

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L1

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

L2

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L5

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U2

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W3

A[27]#

W5

A[28]#

Y4

A[29]#

W2

A[30]#

Y1

A[31]#

V4

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

AA1

RSVD[01]#

AA4

RSVD[02]#

AB2

RSVD[03]#

AA3

RSVD[04]#

M4

RSVD[05]#

N5

RSVD[06]#

T2

RSVD[07]#

V3

RSVD[08]#

B2

RSVD[09]#

C3

RSVD[10]#

B25

RSVD[11]#

PZ47903-2741-01

ADDR GROUP 0

XDP/ITP SIGNALS

THERMH CLK

RESERVED

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

CONTROL

INIT#

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

PROCHOT

THERMDA

THERMDC

THERMTRIP#

BCLK[0]

BCLK[1]

RSVD[12]#

RSVD[13]#

RSVD[14]#

RSVD[15]#

RSVD[16]#

RSVD[17]#

RSVD[18]#

RSVD[19]#

RSVD[20]#

TDI

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

4

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BREQ#0

IERR#

H_INIT#

H_LOCK#

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_HIT#

H_HITM#

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

SYS_RST#

H_PROCHOT#

H_THERMDA

H_THERMDC

TP_EXTBREF

TP_SPARE0

TP_SPARE1

TP_SPARE2

TP_SPARE3

TP_SPARE4

TP_SPARE5

TP_SPARE6

TP_SPARE7

T48

H_ADS# (7)

H_BNR# (7)

H_BPRI# (7)

H_DEFER# (7)

H_DRDY# (7)

H_DBSY# (7)

H_BREQ#0 (7)

H_INIT# (16)

H_LOCK# (7)

H_CPURST# (7)

H_RS#[2:0] (7)

H_TRDY# (7)

H_HIT# (7)

H_HITM# (7)

T6

T13

T176

T10

T175

T76

T20

T21

T18

T172

T173

T71

T73

T69

+1.05V

SYS_RST# (18)

PM_THRMTRIP# (9,16)

CLK_CPU_BCLK (4)

CLK_CPU_BCLK# (4)

+1.05V

+1.05V

R137

56/F

Near to MCH <500mils

R135

56/F

Layout note: 0.5" max

for GTLREF

3

+1.05V (4,6,7,10,11,16,19,36,39)

H_D#[63:0](7)

H_DSTBN#0(7)

H_DSTBP#0(7)

H_DINV#0(7)

+1.05V

R164

1K/F

R165

2K/F

H_DSTBN#1(7)

H_DSTBP#1(7)

R41 populate for Yonah B

stepping.

CPU_BSEL1(4)

H_D#[63:0]

R166

R167

2

AD26

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

H26

F26

K22

H25

H23

G22

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

C26

D25

B22

B23

C21

J24

J23

J26

U28B

D[0]#

D[1]#

D[2]#

DATA GRP 0 DATA GRP 1

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

MISC

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

PZ47903-2741-01

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

DATA GRP 3

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31 H_D#63

H_DSTBN#1

H_DSTBP#1

H_DINV#1

H_GTLREF

*1K/F

51

CPU_BSEL1

CPU_BSEL2

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42H_D#10

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58H_D#26

H_D#59

H_D#60

H_D#61

H_D#62

H_DSTBN#3

H_DSTBP#3

H_DINV#3

COMP0

COMP1

COMP2

COMP3

ICH_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGDCPU_BSEL0

H_CPUSLP#

PSI#

27.4/F

H_D#[63:0]

H_DSTBN#2 (7)

H_DSTBP#2 (7)

H_DINV#2 (7)

H_D#[63:0]

H_DSTBN#3 (7)

H_DSTBP#3 (7)

H_DINV#3 (7)H_DINV#1(7)

R169

R17054.9/F

R4927.4/F

R5054.9/F

ICH_DPRSTP# (16,41)

H_DPSLP# (16)

H_DPWR# (7)

H_PWRGD (16)CPU_BSEL0(4)

H_CPUSLP# (7,16)

PSI# (41)CPU_BSEL2(4)

+3V +3V

1

Resistor placed within 0.5" of

processor pin for all compensation

resistor and routing as 27.4 and 55

ohm impedance.

+3V

R199

2

SYS_RST#

Populate when ITP700FLEX debug port not used.

+1.05V

XDP_TDI

XDP_TMS

XDP_TDO

H_CPURST#

XDP_BPM#5

XDP_TCK

XDP_TRST#

A A

R42 150/F

R44 39.2/F

R45 *54.9/F

R54 54.9/F

R46 56

R47 27.4/F

R43 680

H_PROCHOT#

If PROCHOT# is not used, then it must be

terminated with a 56 pull-up resistor to

VCCP.

R138 *54.9/F

+1.05V

R142

*330

2

1 3

Q8

*MMBT3904

+1.05V

VR_TT# (41)

SYS_SHDN#(38)

+3V

R163

100

C238

0.1U

6657VCC

H_THERMDA

C231

2200P/50V

H_THERMDC

H/W Shutdown

BDATA(30,37)

BCLK(30,37)

H/W MONITOR

1

VCC

2

DXP

3

DXN

4

-OVT

U8

SMCLK

SMDATA

-ALT

GND

MAX6657/GMT-781

8

7

6

5

3

+3V

2

3

THCLK_SMB

THDAT_SMB

THERM_ALERT#

1

Q12

2N7002E

1

Q11

2N7002E

ICH_THRM#

To SB --> System throttling

R190

10K

10K

THDAT_SMB

THCLK_SMB

THERM_ALERT# (18)

PROJECT : DW1

Size Document Number Rev

5

4

3

2

Date: Sheet

Quanta Computer Inc.

CPU HOST BUS (1 OF 2 )

542Tuesday, January 03, 2006

1

of

1ACustom

Page 6

5

www.bufanxiu.com

U28C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

D D

VCC_CORE

C151

C148

C137

10U

10U

C176

C136

10U

10U

C204

C C

B B

A A

C199

10U

10U

C183

C198

10U

10U

C207

C185

10U

10U

C200

C177

10U

10U

C150

C147

10U

10U

C158

C153

10U

10U

B stage:

Change to 10UF/X6S material(105C).

10U

C184

10U

C211

10U

C203

10U

C213

10U

C191

10U

C180

10U

C152

10U

C157

10U

C212

10U

C175

10U

C208

10U

C201

10U

C156

10U

C168

10U

C149

10U

A18

A20

B10

B12

B14

B15

B17

B18

B20

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

B7

B9

C9

D9

E7

E9

F7

F9

+1.05V

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCCSENSE

VCC[066]

VCC[067]

VSSSENSE

PZ47903-2741-01

C178

C145

0.1U

0.1U

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

4

VCC_COREVCC_CORE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

VID0

AD6

VID1

AF5

VID2

AE5

VID3

AF4

VID4

AE3

VID5

AF2

VID6

AE2

AF7

Connect to PWM , special layout

AE7

C179

C209

0.1U

C146

0.1U

0.1U

C210

0.1U

+1.05V

VCC_CORE

+1.5V

VID0 (41)

VID1 (41)

VID2 (41)

VID3 (41)

VID4 (41)

VID5 (41)

VID6 (41)

C51

0.1U

+1.05V

+1.05V (4,5,7,10,11,16,19,36,39)

VCC_CORE (36,41)

+1.5V (11,17,19,34,36,39)

+

C234

330U/2.5V/ESR-9/POS

C229

0.01U

VCC_CORE

R415

100/F

R413

100/F

recommend by EMI

3

R178 0

C242

10U/X6S

VCCSENSE (41)

VSSSENSE (41)

+1.5V

C237

0.1U

U28D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

A26

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

P3

VSS[081]

PZ47903-2741-01

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

2

1

PROJECT : DW1

Quanta Computer Inc.

Size Document Number R ev

5

4

3

2

Date: Sheet

CPU POWER/GND (2 OF 2 )

1

of

642Tuesday, January 03, 2006

1AB

Page 7

5

www.bufanxiu.com

4

3

2

1

+1.05V

D D

C C

+1.05V

+1.05V

R130

54.9/F

H_XSCOMP

H_XRCOMP

R131

24.9/F

R125

54.9/F

H_YSCOMP

H_YRCOMP

R127

24.9/F

15 mils/10mils

15 mils/10mils

+1.05V

R129

221/F

H_XSWING

R128

C197

100/F

R124

221/F

R123

100/F

0.1U

H_YSWING

C196

0.1U

B B

+1.05V

H_D#[63:0](5)

CLK_MCH_BCLK(4)

CLK_MCH_BCLK#(4)

Short Stub < 100m ils

extract from same point

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

CLK_MCH_BCLK

CLK_MCH_BCLK#

W11

AA10

AB11

AC11

AD10

K11

U11

AB7

AA9

Y10

AB8

AA4

AA7

AA2

AA6

AA1

AB4

AC9

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD4

AC8

AG2

AG1

G1

G2

G4

T10

T11

W9

W7

W6

W4

W3

W5

W2

W1

F1

J1

H1

J6

H3

K2

K9

K1

K7

J8

H4

J3

T3

U7

U9

T1

T8

T4

U5

T9

T5

Y3

Y7

Y8

E1

E2

E4

Y1

U1

U27A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

Calistoga

HOST

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_VREF_0

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_VREF_1

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_CPUSLP#

H_TRDY#

H_A#[31:3] (5)

H_ADS# (5)

H_ADSTB#0 (5)

H_ADSTB#1 (5)

H_BNR# (5)

H_BPRI# (5)

H_BREQ#0 (5)

H_CPURST# (5)

H_DBSY# (5)

H_DEFER# (5)

H_DPWR# (5)

H_DRDY# (5)

H_DINV#[3:0] (5)

H_DSTBN#[3:0] (5)

H_DSTBP#[3:0] (5)

H_HIT# (5)

H_HITM# (5)

H_LOCK# (5)

H_REQ#[4:0] (5)

H_RS#[2:0] (5)

H_CPUSLP# (5,16)

H_TRDY# (5)

C142

0.1U

C128

0.1U

+1.05V

R100

100/F

R92

200/F

H_VREF

+1.05V (4,5,6,10,11,16,19,36,39)

< 0.1", Use 1% R

H_VREF :10 mils/20 mils space

A A

PROJECT : DW1

Size Document Number Rev

5

4

3

2

Date: Sheet

Quanta Computer Inc.

GMCH HOST(1 OF 6 )

742Tuesday, January 03, 2006

1

of

1ACustom

Page 8

5

www.bufanxiu.com

D D

4

3

2

1

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

C C

B B

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

U27D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

Calistoga

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

DDR SYSTEM MEMORY A

SA_WE#

AU12

AV14

BA20

AY13

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AW14

AK23

AK24

AY14

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_CAS#

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_RAS#

TP_MA_RCVENIN#

TP_MA_RCVENOUT#

M_A_WE#

M_B_DQ[0..63](15)M_A_DQ[0..63](15)

M_A_BS#0 (14,15)

M_A_BS#1 (14,15)

M_A_BS#2 (14,15)

M_A_CAS# (14,15)

M_A_DM[0..7] (15)

M_A_DQS[0..7] (15)

M_A_DQS#[0..7] (15)

M_A_A[0..13] (14,15)

M_A_RAS# (14,15)

T23

T17

M_A_WE# (14,15)

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AN10

AK13

AH11

AK10

BA10

AW10

AW4

AY10

AW5

AR5

AJ9

AJ8

BA4

AY9

AY5

AV4

AK4

AK3

AT4

AK5

AJ5

AJ3

U27E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

Calistoga

M_B_BS#0

AT24

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

DDR SYSTEM MEMORY B

SB_WE#

AV23

AY28

AR24

AK36

AR38

AT36

BA31

AL17

AH8

BA5

AN4

AM39

AT39

AU35

AR29

AR16

AR10

AR7

AN5

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AU23

AK16

AK18

AR27

M_B_BS#1

M_B_BS#2

M_B_CAS#

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_RAS#

TP_MB_RCVENIN#

TP_MB_RCVENOUT#

M_B_WE#

M_B_BS#0 (14,15)

M_B_BS#1 (14,15)

M_B_BS#2 (14,15)

M_B_CAS# (14,15)

M_B_DM[7:0] (15)

M_B_DQS[0..7] (15)

M_B_DQS#[0..7] (15)

M_B_A[0..13] (14,15)

M_B_RAS# (14,15)

T31

T26

M_B_WE# (14,15)

A A

PROJECT : DW1

Size Document Number Rev

5

4

3

2

Date: Sheet

Quanta Computer Inc.

GMCH DDR(2 OF 6)

842Tuesday, January 03, 2006

1

of

1ACustom

Page 9

5

www.bufanxiu.com

CLK_MCH_OE#

T4

MCH_RSVD_1

T3

MCH_RSVD_2

T2

MCH_RSVD_3

T186

MCH_RSVD_4

T52

MCH_RSVD_5

T41

MCH_RSVD_6

T44

MCH_RSVD_7

T49

MCH_RSVD_8

T25

TV_DCONSEL0

T5

TV_DCONSEL1

T8

MCH_RSVD_11

T161

MCH_RSVD_12

MCH_BSEL0(4)

MCH_BSEL1(4)

MCH_BSEL2(4)

PM_BMBUSY#(18)

PM_EXTTS#0(14,15)

PM_EXTTS#1(14,18)

DELAY_VR_PWRGOOD(18,41)

1.8VSUS

T167

T168

T7

T14

T28

T45

T37

T29

T40

T35

T36

PM_THRMTRIP#(5,16)

R400

100/F

T185

T160

T184

T162

T164

T166

T180

T182

T183

T157

T181

T158

T188

T159

T189

T163

T178

T165

T179

R106

80.6/F

M_RCOMP#

M_RCOMP

R107

80.6/F

MCH_RSVD_13

MCH_RSVD_14

MCH_RSVD_15

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

MCH_CFG_3

MCH_CFG_4

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

PM_BMBUSY#

PM_EXTTS#0

PM_EXTTS#1

RST IN# MCH

SDVO_CtrlClk

SDVO_CtrlData

MCH_ICH_SYNC

TP_MCH_NC0

TP_MCH_NC1

TP_MCH_NC2

TP_MCH_NC3

TP_MCH_NC4

TP_MCH_NC5

TP_MCH_NC6

TP_MCH_NC7

TP_MCH_NC8

TP_MCH_NC9

TP_MCH_NC10

TP_MCH_NC11

TP_MCH_NC12

TP_MCH_NC13

TP_MCH_NC14

TP_MCH_NC15

TP_MCH_NC16

TP_MCH_NC17

TP_MCH_NC18

5

D D

C C

PLT_RST-R#(17)

SDVO_CtrlClk(13)

SDVO_CtrlData(13)

MCH_ICH_SYNC(17)

B B

15mils/10mils

A A

AG11

AF11

AH33

AH34

BA41

BA40

BA39

AY41

AW41

AW1

+3V

H32

T32

R32

K30

A41

A35

A34

D28

D27

K16

K18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

K27

G28

F25

H26

H28

H27

K28

C41

BA3

BA2

BA1

B41

AY1

A40

A39

U27B

F3

F7

H7

J19

J29

J18

J25

J26

G6

D1

C1

B2

A4

A3

RSVD_0

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PM_THRMTRIP#

PWROK

RSTIN#

SDVO_CTRLCLK

SDVO_CTRLDATA

LT_RESET#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

Calistoga

R399 10K/F

R397 *10K/F

CFGRSVD

PM

MISC

NC

PM_EXTTS#0

PM_EXTTS#1

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

DDR MUXINGCLKDMI

SM_VREF_0

SM_VREF_1

G_CLKIN#

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

4

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

G_CLKIN

4

3

M_CLK_DDR0

AY35

M_CLK_DDR1

AR1

M_CLK_DDR2

AW7

M_CLK_DDR3

AW40

M_CLK_DDR#0

AW35

M_CLK_DDR#1

AT1

M_CLK_DDR#2

AY7

M_CLK_DDR#3

AY40

M_CKE0

AU20

M_CKE1

AT20

M_CKE2

BA29

M_CKE3

AY29

M_CS#0

AW13

M_CS#1

AW12

M_CS#2

AY21

M_CS#3

AW21

M_OCDCOMP_0

AL20

M_OCDCOMP_1

AF10

M_ODT0

BA13

M_ODT1

BA12

M_ODT2

AY20

M_ODT3

AU21

M_RCOMP#

AV9

M_RCOMP

AT9

AK1

AK41

CLK_PCIE_3GPLL#

AF33

CLK_PCIE_3GPLL

AG33

DREFCLK#

A27

DREFCLK

A26

DREFSSCLK#

C40

DREFSSCLK

D41

DMI_TXN0

AE35

DMI_TXN1

AF39

DMI_TXN2

AG35

DMI_TXN3

AH39

DMI_TXP0

AC35

DMI_TXP1

AE39

DMI_TXP2

AF35

DMI_TXP3

AG39

DMI_RXN0

AE37

DMI_RXN1

AF41

DMI_RXN2

AG37

DMI_RXN3 CRT_B

AH41

DMI_RXP0

AC37

DMI_RXP1

AE41

DMI_RXP2

AF37

DMI_RXP3

AG41

M_ODT0 (14,15)

M_ODT1 (14,15)

M_ODT2 (14,15)

M_ODT3 (14,15)

SMDDR_VREF

M_CLK_DDR0 (15)

M_CLK_DDR1 (15)

M_CLK_DDR2 (15)

M_CLK_DDR3 (15)

M_CLK_DDR#0 (15)

M_CLK_DDR#1 (15)

M_CLK_DDR#2 (15)

M_CLK_DDR#3 (15)

M_CKE0 (14,15)

M_CKE1 (14,15)

M_CKE2 (14,15)

M_CKE3 (14,15)

M_CS#0 (14,15)

M_CS#1 (14,15)

M_CS#2 (14,15)

M_CS#3 (14,15)

15mils/15mils

R104

*40.2/F

Layout as short as passable

NC from WW45

CLK_PCIE_3GPLL# (4)

CLK_PCIE_3GPLL (4)

DREFCLK# (4)

DREFCLK (4)

DREFSSCLK# (4)

DREFSSCLK (4)

DMI_TXN[3:0] (17)

S-CVBS

S-YD(35)

S-CD(35)

R411 150/F

R412 150/F

DMI_TXP[3:0] (17)

DMI_RXN[3:0] (17)

DMI_RXP[3:0] (17)

R414 75/F

CRT_B(32)

CRT_G(32)

CRT_R(32)

HSYNC(32)

VSYNC(32)

R71

*40.2/F

R398

1.5K/F

DDCCLK(32)

DDCDAT(32)

GMCH Strap pin need to check

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_16

MCH_CFG_19

MCH_CFG_18

MCH_CFG_20

R82 *2.2K

R103 *2.2K

R17 *2.2K

R77 *2.2K

R108 *2.2K

R109 *2.2K

R105 *2.2K

R95 *2.2K

R75 *2.2K

R396 *1K/F

R59 *1K

R41 *1K/F

+3V

+3V

+3V

1.MCH_CFG_5 Low = DMI X2, High=DMIX4

2.MCH_CFG_ 6 DDR : Low =Moby Dic k, High= Calis toga (Def ault)

3.MCH_CFG_7 CPU Strap Low=RSVD, High=Mobile CPU

4.MCH_CFG_9 PCI Exp Graphics Lane: Low =Reserved,High=Mobility

5.MCH_CFG_10 Host PLL VCC Select: Low=Reserved, High=Mobility

6.MCH_CFG_11: Low=Calistoga, High=Reserved

00 = Parti a l C L K g a t ing disable 01 = XOR mode enabled

10 = All Z mode enabled 11 = Normal operation ( Defaul t)

7.MCH_CFG_16 FSB Dynmic ODT: Low=Dynamic ODT Disabled,

High=Dynamic ODT Enabl ed.

8.MCH_CFG_19 DMI LANE Reversal:Low=Normal,

High=LANES Reversed.

9.MCH_CFG_18 VCC Select: LOW=1.05V, High=1.5V

10.MCH_CFG_20 PCIE Backward interpoerability mode: Low= only

SDVO or PCIE x1 is operational (defaults) ,High=SDVO and PCIE x1

are operation simultaneously via the PEG port.

3

+V1.5_PCIE

+3V

SMDDR_VREF

1.8VSUS

DPST_PWM(20)

LCD_BLON(20)

DISP_ON(20)

TXLCLKOUT-(20)

TXLCLKOUT+(20)

EDIDCLK(20)

EDIDDATA(20)

TXLOUT0-(20)

TXLOUT1-(20)

TXLOUT2-(20)

TXLOUT0+(20)

TXLOUT1+(20)

TXLOUT2+(20)

T1

LCD_BLON

DPST_PWM

LCD_BLON

L_CLKCTLA

L_CLKCTLB

EDIDCLK

EDIDDATA

L_IBG

L_VBG

DISP_ON

L_VREFH

L_VREFL

TXLCLKOUTTXLCLKOUT+

TXLOUT0TXLOUT1TXLOUT2-

TXLOUT0+

TXLOUT1+

TXLOUT2+

R25

100K

S-CVBS

S-YD

S-CD

TVIREF

R68 4.99K/F

< 0.1" . 15mils/15mils space

CRT_G

CRT_R

R409 150/F

R406 150/F

R408 150/F

R33 39/F

R64 255/F

R34 39/F

< 0.1" . 15mils/15mils space

use 1% R

HSYNC1

CRTIREF

VSYNC1

D32

H30

H29

G26

G25

C35

C33

C32

C37

G30

D30

D29

C18

D23

C22

C26

C25

G23

H23

J30

B38

F32

A33

A32

E27

E26

B35

A37

B37

B34

A36

F29

F30

F28

A16

A19

J20

B16

B18

B19

E23

B22

A21

B21

J22

2

+V1.5_PCIE (11)

+3V (4,5,11,13,14,15,16,17,18,19,20,24,29,30,31,32,33,34,35,36,38)

SMDDR_ VREF (15,40)

1.8VSUS (10,15, 36,40)

U27C

L_BKLTCTL

L_BKLTEN

L_CLKCTLA

L_CLKCTLB

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LB_CLK#

LB_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_IREF

CRT_VSYNC

Calistoga

TV

L_CLKCTLA

L_CLKCTLB

2

LVDS

VGA

R26 10K/F

R27 10K/F

EXP_A_COMPO

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

PCI-EXPRESS GRAPHICS

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

Place within 500 mils of GMCH

EXP_A_COMPI

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

Size Document Number R ev

Date: Sheet

+3V

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

1

EXP_A_COMPX

EXP_RXN2

EXP_RXP2

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

C34 0.1U

C25 0.1U

C32 0.1U

C27 0.1U

C35 0.1U

C26 0.1U

C33 0.1U

C28 0.1U

SMDDR_VREF

C190

0.1U

R15 24.9/F

C38

2.2U

Place close ball AK1/AK41

PROJECT : DW1

Quanta Computer Inc.

GMCH DMI VEDIO(3 OF 6)

1

+V1.5_PCIE

EXP_RXN2 (13)

EXP_RXP2 (13)

SDVOB_RED- (13)

SDVOB_GREEN- (13)

SDVOB_BLUE- (13)

SDVOB_CLK- (13)

SDVOB_RED+ (13)

SDVOB_GREEN+ (13)

SDVOB_BLUE+ (13)

SDVOB_CLK+ (13)

942Tuesday, J anuary 03, 2006

of

1ACustom

Page 10

5

www.bufanxiu.com

C478

330U/2.5V/ESR-9/POS

+

D D

C C

B B

A A

5

AA33

W33

AA32

W32

M32

AA31

W31

M31

AA30

W30

M30

AA29

W29

M29

AB28

AA28

M28

M27

M25

M24

AB23

AA23

M23

AC22

AB22

W22

M22

AC21

AA21

W21

M21

AC20

AB20

W20

M20

AB19

AA19

M19

M18

M17

M16

U27G

VCC_0

VCC_1

P33

VCC_2

N33

VCC_3

L33

VCC_4

J33

VCC_5

VCC_6

Y32

VCC_7

VCC_8

V32

VCC_9

P32

VCC_10

N32

VCC_11

VCC_12

L32

VCC_13

J32

VCC_14

VCC_15

VCC_16

V31

VCC_17

T31

VCC_18

R31

VCC_19

P31

VCC_20

N31

VCC_21

VCC_22

VCC_23

Y30

VCC_24

VCC_25

V30

VCC_26

U30

VCC_27

T30

VCC_28

R30

VCC_29

P30

VCC_30

N30

VCC_31

VCC_32

L30

VCC_33

VCC_34

Y29

VCC_35

VCC_36

V29

VCC_37

U29

VCC_38

R29

VCC_39

P29

VCC_40

VCC_41

L29

VCC_42

VCC_43

VCC_44

Y28

VCC_45

V28

VCC_46

U28

VCC_47

T28

VCC_48

R28

VCC_49

P28

VCC_50

N28

VCC_51

VCC_52

L28

VCC_53

P27

VCC_54

N27

VCC_55

VCC_56

L27

VCC_57

P26

VCC_58

N26

VCC_59

L26

VCC_60

N25

VCC_61

VCC_62

L25

VCC_63

P24

VCC_64

N24

VCC_65

VCC_66

VCC_67

VCC_68

Y23

VCC_69

P23

VCC_70

N23

VCC_71

VCC_72

L23

VCC_73

VCC_74

VCC_75

Y22

VCC_76

VCC_77

P22

VCC_78

N22

VCC_79

VCC_80

L22

VCC_81

VCC_82

VCC_83

VCC_84

N21

VCC_85

VCC_86

L21

VCC_87

VCC_88

VCC_89

Y20

VCC_90

VCC_91

P20

VCC_92

N20

VCC_93

VCC_94

L20

VCC_95

VCC_96

VCC_97

Y19

VCC_98

N19

VCC_99

VCC_100

L19

VCC_101

N18

VCC_102

VCC_103

L18

VCC_104

P17

VCC_105

N17

VCC_106

VCC_107

N16

VCC_108

VCC_109

L16

VCC_110

Calistoga

VCC

VCC_SM_0

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC_SM_37

VCC_SM_38

VCC_SM_39

VCC_SM_40

VCC_SM_41

VCC_SM_42

VCC_SM_43

VCC_SM_44

VCC_SM_45

VCC_SM_46

VCC_SM_47

VCC_SM_48

VCC_SM_49

VCC_SM_50

VCC_SM_51

VCC_SM_52

VCC_SM_53

VCC_SM_54

VCC_SM_55

VCC_SM_56

VCC_SM_57

VCC_SM_58

VCC_SM_59

VCC_SM_60

VCC_SM_61

VCC_SM_62

VCC_SM_63

VCC_SM_64

VCC_SM_65

VCC_SM_66

VCC_SM_67

VCC_SM_68

VCC_SM_69

VCC_SM_70

VCC_SM_71

VCC_SM_72

VCC_SM_73

VCC_SM_74

VCC_SM_75

VCC_SM_76

VCC_SM_77

VCC_SM_78

VCC_SM_79

VCC_SM_80

VCC_SM_81

VCC_SM_82

VCC_SM_83

VCC_SM_84

VCC_SM_85

VCC_SM_86

VCC_SM_87

VCC_SM_88

VCC_SM_89

VCC_SM_90

VCC_SM_91

VCC_SM_92

VCC_SM_93

VCC_SM_94

VCC_SM_95

VCC_SM_96

VCC_SM_97

VCC_SM_98

VCC_SM_99

VCC_SM_100

VCC_SM_101

VCC_SM_102

VCC_SM_103

VCC_SM_104

VCC_SM_105

VCC_SM_106

VCC_SM_107

AU41

AT41

AM41

AU40

BA34

AY34

AW34

AV34

AU34

AT34

AR34

BA30

AY30

AW30

AV30

AU30

AT30

AR30

AP30

AN30

AM30

AM29

AL29

AK29

AJ29

AH29

AJ28

AH28

AJ27

AH27

BA26

AY26

AW26

AV26

AU26

AT26

AR26

AJ26

AH26

AJ25

AH25

AJ24

AH24

BA23

AJ23

BA22

AY22

AW22

AV22

AU22

AT22

AR22

AP22

AK22

AJ22

AK21

AK20

BA19

AY19

AW19

AV19

AU19

AT19

AR19

AP19

AK19

AJ19

AJ18

AJ17

AH17

AJ16

AH16

BA15

AY15

AW15

AV15

AU15

AT15

AR15

AJ15

AJ14

AJ13

AH13

AK12

AJ12

AH12

AG12

AK11

BA8

AY8

AW8

AV8

AT8

AR8

AP8

BA6

AY6

AW6

AV6

AT6

AR6

AP6

AN6

AL6

AK6

AJ6

AV1

AJ1

4

VCC_SM1

VCC_SM2

VCC_SM106

VCC_SM107

4

C463 0.47U

C464 0.47U

+

330U/2.5V/ESR-9/POS

PC152

C89

0.47U

place Cap on BA23 Ball

C120

0.47U

place Cap on BA15 Ball

C483 0.47U

C484 0.47U

C469

10U/X6S

C193

10U/X6S

C73

0.1U

3

C194

10U/X6S

C124

0.1U

C143

1U

C79

0.1U

C45

0.1U

C82

0.1U

C105

0.1U

C486

C465

10U/X6S

330U/2.5V/ESR-9/POS

+

1.8VSUS

C154

0.47U

+1.05V+1.05V

AD27

AC27

AB27

AA27

W27

AD26

AC26

AB26

AA26

W26

AD25

AC25

AB25

AA25

W25

AD24

AC24

AB24

AA24

W24

AD23

AD22

AD21

AD20

AD19

AD18

AC18

AB18

AA18

W18

Y27

V27

U27

T27

R27

Y26

V26

U26

T26

R26

Y25

V25

U25

T25

R25

Y24

V24

U24

T24

R24

V23

U23

T23

R23

V22

U22

T22

R22

V21

U21

T21

R21

V20

U20

T20

R20

V19

U19

T19

Y18

V18

U18

T18

2

U27F

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

VCC_NCTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

Calistoga

NCTF

+1.5V_AUX(11)

VCCAUX_NCTF0

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VCCAUX_NCTF39

VCCAUX_NCTF40

VCCAUX_NCTF41

VCCAUX_NCTF42

VCCAUX_NCTF43

VCCAUX_NCTF44

VCCAUX_NCTF45

VCCAUX_NCTF46

VCCAUX_NCTF47

VCCAUX_NCTF48

VCCAUX_NCTF49

VCCAUX_NCTF50

VCCAUX_NCTF51

VCCAUX_NCTF52

VCCAUX_NCTF53

VCCAUX_NCTF54

VCCAUX_NCTF55

VCCAUX_NCTF56

VCCAUX_NCTF57

+1.05V(4,5,6,7,11 , 1 6,19,36,39)

1.8VSUS(9,15,36,40)

VSS_NCTF0

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

AE27

AE26

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AC17

Y17

U17

AG27

AF27

AG26

AF26

AG25

AF25

AG24

AF24

AG23

AF23

AG22

AF22

AG21

AF21

AG20

AF20

AG19

AF19

R19

AG18

AF18

R18

AG17

AF17

AE17

AD17

AB17

AA17

W17

V17

T17

R17

AG16

AF16

AE16

AD16

AC16

AB16

AA16

Y16

W16

V16

U16

T16

R16

AG15

AF15

AE15

AD15

AC15

AB15

AA15

Y15

W15

V15

U15

T15

R15

+1.5V_AUX

+1.05V

1.8VSUS

1

+1.5V_AUX

PROJECT : DW1

Size Document Number Rev

3

2

Date: Sheet

Quanta Computer Inc.

GMCH POWER(4 OF 6)

10 42Tuesday, January 03, 2006

1

of

1ACustom

Page 11

5

www.bufanxiu.com

+1.5V +V1.5_DPLLA

L10 10uH/0805

+

C103

C80

0.1U

470U_2.5V_12mOhm

L7 10uH/0805

D D

+

C22

C41

0.1U

470U_2.5V_12mOhm

L13 FCM2012C-121

C205

C192

22U

0.1U

L12 FCM2012C-121

C202

C171

22U

0.1U

R78

C C

+V1.5_PCIE

B B

A A

+1.05V

+1.5V

+V1.5_PCIE

+2.5V

+3V

10

L29

FCM2012C-121

C461

C457

10U/X6S

10U/X6S

R392

0.5/F

+1.5V_AUX

+V3.3_TVDAC +3V

R122

0

C94

0.1U

V1_5SFOLLOW

R405

10

+1.05V (4,5,6,7,10,16,19,36,39)

+1.5V (6,17,19,34,36,39)

+V1.5_PCIE (9)

+2.5V (13,35,36,39)

+3V (4,5,9,13,14,15 ,1 6,1 7, 18,19,20,24,29,30,31,32,33,34,35,36,38)

5

+V1.5_DPLLB

+V1.5_HPLL

+V1.5_MPLL

25mils

VCCGFOLLOW

L27

100nH

+

C458

220U/4V/ESR=15

L28

1uH

+1.5V

30mils

R407 0

+V3.3_TVDAC

L11

FCM2012C-121

C112

10U/X6S

B stage:

Change C103/C22 heigh to 1.9mm

D4

PDZ5.6B

21

PCIE_L