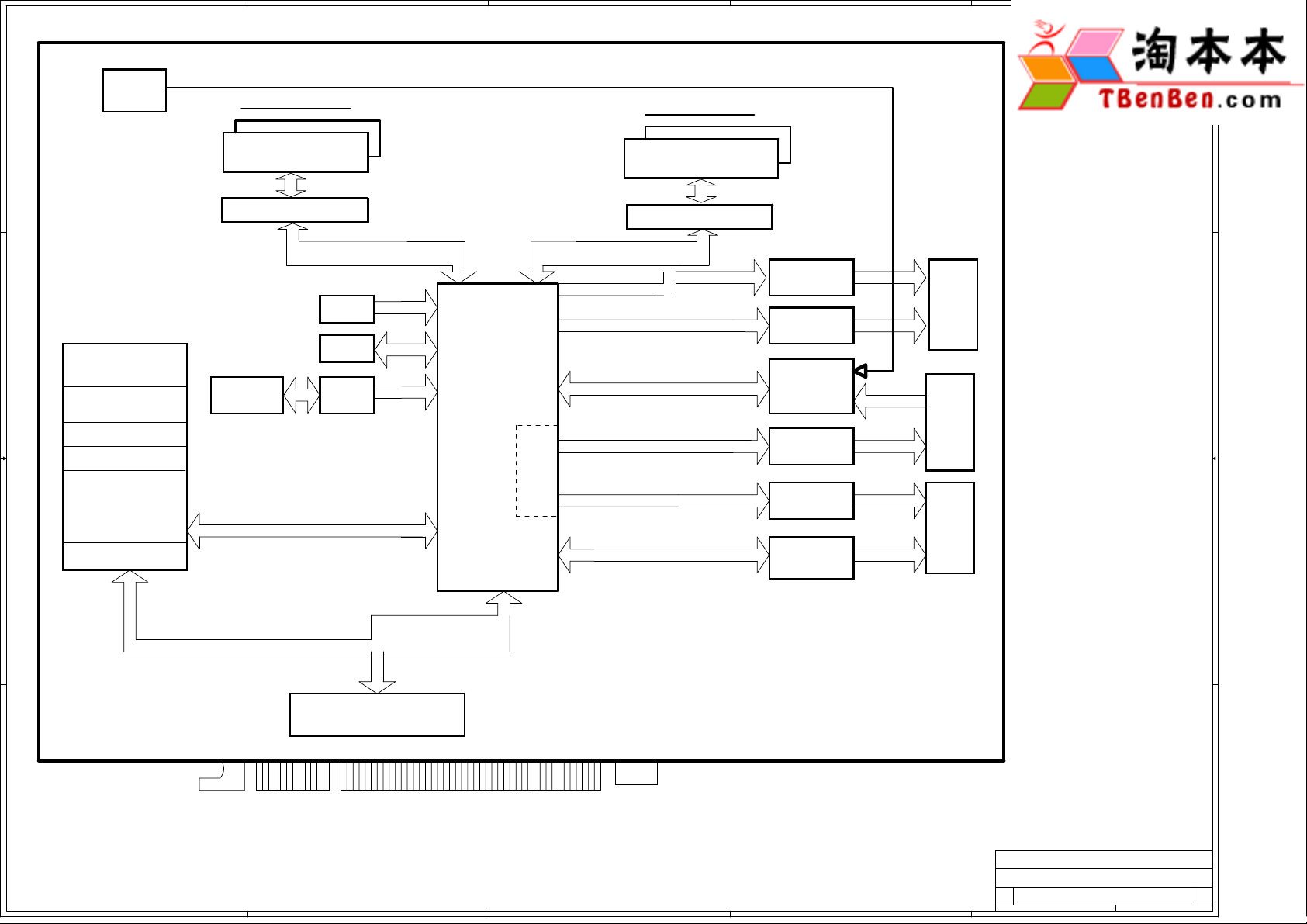

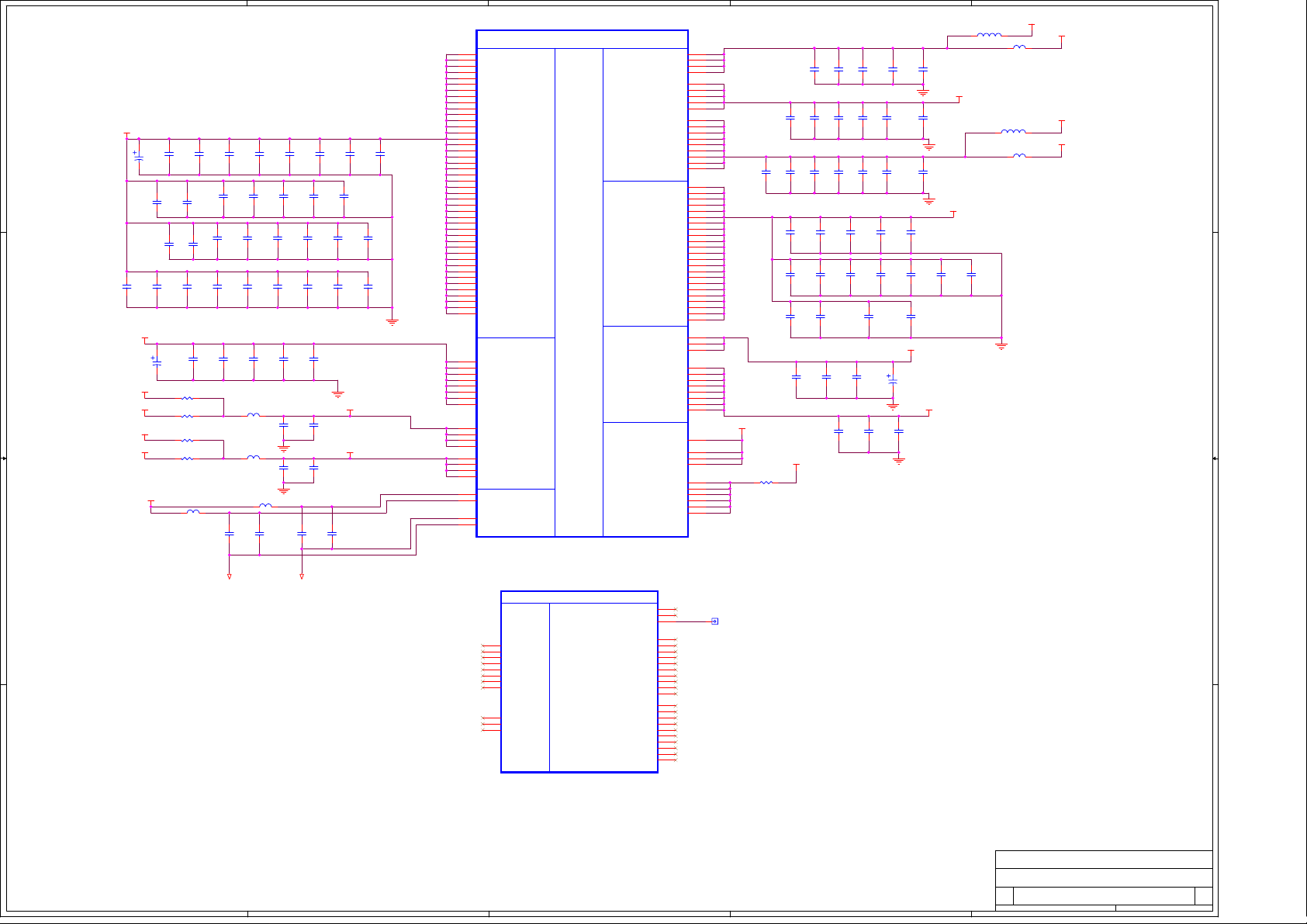

Page 1

5

(Disable)

VIDEO IN

CONNECTOR

SHT 20

D D

MEMORY CHANNEL A

Rank 1

Rank 0

GDDRI (144 BALL BGA)

SHT 13,14

4

3

2

1

MEMORY CHANNEL B

Rank 1

Rank 0

(Disable)

GDDRI (144 BALL BGA)

SHT 13,14

MEMORY TERMINATIONS A

SHT 12

MAA[14..0]

QSA[7..0]

CASA#

MDA[63..0]

QSA#[7..0]

RASA#

CLKA01

DQMA[0..7]

WEA#

CLKA01#

RESET

CSA#01

CKEA/B

MAB[14..0]

QSB[7..0]

CASB#

MAB[14..0]

RASB#

MEM A MEM B

STRAPS

SHT 15

C C

B B

POWER

REGULATION

SHT 5, 6, 7, 8, 9,10

From +12v

SINGLE PHASE SWITCHING:

VDDC, MVDDC, MVDDQ,+VTT

From +12V DIRECT:

FAN

From +12V LINEAR:

+5V, RAGE THEATER

From +3.3 V LINEAR:

AVDD, VDD15, VDDRH

TPVDD, TXVDDR, PVDD,

AVDDDI, A2VDD, A2VDDDI,

A2VDDQ, PCIE_VDDR,

PCIE_PVDD_18, VDDC_CT

VDDR4, VDDR5

From +3.3 V DIRECT:

VDDR3

Speed control

& temperature

SHT 17

sense

POWER DELIVERY

BIOS

SHT 4

FAN

SHT 15

ROMCS#

GPIO

ROM

SHEET 3, 4, 5, 6, 11

RV410

DAC1

DAC2

TMDS

VIP

TVO

CRT

TMDS_TX[C,2..0]N TMDS_TX[C,2..0]P HPD, DDC2CLK DDC2DATA

MEMORY TERMINATIONS B

(Disable)

DQMB[0..7]

WEB#

QSB#[7..0] RESET

CLKB01#

DVP

R G B HSY VSY DDC1DATA DDC1CLK

CSB#01

CKEBCLKB01

SHT 12

External TMDS

(Disable)

PRIMARY CRT

FILTERS

SHEET 16

Rage Theater 1

(Disable)

SHT 19

TVOUT

FILTERS

SHT 20

SECONDARY

CRT FILTERS

SHT 16, 17

IMPEDANCE

MATCHING

SHT 4

DVI-I

CONN

SHT 19

TVout/

VIVO

CONN

SHT 21

DVI-I

CONN

SHT 19

PCI-Express

PCI-Express Bus

SHT 2

A A

5

4

3

RV410 Trinity Board

2

Title

Size Docum e n t N u mb er Re v

C

Date: Sheet

GIGABYTE

RV410 Block_Diagram

RX70128IU-IU 0.1

1

122Wednesday, December 22, 2004

of

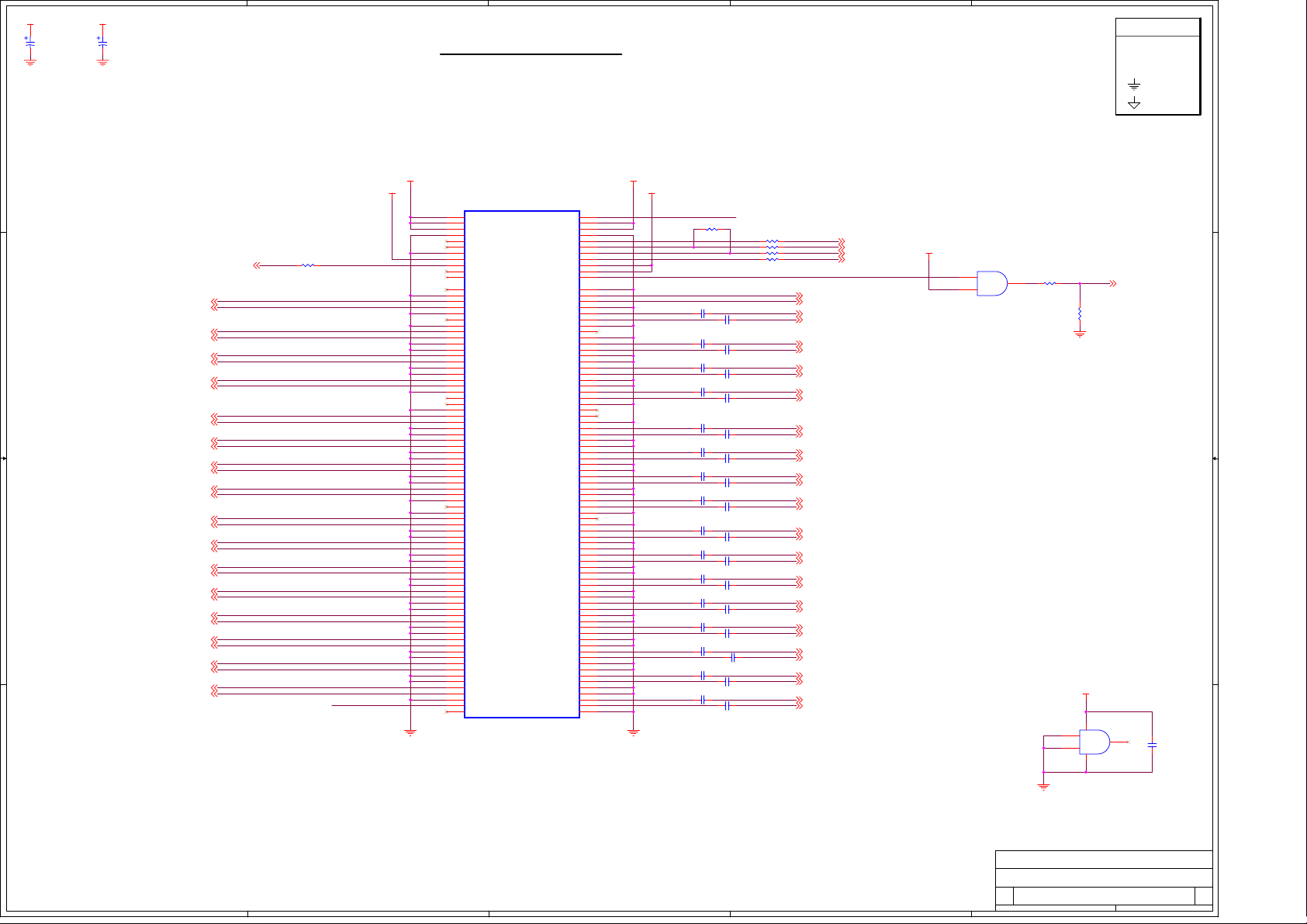

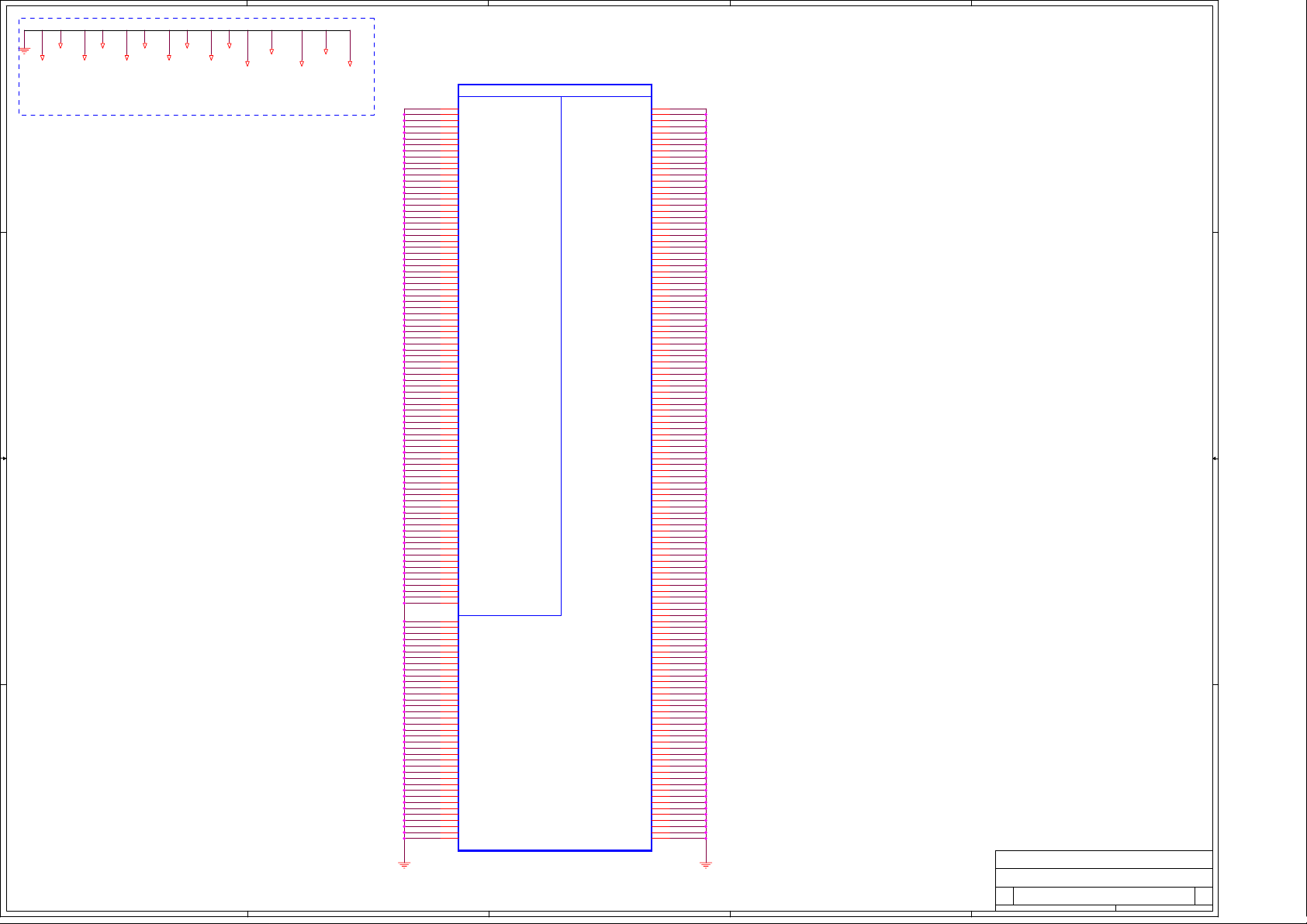

Page 2

5

+12V_BUS +3.3V_BUS

C10

100uF_16V

4260110700

D D

C3

100uF_16V

4260110700

4

PCI-EXPRESS BUS

3

2

1

SYMBOL LEGEND

DO NOT

DNI

INSTALL

#

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

+12V_BUS

+3.3V_BUS

MPCIE1

B1

+12V#B1

B2

+12V#B2

B3

RSVD#B3

B4

GND#B4

B5

SMCLK

B6

SMDAT

B7

GND#B7

DNI

3230000000

JTAG_TRST#

PRESENCE

HSYNC_DAC1(4,14,15)

PETp0_GFXRp0(3) PCIE_REFCLKN (3)

PETn0_GFXRn0(3)

PETp1_GFXRp1(3)

C C

B B

PETn1_GFXRn1(3)

PETp2_GFXRp2(3)

PETn2_GFXRn2(3)

PETp3_GFXRp3(3)

PETn3_GFXRn3(3)

PETp4_GFXRp4(3)

PETn4_GFXRn4(3)

PETp5_GFXRp5(3)

PETn5_GFXRn5(3)

PETp6_GFXRp6(3)

PETn6_GFXRn6(3)

PETp7_GFXRp7(3)

PETn7_GFXRn7(3)

PETp8_GFXRp8(3)

PETn8_GFXRn8(3)

PETp9_GFXRp9(3)

PETn9_GFXRn9(3)

PETp10_GFXRp10(3)

PETn10_GFXRn10(3)

PETp11_GFXRp11(3)

PETn11_GFXRn11(3)

PETp12_GFXRp12(3)

PETn12_GFXRn12(3)

PETp13_GFXRp13(3)

PETn13_GFXRn13(3)

PETp14_GFXRp14(3)

PETn14_GFXRn14(3)

PETp15_GFXRp15(3)

PETn15_GFXRn15(3)

R1008 0R/X

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

x16 PCIe/X

614NOPN084

Mechanical Key

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

+12V_BUS

+3.3V_BUS

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

PRESENCE

R1835 0R

C300

100nF

C302

100nF

C304

100nF

C306

100nF

C308

100nF

C310

100nF

C312

100nF

C314

100nF

C316

100nF

C318

100nF

C320

100nF

C322

100nF

C324

100nF

C326

100nF

C328

100nF

C330

100nF

3270002800

RP1D 0R/X

RP1C 0R/X

RP1B 0R/X

RP1A 0R/X

C301

100nF

C303

100nF

C305

100nF

C307

100nF

C309

100nF

C311

100nF

C313

100nF

C315

100nF

C317

100nF

C319

100nF

C321

100nF

C323

100nF

C325

100nF

C327

100nF

C329

100nF

C331

100nF

54

63

72

81

DNI

DNI

DNI

DNI

PCIE_REFCLKP (3)

GFXTp0_PERp0 (3)

GFXTn0_PERn0 (3)

GFXTp1_PERp1 (3)

GFXTn1_PERn1 (3)

GFXTp2_PERp2 (3)

GFXTn2_PERn2 (3)

GFXTp3_PERp3 (3)

GFXTn3_PERn3 (3)

GFXTp4_PERp4 (3)

GFXTn4_PERn4 (3)

GFXTp5_PERp5 (3)

GFXTn5_PERn5 (3)

GFXTp6_PERp6 (3)

GFXTn6_PERn6 (3)

GFXTp7_PERp7 (3)

GFXTn7_PERn7 (3)

GFXTp8_PERp8 (3)

GFXTn8_PERn8 (3)

GFXTp9_PERp9 (3)

GFXTn9_PERn9 (3)

GFXTp10_PERp10 (3)

GFXTn10_PERn10 (3)

GFXTp11_PERp11 (3)

GFXTn11_PERn11 (3)

GFXTp12_PERp12 (3)

GFXTn12_PERn12 (3)

GFXTp13_PERp13 (3)

GFXTn13_PERn13 (3)

GFXTp14_PERp14 (3)

GFXTn14_PERn14 (3)

GFXTp15_PERp15 (3)

GFXTn15_PERn15 (3)

VSYNC_DAC1 (4,14,15)

CRT1DDCDATA (4,15)

SCL (4,16,17)

CRT1DDCCLK (4,15)

PERST#

+5V

74ACT08MTC

5

4

R3 100R

6

U2B

1

2

R4

180R

402

+5V

14

+-U2A

74ACT08MTC

7

PERST#_buf (3,17,19)

3

C1

4.7uF

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

A A

Title

Size Docum e n t N u mb er Re v

C

5

4

3

2

Date: Sheet

Spare gate

GIGABYTE

PCI-Express_Connector

RX70128IU-IU 0.1

1

222Tuesday, De ce mber 21, 2004

of

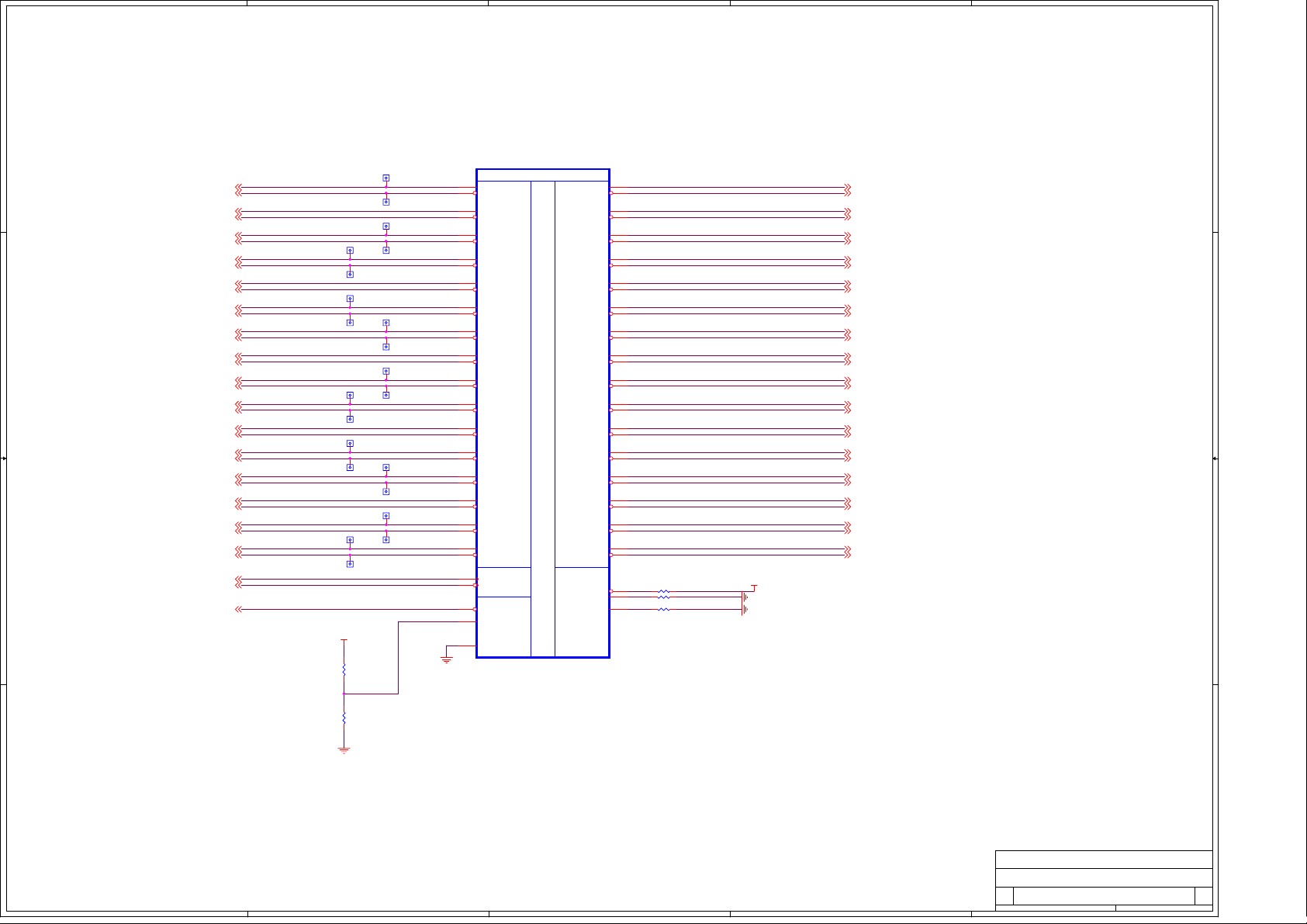

Page 3

5

4

3

2

1

NOTE: some of the PCIE testpoints will

be available trought via on traces.

D D

AH31

AH30

AG30

AG32

AF32

AF31

AE31

AE30

AD30

AD32

AC32

AC31

AB31

AB30

AA30

AA32

AK28

AG24

AA24

AF24

AJ31

W31

W30

AL28

Y32

Y31

V30

V32

U32

U31

T31

T30

R30

R32

P32

P31

N31

U1A

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

PCIE_REFCLKP

PCIE_REFCLKN

PERSTB

PCIE_TEST

MCL_0

RV410

TP34

TP35

TP38

TP39

TP46

TP47

TP50

TP51

TP58

TP59

TP28

TP29

TP32

TP33

TP40

TP41

TP44

TP45

TP52

TP53

TP56

TP57

PETp0_GFXRp0(2)

PETn0_GFXRn0(2)

PETp1_GFXRp1(2)

PETn1_GFXRn1(2)

PETp2_GFXRp2(2)

PETn2_GFXRn2(2)

PETp3_GFXRp3(2)

PETn3_GFXRn3(2)

PETp4_GFXRp4(2)

PETn4_GFXRn4(2)

PETp5_GFXRp5(2)

PETn5_GFXRn5(2)

PETp6_GFXRp6(2)

C C

B B

PETn6_GFXRn6(2)

PETp7_GFXRp7(2)

PETn7_GFXRn7(2)

PETp8_GFXRp8(2)

PETp9_GFXRp9(2)

PETn9_GFXRn9(2)

PETp10_GFXRp10(2)

PETn10_GFXRn10(2)

PETp11_GFXRp11(2)

PETn11_GFXRn11(2)

PETp12_GFXRp12(2)

PETn12_GFXRn12(2)

PETp13_GFXRp13(2)

PETn13_GFXRn13(2)

PETp14_GFXRp14(2)

PETn14_GFXRn14(2)

PETp15_GFXRp15(2)

PETn15_GFXRn15(2)

PCIE_REFCLKP(2)

PCIE_REFCLKN(2)

PERST#_buf(2,17,19)

+3.3V_BUS

R1007

4.7K/X

NI

Clock

PART 1 OF 7

P

C

I

E

X

P

R

E

S

S

I

N

T

E

R

F

A

C

E

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

PCIE_CALRN

PCIE_CALRP

PCIE_CALI

AK27

AJ27

AJ25

AH25

AH28

AG28

AG27

AF27

AF25

AE25

AE28

AD28

AD27

AC27

AC25

AB25

AB28

AA28

AA27

Y27

Y25

W25

W28

V28

V27

U27

U25

T25

T28

R28

R27

P27

AE24

AD24

AB24

R1010 100R

R1009 150R

R1011 10K

+PCIE_VDDR

GFXTp0_PERp0 (2)

GFXTn0_PERn0 (2)

GFXTp1_PERp1 (2)

GFXTn1_PERn1 (2)

GFXTp2_PERp2 (2)

GFXTn2_PERn2 (2)

GFXTp3_PERp3 (2)

GFXTn3_PERn3 (2)

GFXTp4_PERp4 (2)

GFXTn4_PERn4 (2)

GFXTp5_PERp5 (2)

GFXTn5_PERn5 (2)

GFXTp6_PERp6 (2)

GFXTn6_PERn6 (2)

GFXTp7_PERp7 (2)

GFXTn7_PERn7 (2)

GFXTp8_PERp8 (2)

GFXTn8_PERn8 (2)PETn8_GFXRn8(2)

GFXTp9_PERp9 (2)

GFXTn9_PERn9 (2)

GFXTp10_PERp10 (2)

GFXTn10_PERn10 (2)

GFXTp11_PERp11 (2)

GFXTn11_PERn11 (2)

GFXTp12_PERp12 (2)

GFXTn12_PERn12 (2)

GFXTp13_PERp13 (2)

GFXTn13_PERn13 (2)

GFXTp14_PERp14 (2)

GFXTn14_PERn14 (2)

GFXTp15_PERp15 (2)

GFXTn15_PERn15 (2)

R1006

4.7K

A A

Title

Size Docum e n t N u mb er Re v

C

5

4

3

2

Date: Sheet

GIGABYTE

RV410_PCIE_Interface

RX70128IU-IU 0.1

1

322Tuesday, De ce mber 21, 2004

of

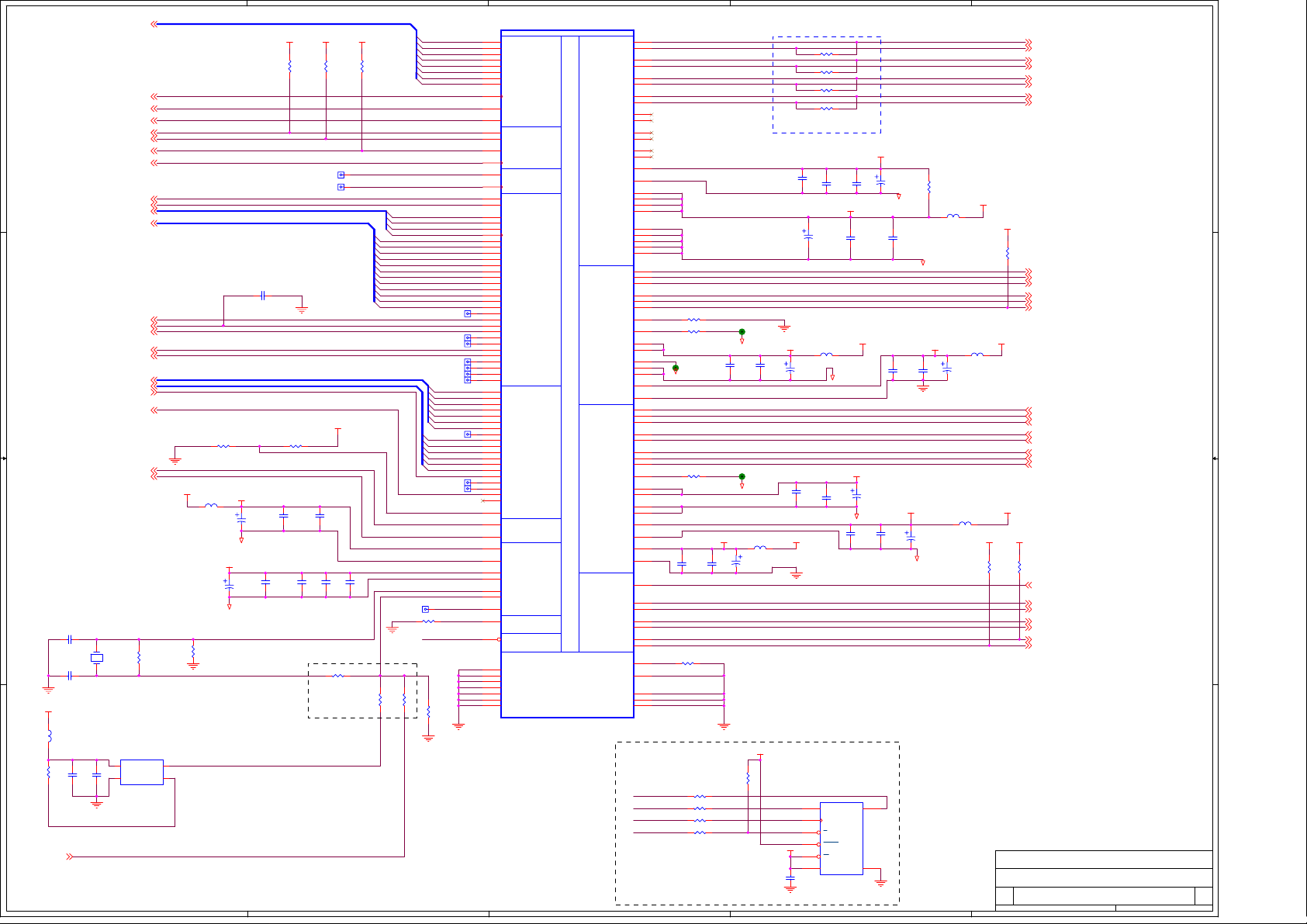

Page 4

5

VID[7..0]

VID[7..0](19)

CLK_VIDCLK(19)

DVALID(14)

D D

C C

B B

C71

12pF

C79

12pF

+3.3V_BUS

B3

220R/X

R1625

1K/X

A A

C1523

C1522

100nF/X

1.0uF/X

4170010400

CLK_RT(19)

PSYNC(14)

VHAD0(19)

VHAD1(19)

VPHCTL(19)

CLK_VIPCLK(19)

DVOMODE_0(14)

DVOMODE_1(14)

LCDCNTL_R[3..0](17)

VID/DVO_R[11..0](17)

DC_Strap2(14)

DC_Strap3(14,20)

DC_Strap4(14)

PAL/NTSC(14)

DEMUX_SEL(14)

GPIO[6..0](14)

GPIO[13..8](14)

HPD_ExtTMDS(17)

ThermINT(16)

GPU_DPLUS(16)

GPU_DMINUS(16)

27MHZ

Y3

27_MHZ

2 1

XTAL

Oscillator Circuit

Y1

4

VCC

2

GND

27.000MHz/X

5

R30

1.0M

OUT

E/D

LCDCNTL_R[3..0]

VID/DVO_R[11..0]

Install close to ASIC to provide

return path for EMI

+VDD_1.8V

B33

NI

Bead/X

GND_PVSS

+MPVDD

GND_MPVSS

XTALIN

R65

NI

150R/X

3

1

R586499R

+PVDD

C46

22uF_16V

4170082000

C27

22uF_16V

+3.3V_BUS

C52582pF

C45

100nF

4170010400

+3.3V_BUS +3.3V_BUS

R51

4.7K

TP12

TP13

R587499R

C26

100nF

4170010400

1.0uF

C44

R64 0R

Overlap pads

R58

4.7K

+3.3V_BUS

C41

1.0uF

1.0uF

C43

1.0uF

C42

PVDD

PVSS

R61

221R/X

4

R60

4.7K

4

DVOMODE_0

DVOMODE_1

MPVDD

MPVSS

R62

221R/X

LCDCNTL_R0

LCDCNTL_R1

LCDCNTL_R2

LCDCNTL_R3

VID/DVO_R0

VID/DVO_R1

VID/DVO_R2

VID/DVO_R3

VID/DVO_R4

VID/DVO_R5

VID/DVO_R6

VID/DVO_R7

VID/DVO_R8

VID/DVO_R9

VID/DVO_R10

VID/DVO_R11

TP14

R43 1K

ROMCS#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

TP60

TP61

TP62

TP63

TP64

TP65

TP66

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

TP67

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

HPD_ExtTMDS

TP68

TP69

XTALIN

XTALOUT

R66

150R/X

TESTEN

AF10

AG10

AE10

AE13

AF13

AG12

AH12

AJ14

AH14

AL26

AM26

AG14

AG22

AK17

AJ19

AF18

AH17

AG17

AG19

AH19

AH9

AJ8

AH8

AG9

AH7

AG8

AF7

AH6

AF8

AE9

AG7

AF9

AK4

AL4

AF2

AF1

AF3

AG1

AG2

AG3

AH2

AH3

AJ2

AJ1

AK2

AK1

AK3

AL2

AL3

AM3

AE6

AF4

AF5

AG4

AJ3

AH4

AJ4

AG5

AH5

AF6

AE7

AG6

AD4

AD2

AD1

AD3

AC1

AC2

AC3

AB2

AC6

AC5

AC4

AB3

AB4

AB5

AD5

AB8

AA8

AB7

AB6

AC8

A6

A5

AC7

U1B

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

VID_7

VPCLK0

DVALID

PSYNC

VHAD_0

VHAD_1

VPHCTL

VIPCLK

SDA

SCL

DVOVMODE_0

DVOVMODE_1

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPCLK

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

NC_22

VREFG

DPLUS

DMINUS

PVDD

PVSS

MPVDD

MPVSS

XTALIN

XTALOUT

PLLTEST

TESTEN

ROMCSb

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

RV410

VIP

Capture

VIP

Host

MMI2C

General

Purpose

I/O

Thermal

Diode

PLL &

XTAL

Test

ROM

PART 2 OF 7

V

I

D

E

O

&

M

U

L

T

I

M

E

D

I

A

Zoom Video Port/ VIP Host/External TMDS

3

Integrated

TMDS

TXVDDR_1

TXVDDR_2

TXVDDR_3

TXVDDR_4

TXVSSR_1

TXVSSR_2

TXVSSR_3

TXVSSR_4

TXVSSR_5

DAC / CRT

GENERICA

GENERICB

AVDD_1

AVDD_2

AVSSN_1

AVSSN_2

DAC2 (TV/CRT2)

H2SYNC

V2SYNC

A2VDD_1

A2VDD_2

A2VSSN_1

A2VSSN_2

A2VDDQ

A2VSSQ

Monitor

Interfa ce

DDC1DATA

DDC1CLK

DDC2DATA

DDC2CLK

DDC3DATA

DDC3CLK

GENERICC

VSS_175

VSS_174

VSS_173

3

AL9

TXCM

AM9

TXCP

AK10

TX0M

AL10

TX0P

AL11

TX1M

AM11

TX1P

AL12

TX2M

AM12

TX2P

AK9

TX3M

AJ9

TX3P

AK11

TX4M

AJ11

TX4P

AK12

TX5M

AJ12

TX5P

AM8

TPVDD

AL8

TPVSS

AJ6

AK6

AL6

AM6

AJ7

AK7

AL7

AM7

AK8

AK24

R

AM24

G

AL24

B

AJ23

HSYNC

AJ22

VSYNC

AK22

R33 1K

AF23

R52 499R

AL22

RSET

AVSSQ

VDD1DI

VSS1DI

COMP

R2SET

VDD2DI

VSS2DI

HPD1

MCL_1

AL25

AM25

AK23

AK25

AJ24

AM23

AL23

AK15

R2

AM15

G2

AL15

B2

AF15

AG15

AJ15

Y

AJ13

C

AH15

AK14

AM16

AL16

AM17

AL17

AL14

AK13

AJ16

AJ17

AF11

AH22

AH23

AH13

AG13

AE12

AF12

AE23

AE18

AF22

AF17

AF21

GPIO8

GPIO9

GPIO10

ROMCS#

AVDD

GND_AVSSQ

R55 715R

GND_R2SET

1.0uF

C35

R34 1K

7 2

5 4

6 3

8 1

GND_RSET

+VDD2DI

C36

100nF

4170010400

RP193B33R

RP193D33R

RP193C33R

RP193A33R

SERIAL EEPROM 512K/1M

C7

1.0uF

DNI

B8 26

22uF_16V

C34

R91

10K

C40

100nF

4170010400

+3.3V_BUS

ROM_SO

SI/A16

SCK/WEb

CSb

HOLD1

2

R797 274R

R796 274R

R795 274R

R794 274R

INSTALL TERMINATION RESISTORS

CLOSE TO ASIC

1.0uF

C17

C15

82pF

4170082000

TXVDDR

C9

C8

22uF_16V

82pF

4170082000

+VDD_1.8V

Ba3

B5

+AVDD

26

C23

22uF_16V

GND_AVSSN

+A2VDD

1.0uF

DNI

C31

GND_A2VSSN

+VDD_1.8V

5

6

1

7

+3.3V_BUS

3

8

C80

100nF

4170010400

ALTERNATIVE PART :M25P05( 512Kbit)

C33

100nF

4170010400

U11

D

C

S

HOLD

W

VCC

M25P05-VMN6T

C32

1.0uF

C37

Q

VSS

2

+TPVDD

C13

100nF

4170010400

22uF_16V

2

4

C16

22uF_16V

GND_TPVSS

C21

100nF

4170010400

1.0uF

C29

+A2VDDQ

C38

100nF

4170010400

GND_A2VSSQ

C39

22uF_16V

R44

Rk

0R/X

DNI

Ba2

B4

26

GND_TXVSSR

+VDDDI

C30

100nF

4170010400

Ba5

1

TXCM (18)

TXCP (18)

TX0M (18 )

TX0P (18)

TX1M (18 )

TX1P (18)

TX2M (18 )

TX2P (18)

+VDD_1.8V

+3.3V_BUS

R50

4.7K

R_DAC1 (15)

G_DAC1 (15)

B_DAC1 (15)

HSYNC _DAC1 (2,14,15)

VSYNC_DAC1 (2,14,15)

STEREOSYNC (20)

+VDD_1.8V

B7

C28

26

22uF_16V

R_DAC2 (15)

G_DAC2 (15)

B_DAC2 (15)

HSYNC_DAC2 (15)

VSYNC_DAC2 (15)

Y_DAC2 (20)

C_DAC2 (20)

COMP_DAC2 (20)

+VDD_1.8V

B9

26

+3.3V_BUS

+3.3V_BUS

R54

R53

4.7K

4.7K

HPD1 (18)

CRT1DDCDATA (2,15)

CRT1DDCCLK (2,15)

CRT2DDCDATA (15)

CRT2DDCCLK (15)

SDA (16,17)

SCL (2,16,17)

Title

Size Docum e n t N u mb er Re v

C

Date: Sheet

GIGABYTE

RV410_Main

RX70128IU-IU 0.1

1

of

422Tuesday, De ce mber 21, 2004

Page 5

5

D D

C C

+MVDDQ

C616

1uF

+3.3V_BUS

+VDD_1.8V

+VDD_1.8V

+3.3V_BUS

+MVDDQ

C68

47uF_6.3V

C600

1uF

C64

C70

10uf

10uf

C65

10uf

C617

C618

1uF

1uF

C67

22uF_16V

DNI

DNI

B29 220R

C602

C603

C613

1uF

C620

1uF

C609

1uF

C625

1uF

C604

1uF

1uF

C611

C610

1uF

1uF

C615

C614

1uF

1uF

C622

C621

1uF

1uF

C627

C626

1uF

1uF

1.0uF

C74

C709

100nF

C75

1.0uF

C667

C669

1uF

1uF

C601

1uF

1uF

C608

1uF

C612

C73

1uF

10uf

C619

1uF

C66

C624

1.0uF

1uF

R700R/X

R690R

R680R/X

R670R

B12

220R

B14

220R

B30 220R

C668

1uF

C605

1uF

+VDDR4

4170010400

+VDDR5

C710

100nF

4170010400

C670

1uF

C623

1uF

C707

4

U1E

C1

VDDR1_1

J1

VDDR1_2

M1

VDDR1_3

R1

VDDR1_4

V1

VDDR1_5

AA1

VDDR1_6

A3

VDDR1_7

P9

VDDR1_8

J10

VDDR1_9

N9

VDDR1_10

P10

VDDR1_11

A9

VDDR1_12

Y10

VDDR1_13

P8

VDDR1_14

R9

VDDR1_15

Y9

VDDR1_16

J11

AB10

AC19

AD18

AC20

AD19

AD20

VDDR1_17

A21

VDDR1_18

M10

VDDR1_20

N10

VDDR1_21

Y8

VDDR1_22

J18

VDDR1_23

J19

VDDR1_24

K21

VDDR1_25

A12

VDDR1_26

H13

VDDR1_27

A15

VDDR1_28

J20

VDDR1_29

J13

VDDR1_30

K11

VDDR1_31

K19

VDDR1_32

A18

VDDR1_33

L23

VDDR1_34

K20

VDDR1_35

K24

VDDR1_36

L24

VDDR1_37

H19

VDDR1_38

A24

VDDR1_39

K13

VDDR1_40

J32

VDDR1_41

A30

VDDR1_42

C32

VDDR1_43

F32

VDDR1_45

L32

VDDR1_46

AB9

VDDR3_1

VDDR3_2

AA9

VDDR3_3

VDDR3_4

VDDR3_5

VDDR3_6

VDDR3_7

VDDR3_8

AJ5

VDDR4_1

AM5

VDDR4_2

AL5

VDDR4_3

AK5

VDDR4_4

AE2

VDDR5_1

AE3

VDDR5_2

AE4

VDDR5_3

AE5

VDDR5_4

A27

VDDRH0

F1

VDDRH1

A28

VSSRH0

E1

VSSRH1

RV410

C607

C606

1uF

1uF

C69

1uF

C708

1uF

1uF

C676

1uF

Clock

I/O

PART 5 OF 7

Memory I/O

I/0

Memory

3

+VDD_1.8V

+PCIE_V DDR _12

C981

1uF

R714.7K

+A2VDD

C970

1uF

C982

1uF

C632

1uF

C637

1uF

C61

10uf

1uF

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

VDD15_1

VDD15_2

VDD15_3

VDDCI_1

VDDCI_2

VDDCI_3

VDDCI_4

VDDCI_5

VDDCI_6

VDDCI_7

VDDCI_8

VDDL0

VDDL0_1

VDDL0_2

VDDL0_3

VDDL1_1

VDDL1_2

VDDL1_3

VDDL2_1

VDDL2_2

VDDL2_3

V23

N23

P23

U23

N29

N28

N27

N26

N25

AL31

AM31

AM30

AL32

AL30

AM28

AL29

AM29

AM27

AC11

AC12

P14

U15

W14

W15

R17

R15

V15

V16

T16

U16

T17

U17

V14

R18

T18

V18

P18

P19

R19

W19

AD11

AC13

AC16

AC18

W10

T14

W17

P16

AC15

T23

K14

U19

AE19

AF20

AE20

AF19

AC21

AC22

AD22

AE21

AD21

AE22

PCIE_PVDD_12_1

PCIE_PVDD_12_2

PCIE_PVDD_12_3

PCIE_PVDD_12_4

PCIE_PVDD_18_1

PCIE_PVDD_18_2

PCIE_PVDD_18_3

PCIE_PVDD_18_4

PCIE_PVDD_18_5

PCIE_VDDR_12_1

PCIE_VDDR_12_2

PCIE_VDDR_12_3

PCIE_VDDR_12_4

PCIE_VDDR_12_5

PCIE_VDDR_12_6

PCIE_VDDR_12_7

PCI-Express

PCIE_VDDR_12_8

PCIE_VDDR_12_9

P

O

W

E

R

I/O Internal Core

2

+VDDC

ALT: 0R

L7 1.8uH/X

B27 200R

C978

C633

1uF

C638

1uF

C62

10uf

C979

1uF

1uF

C971

C976

1uF

1uF

C972

C973

1uF

1uF

C634

1uF

C639

1uF

C59

10uF_10V

C49

C50

1uF

1uF

C646

C648

1uF

1uF

C977

1uF

C974

1uF

C983

1uF

C48

C1675

10uF_6.3V

C1668

10uF_6.3V

C635

1uF

C640

1uF

C968

1uF

+VDDC_CT

C53

22uF_16V

C60

10uf

C1703

10uF_6.3V

C1704

10uF_6.3V

C1702

10uF_6.3V

C636

1uF

C641

1uF

C63

10uF_10V

+VDDC+3.3V_BUS

+PCIE_PVDD_18

+VDDC

C642

1uF

L6 1.8uH/X

B23 60R

C644

1uF

+PCIE_VDDR

ALT: 0R

+PCIE_VDDR

1

+VDDC

B B

A A

5

GND_VSSRH0

GND_VSSRH1

U1G

Forward

Compatibility

Y23

BBN_4

K15

BBN_3

R10

BBN_2

AC17

BBN_1

AC14

BBP_4

M23

BBP_3

V10

BBP_2

K18

BBP_1

L10

VDD25B_1

K22

VDD25B_2

AA10

VDD25A

RV410

4

PART 7 OF 7

No Connect

AD12

NC_0

AE11

NC_1

AD23

GENERICD

AJ21

NC_2

AK21

NC_3

AH21

NC_4

AG21

NC_5

AG20

NC_6

AH20

NC_7

AK20

NC_8

AJ20

NC_9

AG18

NC_10

AH18

NC_11

AK19

NC_12

AL19

NC_13

AL20

NC_14

AM20

NC_15

AL21

NC_16

AM21

NC_17

AK18

NC_18

AJ18

NC_19

AL18

NC_20

AM18

NC_21

3

TP11

Title

Size Docum e n t N u mb er Re v

C

2

Date: Sheet

GIGABYTE

RV410_Power_and_NC

RX70128IU-IU 0.1

1

522Tuesday, De ce mber 21, 2004

of

Page 6

5

GND_TPVSS

GND_MPVSS GND_A2VSSN

GND_PVSS

GND_AVSSN

NOTE: THIS IS A DRAWING. THESE

GROUNDS MUST BE MANUALLY

CONNECTED TO THE GROUND PLANE

D D

C C

B B

A A

GND_TXVSSR

5

GND_A2VSSQ

GND_AVSSQ

GND_RSET

GND_R2SET

GND_VSSRH1

GND_VSSRH0

GND_RT

GND_VIN

GND_TVVSSN

4

U1F

AH27

PCIE_VSS_1

AC23

PCIE_VSS_2

AL27

PCIE_VSS_3

R23

PCIE_VSS_4

P25

PCIE_VSS_5

R25

PCIE_VSS_6

T26

PCIE_VSS_7

U26

PCIE_VSS_8

W26

PCIE_VSS_9

Y26

PCIE_VSS_10

AB26

PCIE_VSS_11

AC26

PCIE_VSS_12

AD25

PCIE_VSS_13

AE26

PCIE_VSS_14

AF26

PCIE_VSS_15

AD26

PCIE_VSS_16

AG25

PCIE_VSS_17

AH26

PCIE_VSS_18

AC28

PCIE_VSS_19

Y28

PCIE_VSS_20

U28

PCIE_VSS_21

P28

PCIE_VSS_22

AH29

PCIE_VSS_23

AF28

PCIE_VSS_24

V29

PCIE_VSS_25

AC29

PCIE_VSS_26

W27

PCIE_VSS_27

AB27

PCIE_VSS_28

V26

PCIE_VSS_29

AJ26

PCIE_VSS_30

AJ32

PCIE_VSS_31

AK29

PCIE_VSS_32

P26

PCIE_VSS_33

P29

PCIE_VSS_34

R29

PCIE_VSS_35

T29

PCIE_VSS_36

U29

PCIE_VSS_37

W29

PCIE_VSS_38

Y29

PCIE_VSS_39

AA29

PCIE_VSS_40

AB29

PCIE_VSS_41

AD29

PCIE_VSS_42

AE29

PCIE_VSS_43

AF29

PCIE_VSS_44

AG29

PCIE_VSS_45

AJ29

PCIE_VSS_46

AK26

PCIE_VSS_47

AK30

PCIE_VSS_48

AG26

PCIE_VSS_49

N30

PCIE_VSS_50

R31

PCIE_VSS_51

AF30

PCIE_VSS_52

AC30

PCIE_VSS_53

V31

PCIE_VSS_54

P30

PCIE_VSS_55

AA31

PCIE_VSS_56

U30

PCIE_VSS_57

AD31

PCIE_VSS_58

AK32

PCIE_VSS_59

AJ28

PCIE_VSS_60

Y30

PCIE_VSS_61

AJ30

PCIE_VSS_62

AK31

PCIE_VSS_63

AA23

PCIE_VSS_64

AG31

PCIE_VSS_65

N24

PCIE_VSS_66

W23

PCIE_VSS_67

AB23

PCIE_VSS_69

P24

PCIE_VSS_70

R24

PCIE_VSS_71

T24

PCIE_VSS_72

U24

PCIE_VSS_73

V24

PCIE_VSS_74

W24

PCIE_VSS_75

Y24

PCIE_VSS_76

AC24

PCIE_VSS_77

AH24

PCIE_VSS_78

V25

PCIE_VSS_79

AA25

PCIE_VSS_80

R26

PCIE_VSS_81

AA26

PCIE_VSS_82

T27

PCIE_VSS_83

AE27

PCIE_VSS_84

B1

VSS_1

H1

VSS_2

L1

VSS_3

P1

VSS_4

U1

VSS_5

Y1

VSS_6

AD7

VSS_7

AE8

VSS_8

AL1

VSS_9

A2

VSS_10

AM2

VSS_11

AD10

VSS_12

E8

VSS_13

H5

VSS_14

K10

VSS_15

M8

VSS_16

T10

VSS_17

E12

VSS_18

AC9

VSS_19

AF14

VSS_20

AD8

VSS_21

C5

VSS_22

F10

VSS_23

J3

VSS_24

L6

VSS_25

M6

VSS_26

P6

VSS_27

AA4

VSS_28

AG11

VSS_29

V3

VSS_30

AG16

VSS_31

R3

VSS_32

C6

VSS_33

C9

VSS_34

F6

VSS_35

H7

VSS_36

J6

VSS_37

RV410

4

Part 6 of 7

PCI-Express GND

CORE GND

3

AD16

VSS_45

AA6

VSS_44

P7

VSS_43

P5

VSS_42

M3

VSS_41

M9

VSS_40

L7

VSS_39

M7

VSS_38

AD17

VSS_47

AH11

VSS_48

A8

VSS_49

U7

VSS_50

C10

VSS_51

E9

VSS_52

F3

VSS_53

J9

VSS_54

N7

VSS_55

N3

VSS_56

Y5

VSS_57

AM13

VSS_58

AC10

VSS_59

Y6

VSS_60

U6

VSS_61

E5

VSS_62

AL13

VSS_63

A11

VSS_64

U8

VSS_65

U9

VSS_66

U10

VSS_67

R6

VSS_68

AD6

VSS_69

V6

VSS_70

AD14

VSS_71

AD13

VSS_72

D11

VSS_73

J12

VSS_74

K12

VSS_75

A13

VSS_77

F13

VSS_78

E13

VSS_79

F15

VSS_80

K16

VSS_81

J21

VSS_82

H16

VSS_83

T15

VSS_84

V17

VSS_85

C15

VSS_86

C4

VSS_87

U14

VSS_88

P15

VSS_89

A16

VSS_90

E16

VSS_91

G13

VSS_92

G16

VSS_93

P17

VSS_94

R16

VSS_95

R14

VSS_97

W16

VSS_98

C18

VSS_99

F16

VSS_100

W18

VSS_101

U18

VSS_102

AE16

VSS_103

AE17

VSS_104

A19

VSS_105

H32

VSS_106

F19

VSS_107

G19

VSS_108

N8

VSS_109

Y7

VSS_110

T19

VSS_112

V19

VSS_113

G21

VSS_114

C21

VSS_115

F21

VSS_116

AE14

VSS_117

AK16

VSS_118

U5

VSS_119

F22

VSS_120

F18

VSS_121

K30

VSS_122

C24

VSS_124

F24

VSS_125

M24

VSS_126

A25

VSS_127

D30

VSS_128

E25

VSS_129

G25

VSS_130

G20

VSS_131

G22

VSS_132

F27

VSS_133

E28

VSS_134

H21

VSS_135

C27

VSS_136

E32

VSS_137

H28

VSS_138

J30

VSS_139

K17

VSS_140

K27

VSS_141

M32

VSS_142

A22

VSS_143

C20

VSS_144

E19

VSS_145

H20

VSS_146

J24

VSS_147

M28

VSS_148

J28

VSS_149

J16

VSS_150

F30

VSS_151

K23

VSS_152

L29

VSS_153

A31

VSS_154

B32

VSS_155

E30

VSS_156

AE15

VSS_157

AG23

VSS_158

AD9

VSS_159

AF16

VSS_160

AH10

VSS_161

AJ10

VSS_163

AD15

VSS_164

AH16

VSS_165

3

2

Title

Size Docum e n t N u mb er Re v

C

2

Date: Sheet

1

GIGABYTE

RV410_Core_GND

RX70128IU-IU 0.1

1

of

622Tuesday, De ce mber 21, 2004

Page 7

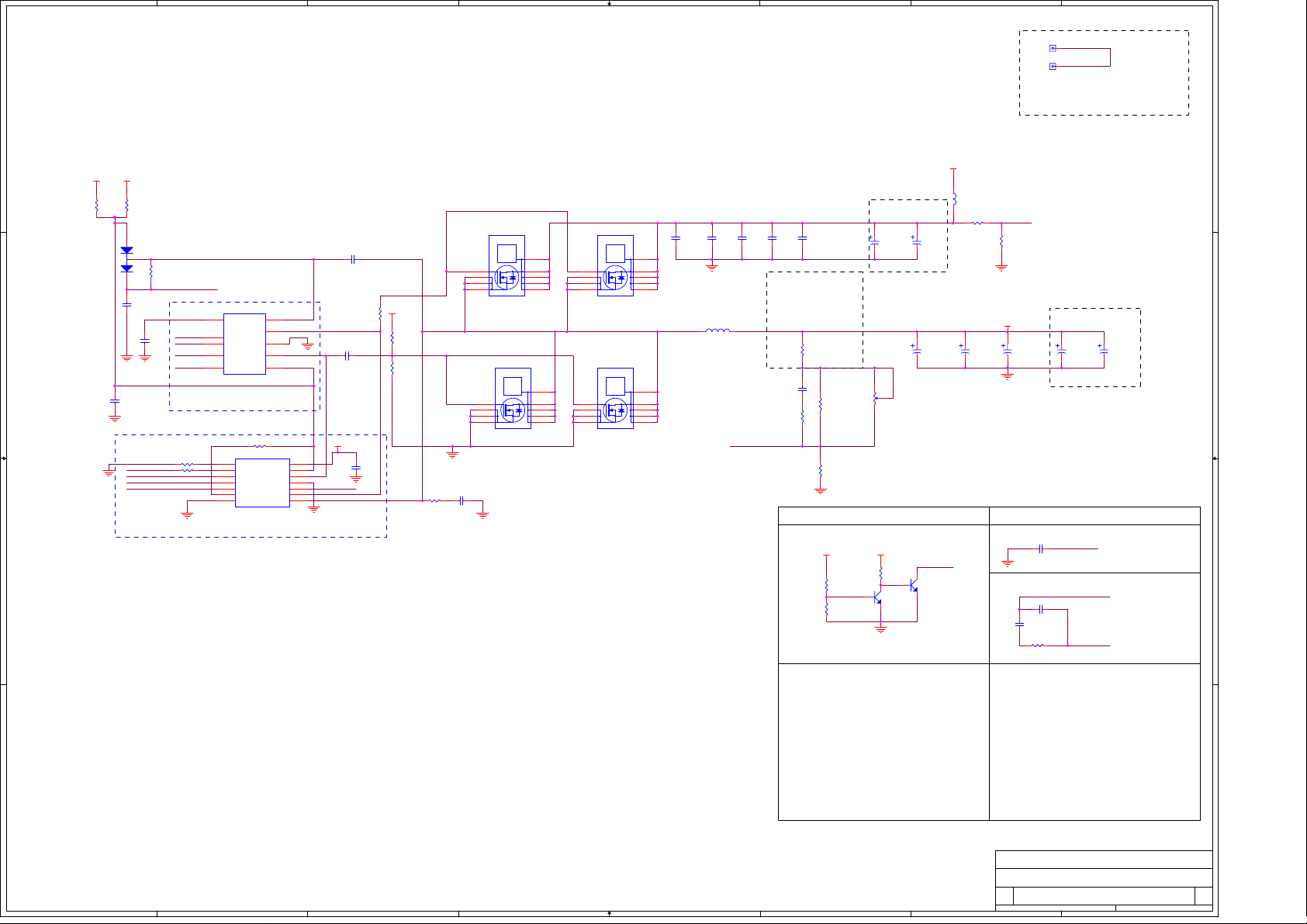

8

7

6

5

4

3

2

1

CORE REGULATOR VDDC

TP1

I_VDDC_LOO P

TP2

Current loop to measure

VDDC output current.

D D

+5V

+12V_BUS

R1589

R1591

0R/X

2R2

1

D28

BAT54SLT1

BST3

3

R1595

0R/X

2

C C

C1692

1uF

Alternative 1

+PW_VDDC3

SS_VDDC3

COMP_VDDC3

B B

DNI

C1151

0.22uF/X

BOOT_VDDC3

SS_VDDC3

Fb_VDDC3

COMP_VDDC3

C1157

22nf

UVIN3

SWN3

VCC3

Alternative 2

R1598 51K/X

R1602 3K/X

U43

7

BST

SS

GH

4

Vfb

5

GND

COMP

6

GL

UVIN

8

Vcc

SWN

SP6132

SIPEX SP6132

R1686 10K/X

MU43

1

RT

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB/X

ISL6522CB : SOIC

ISL6522CV : TSSOP

10

9

3

2

1

PVCC

LGATE

PGND

BOOT

UGATE

PHASE

VCC

BST3

UGATE3

LGATE3

VCC3

14

13

12

11

10

9

8

C1688 100nF

0

C1689

+12V_BUS

BOOT_VDDC3Fb_VDDC3

R1619

10R

C1690

1uF/X

+3.3V_BUS

DNI

SWN3

10K/X

10K/X

R873

R1594

R1618

2.2R/X

Q28

Thermal

Pad

FDS7096N3

Q29

Thermal

Pad

4 5

3

2

1

FDS7096N3

9

6

7

8

9

6

7

8

C1159

1nF/X

4 5

3

2

1

Lower MOSFET should be surrounded by

a lot of copper for heat dissipation

+PW_VDDC3

Q30

Thermal

Pad

4 5

3

2

1

FDS7096N3

Q31

Thermal

Pad

4 5

3

2

1

FDS7096N3

VR1

1K/X

DNI

C1705

180uF_16V/X

Dual footprint

2

1 3

NI

C1149

C1146

10uF

C1532

1.0uF

9

6

7

8

9

6

7

8

10uF

L63

HC1213

Fb_VDDC3

C1147

10uF

Do not install

This resistor will

be shorted in layout.

It is present to

prevent feedback to

be taken at the wrong

place.

C1158

1nf/X

DNI

R1617

1.5K/X

DNI

C1148

10uF

Cc1

Rc4

R1588

0R/X

Rc1

R1592

10K

1%

Rc2

R1597

16.5K

1%

POWER SEQUENCING CIRCUIT:

+3.3V_BUS

R1581

5.1K

R1582

2.4K

1

Q7

CMPT3904

+12V_BUS

R1583

20K

CMPT3904

2 3

FOR ALTERNATE #1

Remove R374, R375, R371, C168 and U32

Install R370 , R112, R954, R305-R308, C160

C159 and MU32

+12V_BUS

B1

60R

R1593

UVIN3

MC1705

470UF

C1152

330uF_2.5V

Cout1

220K

C1153

330uF_2.5V

+VDDC

R1632

100K

C1154

330uF_2.5V/X

C1155

470uF_10V/X

DNI

MC1155

470uF

Dual footprint

DESIGN NOTES:

Add this Capacitor for SP6132

SS_VDDC3

1

2 3

Q8

Compensation Circuit

Cc2

Cc4

COMP_VDDC3

C1161

5.6nF

Rc5

COMP_VDDC3

C1164

100pF

C1163

27pF

R1580

42.2K

Cc3

Fb_VDDC3

FOR ALTERNATE #2

Change C157 for 10 uF and C121 for 1 uF

Replace C764 by 0 Ohm resistor

Replace R314 with a bead

Remove R954, R370, R305-R308, C159,

R112, C160 and MU32

Install R374, R375, R371, C168 and U32

Compensation circuit

A A

Rc1 = 10K, Rc2 = 8.06K

R313 = 93.1K, C171 = 3.9 nF, C170 = 10 pF

Title

Size Docum e n t N u mb er Re v

C

8

7

6

5

4

3

Date: Sheet

2

GIGABYTE

Regulator VDDC

RX70128IU-IU 0.1

of

722Tuesday, De ce mber 21, 2004

1

Page 8

8

+5V

+12V_BUS

R373

R372

2R2/X

0R

1

D4

BAT54SLT1

3

C142

1uF

2

DNI

C136

0.22uF/X

C141

22nf

D D

Alternative 1

+PW_VDDC1

SS_VDDC1

COMP_VDDC1

Fb_VDDC1

C C

MVDDQ Switching Regulator for

Memory Core for 256M

configuration

BST1

R376

0R

BOOT_VDDC1

SS_VDDC1

Fb_VDDC1

COMP_VDDC1

UVIN1

SWN1

VCC1

Alternative 2

R258 51K

R259 3K

U31

7

BST

SS

GH

4

Vfb

5

GND

COMP

6

GL

UVIN

8

Vcc

SWN

SP6132/X

SIPEX SP6132

R257 10K

MU31

1

RT

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB

PVCC

LGATE

PGND

BOOT

UGATE

PHASE

7

0

C765

R251

10R

C113

1uF

SWN1

+3.3V_BUS

R953

DNI

10K/X

R952

DNI

10K/X

C122 100nF

BST1

10

UGATE1

9

3

LGATE1

2

VCC1

1

+12V_BUS

14

VCC

13

12

11

BOOT_VDDC1

10

9

8

R255

2.2R

6

MQ21A

BSO4804

MQ21B

BSO4804

+PW_VDDC1

C137

10uF

L65

3.3uH

C110

1nf

DNI

Cc1 Rc5

R254

1.5K

DNI

Rc4

71

8

2

53

6

4

Fb_VDDC1

C116

1nF

+12V_BUS

Rc1

R253

1.54K

1%

Rc2

R256

1.24K

1%

C138

10uF

5

B21

60R

R377

220K/X

VR2

13

1K/X

2

TP3

TP4

R378

100K/X

C106

MC106

22uF/X

22uF_16V

Cout1

I_MVDDC_LOOP

UVIN1

Current loop to measure

4

3

POWER SEQUENCING CIRCUIT:

2

DESIGN NOTES:

1

Add this Cap ac ito r for ALTERNATE #2

C140

100pF/X

COMP_VDDC1

C111

33pF

C112

10nF

R264

15K

COMP_VDDC1

Cc3

Fb_VDDC1

R250

2K

R249

2.4K

1

Q9

CMPT3904

+12V_BUS

R248

20K

CMPT3904

2 3

SS_VDDC1

1

2 3

Q10

Compensation Circuit

Cc2

FOR ALTERNATE #2

Change C142 for 10uF

Install R377, R378, R373, C122, C140

and U31

Remove R255, C116, R372, R376, D4,

MU31, R257, R258, R259 and C113

+MVDDC

+MVDDQ

C104

22uF

Dual footprint

DNI

MC104

22uF_16V/X

C107

470uF_10V/X

FOR ALTERNATE #1

Install R372, D4, R376, C113, R257,

R258, R259, MU31, R255 and C116

Remove R373, R377, R378, C122,

C140 and U31

DNIDNI

MC105

C105

22uF_16V/X

10uF

Dual footprintDual footprint

Compensation circuit

Rc1 = 10K, Rc2 = 8.06K

R264 = 41.2K, C111 = 27 pF

MVDDQ output current.

ISL6522CB : SOIC

+5V

+12V_BUS

R371

R370

2R2/X

0R

1

D5

BAT54SLT1

3

2

DNI

C158

0.22uF/X

C157

1uF

C169

22nf

B B

Alternative 1

+PW_VDDC2

SS_VDDC2

COMP_VDDC2

MVDDC Switching Regulator for

Memory Core for 256M

configuration

BST2

R112

0R

BOOT_VDDC2

U32

10

BST

SS

9

GH

Vfb

3

GND

COMP

2

GL

UVIN

1

Vcc

SWN

SP6132/X

SIPEX SP6132

R307 10K

MU32

1

RT

2

OCSET

PVCC

3

SS

LGATE

4

COMP

PGND

5

FB

BOOT

6

EN

UGATE

7

GND

PHASE

ISL6522CB

ISL6522CB : SOIC

ISL6522CV : TSSOP

UGATE2

LGATE2

VCC

Fb_VDDC2

COMP_VDDC2

UVIN2

SWN2

VCC2

Alternative 2

R305 51K

R306 3K

7

4

5

6

8

BST2

VCC2

14

13

12

11

10

9

8

BOOT_VDDC2Fb_VDDC2

C121 100nF

R314

10R

0

C764

+12V_BUS

C159

1uF

+3.3V_BUS

DNI

DNI

R955

10K/X

R954

10K/X

SWN2

R308

2.2R

2

4

71

8

MQ23A

BSO4804

53

6

MQ23B

BSO4804

Fb_VDDC2

C160

1nF

+12V_BUS

B28

+PW_VDDC2

L66

3.3uH

C161

1nf

DNI

R309

1.5K

DNI

Cc1

Rc4

C172

10uF

Rc1

R310

2.55K

1%

Rc2

R311

1.21K

1%

C163

10uF

60R

VR3

13

1K/X

2

R374

220K/X

C164

22uF/X

Cout1

Lower MOSFET should be surrounded by

a lot of copper for heat dissipation

UVIN2

R375

100K/X

MC164

22uF_16V

C165

10uF

+MVDDC

DNIDNI DNI DNI

C166

MC165

22uF_16V/X

22uF/X

MC166

22uF_16V

Dual footprintDual footprintDual footprint

TP5

I_MVDDQ_LOOP

TP6

Current loop to measure

MVDDC output current.

***

***

Dual footprint

C1706

470uF_10V/X

MC1706

330uF_6.3V

FOR ALTERNATE #1

Remove R374, R375, R371, C168 and U32

Install R370 , R112, R954, R305-R308, C160

C159 and MU32

DESIGN NOTES:

Add this Capacitor for SP6132

Compensation Circuit

Cc2

Rc5

C171

10nF

COMP_VDDC2

C168

100pF /X

Cc4

COMP_VDDC2SS_VDDC2

C170

Cc3

33pF

Fb_VDDC2

R313

15K

FOR ALTERNATE #2

Change C157 for 10 uF and C121 for 1 uF

Replace C764 by 0 Ohm resistor

Replace R314 with a bead

Remove R954, R370, R305-R308, C159,

R112, C160 and MU32

Install R374, R375, R371, C168 and U32

Compensation circuit

Rc1 = 10K, Rc2 = 8.06K

R313 = 93.1K, C171 = 3.9 nF, C170 = 10 pF

A A

RP602A 0R/X

81

RP602B 0R/X

72

RP602C 0R/X

63

RP602D 0R/X

54

DNI

C987

100nF/X

C988

100nF/X

C986

100nF/X

402 402 402402

8

+MVDDQ MOSFET can be removed and

derive +MVDDQ form +MVDDC

Maximum current measurement must be

obtained and MOSFET dissipation must be

checked

These caps are foo tpri nt-shared alternate of Resistor array RP2

If Plane is not shorted, Decoupling caps can be

C989

used between +MVDDC and +MVDDQ

100nF/X

7

6

+MVDDQ+MVDDQ +MVDDC+MVDDC

RP198A 0R/X

RP198B 0R/X

RP198C 0R/X

RP198D 0R/X

C990

100nF/X

+MVDDQ MOSFET can be removed and

81

72

63

54

derive +MVDDQ form +MVDDC

Maximum current measurement must be

obtained and MOSFET dissipation must be

checked

DNI

C991

100nF/X

402402

C992

100nF/X

These caps are foo tpri nt-shared alternate of Resistor array RP2

If Plane is not shorted, Decoupling caps can be

C993

used between +MVDDC and +MVDDQ

100nF/X

5

Title

Size Docum e n t N u mb er Re v

C

4

3

Date: Sheet

2

GIGABYTE

Memory regulators

RX70128IU-IU 0.1

of

822Friday, April 01, 2005

1

Page 9

5

4

3

2

1

Current limit circuit M A X 125 mA

+12V_BUS

+1.8V Regulator +1.5V Regulator for VDDC_CT (VDD15)

R1448

R406

1.0M

R1447

220R

R404

3.32R

23

TL431CDBVR

Q19

MMBT3906

1

Max: 55 mA

R139

R140

681R

1%

R141

1.50K

1%

+3.3V_BUS

B22 200R

R128

+VDDC_CT

33R

R125

432R

AS432S

1%

1

R127

MREG7

2.0K

3 2

1%

REGULATOR

FOR PVDD

(+1.8V)

Max: 55 mA Max: 20 mA Max: 20 mA

+PVDD

27R

REG4

4

SC431LC5SK-1/X

NC

1

NC

2

5 3

GND_PVSS

C980

C984

10uF

10uF

REG7

4

SC431LC5SK-1/X

NC

1

NC

2

5 3

+3.3V_BUS+3.3V_BUS +3.3V_BUS

B15 200R

AS432S

1

MREG6

3 2

+VDD_1.8V

R143

R145

681R

1%

R147

1.50K

1%

75R

R108

1.0K

C127

100nF

B1320 0R

4

1

2

+3.3V_BUS

R110

2K

C126

10uf

REGULATOR

FOR TPVDD

(+1.8V)

NC

NC

5 3

C176

1.0uF

C175

1.0uF

REG6

SC431LC5SK-1/X

MREG1

1

RT9173ACL5

3

6

IN

VCNTL

REFEN4GND

VOUT

TAB

+5V

NI

R407

0R/X

+5VCON1(15,18,20)

B26 200R

AS432S

1

MREG5

3 2

Regulator for PCIE_VDDR

Vout = 1.2V

Iout = 1200mA MAX

5

2

R106

1K

23

R142

R144

681R

1%

R146

1.50K

1%

Q16

R405

4.7K

75R

1

MMBT3906

+5VCON1

CMPT3904

+MPVDD+TPVDD

4

1

2

+PCIE_VDDR

C167

10uF

Q17

2N7002E

1

Q18

REGULATOR

FOR

MPVDD(+1.8V)

NC

NC

5 3

GND_MPVSSGND_TPVSS

C173

22uF

1

2 3

REG5

SC431LC5SK-1/X

C174

22uF

32

+5V

+12V_BUS

C400

1uF

D D

C C

B B

+3.3V_BUS

B10

REG2

60R

LT1117CST

IN3OUT

C135

C134

100nF

22uF_16V

+3.3V_BUS

B24

200R

1

1uF

3

C145

GND_A2VSSN GN D _A2VSSN

+3.3V_BUS

C139

22uF_16V

REG3

VIN

SHDN

2.5V

B11

60R

C143

100nF

ADJ

1

BYPASS

GND

2

REG10

LT1117CST

IN3OUT

1

+VDD_1.8V

2

4

CASE

VOUT

CASE

ADJ

REGULATOR

FOR

A2VDD(+2.5V)

5

4

C147

470pF

DNI

+PCIE_PVDD_18

2

4

R129

49.9R

1%

R126

22.1R

1%

+A2VDD

1uF

C146

R130

49.9R

1%

R131

22.1R

1%

+VDD_1.8V

C131

100nF

B2

60R/X

C132

22uF_50V

B25 200R

AS432S

MREG4

3 2

+PCIE_PVDD_18

1

C957

10uf

REG29

220R

R1449

220R

R1042

14R

NC

NC

5 3

Regulator for +5V

Vout = 5V

Iout = 125mA MAX

R1450

220R

R1043

14R

R1

4

1

2

R2

R1040

2.0K

1%

402

R1041

2.0K

1%

402

+5V

C917

4.7uF

+VTT Linear Regulator

Vin = +MVDDQ

Vout = 1.25V

Iout = 2000mA MAX

Iout = 750mA Est. MAX

A A

1.4V

R273

1K

R275

1K

5

+MVDDQ

***

C133

470uF_6.3V

***

R1836

1.00K/X

R1838

1.00K/X

REG20

1

IN

REFEN4GND

RT9173ACL5/X

C2190

10uF/X

+3.3V_BUS

C130

47uF_6.3V/X

3

6

VOUT

TAB

VCNTL

+VTT

5

R1837

1K/X

4

***

C2189

22uF_16V/X

***

Title

Size Docum e n t N u mb er Re v

C

3

2

Date: Sheet

GIGABYTE

Miscellaneous_Regulators

RX70128IU-IU 0.1

1

922Friday, April 01, 2005

of

2

Page 10

5

4

3

2

1

RV410 MEMORY CHANNELS A and B

D D

MDA[63..0]

MDA[63..0](11,12,13)

C C

+MVDDQ

R137

100R

B B

R138

C149

100nF

100R

4170010400

+MVDDQ

R148

100R

R149

C148

100nF

100R

4170010400

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

U1C

M31

DQA_0

M30

DQA_1

L31

DQA_2

L30

DQA_3

H30

DQA_4

G31

DQA_5

G30

DQA_6

F31

DQA_7

M27

DQA_8

M29

DQA_9

L28

DQA_10

L27

DQA_11

J27

DQA_12

H29

DQA_13

G29

DQA_14

G27

DQA_15

M26

DQA_16

L26

DQA_17

M25

DQA_18

L25

DQA_19

J25

DQA_20

G28

DQA_21

H27

DQA_22

H26

DQA_23

F26

DQA_24

G26

DQA_25

H25

DQA_26

H24

DQA_27

H23

DQA_28

H22

DQA_29

J23

DQA_30

J22

DQA_31

E23

DQA_32

D22

DQA_33

D23

DQA_34

E22

DQA_35

E20

DQA_36

F20

DQA_37

D19

DQA_38

D18

DQA_39

B19

DQA_40

B18

DQA_41

C17

DQA_42

B17

DQA_43

C14

DQA_44

B14

DQA_45

C13

DQA_46

B13

DQA_47

D17

DQA_48

E18

DQA_49

E17

DQA_50

F17

DQA_51

E15

DQA_52

E14

DQA_53

F14

DQA_54

D13

DQA_55

H18

DQA_56

H17

DQA_57

G18

DQA_58

G17

DQA_59

G15

DQA_60

G14

DQA_61

H14

DQA_62

J14

DQA_63

C31

MVREFD_0

C30

MVREFS_0

RV410

Channel A

Part 3 of 7

MEMORY INTERFACE A

DDR1 D DR2 DDR3

bidir. differential strobe

Not used bidir. strobe

For DDR2

write strobe read strobe

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

MAA_15

DQMAb_0

DQMAb_1

DQMAb_2

DQMAb_3

DQMAb_4

DQMAb_5

DQMAb_6

DQMAb_7

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

QSA_0B

QSA_1B

QSA_2B

QSA_3B

QSA_4B

QSA_5B

QSA_6B

QSA_7B

ODTA

ODTA1

CLKA0

CLKA0b

CKEA0

RASA0b

CASA0b

WEA0b

CSA0b_0

CSA0b_1

CLKA1

CLKA1b

CKEA1

RASA1b

CASA1b

WEA1b

CSA1b_0

CSA1b_1

U1D

B12

DQB_0

C12

DQB_1

B11

DQB_2

C11

DQB_3

C8

DQB_4

B7

DQB_5

C7

DQB_6

B6

DQB_7

F12

DQB_8

D12

DQB_9

E11

DQB_10

F11

DQB_11

F9

DQB_12

D8

DQB_13

D7

DQB_14

F7

DQB_15

G12

DQB_16

G11

DQB_17

H12

DQB_18

H11

DQB_19

H9

DQB_20

E7

DQB_21

F8

DQB_22

G8

DQB_23

G6

DQB_24

G7

DQB_25

H8

DQB_26

J8

DQB_27

K8

DQB_28

L8

DQB_29

K9

DQB_30

L9

DQB_31

K5

DQB_32

L4

DQB_33

K4

DQB_34

L5

DQB_35

N5

DQB_36

N6

DQB_37

P4

DQB_38

R4

DQB_39

P2

DQB_40

R2

DQB_41

T3

DQB_42

T2

DQB_43

W3

DQB_44

W2

DQB_45

Y3

DQB_46

Y2

DQB_47

T4

DQB_48

R5

DQB_49

T5

DQB_50

T6

DQB_51

V5

DQB_52

W5

DQB_53

W6

DQB_54

Y4

DQB_55

R8

DQB_56

T8

DQB_57

R7

DQB_58

T7

DQB_59

V7

DQB_60

W7

DQB_61

W8

DQB_62

W9

DQB_63

B3

MVREFD_1

C3

MVREFS_1

AA3

DRAM_RST

AA5

TEST_MCLK

AA2

TEST_YCLK

AA7

MEMTEST

R166243R

RV410

+MVDDQ

+MVDDQ

R158

100R

R159

100R

R150

100R

R151

100R

MDB[63..0](11,12,13)

C151

100nF

4170010400

C150

100nF

4170010400

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

TEST_MCLK

TEST_YCLK

R1634.7K/X

R1564.7K

R1574.7K

NI

MAA0

D26

MAA1

F28

MAA2

D28

MAA3

D25

MAA4

E24

MAA5

E26

MAA6

D27

MAA7

F25

MAA8

C26

MAA9

B26

MAA10

D29

MAA11

B27

MAA12

B25

MAA13

C25

E27

CSA#1

E29

DQMA#0

H31

DQMA#1

J29

DQMA#2

J26

DQMA#3

G23

DQMA#4

E21

DQMA#5

B15

DQMA#6

D14

DQMA#7

J17

QSA0

J31

QSA1

K29

QSA2

K25

QSA3

F23

QSA4

D20

QSA5

B16

QSA6

D16

QSA7

H15

K31

K28

K26

G24

D21

C16

D15

J15

F29

D24

D31

E31

B30

RASA#

B28

CASA#

C29

WEA#

B31

CSA#0

B29

C28

B20

C19

C22

B24

B22

B21

B23

C23

MAA[13..0] (11,12,13)

CSA#1 (11,12,13)

DQMA#[7..0] (11,12,13)

QSA[7..0] (11,12,13)

CLKA0 (11,12,13)

CLKA#0 (11, 12,13)

CKEA (11,12,13)

RASA# (11,12,13)

CASA# (11,12,13)

WEA# (11,12,13)

CSA#0 (11,12)

CLKA1 (11,12,13)

CLKA#1 (11, 12,13)

Channel B

Part 4 of 7

MEMORY INTERFACE B

DDR1 DDR2 D DR3

read strobe

Not used bidir. strobe

bidir. differential strobe

write strobe

For DDR2

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13

MAB_14

MAB_15

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

QSB_0B

QSB_1B

QSB_2B

QSB_3B

QSB_4B

QSB_5B

QSB_6B

QSB_7B

ODTB

ODTB1

CLKB0

CLKB0b

CKEB0

RASB0b

CASB0b

WEB0b

CSB0b_0

CSB0b_1

CLKB1

CLKB1b

CKEB1

RASB1b

CASB1b

WEB1b

CSB1b_0

CSB1b_1

MAB0

G4

MAB1

E6

MAB2

E4

MAB3

H4

MAB4

J5

MAB5

G5

MAB6

F4

MAB7

H6

MAB8

G3

MAB9

G2

MAB10

D4

MAB11

F2

MAB12

H2

MAB13

H3

F5

CSB#1

D5

DQMB#0

B8

DQMB#1

D9

DQMB#2

G9

DQMB#3

K7

DQMB#4

M5

DQMB#5

V2

DQMB#6

W4

DQMB#7

T9

QSB0

B9

QSB1

D10

QSB2

H10

QSB3

K6

QSB4

N4

QSB5

U2

QSB6

U4

QSB7

V8

B10

E10

G10

J7

M4

U3

V4

V9

D6

J4

B4

B5

C2

RASB#

E2

CASB#

D3

WEB#

B2

CSB#0

D2

E3

N2

P3

L3

J2

L2

M2

K2

K3

MAB[13..0] (11,12,13)

CSB#1 (11, 12,13)

DQMB#[7..0] (11,12,13)

QSB[7..0] (11,12,13)

CLKB0 (11,12,13)

CLKB#0 (11, 12,13)

CKEB (11,12,13)

RASB# (11,12,13)

CASB# (11,12,13)

WEB# (11,12,13)

CSB#0 (11,12)

CLKB1 (11,12,13)

CLKB#1 (11, 12,13)

A A

Title

Size Docum e n t N u mb er Re v

C

5

4

3

2

Date: Sheet

GIGABYTE

RV410_MEM_A_B

RX70128IU-IU 0.1

1

of

10 22Tuesday, De ce mber 21, 2004

Page 11

8

+MVDDQ

C2163

0

D D

C2165

100nF/X

+MVDDQ

C2167

0

C2168

100nF/X

+MVDDQ

C2171

0

C C

C2172

100nF/X

+MVDDQ

C2174

0

C2176

100nF/X

+MVDDQ

C2178

0

B B

C2180

100nF/X

+MVDDQ

C2183

0

C2185

100nF/X

A A

+MVDDQ

+VTT

RP601A 56R/X

8 1

RP601B 56R/X

7 2

RP601C 56R/X

6 3

RP601D 56R/X

5 4

RP2A 56R/X

8 1

RP2B 56R/X

7 2

RP2C 56R/X

6 3

RP2D 56R/X

5 4

RP3A 56R/X

8 1

RP3B 56R/X

7 2

RP3C 56R/X

6 3

RP3D 56R/X

5 4

RP4A 56R/X

8 1

RP4B 56R/X

7 2

RP4C 56R/X

6 3

RP4D 56R/X

5 4

RP5D 56R/X

5 4

RP5C 56R/X

6 3

RP5B 56R/X

7 2

RP5A 56R/X

8 1

RP6D 56R/X

5 4

RP6C 56R/X

6 3

RP6B 56R/X

7 2

RP6A 56R/X

8 1

RP7D 56R/X

RP7C 56R/X

RP7B 56R/X

RP7A 56R/X

RP8D 56R/X

RP8C 56R/X

RP8B 56R/X

RP8A 56R/X

RP9A 56R/X

RP9B 56R/X

RP9C 56R/X

RP9D 56R/X

RP10A 56R/X

RP10B 56R/X

RP10C 56R/X

RP10D 56R/X

RP11A 56R/X

8 1

RP11B 56R/X

7 2

RP11C 56R/X

6 3

RP11D 56R/X

5 4

RP12A 56R/X

8 1

RP12B 56R/X

7 2

RP12C 56R/X

6 3

RP12D 56R/X

5 4

RP13A 56R/X

RP13B 56R/X

RP13C 56R/X

RP13D 56R/X

RP14A 56R/X

RP14B 56R/X

RP14C 56R/X

RP14D 56R/X

RP15A 56R/X

RP15B 56R/X

RP15C 56R/X

RP15D 56R/X

RP16A 56R/X

RP16B 56R/X

RP16C 56R/X

RP16D 56R/X

RP23A 56R/X

8 1

RP20B 56R/X

7 2

RP20A 56R/X

8 1

RP20D 56R/X

5 4

RP20C 56R/X

6 3

RP17A 56R/X

8 1

RP23B 56R/X

7 2

RP18D 56R/X

5 4

RP18A 56R/X

8 1

RP23C 56R/X

6 3

RP23D 56R/X

5 4

RP19A 56R/X

8 1

RP17C 56R/X

6 3

RP17D 56R/X

5 4

R189 56R/X

R190 56R/X

R192 56R/X

R194 56R/X

R196 56R/X

R198 56R/X

R200 56R/X

R202 56R/X

RP17B 56R/X

7 2

RP18B 56R/X

7 2

RP18C 56R/X

6 3

RP19B 56R/X

7 2

RP19D 56R/X

5 4

RP19C 56R/X

6 3

R718 56R/X

R719 56R/X

R720 56R/X

R721 56R/X

R722 56R/X

R723 56R/X

R724 56R/X

C2187

R725 56R/X

0

8

C179

22uF/X

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

54

MDA25

63

MDA26

72

MDA27

81

MDA28

54

MDA29

63

MDA30

72

MDA31

81

MDA32

81

MDA33

72

MDA34

63

MDA35

54

MDA36

81

MDA37

72

MDA38

63

MDA39

54

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

81

MDA49

72

MDA50

63

MDA51

54

MDA52

81

MDA53

72

MDA54

63

MDA55

54

MDA56

81

MDA57

72

MDA58

63

MDA59

54

MDA60

81

MDA61

72

MDA62

63

MDA63

54

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

WEA#

CASA#

RASA#

CSA#0

CSA#1

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

7

+VTT

C2195

C2196

100nF/X

100nF/X

+VTT

C2202

C2201

100nF/X

100nF/X

DQMA#[7..0] (10,12,13)

WEA# (10,12,13)

CASA# (10,12,13)

RASA# (10,12,13)

CSA#0 (10,12)

CSA#1 (10,12,13)

QSA[7..0] (10,12,13)

7

C2197

100nF/X

C2203

100nF/X

+VTT

<GroupName>

R832 56R/X

6

MDA[63..0]

MAA[13..0]

Vtt

TERMINATION

for DDR

C2198

C2199

100nF/X

100nF/X

C2204

C2205

100nF/X

100nF/X

CKEA

6

MDA[63..0] (10,12,13)

MAA[13..0] (10,12,13)

C2200

100nF/X

+MVDDQ

C2206

100nF/X

CKEA (10,12,13)

+MVDDQ

0

C2166

100nF/X

+MVDDQ

0

C2169

100nF/X

+MVDDQ

0

C2173

100nF/X

+MVDDQ

0

100nF/X

+MVDDQ

C2179

0

C2181

100nF/X

+MVDDQ

C2182

0

C2184

100nF/X

+MVDDQ

C2186

0

C2164

C2188

C2170

C2175

C2177

5

+VTT

RP46A 56R/X

8 1

RP46B 56R/X

7 2

RP46C 56R/X

6 3

RP46D 56R/X

5 4

RP47A 56R/X

8 1

RP47B 56R/X

7 2

RP47C 56R/X

6 3

RP47D 56R/X

5 4

RP48D 56R/X

RP48C 56R/X

RP48B 56R/X

RP48A 56R/X

RP49D 56R/X

RP49C 56R/X

RP49B 56R/X

RP49A 56R/X

RP50D 56R/X

RP50C 56R/X

RP50B 56R/X

RP50A 56R/X

RP51D 56R/X

RP51C 56R/X

RP51B 56R/X

RP51A 56R/X

RP52A 56R/X

RP52B 56R/X

RP52C 56R/X

RP52D 56R/X

RP53A 56R/X

RP53B 56R/X

RP53C 56R/X

RP53D 56R/X

RP54A 56R/X

RP54B 56R/X

RP54C 56R/X

RP54D 56R/X

RP55A 56R/X

RP55B 56R/X

RP55C 56R/X

RP55D 56R/X

RP56A 56R/X

RP56B 56R/X

RP56C 56R/X

RP56D 56R/X

RP57A 56R/X

RP57B 56R/X

RP57C 56R/X

RP57D 56R/X

RP58A 56R/X

RP58B 56R/X

RP58C 56R/X

RP58D 56R/X

RP59A 56R/X

RP59B 56R/X

RP59C 56R/X

RP59D 56R/X

RP60A 56R/X

RP60B 56R/X

RP60C 56R/X

RP60D 56R/X

RP61A 56R/X

RP61B 56R/X

RP61C 56R/X

RP61D 56R/X

RP65A 56R/X

RP66B 56R/X

RP66A 56R/X

RP66D 56R/X

RP66C 56R/X

RP64A 56R/X

RP65B 56R/X

RP62D 56R/X

RP62A 56R/X

RP65C 56R/X

RP65D 56R/X

RP63A 56R/X

RP64C 56R/X

RP64D 56R/X

R191 56R/X

R193 56R/X

R195 56R/X

R197 56R/X

R199 56R/X

R201 56R/X

R203 56R/X

R204 56R/X

RP64B 56R/X

RP62B 56R/X

RP62C 56R/X

RP63B 56R/X

RP63D 56R/X

RP63C 56R/X

R726 56R/X

R727 56R/X

R728 56R/X

R729 56R/X

R730 56R/X

R731 56R/X

R732 56R/X

R733 56R/X

5

5 4

6 3

7 2

8 1

5 4

6 3

7 2

8 1

8 1

7 2

6 3

5 4

8 1

7 2

6 3

5 4

8 1

7 2

6 3

5 4

8 1

7 2

6 3

5 4

8 1

7 2

8 1

5 4

6 3

8 1

7 2

5 4

8 1

6 3

5 4

8 1

6 3

5 4

7 2

7 2

6 3

7 2

5 4

6 3

C178

22uF/X

54

63

72

81

54

63

72

81

81

72

63

54

81

72

63

54

81

72

63

54

81

72

63

54

81

72

63

54

81

72

63

54

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

WEB#

CASB#

RASB#

CSB#0

CSB#1

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

4

+VTT

DQMB#[7..0] (10,12,13)

WEB# (10,12,13)

CASB# (10,12,13)

RASB# (10,12,13)

CSB#0 (10,12)

CSB#1 (10,12,13)

QSB[7..0] (10,12,13)

4

<GroupName>

R830 56R/X

CKEB

3

3

MDB[63..0]

MAB[13..0]

CLKA1(10,12,13)

CLKA#1(10,12,13)

CKEB (10,12,13)

2

MDB[63..0] (10,12,13)

MAB[13..0] (10,12,13)

Differential CLOCK termination

CLKA1 CLKA0

R826

56R

C711 10nF

R169

56R

CLKA#1

Differential CLOCK termination

CLKB1

CLKB1(10,12,13)

Title

Size Document Number Rev

B

Date: Sheet

CLKB#1

R828

56R

C713 10nF

R172

56R

2

CLKA#0

CLKB0

CLKB#0

GIGABYTE

VTT_TERM_A_B

RX70128IU-IU 0.1

1

CLKA0 (10,12,13)

R827

56R

C712 10nF

R170

56R

CLKA#0 (10,12,13)

CLKB0 (10,12,13)

R829

56R

C714 10nF

R171

56R

CLKB#0 (10,12,13)CLKB#1(10,12,13)

11 22Tuesday, December 21, 2004

1

of

Page 12

5

0R/X

R1839

0R/X

R1840

C218

100nF

C238

100nF

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

+MVDDC