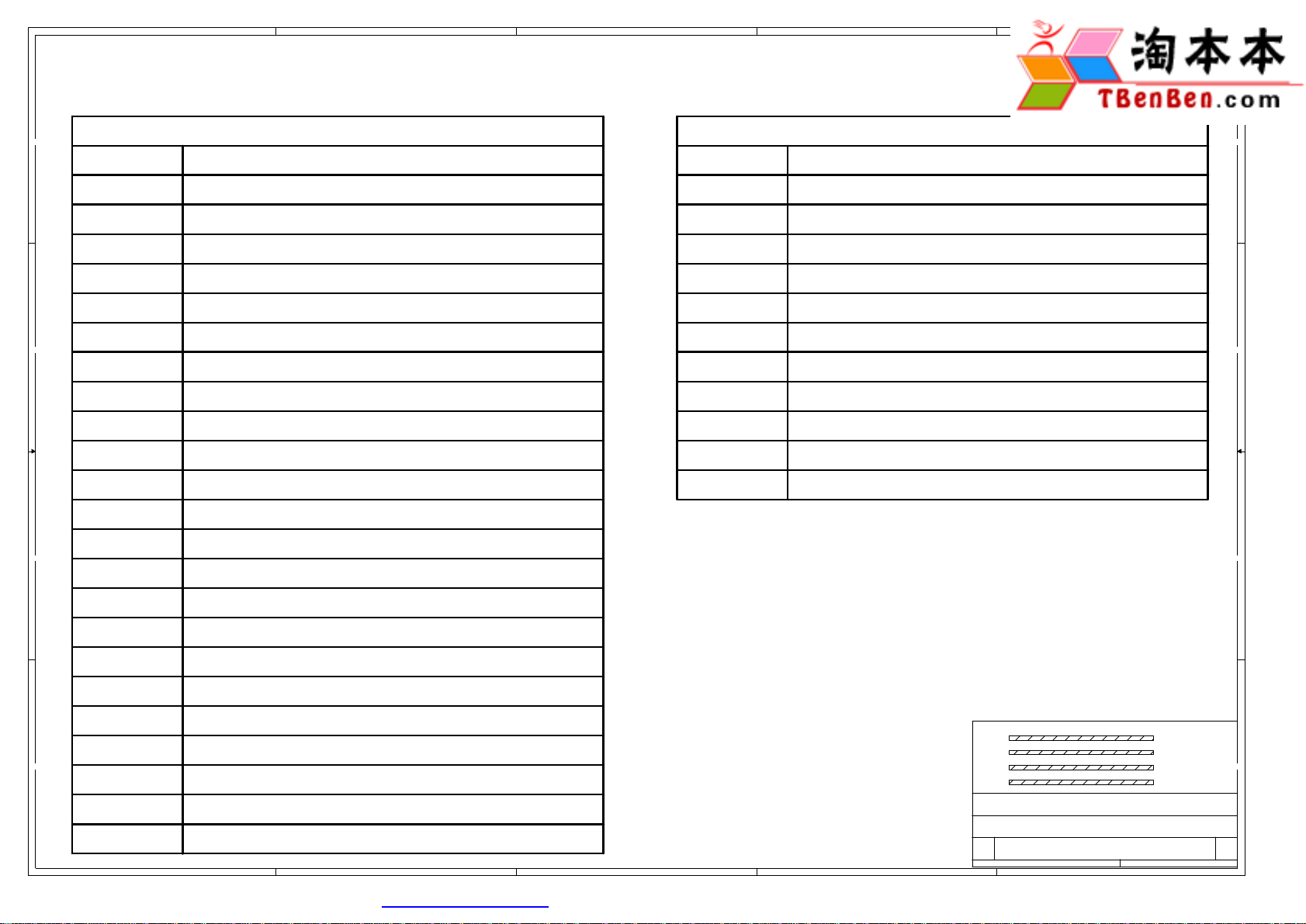

Gigabyte m2vler-le-12c_opj rev.Restored Schematics

5

4

3

2

1

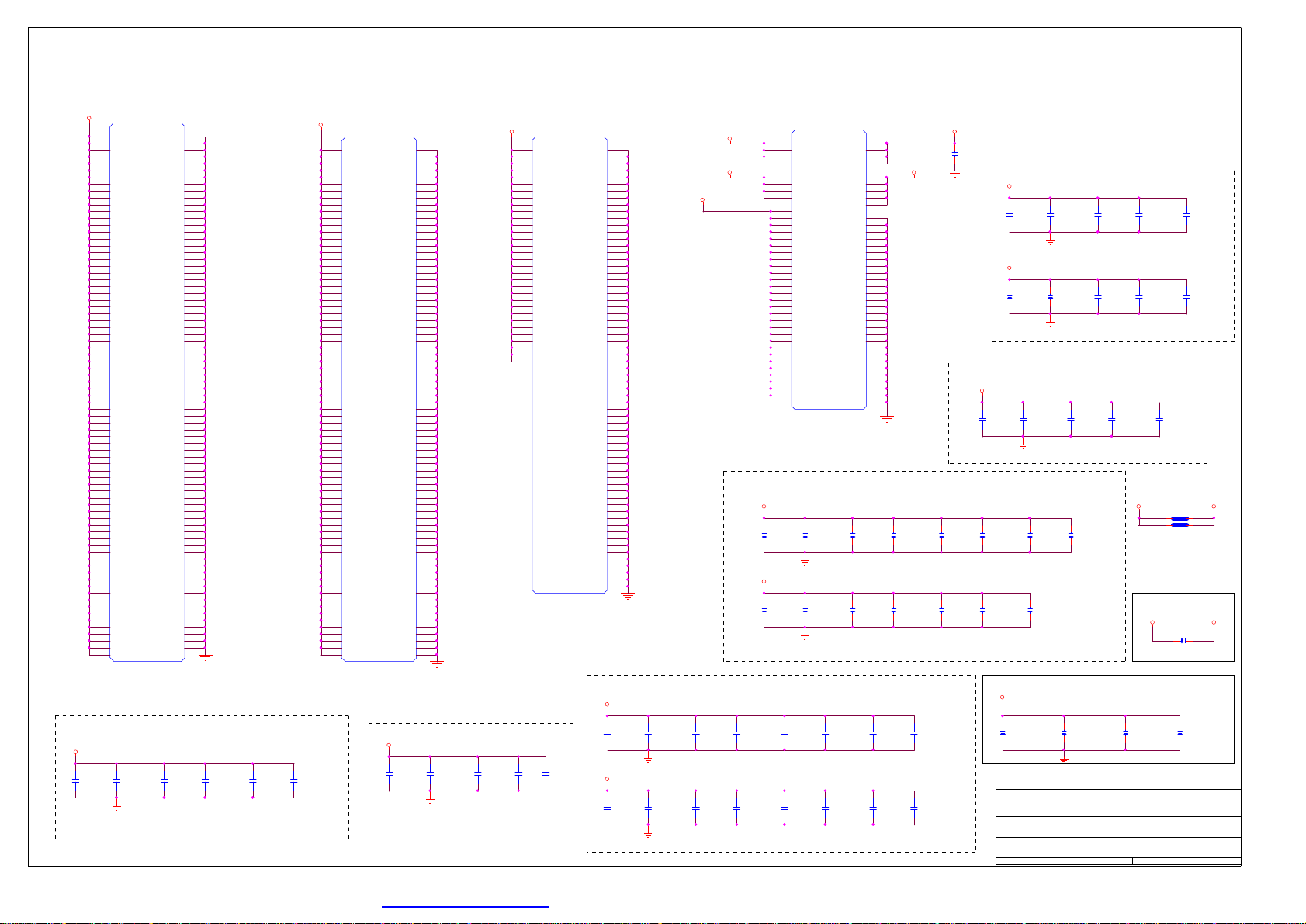

M2VLE-RH-LE Schematics

REV:1.2

(L-VK8M890G)

DD

CC

SHEET

1

2

3

4,5,6,7

8,9,10

11,12,13,14

15,16,17

18

19

20

21

22

23

COVER SHEET

BOM & PCB MODIFY HISTORY

BLOCK DIAGRAM

AMD K8-M2

DDR DIMMS 1,2,3,4 & DDR Termination

VIA_K8M890 (NORTH BRIDGE)

VIA_VT8237A (SOUTH BIRDGE)

VGA CONNECTOR

CLOCK GENERATOR

PCI SLOT 1,2

PCI EXPRESS 16PORT SLOT

PCI EXPRESS 1PORT SLOT 1

LPC I/O_SCH5137

TITLE

SHEETTITLE

35

FAN CONTROL

BB

24

25

26

27

28

29

30

31

AA

32

33

34VCORE PWM

BIOS & POWER SEQUENCE

IDE,FRONT USB

AUDIO CODEC

AUDIO JACK

FDD,COM,PRT,KB/MS

FRONT PANEL & FAN

ATX, DC POWER

LINEAR POWER 1

DDR POWER & MISC POWER

BCM LAN

5

COMPONENT SIDE

(0.5 oz. Copper)

GND SIDE

(1 oz. Copper)

VCC SIDE

(1 oz. Copper)

SOLDER SIDE

(0.5 oz. Copper)

GIGABYTE THCHNOLOGIES , INC.

Title

SizeDocument NumberRev

Custom

4

3

2

Date:Sheet of

COVER SHEET

M2VLE-RH-LE

1

136Tuesday, April 03, 2007

1.2

PDF "pdfFactory Pro" www.pdffactory.com

5

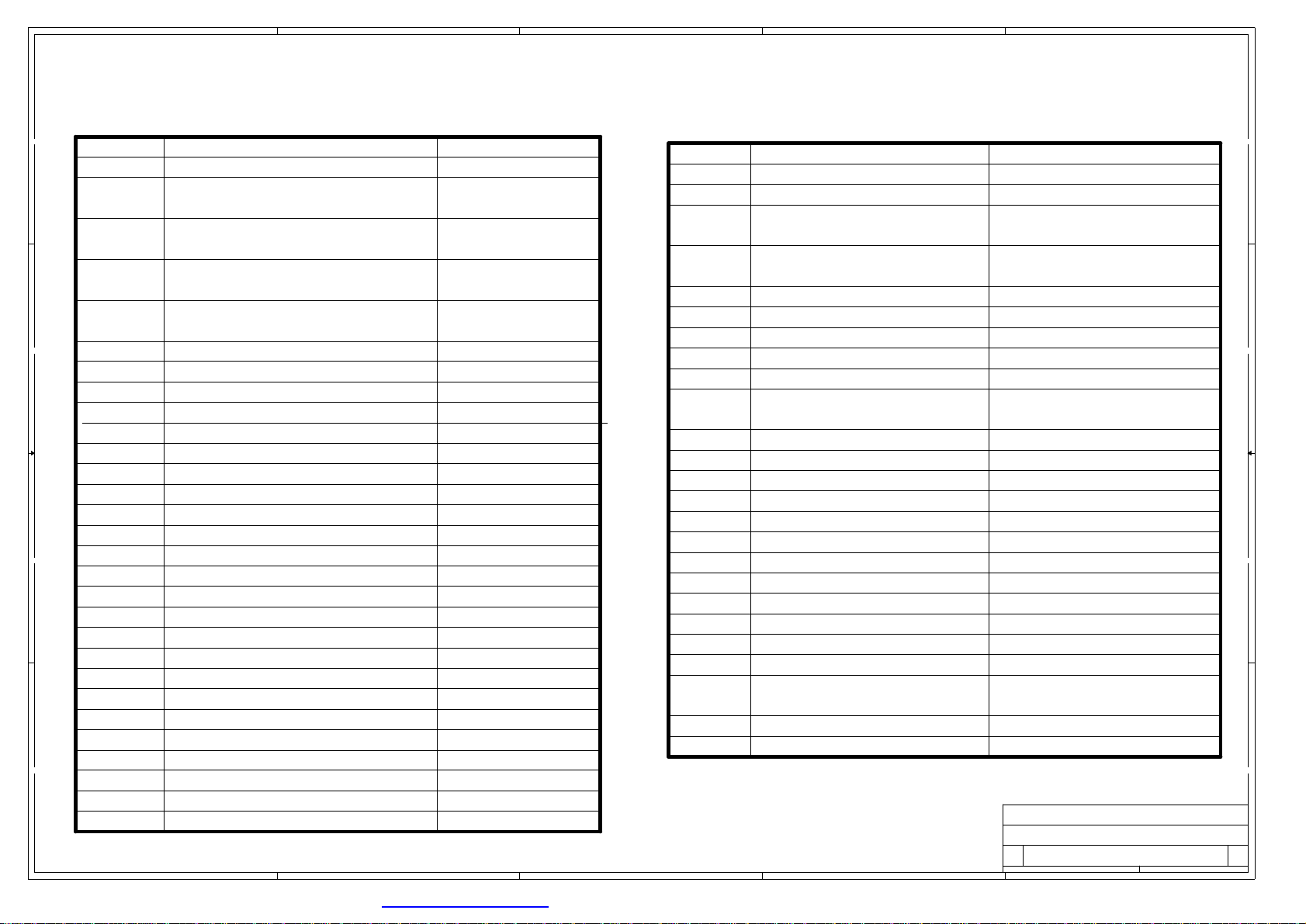

M2VLE-RH-LE REV1.2

4

3

2

1

Component value change history

DD

CC

DateChange ItemReason

add LR20

03/29change R139 from 6.04K/4/1 to 5.6K/4/1

4/7

4/7

4/7

change AEC1 from 100u/D/6.3V/58 to

10u/D/25V/55

change AEC9 & AEC10 from

2.2u/8/Y5V/10V/K to 220u/D/6.3V/57

and add AR46 AR47

change AEC6 & AEC7 from

100u/D/6.3V/57 to 220u/D/6.3V/57

and add AR44 AR45

4/7add AR48 AR49 & AD2

4/10

change R448 R449 R450 R451 R452 from

0/4 to 1k/4

fix lan link down issue03/28

Fix USB EYE measurement

fail issue

ADI update reference

design

ADI update reference

design

ADI update reference

design

ADI update reference

design

to imporve the leakage

current of VID

4/10change DR6 from 8.2K/6 to 0/6Lenovo suggestion

change DR21 & DR23 from short to 0/6Lenovo suggestion4/10

4/10Lenovo suggestion

add DR41 DR42 & DR43 at low side gate

change R1 & R2 from 49.9/4 to 51/4Lenovo suggestion4/10

4/10remove HDTIt's only for EVT

change R127 & R128 from 8.2K/4 to

4.7K/4

Lenovo suggestion4/10

change R118 from 22/4 to 22/4/X4/10Lenovo suggestion

change RN10 from 8.2K/8P4R/6 to

4.7K/8P4R/6

BB

4/13

add Q103 & Q104

Lenovo suggestion4/10

Patch reset function

Change FB2 FB3 FB4 to 10LF1-01750A-01R4/21fix RGB waveform

to fix PCIEX clk

waveform

fix under shut for

GUICLK

fix under shut for

PCICLK

4/21

4/21

Change R224~R230 from 49.9 to 514/21

Add 10pf at SC61

Add 10pf at C1382 C1383

change DBC4 from Y5V to X5RLenovo suggestion4/24

4/24Add 1nf at AC17for EMI solution

Change RN6 from 8.2K to 4.7K & R133

from 75K to 100K

Lenovo suggestion4/24

4/24change R127 from 75K/4 to 75K/4/XLenovo suggestion

4/24change R160 & R162 from 1K/4 to 4.7K/4Lenovo suggestion

AA

4/24change R341 from 4.7K/4 to 200/4Lenovo suggestion

Circuit or PCB layout change for next version

DateChange ItemReason

03/23swap USBDT0+/- & USBDT1+/-Fix rear USB no function issue

03/28

4/7

4/7

link USB_LAN pin L1 & L10

change AEC9 & AEC10 from

2.2u/8/Y5V/10V/K to

220u/D/6.3V/57 and add AR46 AR47

change AEC6 & AEC7 from

100u/D/6.3V/57 to 220u/D/6.3V/57

and add AR44 AR45

add AR48 AR49 & AD24/7

change DR21 & DR23 from short to

0/6

4/10Lenovo suggestion

4/13

4/25

4/25to make sure the pll power clear

add DR41 DR42 & DR43 at low side

gate

add Q103 & Q104

add FB9 SFB1 SC87 & C1387

change VCC3 to VCC3_HT1, VCC3_HT2,

VCC3_PE, VCC3_PE1, VCC3_RGBPLL1,

VCC

4/25add FB26to make sure the PLLVCC clear

4/25

4/25Lenovo suggestion

change DR5 DR18 DR31 from after

DR7 DR20 DR33 to before them.

remove R343~346 U45 U46 BC95~96

and Q43

remove C139~1454/25no need those cap

4/26add C1426 & C1427for EMI solution

4/26modify clear cmosLenovo suggestion

4/26

4/26

change U5 pin 8 from 5VDUAL to NCmeet spec

add SFB2 SFB3 SC88 SC89 SC90 SC91

& SC92

4/26add FB19 & C1417

add FB214/26

add FB24 & FB254/26

4/26

4/26

4/26

add FB27 & change source from

5VDUAL to VCC

change input pull high source

from 3VDUAL to VCC3

high to VCC

4/26remove RN59Lenovo suggestion

fix lan link down issue

ADI update reference

design

ADI update reference

design

ADI update reference

design

Lenovo suggestion4/10

Patch reset function

to make sure the VCC3_HT

& VCC3_HT13 clear

to make sure the gate un-floating

to make sure the VCC3_PE

& VCC3_PE1 clear

to make sure the VCC3_RGBPLL

clear

to make sure the

PLLVDDA clear

to make sure the VDDA0

& VDDA33 clear

to make sure the VCC

clear

VCC12 VDD & VCC25 is not a

stanby power, no need a stanby

power source

to stronger the drivingadd R526 R527 R528 R529 pull

4/25remove R343~346 U45 U46 BC95~96 and Q43Lenovo suggestion

4/25add FB9 SFB1 SC87 & C1387

remove C139~1454/25no need those cap

5

to make sure the VCC3_HT

& VCC3_HT13 clear

4

GIGABYTE THCHNOLOGIES , INC.

Title

SizeDocument NumberRev

Custom

3

2

Date:Sheet of

BOM & PCB MODIFY HISTORY

M2VLE-RH-LE

1

236Tuesday, April 03, 2007

1.2

PDF "pdfFactory Pro" www.pdffactory.com

5

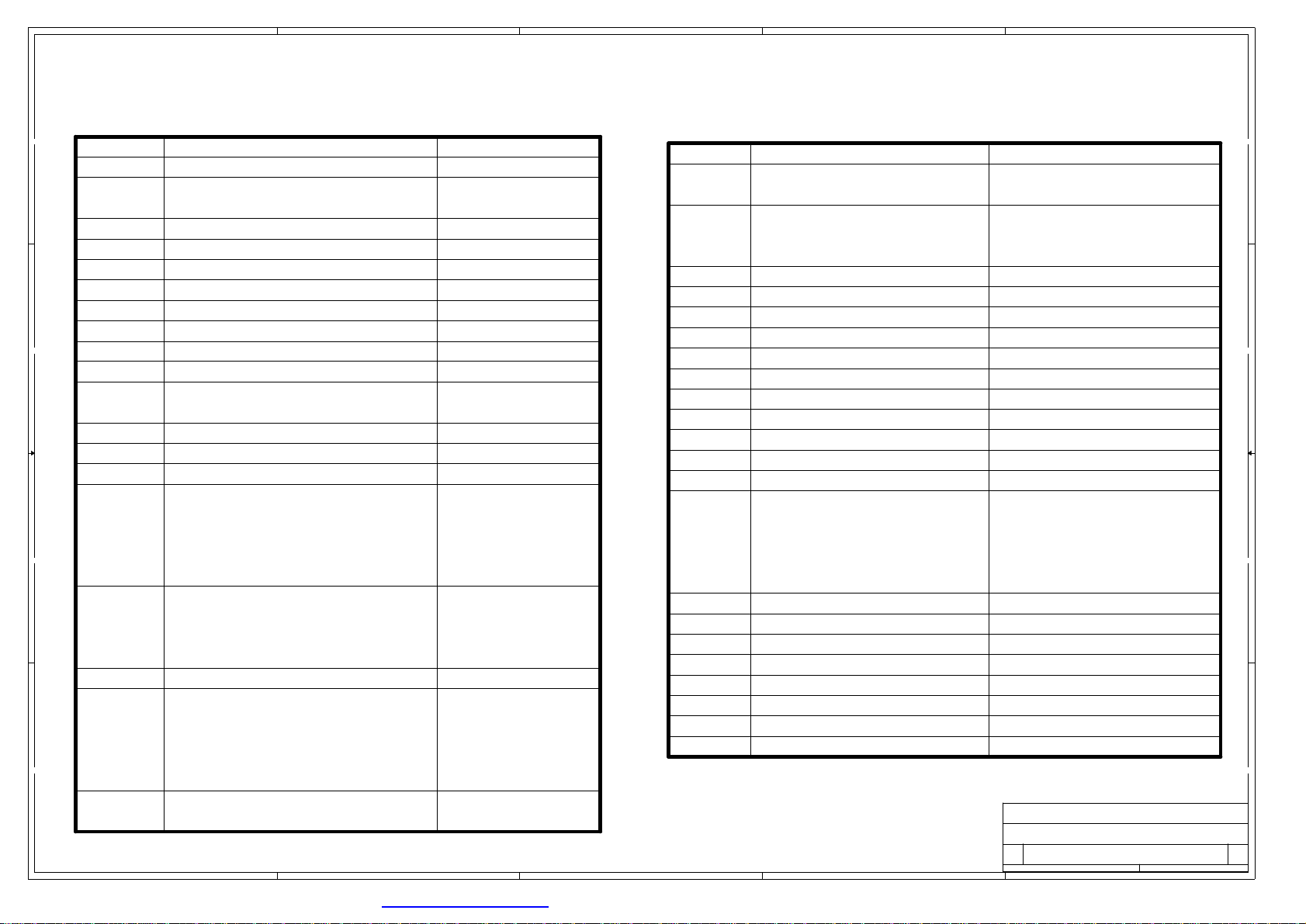

M2VLE-RH-LE REV1.2

4

3

2

1

Component value change history

DD

DateChange ItemReason

4/26change Q55 Q61 from MMBT2222 to 2N7002Lenovo suggestion

4/26change DR27 from 10K to 18K and R37~39

from 15K to 22K

to pass Sustained

Load(AMD)

for EMI solutionadd C1426 & C14274/26

add C14284/26

4/26

add SFB2 SFB3 SC88 SC89 SC90 SC91

& SC92

add FB19 & C14174/26

add FB214/26

4/26

CC

4/26

4/26

add FB24 & FB25

add FB264/26

add FB27

change R3350 R352 R354 R362 R368 R378

R381 R393 & R396 from 100 to 10 and add

R526 R527 R528 R529 pull high to VCC

to pass STPCLK

transtion responce

to make sure the VCC3_PE

& VCC3_PE1 clear

to make sure the

VCC3_RGBPLL clear

to make sure the

PLLVDDA clear

to make sure the VDDA0

& VDDA33 clear

to make sure the

PLLVCC clear

to make sure the VCC

clear

to stronger the driving

4/26change R497 R390 R392 from 8.2K to 470Lenovo suggestion

4/26Lenovo suggestion

4/26remove RN59Lenovo suggestion

5/11

BB

5/29Change R370 from 6.04K to 2.7K

change R376 R391 from 1K to 100 and

R380 R394 from 3.3K to 330

Change AEC6, 7, 9, 10 from 220uF to 100uF

Change AC5, 6, 9, 10 from 2.2uF to 4.7uF

Change AR44, 45, 46, 47 from 16 ohm to 0 ohm

Change AR26, 27 from 1K ohm to 4.7K ohm

Change AR39, 40 from 4.7K ohm to 6.2K ohm

Change AR37, 38 from 4.7K ohm to 33K ohm

Add 470 ohm at AR50, 51

Add 2N3906 at AQ3

Add 22K ohm at AR52

Remove R506

Add 0 ohm at R270

Add 180pF at C289

Add 33pF at C288

ADI reference design

change

to fine turn the

waveform

Circuit or PCB layout change for next version

DateChange ItemReason

5/11

5/29

5/29

Add 470 ohm at AR50, 51

Add 2N3906 at AQ3

Add 22K ohm at AR52

change VDD ref voltage from VCC3

to VCC

change R349 pull high voltage

from 5VDUAL to 5VSB.

8/30change U42,U53 pin 5 to 5VDLSBTo fix S3 fail issue

9/16

9/19

9/19

9/19

change U34 power from 3VDUAL to

25VDUAL

Remove R448 R449 R450 R451 R452

R453 R455 R457 R458

Change C150 foot print to C0402-2

modify audio jack design

9/21add C1431 C1432 R535 at 5VDLSB_ENto make sure signal quality

9/21add R538 RN67to adjust VID level

9/21add a 1N4148 at D23To fix boot fail issue

9/26

add a 0.1u mlcc at c1435

remove R542

add 8.2K at R536 & 0.22u at C143610/02fix AM2 power sequence

11/30Add 1N4148 at D24 & D25

Add 330 at R541 to R544

Add 2N7002 at Q107

Add MMBT2222 at Q108

Add 1K at R546

Add 8.2K at R545

Add 0.1u at BC159

ADI reference design

change

Fix VDD ref level is same as

the source that will cause the

VDD level change when VCC have

a heavy loading.

To fix the leakage current of

5VDUAL as S5.

To fix boot fail issue

change level shift design

fix foot print error

to add audio posection test

margin

To fix com2 emi issue

To fix USB device detect fail

issue

5/29

6/06

AA

6/07

Remove R305

Add R515

add MMBT2222 at Q75

add 2SA1213 at Q74

add 4.7K at R426, R421

add 2.7K at R429

add 330 at R430

add 1uF at BC123

add 10uF at BC124

remove R422

change C163,C164,C165 from 10p to 30p

change C166,C167,C168 from 10p to 39p

change C153,C154 from 22p to 30p

5

to fix the function of

WP and clear CMOS

Enable 3 pin smart fan

fine tune RGB & Sink

waveform

4

GIGABYTE THCHNOLOGIES , INC.

Title

SizeDocument NumberRev

Custom

3

2

Date:Sheet of

BOM & PCB MODIFY HISTORY

M2VLE-RH-LE

1

336Tuesday, April 03, 2007

1.2

PDF "pdfFactory Pro" www.pdffactory.com

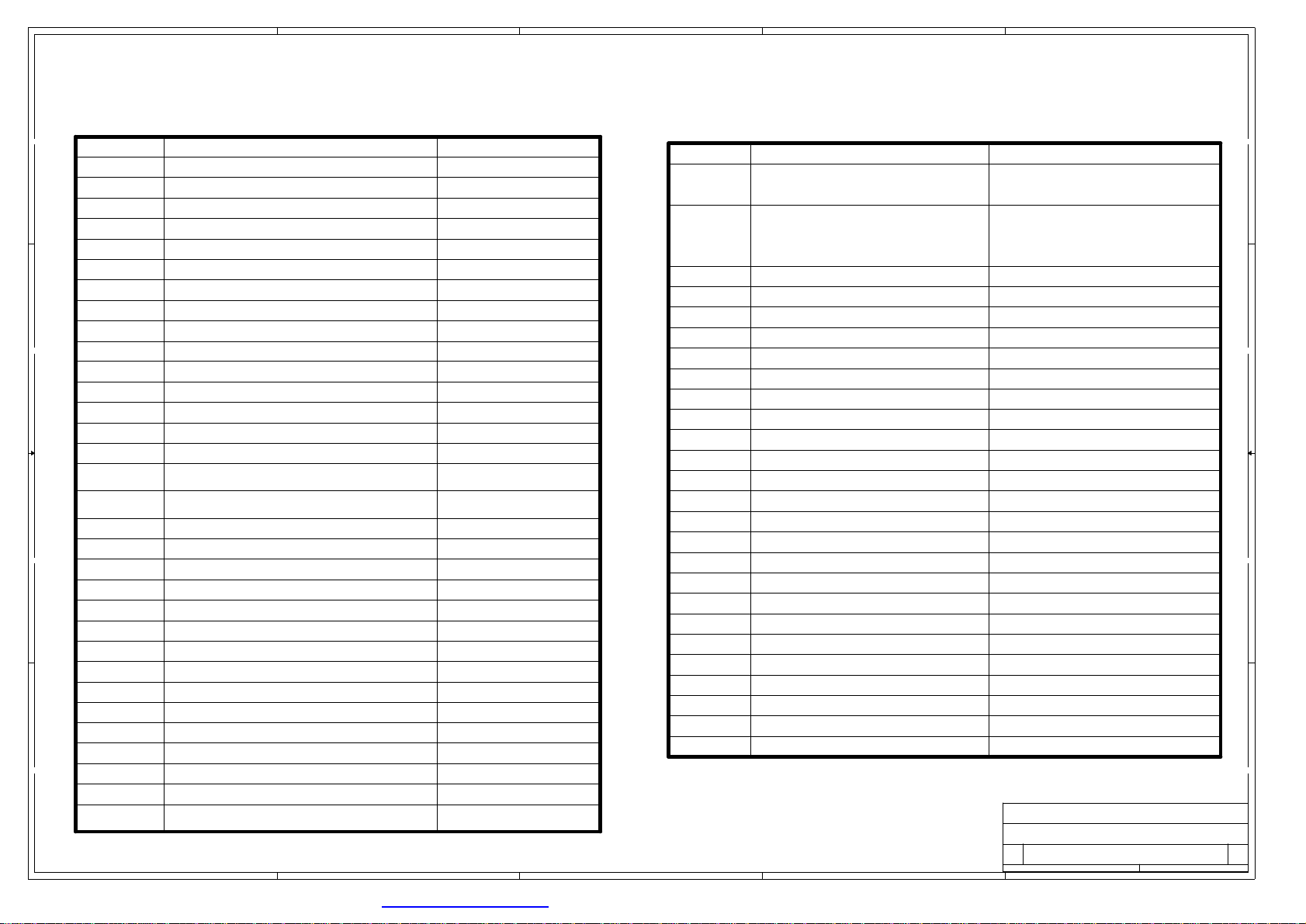

5

M2VLE-RH-LE REV1.2

4

3

2

1

Component value change history

DD

DateChange ItemReason

Circuit or PCB layout change for next version

DateChange ItemReason

06/09Add RT9701 at U42 & U53fix USB drop voltage

06/09

06/09Add 33pF at C290 & C291

06/09Add 33pF at BC81

06/09Add 10uF at C275

06/20change R415, R429 from 2.7K to 6.8K

change R443 from 22 ohm to 0 ohm

change R506 from 8.2K ohm to 330 ohm

Fine tune IDERST

fine tune the pcirst

waveform

fine tune the FWH33

waveform

fix 4 corner test fail

issue

fix minimum voltage of

Fan control

09/16change R415, R429 from 51 to 49.9to meet AM2 SPWC

09/16Add R41 8.2Kfor LM393 output level

09/19

CC

09/19

09/19

09/19Change R328 R500 to 0 ohm

Add U33 74LVC07

Add R124 100k

Change R127 R128 from 4.7K to 8.2K

add R463 1K

Remove R467

fix VID level to 1.8V

to simplify the kind of

parts

Enable ROMSIP function

adjust LED light

09/21add R9to meet AMD design guide

09/26change C1427 to 0.1u C1434 to 4.7nfix com2 emi issue

Change R367 to 5.9K ohm10/02

11/01

add 1uf MLCC at C162

add 0.1uf MLCC at C267

1/26change R211, R212 from 22/4 to 33/4fine tune sda scl

BB

to fix via K8M890 1.5V low

margin too small issue

fine tune RGB waveform

waveform

AA

GIGABYTE THCHNOLOGIES , INC.

Title

SizeDocument NumberRev

Custom

5

4

3

2

Date:Sheet of

BOM & PCB MODIFY HISTORY

M2VLE-RH-LE

1

436Tuesday, April 03, 2007

1.2

PDF "pdfFactory Pro" www.pdffactory.com

5

4

3

2

1

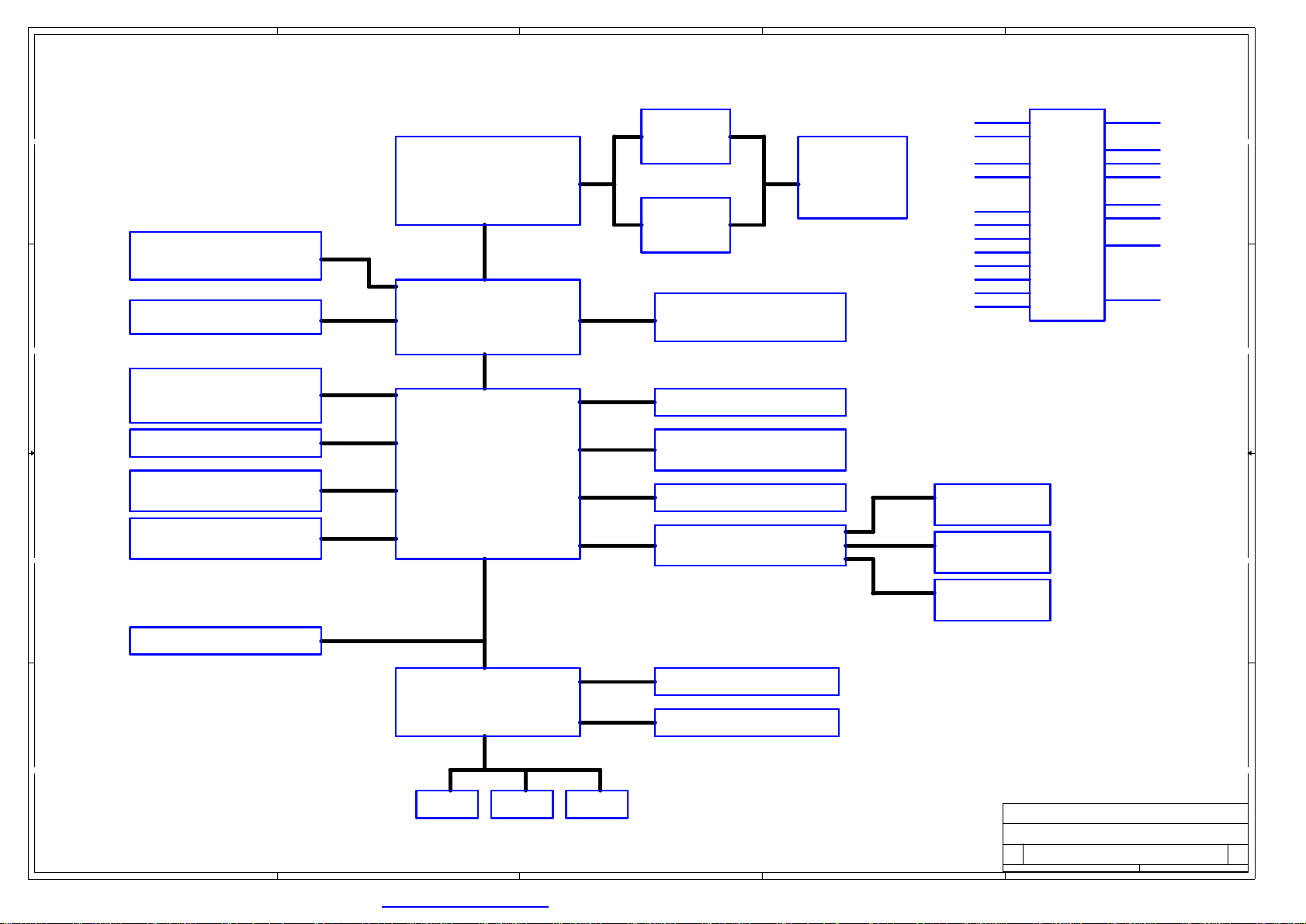

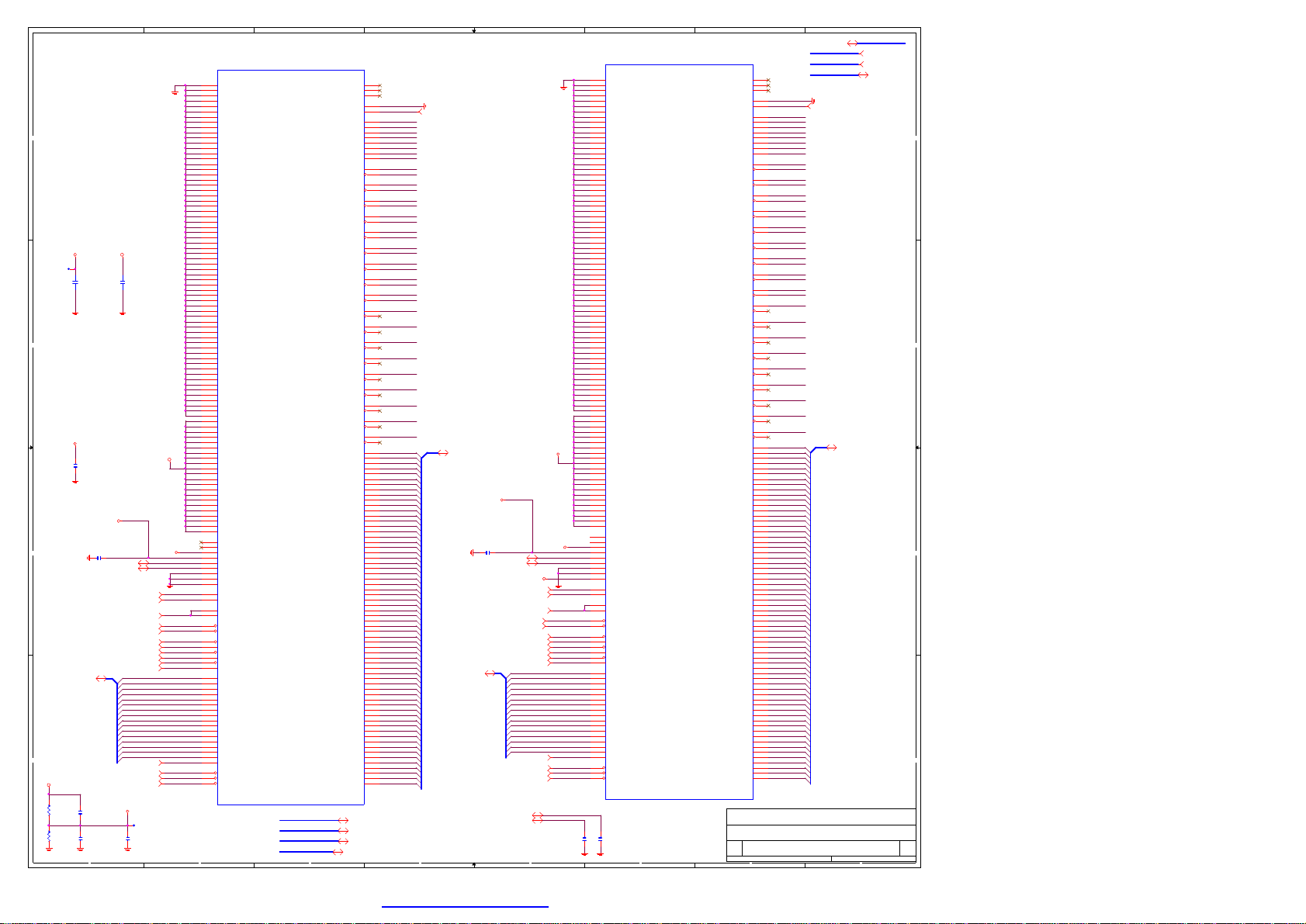

M2VLE-RH-LE BLOCK DIAGRAM

System Block Diagram

DD

PCI-E X16 SLOT

VDDQ=3.3V

P.21

PCI-E X1 SLOT 1

P.22

CC

LAN

BCM4401

VDD25=2.5VAVDD33=3.3V

P.35

PCI SLOT 1~2

P.20

AMD AM2 CPU

VCC12=1.2V

VCC25=2.5V

25VSTR=2.5VCPUVREF=1.25V

HT12B=1.2V

P.5,6,7,8

25VDDA=2.5V

VTTDDR=1.25V

LDT

LINK

VIA K8M890 CE

VCC12=1.2VVDD=1.5V

P.9,10,11,12

V-LINK

VIA VT8237A

DDR SDRAM

Channel 1

25VSTR=1.8V

DDRVREF=0.9V

Channel2

25VSTR=1.8V

DDRVREF=0.9V

DeltaChrome

Integrated Grapics

P.16

IDE 1,2 (ATA133)

P.25

KEYBOARD/MOUSE

P.28

5VDUAL=5VFUSEVCC=5V

Rtt

SSTL-2

Termination

25VSTR=1.8V

DDRVREF=0.9V

CPUCLKT

CPUCLKC

NBGCLK

GUICLK

VCLK

SBPCLK

SB14CLK

APICCLK

USBCLK

-PCICLK

SMBCLK

SMBDAT

CLOCK

GEN

ICS953201

AGPGCLK

PCICLK0

PCICLK1

PCICLK2

SIOPCLK

SIO48CLK

LANCLK

AUDIO14

REAR USB2.0 X4

FUSEPWR=5V

P.34,35

FRONT USB2.0 X4

FUSEPWR1=5V

BB

P.25

VCC25=2.5V

3VDUAL=3.3V

25VDUAL=2.5V

P.13,14,15

VLVREF=0.625V

RTCVDD=3.3V

VSUS= 2.5V

SATA 2PORT

P.14

AZALIA

ADI1986

AVDD=5V

P.26

Analog Out

AVDD=5V

P.27

Analog In

AVDD=5V

P.27

MIC

AVDD=5V

P.27

BIOS

P.24

LPC

LPC

Bus

LPC

SCH5137

VCC3=3.3V3VDUAL=3.3V

P.23

AA

VSUS15約45mA

VCC25約380mA

VDD約2.2230mAA

VCC12約370mA

VSUS25V約5.05mA

5

COM PORT

P.28P.28P.24

4

LPTFLOPPY

VOLTAGE MONITOR

P.23

TEMPERATURE MONITOR

P.23

3

GIGABYTE THCHNOLOGIES , INC.

Title

SizeDocument NumberRev

Custom

2

Date:Sheet of

BLOCK DIAGRAM

M2VLE-RH-LE

1

536Tuesday, April 03, 2007

1.2

PDF "pdfFactory Pro" www.pdffactory.com

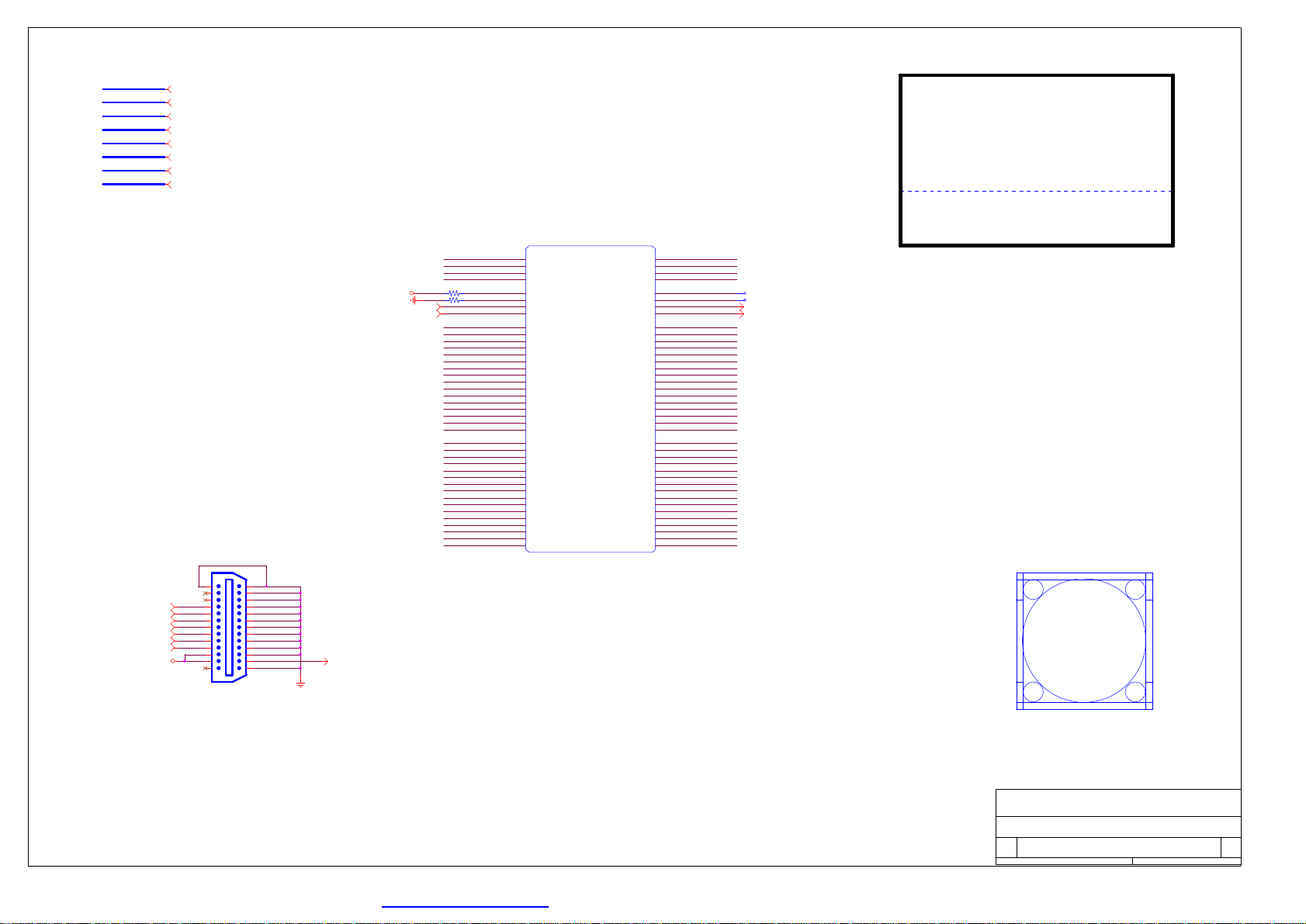

L0_CADIN_L[0..15]

L0_CADIN_H[0..15]

L0_CLKIN_L[0..1]

L0_CLKIN_H[0..1]

L0_CADOUT_L[0..15]

L0_CADOUT_H[0..15]

L0_CLKOUT_L[0..1]

L0_CLKOUT_H[0..1]

L0_CADIN_L[0..15]<12>

L0_CADIN_H[0..15]<12>

L0_CLKIN_L[0..1]<12>

L0_CLKIN_H[0..1]<12>

L0_CADOUT_L[0..15]<12>

L0_CADOUT_H[0..15]<12>

L0_CLKOUT_L[0..1]<12>

L0_CLKOUT_H[0..1]<12>

DBREQ_L<8>

DBRDY_M2<8>

TCK_M2<8>

TMS_M2<8>

TDI_M2<8>

TRST_L<8>

TDO_M2<8>

DDR18V

PH/2*13K25/BK/1.27/VA/S[10NH5-040213-00R]/X

only for EVT

,DVT remove .

HDT

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19

21 22

23 24

25 26

CPU_VDD_RUN = VCORE

CPU_VDDA_RUN = VDDA25

VLDT_RUN = VCC12_HT

CPU_VDDIO_SUS = DDR18V

CPU_VTT_SUS = DDRVTT

VLDT_A = VCC12_HT

AM2CPUA

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

VCC12_HT

GND

L0_CTLIN_H0<12>

L0_CTLIN_L0<12>

20

-PCIRST1<8,14,24>

GND

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

N6

P6

N3

N2

49.9/4/1R1

V4

49.9/4/1R2

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

1

TP1

1

TP2

L0_CTLOUT_H0<12>

L0_CTLOUT_L0<12>

VLDT_B = HT12B

SOCKET_M

M2/[12KRC-04K807-01R]/X

PDF "pdfFactory Pro" ÿÿ www.pdffactory.com

GIGABYTE THCHNOLOGIES , INC.

Title

SizeDocument NumberRev

Custom

Date:Sheet of

CPU HYPER TRANSPORT

M2VLE-RH-LE

636Wednesday, April 04, 2007

1.2

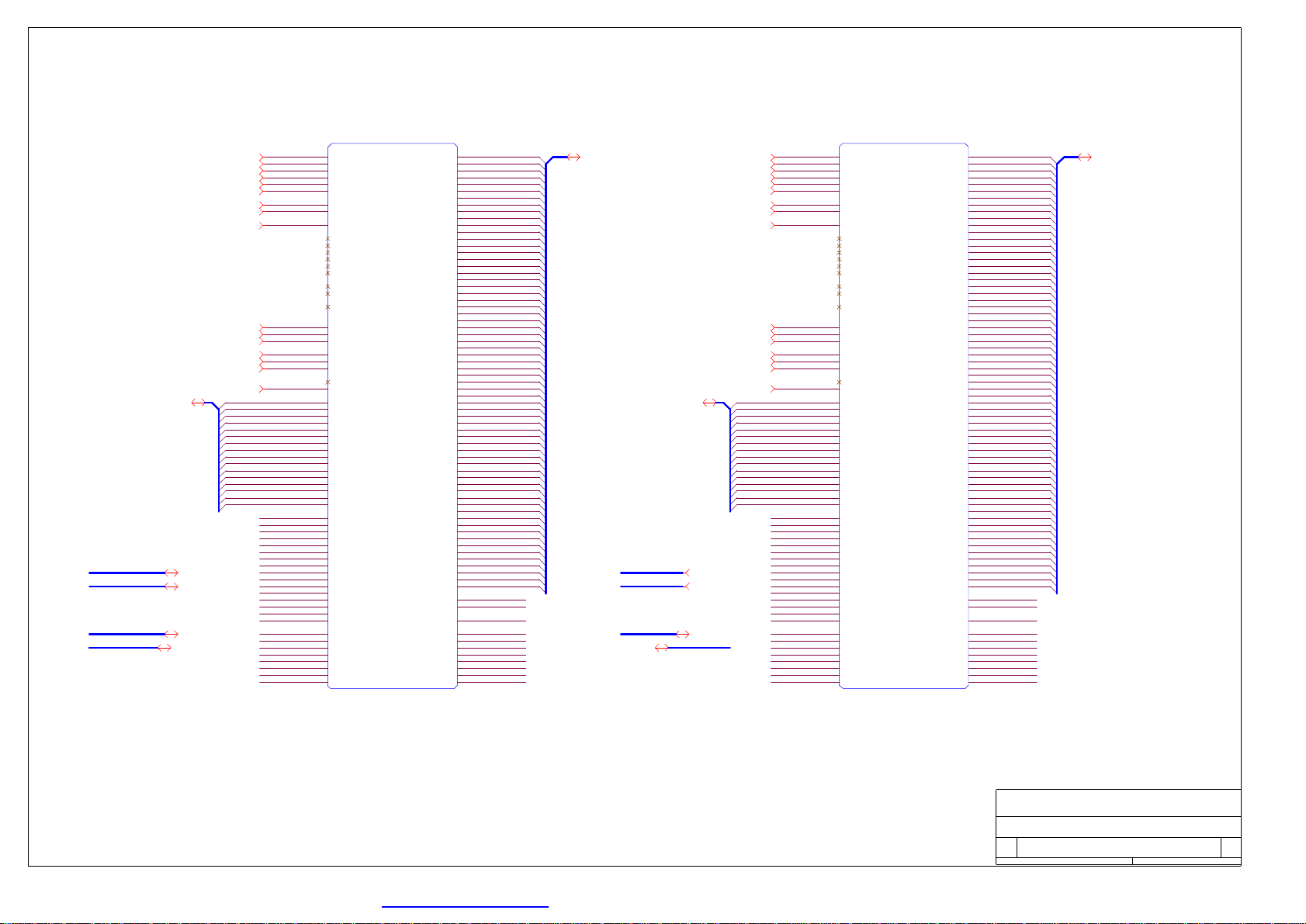

AM2CPUB

DCLKA2

-DCLKA2

DCLKA1

-DCLKA1

DCLKA0

-DCLKA0

MODT_A0

-SCASA

-SWEA

-SRASA

SBAA2

SBAA1

SBAA0

CKEA0

DQSA7

-DQSA7

DQSA6

-DQSA6

DQSA5

-DQSA5

DQSA4

-DQSA4

DQSA3

-DQSA3

DQSA2

-DQSA2

DQSA1

-DQSA1

DQSA0

-DQSA0

DMA7

DMA6

DMA5

DMA4

DMA3

DMA2

DMA1

DMA0

AG21

AG20

AC25

AA24

AC28

AE20

AE19

AD27

AA25

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

G19

H19

U27

U26

G20

G21

V27

W27

N25

Y27

L27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

D29

C29

C25

D25

E19

F19

F15

G15

B29

E24

E18

H15

DCLKA2<10,11>

-DCLKA2<10,11>

DCLKA1<10,11>

-DCLKA1<10,11>

DCLKA0<10,11>

-DCLKA0<10,11>

-CSA1<10,11> -CSB1<10,11>

-CSA0<10,11>

MODT_A0<10,11> MODT_B0<10,11>

-SCASA<10,11>

-SWEA<10,11>

-SRASA<10,11>

SBAA2<10,11>

SBAA1<10,11>

SBAA0<10,11>

MAAA15

MAAA[0..15]<10,11> MAAB[0..15]<10,11>

-DQSA[0..8]-DQSB[0..8]

DQSA[0..8]

DMA[0:8]

SACB[0..7]

-DQSA[0..8]<10>

DQSA[0..8]<10>

DMA[0..8]<10>

SACB[0..7]<10>

MAAA14

MAAA13

MAAA12

MAAA11

MAAA10

MAAA9

MAAA8

MAAA7

MAAA6

MAAA5

MAAA4

MAAA3

MAAA2

MAAA1

MAAA0

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MDA63

MDA62

MDA61

MDA60

MDA59

MDA58

MDA57

MDA56

MDA55

MDA54

MDA53

MDA52

MDA51

MDA50

MDA49

MDA48

MDA47

MDA46

MDA45

MDA44

MDA43

MDA42

MDA41

MDA40

MDA39

MDA38

MDA37

MDA36

MDA35

MDA34

MDA33

MDA32

MDA31

MDA30

MDA29

MDA28

MDA27

MDA26

MDA25

MDA24

MDA23

MDA22

MDA21

MDA20

MDA19

MDA18

MDA17

MDA16

MDA15

MDA14

MDA13

MDA12

MDA11

MDA10

MDA9

MDA8

MDA7

MDA6

MDA5

MDA4

MDA3

MDA2

MDA1

MDA0

DQSA8

-DQSA8

DMA8

SACB7

SACB6

SACB5

SACB4

SACB3

SACB2

SACB1

SACB0

MDA[0..63]<10> MDB[0..63]<10>

DQSB[0..8]

DMB[0..8]

SBCB[0..7]<10>

-DQSB[0..8]<10>

DQSB[0..8]<10>

DMB[0..8]<10>

SBCB[0..7]

AM2CPUC

DCLKB2

-DCLKB2

DCLKB1

-DCLKB1

DCLKB0

-DCLKB0

MODT_B0

-SCASB

-SWEB

-SRASB

SBAB2

SBAB1

SBAB0

CKEB0

DQSB7

-DQSB7

DQSB6

-DQSB6

DQSB5

-DQSB5

DQSB4

-DQSB4

DQSB3

-DQSB3

DQSB2

-DQSB2

DQSB1

-DQSB1

DQSB0

-DQSB0

DMB7

DMB6

DMB5

DMB4

DMB3

DMB2

DMB1

DMB0

AJ19

AK19

AE30

AC31

AD29

AL19

AL18

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

M31

M29

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

A18

A19

U31

U30

C19

D19

N31

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

DCLKB2<10,11>

-DCLKB2<10,11>

DCLKB1<10,11>

-DCLKB1<10,11>

DCLKB0<10,11>

-DCLKB0<10,11>

-CSB0<10,11>

-SCASB<10,11>

-SWEB<10,11>

-SRASB<10,11>

SBAB2<10,11>

SBAB1<10,11>

SBAB0<10,11>

CKEB0<10,11>CKEA0<10,11>

MAAB15

MAAB14

MAAB13

MAAB12

MAAB11

MAAB10

MAAB9

MAAB8

MAAB7

MAAB6

MAAB5

MAAB4

MAAB3

MAAB2

MAAB1

MAAB0

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MDB63

MDB62

MDB61

MDB60

MDB59

MDB58

MDB57

MDB56

MDB55

MDB54

MDB53

MDB52

MDB51

MDB50

MDB49

MDB48

MDB47

MDB46

MDB45

MDB44

MDB43

MDB42

MDB41

MDB40

MDB39

MDB38

MDB37

MDB36

MDB35

MDB34

MDB33

MDB32

MDB31

MDB30

MDB29

MDB28

MDB27

MDB26

MDB25

MDB24

MDB23

MDB22

MDB21

MDB20

MDB19

MDB18

MDB17

MDB16

MDB15

MDB14

MDB13

MDB12

MDB11

MDB10

MDB9

MDB8

MDB7

MDB6

MDB5

MDB4

MDB3

MDB2

MDB1

MDB0

DQSB8

-DQSB8

DMB8

SBCB7

SBCB6

SBCB5

SBCB4

SBCB3

SBCB2

SBCB1

SBCB0

PDF "pdfFactory Pro" www.pdffactory.com

GIGABYTE THCHNOLOGIES , INC.

Title

SizeDocument NumberRev

Custom

Date:Sheet of

CPU DDRII MEMORY

M2VLE-RH-LE

736Wednesday, April 04, 2007

1.2

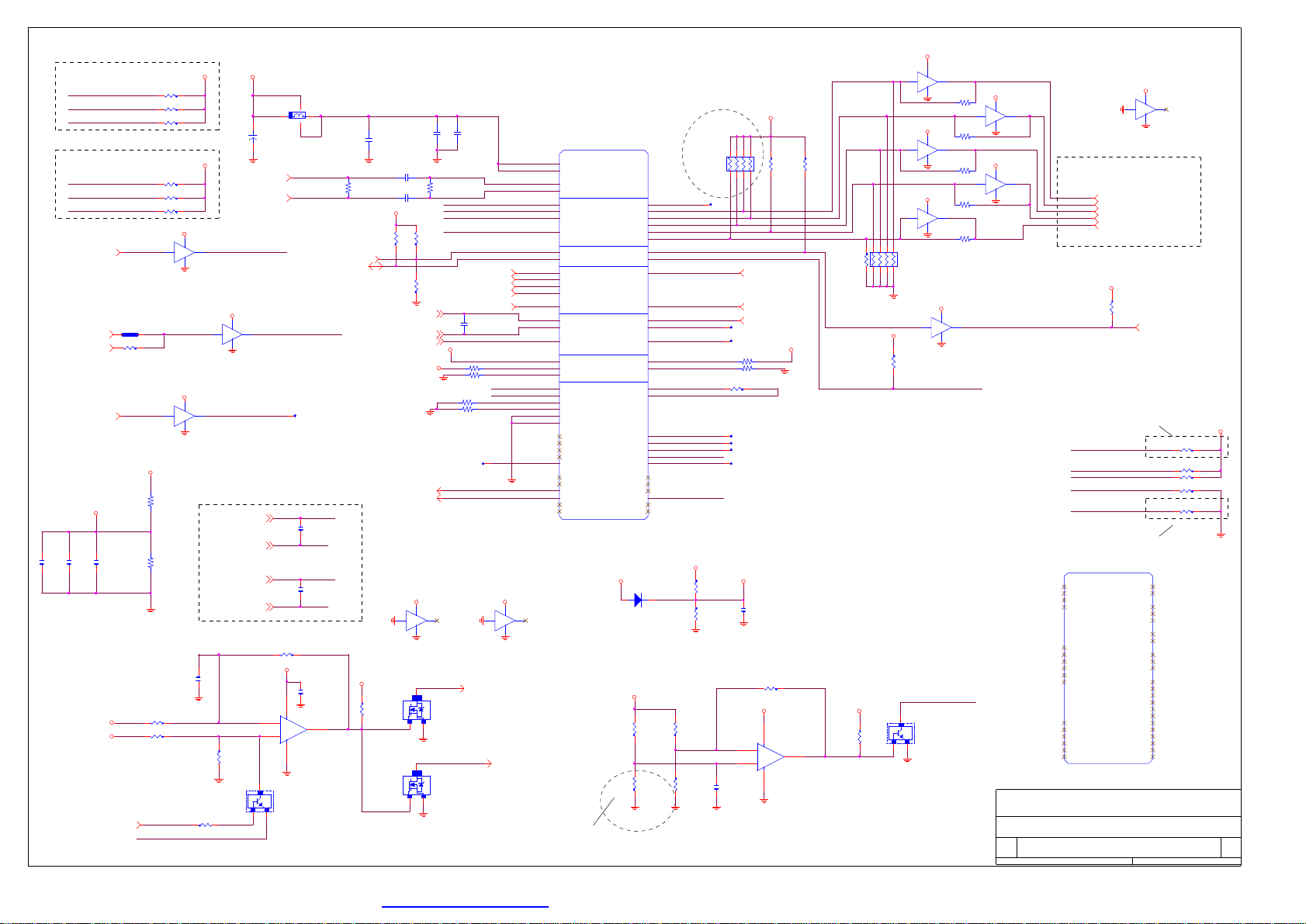

CPUVREF

40 MILS WIDTH

SC66

1N/4/X7R/50V/K

-CPURST_C

CPU_PWRGD_C

HTSTOP_L_C

-PCIRST1

CPU_PWRGD

-HTSTOP_L

CPU_PWRGD<24,30>

-HTSTOPSB<12,18>

-HTSTOPNB<12>

-PCIRST1<6,14,24>

CPU_M_VREF

SC67

0.1u/4/Y5V/16V/Z

VCC

5VSB

PWRGD<14,18,24,30>

R5300/4

R7300/4

R8300/4

R111K/4/X

R131K/4

R141K/4/X

1 2

R4540/4/SHT/X

R4560/4/X

5 6

DDR18V

SC68

0.1u/4/X7R/10V/K

1u/6/Y5V/10V/Z/X

R3710K/4/X

R408.2K/4/X

THERMTRIP_CPU_L

25VDUAL

147

U34A

-HTSTOP_L

25VDUAL

147

U34C

SN74LVC07APWR/TSSOP14

SR2

16.9/6/1

SR3

16.9/6/1

C7

R458.2K/4/X

DDR18V

VCC3

SN74LVC07APWR/TSSOP14

VDDA25V

1

EC36

100u/D/16V/5B

CPU_PWRGD_C

25VDUAL

147

U34B

3 4

SN74LVC07APWR/TSSOP14

-CPURST_C

COREFB-<35>

COREFB+<35>

COREFB-<35>

COREFB+<35>

R42

8.2K/4/X

FB130/8/4A/S

+

CPUCLK0_H<20>

CPUCLK0_L<20>

HTSTOP_L_C

R344.7K/4/X

5VSB

84

3

+

2

-

Q4

MMBT2222A/SOT23/600mA/40/X

SOT23

132

2.5V/0.11A

CPUCLK0_H

CPUCLK0_L

TP_CPURST

BC1

0.1u/4/Y5V/16V/Z

SC1

0.1u/4/Y5V/16V/Z/X

C8

0.1u/6/Y5V/25V/Z/X

U35A

1

KA393D/SO8

R477

AMD_SIC<24>

AMD_SID<24>

3.9n/4/X7R/50V/K

261/4/1

3.9n/4/X7R/50V/K

VCC

patch when Super IO power sequency fail

C1

4.7u/8/Y5V/10V/Z/X

R36

1K/4/X

C2

3.3n/4/X7R/50V/K

C4

R12

C5

169/4/1

DDR18V

R15

R16

300/4

300/4

R18

300/4/X

COREFB+<35>

10u/8/X5R/6.3V/K

COREFB-<35>

VTTDDR_SENSE<33>

CPU_M_VREF

DDR18V

CPUTHERMDC<24>

CPUTHERMDA<24>

25VDUAL 25VDUAL

147

U34E

11 10

SN74LVC07APWR/TSSOP14

3

Q1

D

2N7002/SOT23/25pF/5/X

GS

2

1

CPUVDD_EN

3

Q3

D

2N7002/SOT23/25pF/5/X

GS

2

1

C3

0.22u/6/X7R/10V/K

CLKIN_H

CLKIN_L

CPU_PWRGD_C

HTSTOP_L_C

-CPURST_C

CPU_PRESENT_L

TDI_M2<6>

TRST_L<6>

TCK_M2<6>

TMS_M2<6>

DBREQ_L<6> DBRDY_M2<6>

C1428

39.2/4/1R22

39.2/4/1R25

CPU_TEST25_H

CPU_TEST25_L

300/4R29

300/4R30

TP12

CPUTHERMDC

CPUTHERMDA

AL10

AH10

AH11

AJ10

AJ11

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AL9

A5

G2

G1

E12

F12

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

AM2CPUD

MISC

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

TDO

D2

D1

C1

E3

E2

E1

AK7

AL7

AK10

B6

AK11

AL11

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

RESERVE

RN1

300/8P4R/6/X

1 2

3 4

CPU_TEST21

CPU_TEST26

TP3

TP24

TP4

R2780.6/4/1

TP6

TP8

TP10

TP13

CPU_VID5

CPU_VID4

CPU_VID3

CPU_VID2

CPU_VID1

CPU_VID0

LAYOUT: Route trace 50 mils wide and

500 to 750 mils long between these caps.

147

U34F

13 12

SN74LVC07APWR/TSSOP14

-PWRBTSW<17,24,30>

CPUVDD_EN<24,25,35>

D23

LL4148/SOD80C/300mA

RS3 CLOSE CPU VR MOSFET

VCC

HR100K/[10RH2-001003-21]

Plase at PH3 copper

R38

12K/4/1

RS1

100K/1/6/S

3VDUAL

R39

2.4K/4/1

R43

1K/4/1

R539

330/4/X

R540

1K/4

25VDUAL3VDUAL

C9

0.1u/6/Y5V/25V/Z

DDR18V

R10

R9

300/4

300/4

5 6

7 8

THERMTRIP_L

TDO_M2<6>

VDDIO_FB_H<33>

VCC12_HT

44.2/4/1R20

44.2/4/1R23

Route as 80-Ohm differential impedance

Keep trace to resistor less than 1" from CPU pin

C1430

0.1u/6/Y5V/25V/Z/X

R356.98K/4/1

5VSB VCC

84

U35B

5

+

7

6

-

KA393D/SO8

147

1 2

147

5 6

147

11 10

R538

1.2K/6/X

1 2

DDR18V

3 4

5 6

RN67

1.2K/8P4R/6/X

7 8

9 8

R21

300/4

-PROCHOT

25VDUAL

asserted at 131 degree

deasserted at 116 degree

-PROCHOT

R41

8.2k/4

Q2

2N7002/SOT23/25pF/5

SOT23

132

DDR18V

U33A

74LVC07A/X

3 4

DDR18V

U33C

74LVC07A/X

9 8

DDR18V

U33E

74LVC07A/X

147

U34D

SN74LVC07APWR/TSSOP14

DDR18V

DDR18V

147

1k/4R448

U33B

74LVC07A/X

1k/4R449

DDR18V

147

1k/4R450

U33D

74LVC07A/X

1k/4R451

1k/4R452

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

Title

SizeDocument NumberRev

Custom

Date:Sheet of

PULL HIGH 3VDUAL ==>

3VDUAL

CPU_TEST26

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

CPU_TEST21

AM2CPUE

INTERNAL MISC

L25

RSVD1

L26

RSVD2

L31

RSVD3

L30

RSVD4

W26

RSVD5

W25

RSVD6

AE27

RSVD7

U24

RSVD8

V24

RSVD9

AE28

RSVD10

Y31

RSVD11

Y30

RSVD12

AG31

RSVD13

V31

RSVD14

W31

RSVD15

AF31

RSVD16

GIGABYTE THCHNOLOGIES , INC.

CPU CONTROL

M2VLE-RH-LE

147

U33F

13 12

74LVC07A

VID4<24,35>

VID3<24,35>

VID2<24,35>

VID1<24,35>

VID0<24,35>

R17

8.2K/4

THERMTRIP_CPU_L<17>

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

R19300/4

R241K/4

R26510/4

R28510/4

R31300/4

E20

B19

AL4

AK4

AK3

F2

F3

G4

G3

G5

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

836Wednesday, April 04, 2007

DDR18V

1.2

PDF "pdfFactory Pro" ÿÿ www.pdffactory.com

VCORE

AA10

AA12

AA14

AA16

AA18

AB11

AC10

AE10

VLDT_RUN_B is connected to the VLDT_RUN power

supply through the package or on the die. It is only connected

AM2CPUF

VDD1

A4

VDD1

A6

VDD2

AA8

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

AB7

VDD9

AB9

VDD10

VDD11

AC4

VDD12

AC5

VDD13

AC8

VDD14

VDD15

AD2

VDD16

AD3

VDD17

AD7

VDD18

AD9

VDD19

VDD20

AF7

VDD21

AF9

VDD22

AG4

VDD23

AG5

VDD24

AG7

VDD25

AH2

VDD26

AH3

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

E10

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

F11

VDD46

G6

VDD47

G8

VDD48

G10

VDD49

G12

VDD50

H7

VDD51

H11

VDD52

H23

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

K11

VDD64

K13

VDD65

K15

VDD66

K17

VDD67

K19

VDD68

K21

VDD69

K23

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

Y17

VDD150

Y19

VDD151

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

GND

VCORE

AM2CPUG

VDD2

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

M11

VDD8

M13

VDD9

M15

VDD10

M17

VDD11

M19

VDD12

N8

VDD13

N10

VDD14

N12

VDD15

N14

VDD16

N16

VDD17

N18

VDD18

P7

VDD19

P9

VDD20

P11

VDD21

P13

VDD22

P15

VDD23

P17

VDD24

P19

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

R10

VDD29

R12

VDD30

R14

VDD31

R16

VDD32

R18

VDD33

R20

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

U10

VDD46

U12

VDD47

U14

VDD48

U16

VDD49

U18

VDD50

U20

VDD51

V9

VDD52

V11

VDD53

V13

VDD54

V15

VDD55

V17

VDD56

V19

VDD57

V21

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

W10

VDD62

W12

VDD63

W14

VDD64

W16

VDD65

W18

VDD66

W20

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

Y11

VDD72

Y13

VDD73

Y15

VDD74

Y21

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

GND

VCORE

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

W22

AM2CPUH

VDD3

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

M21

VDD21

M23

VDD22

N20

VDD23

N22

VDD24

P21

VDD25

P23

VDD26

R22

VDD27

T23

VDD28

U22

VDD29

V23

VDD30

VDD31

Y23

VDD32

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

DDRVTT

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

GND

on the board to decoupling near the CPU package.

VCC12_HT

DDRVTT

DDR18V

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

AM2CPUI

VDDIO

AJ4

VLDT_A1

AJ3

VLDT_A2

AJ2

VLDT_A3

AJ1

VLDT_A4

D12

VTT1

C12

VTT2

B12

VTT3

A12

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO29

M24

VDDIO9

M26

VDDIO10

M28

VDDIO11

M30

VDDIO12

P24

VDDIO13

P26

VDDIO14

P28

VDDIO15

P30

VDDIO16

T24

VDDIO17

T26

VDDIO18

T28

VDDIO19

T30

VDDIO20

V25

VDDIO21

V26

VDDIO22

V28

VDDIO23

V30

VDDIO24

Y24

VDDIO25

Y26

VDDIO26

Y28

VDDIO27

Y29

VDDIO28

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

GND

BUTTOM SIDE

VCORE

SC17

22u/8/X5R/6.3V/M

VCORE

SC25

22u/8/X5R/6.3V/M

SC18

22u/8/X5R/6.3V/M

GND

SC26

22u/8/X5R/6.3V/M

GND

SC19

22u/8/X5R/6.3V/M

SC27

22u/8/X5R/6.3V/M

DDRVTT

SC20

22u/8/X5R/6.3V/M

SC28

22u/8/X5R/6.3V/M

HT12B

BC4

4.7u/8/X5R/6.3V/K

GND

VCORE

SC21

22u/8/X5R/6.3V/M

SC29

22u/8/X5R/6.3V/M

DDR18V

SC2

0.22u/6/X7R/10V/K

DDR18V

SC10

22u/8/X5R/6.3V/M

SC12

0.22u/6/X7R/10V/K

GND

SC22

22u/8/X5R/6.3V/M

SC30

22u/8/X5R/6.3V/M

1021 EMI

DDRVTT

SC3

0.22u/6/X7R/10V/K

GND

SC11

22u/8/X5R/6.3V/M

GND

BUTTOM SIDE

SC23

SC31

SC14

0.22u/6/X7R/10V/K

SC24

22u/8/X5R/6.3V/M

SC13

0.22u/6/X7R/10V/K

22u/8/X5R/6.3V/M

22u/8/X5R/6.3V/M

BUTTOM SIDE

SC4

SC5

0.22u/6/X7R/10V/K

0.01u/6/X7R/50V/K

SC7

SC8

4.7u/8/X5R/6.3V/K

4.7u/8/X5R/6.3V/K

SC15

0.01u/6/X7R/50V/K

VCC12 VCC12_HT

FB70/8/SHT/X

FB80/8/SHT/X

1021 EMI

VCC12

100P/4/NPO/50V/J/X

SC6

180P/6/NPO/50V/J

SC9

180P/6/NPO/50V/J

SC16

180P/6/NPO/50V/J

BC5

DDRVTT

VCC12_HT

C22

4.7u/8/X5R/6.3V/K

C23

4.7u/8/X5R/6.3V/K

GND

C24

0.22u/6/X7R/10V/K

C25

0.22u/6/X7R/10V/K

C26

180P/4/NPO/50V/J

C27

180P/4/NPO/50V/J

DDR18V

C18

4.7u/8/X5R/6.3V/K

C19

4.7u/8/X5R/6.3V/K

GND

C20

0.22u/6/X7R/10V/K

C21

0.22u/6/X7R/10V/K

PDF "pdfFactory Pro" ÿÿ www.pdffactory.com

SC86

180P/6/NPO/50V/J

C10

4.7u/8/X5R/6.3V/K

DDRVTT

C28

4.7u/8/X5R/6.3V/K

C11

4.7u/8/X5R/6.3V/K

GND

C29

4.7u/8/X5R/6.3V/K

GND

C12

0.22u/6/X7R/10V/K

C30

0.22u/6/X7R/10V/K

C13

0.22u/6/X7R/10V/K

C31

0.22u/6/X7R/10V/K

C14

1N/4/X7R/50V/K

C32

1N/4/X7R/50V/K

C15

1N/4/X7R/50V/K

C33

1N/4/X7R/50V/K

C16

180P/4/NPO/50V/J

C34

180P/4/NPO/50V/J

C17

180P/4/NPO/50V/J

C35

180P/4/NPO/50V/J

BC6

100P/4/NPO/50V/J/X

Title

SizeDocument NumberRev

Custom

Date:Sheet of

BC7

100P/4/NPO/50V/J/X

GIGABYTE THCHNOLOGIES , INC.

CPU POWER & GND

BC8

100P/4/NPO/50V/J/X

M2VLE-RH-LE

BC9

100P/4/NPO/50V/J/X

936Tuesday, April 03, 2007

1.2

8

DD

DDR18V DDR18V

TP_DDR18V

BC135

180P/4/NPO/50V/J

CC

BC136

180P/4/NPO/50V/J

VCC3

BC10

0.1u/6/Y5V/25V/Z

DDR_VREF

BB

AA

DDR18V

R46

59/6/1

R47

59/6/1

C37

0.1u/4/Y5V/16V/Z

SMBCLK<17,20,22,23,34> SMBDATA<17,20,22,23,34>

SMBDATA<17,20,22,23,34>

SBAA1<7,11>

SBAA0<7,11>

CKEA0<7,11>

-CSA1<7,11>

-CSA0<7,11>

-DCLKA2<7,11>

DCLKA2<7,11>

-DCLKA1<7,11>

DCLKA1<7,11>

-DCLKA0<7,11>

DCLKA0<7,11>

MAAA0

MAAA[0..15]<7,11>

BC11

0.1u/6/Y5V/25V/Z/X

BC12

0.1u/4/Y5V/16V/Z C39

8

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

SBAA2<7,11>

-SCASA<7,11>

-SRASA<7,11>

-SWEA<7,11>

DDR_VREF

TP_DDR_VREF

BC13

1N/4/X7R/50V/K C38

VCC3

DDR18V

SBAA1

SBAA0

CKEA0

-DCLKA2

DCLKA2

-DCLKA1

DCLKA1

-DCLKA0

DCLKA0

SBAA2

-SCASA

-SRASA

-SWEA

7

100

103

106

109

112

115

118

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

169

198

201

204

207

210

213

216

219

222

225

228

231

234

237

191

194

181

175

170

197

172

187

184

178

189

238

120

119

101

240

239

190

171

193

221

220

138

137

186

185

188

183

182

180

179

177

176

196

174

173

192

7

DDRII_1

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

51

VDDQ

56

VDDQ

62

VDDQ

72

VDDQ

75

VDDQ

78

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

53

VDD

59

VDD

64

VDD

VDD

69

VDD

VDD

VDD

VDD

VDD

VDD

67

VDD

18

RC1

55

RC0

VDDSPD

1

VREF

SCL

SDA

SA2

SA1

SA0

BA1

71

BA0

CKE1

52

CKE0

76

S1*

S0*

CK2*/RFU

CK2/RFU

CK1*/RFU

CK1/RFU

CK0*

CK0

A0

A1

63

A2

A3

61

A4

60

A5

A6

58

A7

A8

A9

70

A10/AP

57

A11

A12

A13

A14

A15

54

A16/BA2

74

CAS*

RSA*

73

WE*

DDR2/240/BU/VA/D[11SM1-510240-D1R]

6

-DQSA[0..8]

DQSA[0..8]

DMA[0:8]

SACB[0..7]

6

NC/TEST

ODT1

ODT0

CB(0)

CB(1)

CB(2)

CB(3)

CB(4)

CB(5)

CB(6)

CB(7)

DQS(0)

DQS*(0)

DQS(1)

DQS*(1)

DQS(2)

DQS*(27)

DQS(3)

DQS*(3)

DQS(4)

DQS*(4)

DQS(5)

DQS*(5)

DQS(6)

DQS*(6)

DQS(7)

DQS*(7)

DQS8

DQS8*

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DQ(0)

DQ(1)

DQ(2)

DQ(3)

DQ(4)

DQ(5)

DQ(6)

DQ(7)

DQ(8)

DQ(9)

DQ(10)

DQ(11)

DQ(12)

DQ(13)

DQ(14)

DQ(15)

DQ(16)

DQ(17)

DQ(18)

DQ(19)

DQ(20)

DQ(21)

DQ(22)

DQ(23)

DQ(24)

DQ(25)

DQ(26)

DQ(27)

DQ(28)

DQ(29)

DQ(30)

DQ(31)

DQ(32)

DQ(33)

DQ(34)

DQ(35)

DQ(36)

DQ(37)

DQ(38)

DQ(39)

DQ(40)

DQ(41)

DQ(42)

DQ(43)

DQ(44)

DQ(45)

DQ(46)

DQ(47)

DQ(48)

DQ(49)

DQ(50)

DQ(51)

DQ(52)

DQ(53)

DQ(54)

DQ(55)

DQ(56)

DQ(57)

DQ(58)

DQ(59)

DQ(60)

DQ(61)

DQ(62)

DQ(63)

-DQSA[0..8]<7>

DQSA[0..8]<7>

DMA[0..8]<7>

SACB[0..7]<7>

5

4

3

DDRII_2

2

SBAB1

SBAB0

CKEB0

-DCLKB2

DCLKB2

-DCLKB1

DCLKB1

-DCLKB0

DCLKB0

SBAB2

-SCASB

-SRASB

-SWEB

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

50

VSS

65

VSS

66

VSS

79

VSS

82

VSS

85

VSS

88

VSS

91

VSS

94

VSS

97

VSS

100

VSS

103

VSS

106

VSS

109

VSS

112

VSS

115

VSS

118

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

169

VSS

198

VSS

201

VSS

204

VSS

207

VSS

210

VSS

213

VSS

216

VSS

219

VSS

222

VSS

225

VSS

228

VSS

231

VSS

234

VSS

237

VSS

51

VDDQ

56

VDDQ

62

VDDQ

72

VDDQ

75

VDDQ

78

VDDQ

191

VDDQ

194

VDDQ

181

VDDQ

175

VDDQ

170

VDDQ

53

VDD

59

VDD

64

VDD

197

VDD

69

VDD

172

VDD

187

VDD

184

VDD

178

VDD

189

VDD

67

VDD

18

RC1

55

RC0

238

VDDSPD

1

VREF

120

SCL

119

SDA

101

SA2

240

SA1

239

SA0

190

BA1

71

BA0

171

CKE1

52

CKE0

76

S1*

193

S0*

221

CK2*/RFU

220

CK2/RFU

138

CK1*/RFU

137

CK1/RFU

186

CK0*

185

CK0

188

A0

183

A1

63

A2

182

A3

61

A4

60

A5

180

A6

58

A7

179

A8

177

A9

70

A10/AP

57

A11

176

A12

196

A13

174

A14

173

A15

54

A16/BA2

74

CAS*

192

RSA*

73

WE*

DDR2/240/GE-3395C/VA/D

100P/4/N/50V/X

3

68

NC

102

19

NC

77

MODT_A0

195

42

43

48

49

161

162

167

168

7

6

16

15

28

27

37

36

84

83

93

92

105

104

114

113

46

45

125

126

134

135

146

147

155

156

202

203

211

212

223

224

232

233

164

165

3

4

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

MODT_A0<7,11>

SACB0

SACB1

SACB2

SACB3

SACB4

SACB5

SACB6

SACB7

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

DQSA8

-DQSA8

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DMA8

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57MDB58

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

MDA[0..63]<7>

DDR_VREF

MAAB[0..15]<7,11>

C36

0.1u/4/Y5V/16V/Z

SMBCLK<17,20,22,23,34>

SMBCLK<17,20,22,23,34>

SMBDATA<17,20,22,23,34>

VCC3

DDR18V

VCC3

SBAB1<7,11>

SBAB0<7,11>

CKEB0<7,11>

-CSB1<7,11>

-CSB0<7,11>

-DCLKB2<7,11>

DCLKB2<7,11>

-DCLKB1<7,11>

DCLKB1<7,11>

-DCLKB0<7,11>

DCLKB0<7,11>

MAAB0

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

MAAB13

MAAB14

MAAB15

SBAB2<7,11>

-SCASB<7,11>

-SRASB<7,11>

-SWEB<7,11>

100P/4/NPO/50V/X

5

4

2

68

NC

102

NC/TEST

19

NC

77

ODT1

MODT_B0

195

ODT0

42

CB(0)

43

CB(1)

48

CB(2)

49

CB(3)

161

CB(4)

162

CB(5)

167

CB(6)

168

CB(7)

7

DQS(0)

6

DQS*(0)

16

DQS(1)

15

DQS*(1)

28

DQS(2)

27

DQS*(27)

37

DQS(3)

36

DQS*(3)

84

DQS(4)

83

DQS*(4)

93

DQS(5)

92

DQS*(5)

105

DQS(6)

104

DQS*(6)

114

DQS(7)

113

DQS*(7)

46

DQS8

45

DQS8*

125

DM0/DQS9

126

NC/DQS9*

134

DM1/DQS10

135

NC/DQS10*

146

DM2/DQS11

147

NC/DQS11*

155

DM3/DQS12

156

NC/DQS12*

202

DM4/DQS13

203

NC/DQS13*

211

DM5/DQS14

212

NC/DQS14*

223

DM6/DQS15

224

NC/DQS15*

232

DM7/DQS16

233

NC/DQS16*

164

DM8/DQS17

165

NC/DQS17*

3

DQ(0)

4

DQ(1)

9

DQ(2)

10

DQ(3)

122

DQ(4)

123

DQ(5)

128

DQ(6)

129

DQ(7)

12

DQ(8)

13

DQ(9)

21

DQ(10)

22

DQ(11)

131

DQ(12)

132

DQ(13)

140

DQ(14)

141

DQ(15)

24

DQ(16)

25

DQ(17)

30

DQ(18)

31

DQ(19)

143

DQ(20)

144

DQ(21)

149

DQ(22)

150

DQ(23)

33

DQ(24)

34

DQ(25)

39

DQ(26)

40

DQ(27)

152

DQ(28)

153

DQ(29)

158

DQ(30)

159

DQ(31)

80

DQ(32)

81

DQ(33)

86

DQ(34)

87

DQ(35)

199

DQ(36)

200

DQ(37)

205

DQ(38)

206

DQ(39)

89

DQ(40)

90

DQ(41)

95

DQ(42)

96

DQ(43)

208

DQ(44)

209

DQ(45)

214

DQ(46)

215

DQ(47)

98

DQ(48)

99

DQ(49)

107

DQ(50)

108

DQ(51)

217

DQ(52)

218

DQ(53)

226

DQ(54)

227

DQ(55)

110

DQ(56)

111

DQ(57)

116

DQ(58)

117

DQ(59)

229

DQ(60)

230

DQ(61)

235

DQ(62)

236

DQ(63)

GIGABYTE THCHNOLOGIES , INC.

Title

SizeDocument NumberRev

Custom

Date:Sheet of

2

MODT_B0<7,11>

SBCB0

SBCB1

SBCB2

SBCB3

SBCB4

SBCB5

SBCB6

SBCB7

DQSB0

-DQSB0

DQSB1

-DQSB1

DQSB2

-DQSB2

DQSB3

-DQSB3

DQSB4

-DQSB4

DQSB5

-DQSB5

DQSB6

-DQSB6

DQSB7

-DQSB7

DQSB8

-DQSB8

DMB0

DMB1

DMB2

DMB3

DMB4

DMB5

DMB6

DMB7

DMB8

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB59

MDB60

MDB61

MDB62

MDB63

DDRII CHANNEL A0,B0

M2VLE-RH-LE1.2

SBCB[0..7]<7>

DQSB[0..8]

-DQSB[0..8]

DMB[0..8]

1

MDB[0..63]<7>

1036

1

SBCB[0..7]

DQSB[0..8]<7>

-DQSB[0..8]<7>

DMB[0..8]<7>

PDF "pdfFactory Pro" ÿÿ www.pdffactory.com

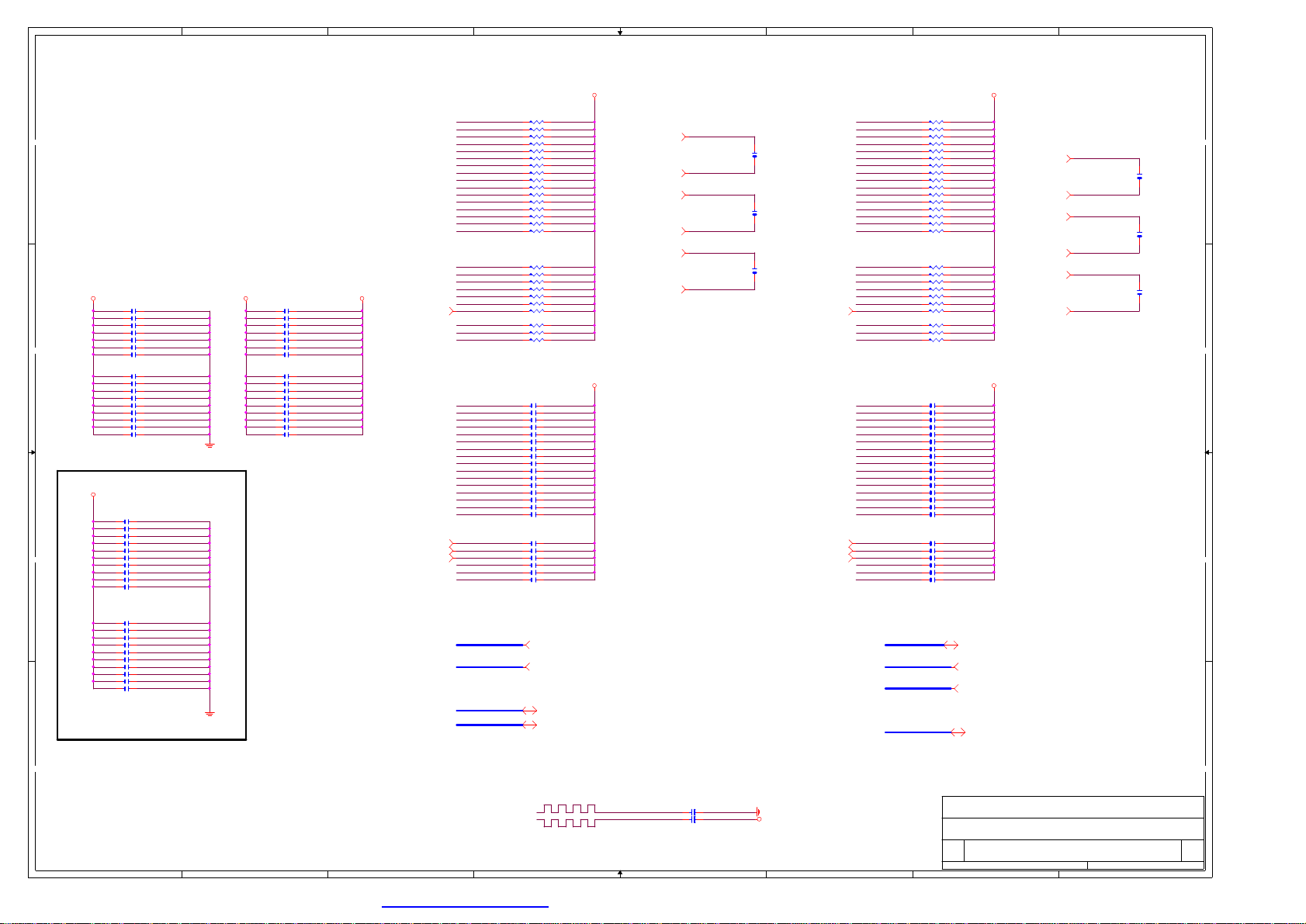

8

7

6

5

4

3

2

1

DDRVTT

MAAA0

MAAA1

MAAA2

DD

DDRVTT

C480.1u/4/X7R/10V/K R9247/4

C500.1u/4/X7R/10V/K

C520.1u/4/X7R/10V/K

C540.1u/4/X7R/10V/K

C570.1u/4/X7R/10V/K

CC

BB

C590.1u/4/X7R/10V/K

C610.1u/4/X7R/10V/K

C640.1u/4/X7R/10V/K

C660.1u/4/X7R/10V/K

C680.1u/4/X7R/10V/K

C710.1u/4/X7R/10V/K

C730.1u/4/X7R/10V/K

C770.1u/4/X7R/10V/K

C820.1u/4/X7R/10V/K

C860.1u/4/X7R/10V/K

C900.1u/4/X7R/10V/K

DDRVTT

C13570.1u/4/X7R/10V/K/X

C13580.1u/4/X7R/10V/K/X

C13590.1u/4/X7R/10V/K/X

C13600.1u/4/X7R/10V/K/X

C13610.1u/4/X7R/10V/K/X

C13620.1u/4/X7R/10V/K/X

C13630.1u/4/X7R/10V/K/X

C13640.1u/4/X7R/10V/K/X

C13650.1u/4/X7R/10V/K/X

C13660.1u/4/X7R/10V/K/X

DDRVTT DDR18V

C490.1u/4/X7R/10V/K

C510.1u/4/X7R/10V/K

C530.1u/4/X7R/10V/K

C550.1u/4/X7R/10V/K

C580.1u/4/X7R/10V/K

C600.1u/4/X7R/10V/K

C620.1u/4/X7R/10V/K

C650.1u/4/X7R/10V/K

C670.1u/4/X7R/10V/K

C690.1u/4/X7R/10V/K

C720.1u/4/X7R/10V/K

C740.1u/4/X7R/10V/K

C780.1u/4/X7R/10V/K

C830.1u/4/X7R/10V/K

C870.1u/4/X7R/10V/K

C910.1u/4/X7R/10V/K

CKEA0<7,10> CKEB0<7,10>

-SWEA<7,10>

-SCASA<7,10>

-SRASA<7,10>

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

R4847/4

R5047/4

R5247/4

R5447/4

R5647/4

R5847/4

R6047/4

R6247/4

R6447/4

R6647/4

R6847/4

R7047/4

R7247/4

R7447/4

R7647/4

R7847/4

-SWEA

R8047/4

-SCASA

R8247/4

-SRASA

R8447/4

SBAA0

R8647/4

SBAA1

R8847/4

SBAA2

R9047/4

CKEA0

-CSA0

R9647/4

-CSA1

R9847/4

MODT_A0

R10047/4

C7522p/4/NPO/50V/J

C7922p/4/NPO/50V/J

C8422p/4/NPO/50V/J

C8822p/4/NPO/50V/J

C9222p/4/NPO/50V/J

C9422p/4/NPO/50V/J

C9622p/4/NPO/50V/J

C9922p/4/NPO/50V/J

C10122p/4/NPO/50V/J

C10322p/4/NPO/50V/J

C10622p/4/NPO/50V/J

C10822p/4/NPO/50V/J

C11022p/4/NPO/50V/J

C11222p/4/NPO/50V/J

C11422p/4/NPO/50V/J

C11622p/4/NPO/50V/J

-SWEA

C11822p/4/NPO/50V/J

-SCASA

C12022p/4/NPO/50V/J

-SRASA

C12222p/4/NPO/50V/J

SBAA0

C12422p/4/NPO/50V/J

SBAA1

C12622p/4/NPO/50V/J

SBAA2

C12822p/4/NPO/50V/J

DCLKA2

DCLKA2<7,10>

C42

-DCLKA2

-DCLKA2<7,10>

DCLKA1

DCLKA1<7,10>

-DCLKA1

-DCLKA1<7,10>

DCLKA0

DCLKA0<7,10>

-DCLKA0

-DCLKA0<7,10>

DDR18V DDR18V

1.5p/4/NPO/50V/C

C44

1.5p/4/NPO/50V/C

C46

1.5p/4/NPO/50V/C

-SWEB<7,10>

-SCASB<7,10>

-SRASB<7,10>

MAAB0

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

MAAB13

MAAB14

MAAB15

-SWEB

-SCASB

-SRASB

SBAB0

SBAB1

SBAB2

CKEB0

-CSB0

-CSB1

MODT_B0

MAAB0

C7622p/4/NPO/50V/J

MAAB1

C8022p/4/NPO/50V/J

MAAB2

C8522p/4/NPO/50V/J

MAAB3

C8922p/4/NPO/50V/J

MAAB4

C9322p/4/NPO/50V/J

MAAB5

C9522p/4/NPO/50V/J

MAAB6

C9822p/4/NPO/50V/J

MAAB7

C10022p/4/NPO/50V/J

MAAB8

C10222p/4/NPO/50V/J

MAAB9

C10422p/4/NPO/50V/J

MAAB10

C10722p/4/NPO/50V/J

MAAB11

C10922p/4/NPO/50V/J

MAAB12

C11122p/4/NPO/50V/J

MAAB13

C11322p/4/NPO/50V/J

MAAB14

C11522p/4/NPO/50V/J

MAAB15

C11722p/4/NPO/50V/J

-SWEB

C11922p/4/NPO/50V/J

-SCASB

C12122p/4/NPO/50V/J

-SRASB

C12322p/4/NPO/50V/J

SBAB0

C12522p/4/NPO/50V/J

SBAB1

C12722p/4/NPO/50V/J

SBAB2

C12922p/4/NPO/50V/J

R4947/4

R5147/4

R5347/4

R5547/4

R5747/4

R5947/4

R6147/4

R6347/4

R6547/4

R6747/4

R6947/4

R7147/4

R7347/4

R7547/4

R7747/4

R7947/4

R8147/4

R8347/4

R8547/4

R8747/4

R8947/4

R9147/4

R9347/4

R9747/4

R9947/4

R10147/4

DDRVTT

DCLKB2

DCLKB2<7,10>

C43

-DCLKB2

-DCLKB2<7,10>

DCLKB1

DCLKB1<7,10>

-DCLKB1

-DCLKB1<7,10>

DCLKB0

DCLKB0<7,10>

-DCLKB0

-DCLKB0<7,10>

1.5p/4/NPO/50V/C

C45

1.5p/4/NPO/50V/C

C47

1.5p/4/NPO/50V/C

C13670.1u/4/X7R/10V/K/X

C13680.1u/4/X7R/10V/K/X

C13690.1u/4/X7R/10V/K/X

C13700.1u/4/X7R/10V/K/X

C13710.1u/4/X7R/10V/K/X

C13720.1u/4/X7R/10V/K/X

C13730.1u/4/X7R/10V/K/X

C13740.1u/4/X7R/10V/K/X

C13750.1u/4/X7R/10V/K/X

C13760.1u/4/X7R/10V/K/X

For the tunnels

to CPU side

AA

8

7

6

SBAA[0:2]

-CSA[0:1]

MAAA[0..15]

MODT_A[0..1]

SBAA[0:2]<7,10>

-CSA[0:1]<7,10>

MAAA[0..15]<7,10>

MODT_A[0..1]<7,10>

5

COUPON1

COUPON1COUPON/X

COUPON2

COUPON2COUPON/X

21

21

IMPEDENCE TESTING COUPON

4

VCC

MODT_B[0..1]

SBAB[0:2]

-CSB[0:1]

MAAB[0..15]

3

MODT_B[0..1]<7,10>

SBAB[0:2]<7,10>

-CSB[0:1]<7,10>

MAAB[0..15]<7,10>

GIGABYTE THCHNOLOGIES , INC.

Title

SizeDocument NumberRev

B

Date:Sheet of

2

DDRII TERMINATOR

M2VLE-RH-LE

1136Wednesday, April 04, 2007

1

1.2

PDF "pdfFactory Pro" ÿÿ www.pdffactory.com

Loading...

Loading...