Page 1

1

2

34

5

6

7

8

A

A

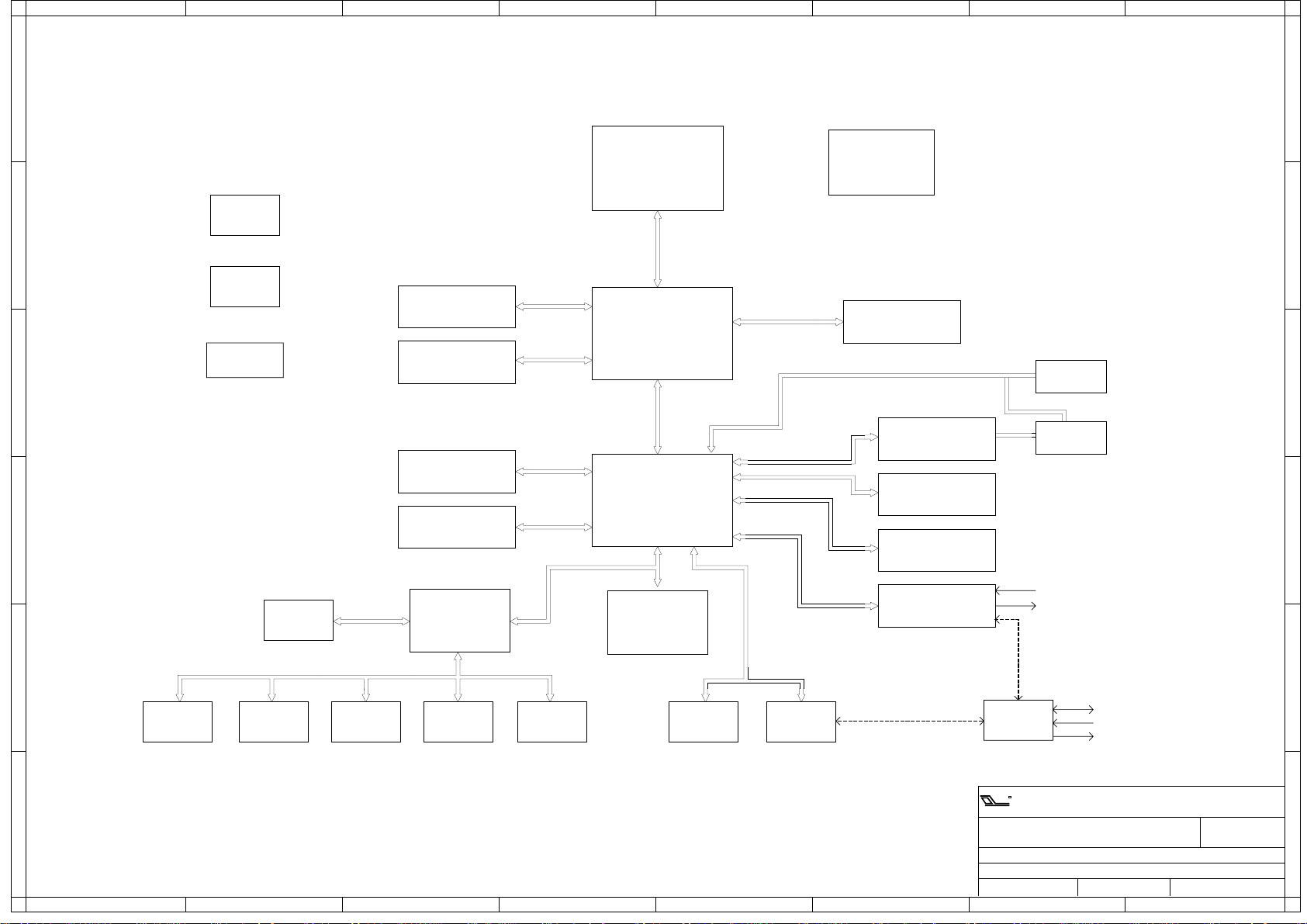

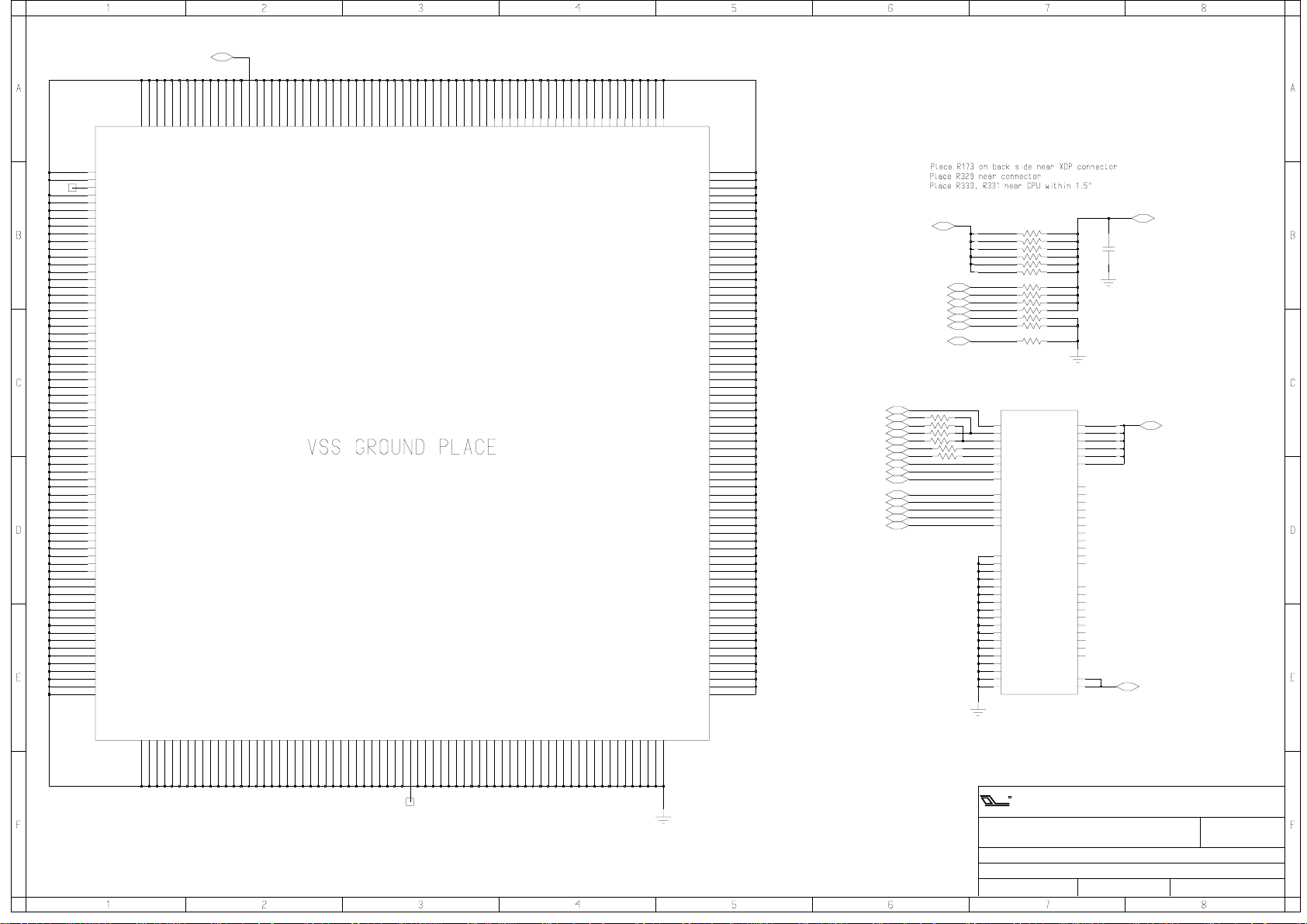

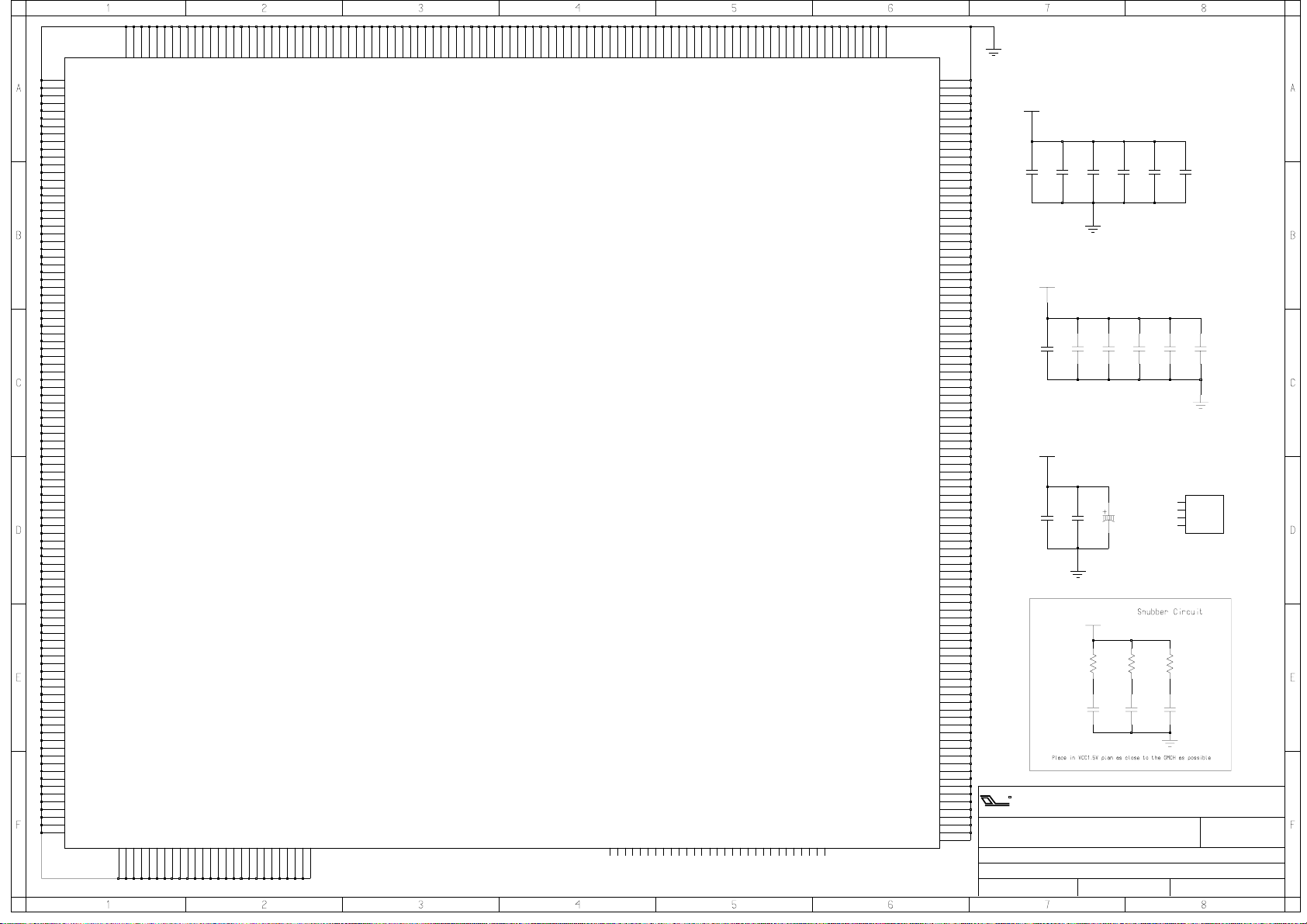

Jamaica Schematics

CONTENTS

B

PAGE 1 TITLE

PAGE 2 SYSTEM BLOCK DIAGRAM

PAGE 3,4,5 LGA775 SOCKET

PAGE 6,7,8,9 INTEL LAKEPORT

PAGE 10 DDR2 CHANNEL A DIMM X 2

PAGE 11 DDR2 CHANNEL B DIMM X 2

PAGE 12 DDR2 TERMINATION RESISTORS

C

PAGE 13 DDR2 DECOUPLING CAPACITORS

PAGE 14 VGA CONNECTOR

PAGE 15,16,17 ICH7

PAGE 18 CLOCK GENERATOR

PAGE 19 SIO(PC8375T/PC8375S)

PAGE 20 PARALLEL & SERIAL PORTS

PAGE 21 FAN X 3,S-ATA2

PAGE 22 IDE,K/B,MOUSE CONNECTORS AND REAR USB PORTS X 4

D

PAGE 23 AC97/AZALIA CODEC(AD1981B/AD1981HD) & MONO AMP

PAGE 24 AUDIO CONNECTOR,REAR USB PORTS X 2 & AFPIO

PAGE 25 LAN TEKOA (10/100/1000Mbps)

PAGE 26 SYSTEM POWER

PAGE 27 CPU PWM

PAGE 28 PCI-EXP X 1 SLOT & PCI-EXP X 16 SLOT

PAGE 29 PCI SLOTS X 2

E

PAGE 30 CHANGED HISTORY

B

C

D

E

R

USI

F

1

2

REV : 3.1

3

45

6

Universal Scientific Industrial Co.,Ltd.

TITLE:

Document Number:

Prepared by:

A3

XXXXXXXX

I.J. Shen

7

Jamaica

TITLE

Date:

2005/4/12

REV:

3.1

PAGE:SIZE:

OF

301

8

F

Page 2

1

2 8

3

4

5

6

7

A

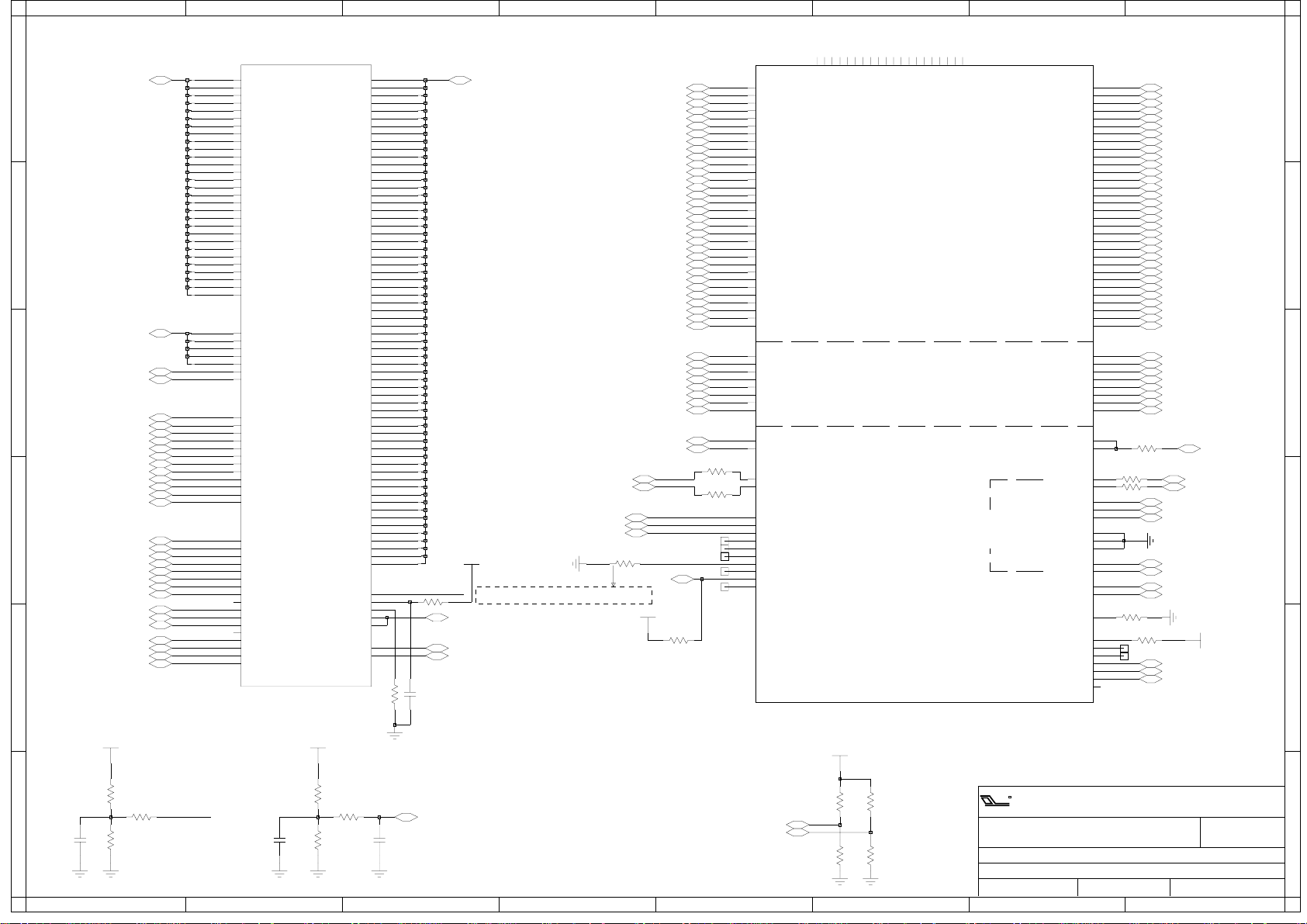

LGA775

Processor

(Smithfield)

(Prescott)

CPU CORE

B

C

D

PWM

P27

SYSTEM

POWER

P26

ATX Connector

P19,21

PCI Express X 16 SLOT

SDVO

P28

VGA CONNECTOR

P14

1 IDE Connector

ATA66/ATA100

P22

4 Serial ATA2

3Gb/s

P25

PCI-EXP Bus

R,G,B

LPC Bus(33MHZ)

Super I/O

Fan x 3

P21

NS PC8375T

NS PC8375S

P19

(Cedar Mill)

P3,4,5

Intel Lakeport

P6,7,8,9

P15,16,17

FWH 8M

FSB (533/800/1066MHz)

GMCH

DMI(100MHZ)

Intel ICH7

DDR2 533/667 MHz

PCI -EXP X 1(100MHZ)

33MHZ

PCI -EXP X 1(100MHZ)

AC97/Azalia Link

USB 2.0

CLOCK

Generator

CK-410

P18

Support Dual Channel mode.

DDR2 DIMM X 4

P10,11,12,13

P25

P29

PCI-EXP X 1 Slot

P28

P23,24

PCI-EXP X 1 LAN

INTEL 82573E

10/100/1000Mbps

PCI Slots X 2

Audio Codec

SPI FOR ICH7

Shared for ICH7 and LAN

SPI FOR LAN

Line In

Line Out

A

B

C

D

EE

Jamaica Block Diagram

USB Port X 2

Mic In

Line Out

Jamaica

System Block

Date:

2005/4/12

PAGE:SIZE:

230

REV:

3.1

OF

84

F

P19

Floppy

Connector

2

6M bit Flash

P19

F

1

Keyboard/Mouse

Connector

P22

Parallel Front

Connector

P20

3

Serial

Connector x 2

P20

Rear

USB Ports X 6

P22,24

Front

USB Ports X 2

P24

5

6

Board

R

USI

Universal Scientific Industrial Co.,Ltd.

TITLE:

Document Number:

Prepared by:

XXXXXXXX

I.J. Shen

A3

7

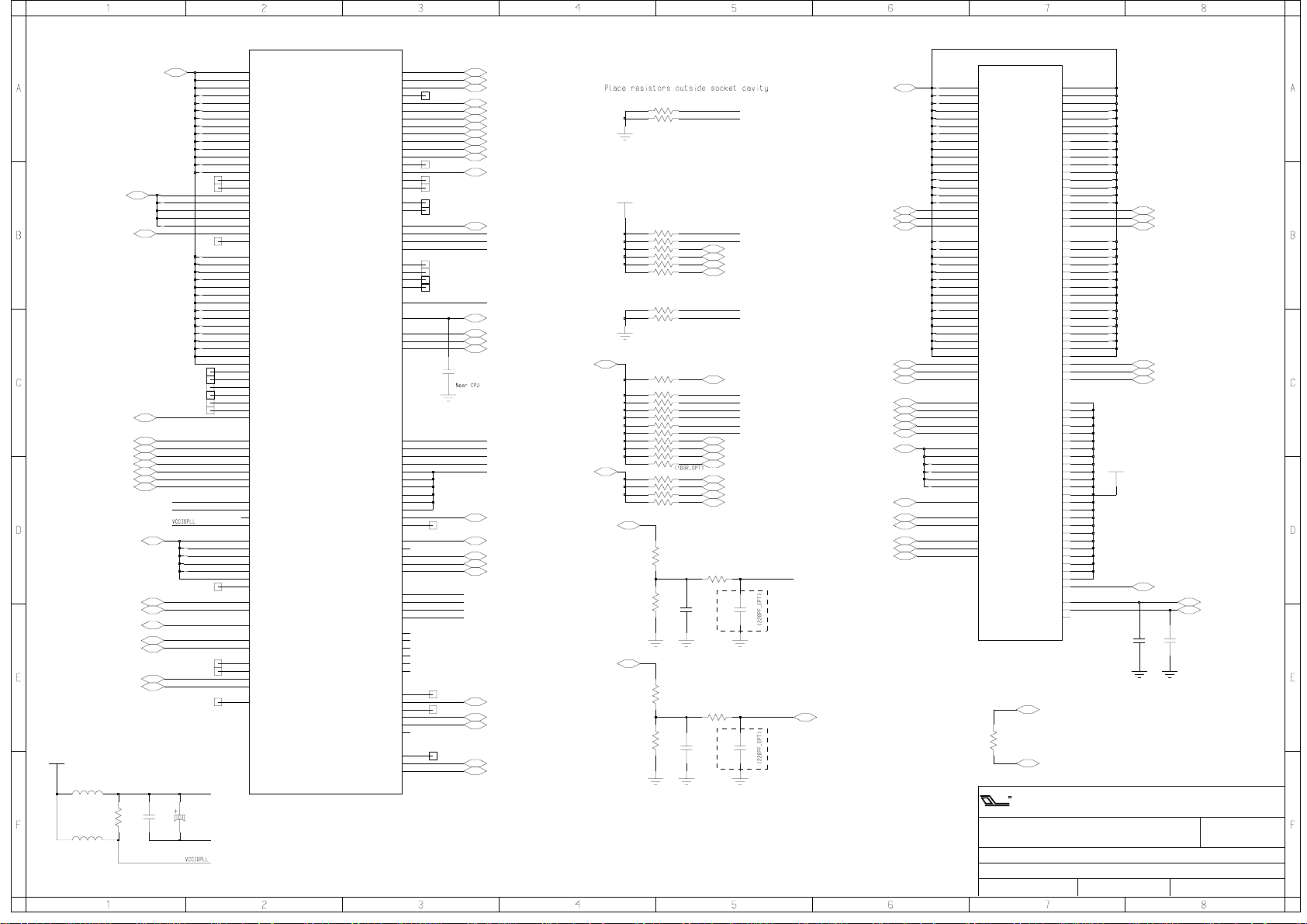

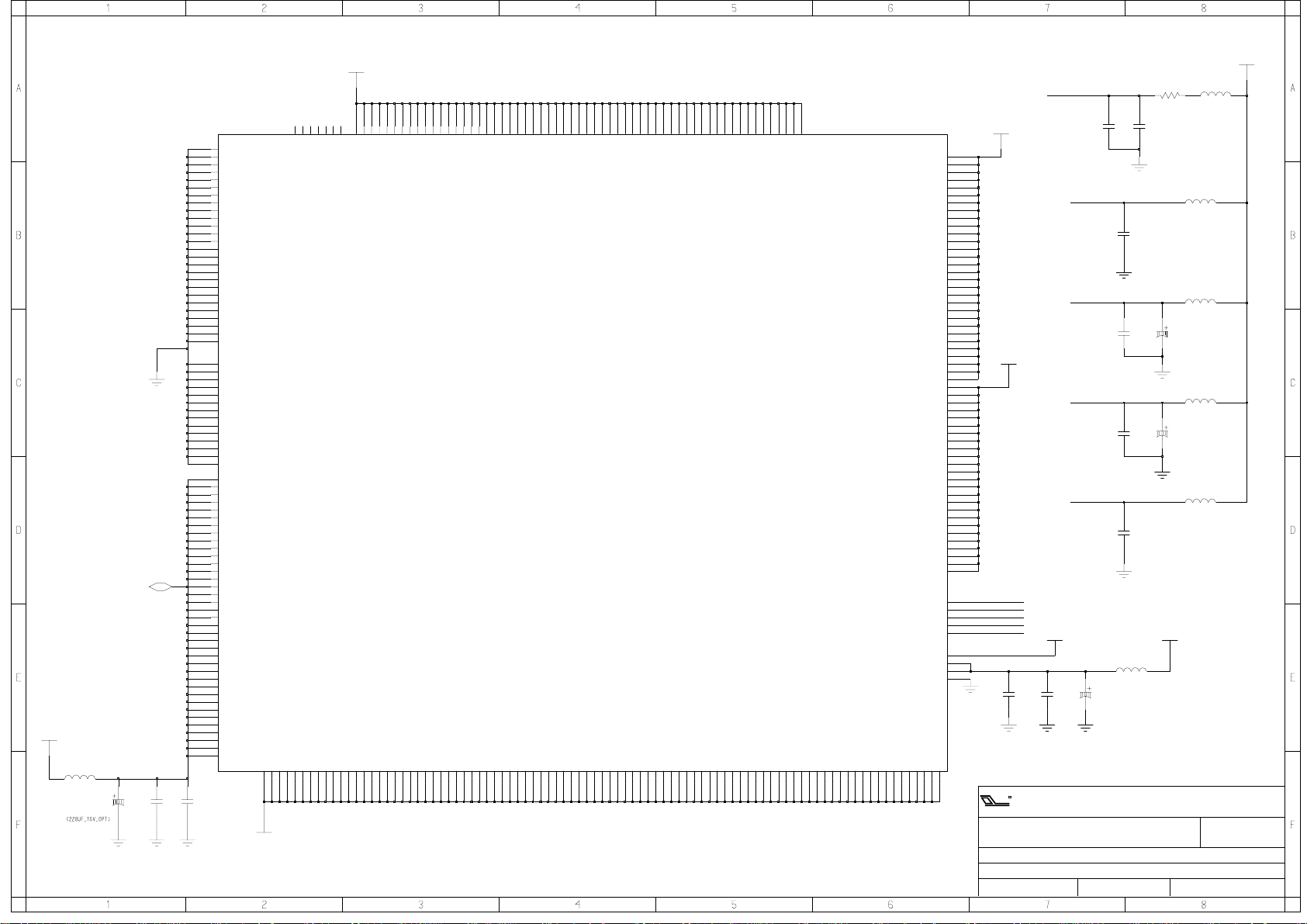

Page 3

6

FSB_VTT

6

H_REQ-(0:4)

H_ADSTB0-

6

H_ADSTB1-

6

15

H_A20M-

15

15

H_FERR15

15

H_IGNNE-

15

15

H_STPCLK-

27

CPUVID(0:5)

18

CLK_HOST_CPU

18

CLK_HOST_CPU19

19

CPU_THERMDA

CPU_THERMDC

19

VCC_SENSE

27

VSS_SENSE

27

LB2012T100MR

L46

10UH_100MA

R404

L47

10UH_100MA

H_A-(3:31)

H_SMI-

H_INTR

H_NMI

SKTOCC-

JMK325BJ476MM-T

0R

H_REQ-(0)

H_REQ-(1)

H_REQ-(2)

H_REQ-(3)

H_REQ-(4)

H_VCCA_VCCIOPLL

H_VSSA

H_VCCA_VCCIOPLL

V

0

3

X

.

1

6

2

_

1

F

_

P

U

7

7

1

A

4

1

C

C

T156

T157

T158

T43

T48

T50

T67

T154

T155

CPUVID(0)

CPUVID(1)

CPUVID(2)

CPUVID(3)

CPUVID(4)

CPUVID(5)

T136

T159

V

0

1

_

F

U

3

3

H_VSSA

T30

T31

J14

L5

H_A-(3)

H_A-(4)

H_A-(5)

H_A-(6)

H_A-(7)

H_A-(8)

H_A-(9)

H_A-(10)

H_A-(11)

H_A-(12)

H_A-(13)

H_A-(14)

H_A-(15)

H_A-(16)

H_A-(17)

H_A-(18)

H_A-(19)

H_A-(20)

H_A-(21)

H_A-(22)

H_A-(23)

H_A-(24)

H_A-(25)

H_A-(26)

H_A-(27)

H_A-(28)

H_A-(29)

H_A-(30)

H_A-(31)

1

L

C

A3-

P6

A4-

M5

A5-

L4

A6-

M4

A7-

R4

A8-

T5

A9-

U6

A10-

T4

A11-

U5

A12-

U4

A13-

V5

A14-

V4

A15-

W5

A16-

N4

RSVED1

P5

RSVED2

K4

REQ0-

J5

REQ1-

M6

REQ2-

K6

REQ3-

J6

REQ4-

R6

ADSTB0-

G5

PCREQ

AB6

A17-

W6

A18-

Y6

A19-

Y4

A20-

AA4

A21-

AD6

A22-

AA5

A23-

AB5

A24-

AC5

A25-

AB4

A26-

AF5

A27-

AF4

A28-

AG6

A29-

AG4

A30-

AG5

A31-

AH4

A32-

AH5

A33-

AJ5

A34-

AJ6

A35-

AC4

RSVD3

AE4

RSVD4

AD5

ADSTB1-

P2

SMI-

K3

A20M-

R3

FERR-_PBE-

K1

LINT0

L1

LINT1

N2

IGNNE-

M3

STPCLK-

A23

VCCA

B23

VSSA

D23

RSVD5

C23

VCCIOPLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

RSVD6_FC11

F28

BCLK0

G28

BCLK1

AE8

SKTOCC-

AL1

THERMDA

AK1

THERMDC

AN3

RSVD7

AN4

RSVD8

AN5

VCC_SENSE

AN6

VSS_SENSE

F29

RSVD118

LGA775_BW_CDM_1

FORCEPH_RSVD9

TESTHI_13_SLP-

CS_GTLREF_RSVD120

GTLREF1_RSVD122

COMP4_RSVD123

ADSBNR-

BPRIDBSYDRDYHITM-

IERR-

INITLOCKTRDYBINIT-

DEFEREDRDYMCERR-

TESTHI_8

TESTHI_9

TESTHI_10

GTLREF

RESET-

TESTHI_00

TESTHI_01

TESTHI_011

TESTHI_012

TESTHI_02

TESTHI_03

TESTHI_04

TESTHI_05

TESTHI_06

TESTHI_07

RSVD10

RSVD11

PWRGOOD

PROCHOT-

THERMTRIP-

COMP0

COMP1

COMP2

COMP3

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD119

RSVD121

RSVD124

BOOTSELECT

LL_ID0

LL_ID1

HITRSP-

AP0AP1-

BR0-

DP0DP1DP2DP3-

RS0RS1RS2-

D2

C2

D4

H4

T32

G8

B2

C1

E4

AB2

P3

C3

E3

AD3

T33

G7

F2

T160

AB3

T34

U2

T35

U3

T36

F3

G3

TESTHI_8

G4

TESTHI_9

H5

TESTHI_10

J16

T107

H15

T108

H16

T109

J17

T110

H1

G23

B3

F5

A3

F26

W3

P1

W2

F25

G25

G27

G26

G24

F24

AK6

G6

T42

L2

AH2

N1

AL2

M2

H_COMP0

A13

H_COMP1

T1

H_COMP2

G2

R1

H_COMP3

N5

AE6

C9

G10

D16

A20

E23

T111

E24

F23

T112

H2

J2

J3

Y1

T68

V2

AA2

CPU_GTLREF0

2

0

4

0

2

_

X

8

P

1

A

C

C

TESTHI_0

TESTHI_1

TESTHI_11

TESTHI_12

TESTHI_2-7

H_ADSH_BNRH_HIT-

H_BPRIH_DBSYH_DRDYH_HITMH_IERRH_INITH_LOCKH_TRDY-

H_DEFER-

H_BR0-

H_CPURSTH_RS0-

H_RS1H_RS2-

H_FORCEPH_IO-

TESTHI_13

H_PWRGD-

H_PROCHOTTHERMTRIP_ICH-

CPU_GMCH_GTLREF

CPU_GTLREF1

H_COMP4

LL_ID0

LL_ID1

3,4,5,27

3,4

3,4,5,27

3,4,5,27

27

3

6

6

6

6

6

6

6

3

15

6

6

6

3,6

3,5,6

6

6

6

VTT_OUT_L

VTT_OUT_R

3,19

VTT_OUT_R

3

3,15

3,15

15,19

VTT_OUT_R

3

3

H_BPM-(0)

H_BPM-(1)

H_BPM-(2)

H_BPM-(3)

H_BPM-(4)

H_BPM-(5)

H_D-(0)

H_D-(1)

H_D-(2)

H_D-(3)

H_D-(4)

H_D-(5)

H_D-(6)

H_D-(7)

H_D-(8)

H_D-(9)

H_D-(10)

H_D-(11)

H_D-(12)

H_D-(13)

H_D-(14)

H_D-(15)

H_D-(16)

H_D-(17)

H_D-(18)

H_D-(19)

H_D-(20)

H_D-(21)

H_D-(22)

H_D-(23)

H_D-(24)

H_D-(25)

H_D-(26)

H_D-(27)

H_D-(28)

H_D-(29)

H_D-(30)

H_D-(31)

6

H_D-(0:63)

60R4_1%R340

R341 60R4_1%

H_COMP0

H_COMP1

FSB_VTT

H_DBI0-

6

H_DSTBN0- H_DSTBN2-

6

H_DSTBP0- H_DSTBP2-

3

3,6

3

4

3,15

3

3

3,15

3,6,18

3,6,18

3,6,18

3,5,6

3,19

3,6,18

3,6,18

3,6,18

6

H_DBI1-

6

6

H_DSTBN1-

H_DSTBP1-

6

5

5

5

5

5

H_TRST-

5

H_BPM-(0:5)

5,15

DBRESET-

5

ITP_CLKOUT

ITP_CLKOUT-

5

FSB_SEL0

FSB_SEL1

FSB_SEL2

CPU_GTLREF1

H_TCK

H_TDI

H_TDO

H_TMS

3

62R

R403

R335 62R

R337

R338

R353 62R

R348

R349

R613 62R

R365

R343 62R

R344 62R

R345 62R

R350 62R

R615 60R4_1%

R378

R80 X

R334 130R

%

1

_

1

R

9

4

3

2

1

R

%

1

_

9

R

1

0

4

1

2

R

%

1

_

7

R

1

4

6

2

1

6

R

%

1

_

8

R

1

0

6

1

2

R

470RR336

470R

470R

60R4_1%

60R4_1%

62R

62RR346

62RR347

60R4_1%R614

X

62RR342

XR396

3

0

6

4

0

1

M

C

3

0

3

6

0

6

M

C

TESTHI_0

TESTHI_2-7

H_COMP2

H_COMP3

TESTHI_1

TESTHI_8

TESTHI_9

TESTHI_10

TESTHI_11

TESTHI_12

R620

10R

R621

10R

FSB_SEL0

FSB_SEL1

FSB_SEL2

H_CPURST-

TESTHI_13

H_BR0H_COMP4

H_COMP5

H_PWRGD-

H_IERRLL_ID1

H_FORCEPH_IOH_PROCHOT-

CPU_GTLREF0

2

0

2

4

7

0

X

_

C

P

A

C

CLOSE TO CPU_GTLREF PIN

2

4

0

8

4

1

0

X

_

C

P

A

C

CLOSE TO CPU_GTLREF PIN

J14

B4

D0-

C5

D1-

A4

D2-

C6

D3-

A5

D4-

B6

D5-

B7

D6-

A7

D7-

A10

D8-

A11

D9-

B10

D10-

C11

D11-

D8

D12-

B12

D13-

C12

D14-

D11

D15-

A8

DBI0-

C8

DSTBN0-

B9

DSTBP0

G9

D16-

F8

D17-

F9

D18-

E9

D19-

D7

D20-

E10

D21-

D10

D22-

F11

D23-

F12

D24-

D13

D25-

E13

D26-

G13

D27-

F14

D28-

G14

D29-

F15

D30-

G15

D31-

G11

DBI1-

G12

DSTBN1-

E12

DSTBP1

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

TRST-

AJ2

BPM0-

AJ1

BPM1-

AD2

BPM2-

AG2

BPM3-

AF2

BPM4-

AG3

BPM5-

AC2

DBR-

AK3

ITPCLK0

AJ3

ITPCLK1

G29

BSEL0

H30

BSEL1

G30

BSEL2

LGA775_BW_CDM_2

7

5

3

K

R

1

USI

TITLE:

Document Number:

Prepared by:

H_D-(32)

G16

D32-

H_D-(33)

E15

D33-

H_D-(34)

E16

D34-

H_D-(35)

G18

D35-

H_D-(36)

G17

D36-

H_D-(37)

F17

D37-

H_D-(38)

F18

D38-

H_D-(39)

E18

D39-

H_D-(40)

E19

D40-

H_D-(41)

F20

D41-

H_D-(42)

E21

D42-

H_D-(43)

F21

D43-

H_D-(44)

G21

D44-

H_D-(45)

E22

D45-

H_D-(46)

D22

D46-

H_D-(47)

G22

D47-

D19

DBI2-

G20

DSTBN2-

G19

DSTBP2

DBI3-

DSTBN3-

DSTBP3

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT_PWRGD

VTT_OUT_R

VTT_OUT_L

VTT_SEL

VTT_OUT_L

VTT_PWRGD

R

Universal Scientific Industrial Co.,Ltd.

H_D-(48)

D20

D48-

H_D-(49)

D17

D49-

H_D-(50)

A14

D50-

H_D-(51)

C15

D51-

H_D-(52)

C14

D52-

H_D-(53)

B15

D53-

H_D-(54)

C18

D54-

H_D-(55)

B16

D55-

H_D-(56)

A17

D56-

H_D-(57)

B18

D57-

H_D-(58)

C21

D58-

H_D-(59)

B21

D59-

H_D-(60)

B19

D60-

H_D-(61)

A19

D61-

H_D-(62)

A22

D62-

H_D-(63)

B22

D63-

C20

A16

C17

A29

B25

B29

B30

C29

A26

B27

C28

A25

FSB_VTT

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

3,4

3,26,27

H_DBI2-

H_DBI3H_DSTBN3H_DSTBP3-

VTT_PWRGD

2

0

4

8

0

3

B

C

2

0

4

0

Jamaica

CPU SOCKET(Host Bus)

XXXXXXXX

I.J. Shen

A3

Date:

2005/4/12

PAGE:SIZE:

6

6

6

6

6

6

3,26,27

VTT_OUT_R

VTT_OUT_L

9

3

B

C

REV:

3.1

330

OF

3,4,5,27

3,4

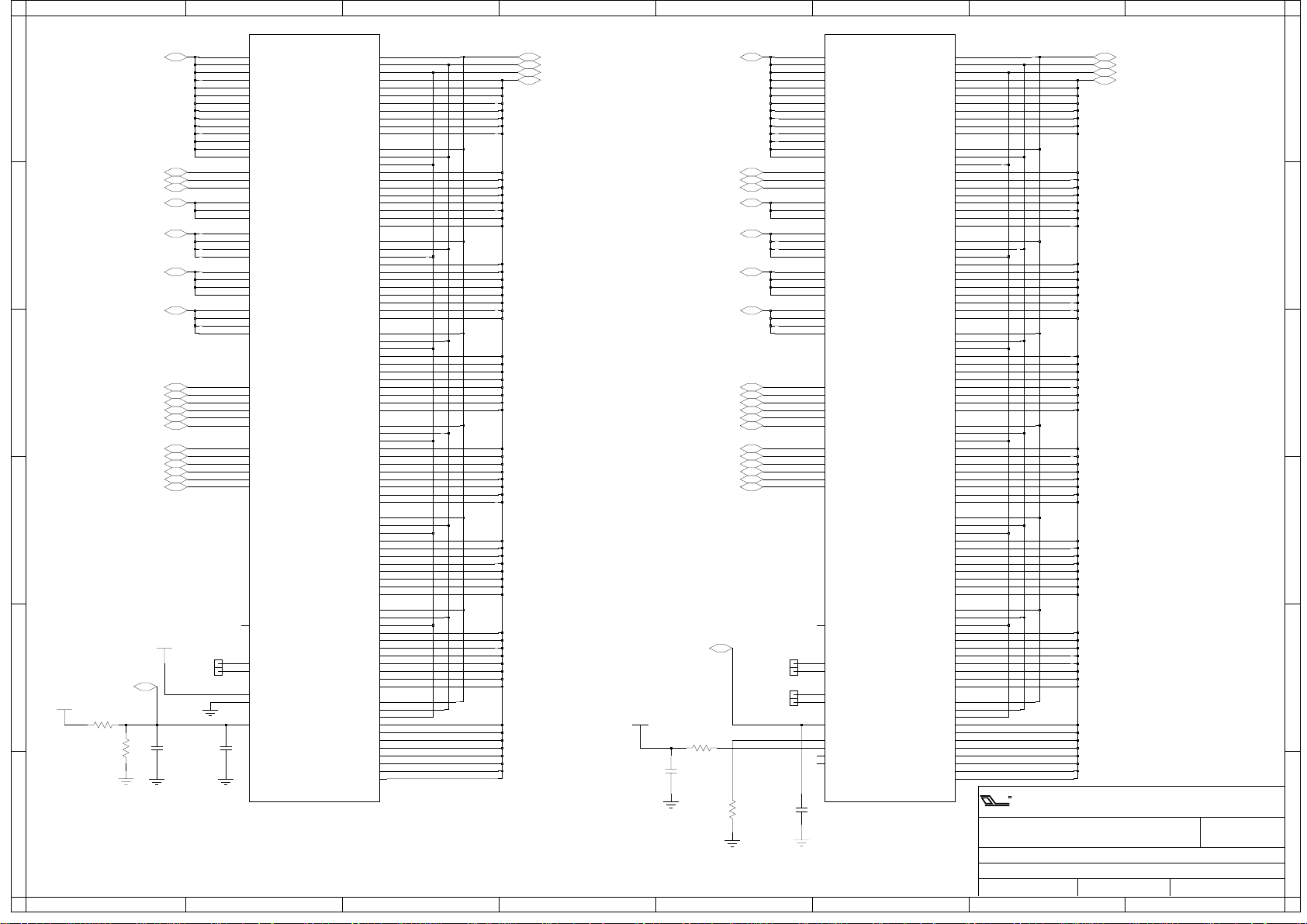

Page 4

4

4

4

3

4

MS_ID0

COMP7

COMP6

H_COMP5

MS_ID1

AG22

K29

AM26

AL8

AE12

AE11

W23

W24

W25

Y28

AL18

AC25

W30

Y30

AN14

AD28

Y26

AC29

M29

U24

AC27

AM18

AM19

AB8

AC26

AM9

AF15

AC8

AE14

N23

W29

U29

AC24

AC23

Y23

AN26

AN25

AN11

AN18

Y27

Y25

AD24

AE23

AE22

AN19

AE21

AM30

AE19

AC30

AE15

M30

K27

M24

AN21

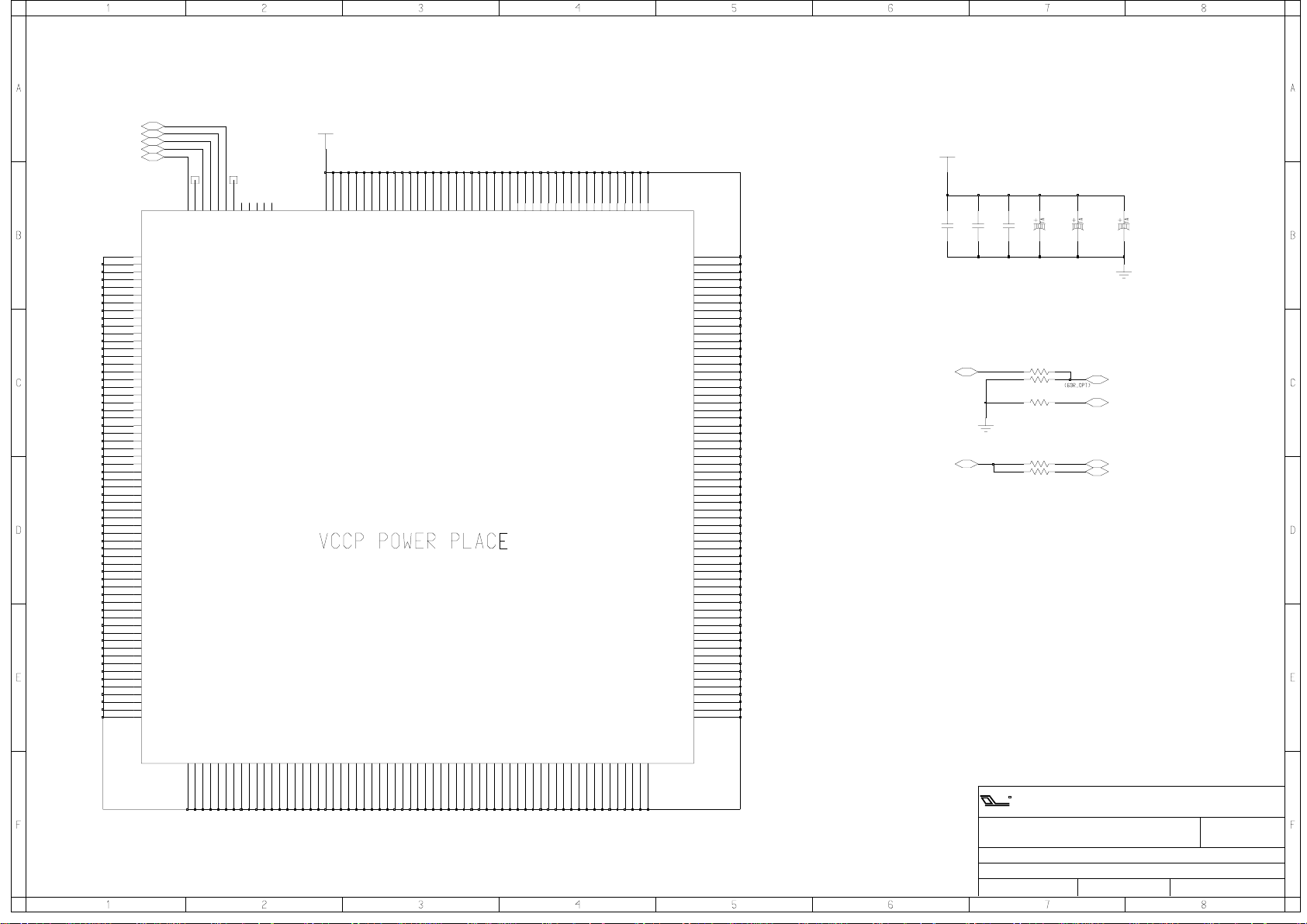

VCORE

3

VTT_OUT_L

VTT_OUT_R

VCORE

7

F

9

U

C

2

2

3

0

0

F

1

U

C

2

2

TITLE:

Document Number:

Prepared by:

0

F

1

U

C

2

2

USI

V

5

.

4

3

2

T

T

_

C

C

F

U

0

0

1

R394 62R

R377

X

NOPOP_RES_0603

62RR610

60R4_1%R105

R269 60R4_1%

R

Universal Scientific Industrial Co.,Ltd.

Jamaica

CPU SOCKET(Vcore)

XXXXXXXX

I.J. Shen

A3

Date:

V

V

5

.

5

.

2

2

_

5

_

F

T

F

U

C

U

0

0

0

0

1

1

MS_ID0

MS_ID1

COMP7

COMP6

2005/4/12

4

4

4

4

REV:

3.1

PAGE:SIZE:

OF

304

6

5

0

0

1

1

T

T

2

9

2

9

2

J14

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

T25

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

J23

VCCP22

VCCP23

VCCP24

VCCP25

VCCP26

VCCP27

J8

VCCP28

J28

VCCP29

T30

VCCP30

VCCP31

VCCP32

VCCP33

VCCP34

VCCP35

VCCP36

VCCP37

VCCP38

VCCP39

VCCP40

VCCP41

VCCP42

VCCP43

VCCP44

VCCP45

VCCP46

VCCP47

VCCP48

VCCP49

VCCP50

V8

VCCP51

K8

VCCP52

VCCP53

VCCP54

VCCP55

VCCP56

VCCP57

VCCP58

VCCP59

VCCP60

VCCP61

3

4

3

1

1

1

E

3

1

V

1

0

3

D

V

S

R

_

1

D

I

S

M

2

6

P

C

C

V

8

T

1

5

6

7

2

6

A

Y

F

T

5

4

2

3

0

0

0

0

3

3

3

3

D

D

D

D

V

V

V

V

S

S

S

S

R

R

R

R

_

5

P

M

O

C

6

5

4

3

6

6

6

6

P

P

P

P

C

C

C

C

C

C

C

C

V

V

V

V

6

8

5

8

2

1

2

2

E

C

N

W

A

A

E

D

E

D

B

E

W

1

0

9

8

7

6

2

1

1

0

0

0

0

1

3

3

3

3

3

3

3

D

D

D

D

D

D

D

V

V

V

V

V

V

V

S

S

S

S

S

S

S

R

R

R

R

R

R

R

_

0

D

I

S

M

6

7

8

7

6

6

P

P

C

C

C

C

V

V

5

8

0

2

3

M

D

N

A

5

4

2

3

1

0

9

6

P

C

C

V

6

2

D

A

7

7

7

7

7

7

7

7

P

P

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

V

5

8

8

6

9

5

6

2

2

2

2

2

L

Y

J

U

M

M

M

A

A

9

9

8

1

1

6

2

4

K

F

F

2

8

1

A

M

A

A

K

N

J

6

5

4

2

3

1

2

2

2

2

2

2

2

2

2

2

2

2

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

LGA775_BW_CDM_3

5

4

8

9

3

0

1

2

8

8

7

7

8

8

8

8

P

P

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

V

8

2

2

1

J

A

8

7

7

3

3

9

2

2

2

2

2

2

2

D

G

U

N

U

M

M

A

A

A

9

2

8

2

8

2

4

8

N

2

H

D

G

L

A

N

A

W

A

A

A

9

8

7

6

5

4

0

2

2

P

C

C

V

6

7

8

8

P

P

C

C

C

C

V

V

8

2

U

K

3

1

1

1

1

1

1

1

2

2

2

2

2

2

2

P

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

9

8

3

0

1

2

8

8

9

9

9

9

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

8

8

4

8

1

2

1

2

2

2

1

D

K

H

H

K

K

A

A

A

A

A

4

8

8

1

0

A

G

3

A

A

J

2

1

0

1

1

1

2

2

2

P

P

P

C

C

C

C

C

C

V

V

V

6

5

4

9

9

9

P

P

P

C

C

C

C

C

C

V

V

V

4

9

2

1

2

2

T

H

M

A

A

0

4

7

1

2

F

A

M

9

8

0

0

2

2

P

P

C

C

C

C

V

V

8

7

9

9

P

P

C

C

C

C

V

V

5

9

2

E

A

M

A

9

1

1

3

1

9

2

4

7

K

2

F

D

L

G

9

J

7

0

2

P

C

C

V

9

9

P

C

C

V

9

2

Y

2

A

Y

A

A

A

A

J

6

5

4

3

2

1

0

0

0

0

0

0

2

2

2

2

2

2

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

5

4

2

3

1

0

0

0

0

0

0

0

1

1

1

1

1

1

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

1

4

1

5

2

5

9

2

2

2

1

2

2

1

J

T

G

G

K

K

M

A

A

A

A

A

1

8

8

2

2

3

4

M

2

1

1

2

J

W

T

J

J

A

9

8

7

6

5

0

6

0

1

P

C

C

V

4

9

9

9

9

9

9

0

1

1

1

1

1

1

2

P

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

7

1

9

2

8

0

0

1

0

1

0

1

1

1

1

1

1

1

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

5

8

1

9

5

0

2

1

2

1

2

3

J

J

J

L

G

U

A

A

A

1

8

7

9

6

2

L

A

3

9

1

P

C

C

V

3

1

1

P

C

C

V

0

3

H

A

2

4

1

1

2

2

2

2

9

6

1

H

J

H

F

G

H

F

H

2

A

A

A

A

A

A

A

A

N

9

8

7

6

2

9

1

P

C

C

V

4

1

1

P

C

C

V

5

2

1

1

J

G

A

5

1

0

4

8

8

8

8

8

9

9

8

1

1

1

1

1

1

1

1

P

P

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

V

AG9

VCCP183

AN12

VCCP182

AK8

VCCP181

T27

VCCP180

AJ19

VCCP179

U26

VCCP178

AJ8

VCCP177

AN15

VCCP176

AL22

VCCP175

AH12

VCCP174

N28

VCCP173

T26

VCCP172

AM8

VCCP171

AL19

VCCP170

K23

VCCP169

P8

VCCP168

K25

VCCP167

J11

VCCP166

J29

VCCP165

AH9

VCCP164

AJ25

VCCP163

AL30

VCCP162

N29

VCCP161

AG14

VCCP160

AK11

VCCP159

AJ9

VCCP158

AL12

VCCP157

AH25

VCCP156

AN30

VCCP155

AL14

VCCP154

K30

VCCP153

AJ11

VCCP152

AL11

VCCP151

AM11

VCCP150

AJ21

VCCP149

AG30

VCCP148

AK21

VCCP147

AF8

VCCP146

AM15

VCCP145

AD23

VCCP144

AF11

VCCP143

AK15

VCCP142

AG27

VCCP141

J21

VCCP140

J18

VCCP139

J26

VCCP138

AL15

VCCP137

AF18

VCCP136

AH15

VCCP135

AN9

VCCP134

AG26

VCCP133

AJ15

VCCP132

J10

VCCP131

AK26

VCCP130

AG11

VCCP129

AN29

VCCP128

AK22

VCCP127

R8

VCCP126

T23

VCCP125

U27

VCCP124

AH14

VCCP123

6

5

9

8

1

2

7

0

1

1

1

1

2

2

1

2

1

1

1

1

1

1

1

1

P

P

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

V

2

0

8

5

6

8

7

2

2

1

2

2

2

N

J

J

L

H

H

A

W

A

A

A

A

3,5,27

Page 5

5

FC16

T135

AE16

AL10

AK23

AL16

AL24

AK13

AL20

AK16

AK20

AM27

AL13

AL17

AK30

AL23

AE28

AE29

AE30

AN20

AF10

AE24

AM24

AN23

AM16

AE25

AE27

AH13

7

8

3

3

J14

C10

VSS1

D12

VSS2

AM7

VSS3_FC12

C24

VSS4

K2

VSS5

C22

VSS6

AN1

VSS7

B14

VSS8

K7

VSS9

VSS10

B11

VSS11

VSS12

VSS13

H12

VSS14

AF7

VSS15

AK7

VSS16

H7

VSS17

E14

VSS18

L28

Y5

VSS20

E11

VSS21

VSS22

VSS23

VSS24

AL3

VSS25

D21

VSS26

VSS27

D18

VSS28

AN2

VSS29

VSS30

VSS31

VSS32

AM1

VSS33

VSS34

VSS35

C19

VSS36

E28

VSS37

AH7

VSS38

VSS39

D24

VSS40

VSS41

A12

VSS42

L25

VSS43

J7

VSS44

VSS45

VSS46

K5

VSS47

J4

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

H9

VSS55

H8

VSS56

H13

VSS57

AC6

VSS58

AC7

VSS59

AH6

VSS60

C16

VSS61

VSS62

VSS63

VSS64

AJ28

VSS65

AJ7

VSS66

F19

VSS67

VSS68

AD7

VSS69

2

2

2

2

6

F

2

L

A

G

A

V

A

A

A

6

2

4

3

5

7

7

7

7

7

2

2

2

2

2

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

2

0

1

4

3

7

7

7

7

7

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

6

7

0

7

7

1

1

2

1

1

E

H

K

H

H

A

A

A

A

8

0

7

4

7

1

1

0

2

7

M

E

B

J

3

2

7

E

A

A

A

A

T

R

1

5

0

9

8

6

7

7

6

7

6

6

6

6

2

2

2

2

2

2

2

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

8

9

7

6

1

5

0

7

7

7

7

8

7

8

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

3

4

7

3

5

0

0

1

2

2

3

1

E

E

J

J

H

H

A

A

M

A

A

A

A

A

4

4

0

2

4

E

2

P

A

4

3

6

6

2

2

S

S

S

S

V

V

4

3

7

7

2

1

F

N

3

N

A

A

H

A

6

9

1

0

1

5

6

6

2

2

2

C

S

S

S

F

S

S

S

_

2

V

V

V

6

2

S

S

V

6

7

5

2

2

2

2

2

2

2

2

F

N

N

G

F

F

1

F

F

A

A

A

A

A

A

G

A

A

5

4

3

6

8

7

5

5

2

2

S

S

S

S

V

V

0

2

1

5

5

5

5

5

5

5

2

2

2

2

2

2

2

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

LGA775_BW_CDM_4

9

8

7

6

5

4

3

2

8

S

S

V

3

5

F

K

A

A

8

8

8

8

8

8

8

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

2

3

7

9

6

6

0

2

1

2

1

1

F

H

J

J

F

K

K

A

A

A

A

A

A

6

4

5

3

2

1

0

9

9

9

9

9

9

9

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

0

3

7

3

6

0

1

1

2

1

1

G

J

F

F

F

M

A

A

A

0

3

9

0

8

1

1

2

3

2

8

F

F

E

F

2

G

7

4

A

A

A

A

F

H

A

F

7

4

8

6

5

9

4

2

S

S

V

7

9

S

S

V

6

2

L

3

2

4

4

4

4

4

4

4

2

2

2

2

2

2

2

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

4

2

3

1

0

8

9

0

0

0

0

0

9

9

1

1

1

1

1

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

4

1

0

3

5

3

4

1

1

2

1

2

2

D

L

L

H

H

A

M

A

A

A

6

0

3

3

2

B

A

3

A

A

N

9

1

0

3

4

4

2

2

2

S

S

S

S

S

S

V

V

V

L

E

S

_

F

E

R

L

T

G

_

7

6

5

0

0

0

1

1

1

S

S

S

S

S

S

V

V

V

3

4

9

2

2

L

B

H

7

4

5

2

2

B

B

A

A

8

3

2

S

S

V

8

0

1

S

S

V

7

1

2

2

H

A

0

6

7

1

1

2

2

2

7

N

B

B

N

G

8

M

A

A

E

A

A

A

5

4

7

6

3

2

1

0

3

3

3

3

3

3

3

3

2

2

2

2

2

2

2

2

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

V

6

4

5

2

3

1

9

0

0

1

1

1

S

S

S

S

V

V

2

E

A

1

1

1

1

1

1

1

1

1

1

1

1

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

0

8

0

4

7

9

2

2

2

2

2

2

J

B

K

K

A

M

A

A

A

A

4

8

9

0

6

1

2

2

2

3

2

3

4

1

B

B

7

A

M

A

L

9

8

7

2

2

2

2

2

2

S

S

S

S

S

S

V

V

V

9

8

7

1

1

1

1

1

1

S

S

S

S

S

S

V

V

V

7

5

6

4

1

2

2

2

B

H

H

H

9

H

E

J

B

K

7

1

6

2

L

A

A

C

V

E

4

6

5

3

2

1

0

2

2

2

2

2

2

2

2

2

2

2

2

2

2

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

6

4

5

2

3

0

1

2

2

2

2

2

2

2

1

1

1

1

1

1

1

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

2

6

0

7

3

3

2

1

2

A

A

A

H

H

H

A

A

A

3

9

5

6

6

1

8

5

A

A

A

B

B

9

8

7

6

5

1

1

1

1

1

2

2

2

2

2

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

8

7

1

9

0

2

2

3

2

3

1

1

1

1

1

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

0

1

7

8

9

2

2

1

1

B

H

H

H

H

A

4

B

D

A

D

A

C

D

4

3

2

1

0

9

1

2

S

S

V

2

3

1

S

S

V

7

1

H

8

1

1

1

1

0

0

2

2

2

2

2

2

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

D9

VSS207

E2

VSS206

A2

VSS205

A18

VSS204

H6

VSS203

AF13

VSS202

AE10

VSS201

AF16

VSS200

P29

VSS199

V3

VSS198

P30

VSS197

R23

VSS196

R24

VSS195

U7

VSS194

R25

VSS193

R26

VSS192

R27

VSS191

R28

VSS190

R29

VSS189VSS19

U1

VSS188

E25

VSS187

AL7

VSS186

T6

VSS185

V23

VSS184

V24

VSS183

T3

VSS182

V25

VSS181

AN10

VSS180

E20

VSS179

R7

VSS178

V27

VSS177

R5

VSS176

V28

VSS175

V29

VSS174

R2

VSS173

V30

VSS172

E26

VSS171

P7

VSS170

AA24

VSS169

AA25

VSS168

P4

VSS167

AA26

VSS166

AA27

VSS165

AN13

VSS164

AA28

VSS163

N7

VSS162

N6

VSS161

AA29

VSS160

L27

VSS159

Y7

VSS158

AL27

VSS157

D15

VSS156

L29

VSS155

L30

VSS154

Y2

VSS153

C7

VSS152

AG17

VSS151

AG16

VSS150

AG13

VSS149

P23

VSS148

W7

VSS147

AJ20

VSS146

P25

VSS145

W4

VSS144

AJ13

VSS143

AM28

VSS142

P26

VSS141

P27

VSS140

AK2

VSS139

8

7

6

5

4

3

3

3

3

3

3

3

1

1

1

1

1

1

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

4

8

3

7

4

6

1

2

1

2

C

V

J

P

H

M

A

A

A

18

18

3

3

3,4,5,27

10,11,18,19

10,11,18,19

3,15

3,6

3,5

3,5

3,5

3,5

3,5

3,5

DBRESET-

CLK_HOST_ITP-

CLK_HOST_ITP

ITP_CLKOUT-

ITP_CLKOUT

VTT_OUT_R

H_CPURST-

SMB_CLK

SMB_DATA

TESTIN-

5

H_TDO

H_TDI

H_TMS

H_TCK

H_TRST-

H_BPM-(0:5)

5

3,5

3,5

3,5

3,5

3,5

5

TESTIN-

H_TDO

H_TDI

H_TMS

H_TCK

H_TRST-

FC16

R3180R

0R

R319

R320

X

R321X

49R9_1% R608

1K

H_BPM-(0)

H_BPM-(1)

H_BPM-(2)

H_BPM-(3)

H_BPM-(4)

H_BPM-(5)

R330 49R9_1%

R331

R332 49R9_1%

R609

48

42

40

39

R322

46

53

51

41

52

56

58

57

54

1

2

7

8

13

14

19

20

25

26

31

32

37

38

49

50

59

60

SAMTEC BSH-03-01-H-D

R323

R324

R325

R326

R327

X

J12

DBR

ITP_CLKN

ITP_CLKP

PWRGOOD

RESETSCL

SDA

TESTIN-

TDO

TDI

TMS

TCK

TRST-

VSS1

VSS2

VSS3

VSS4

VSS5

NOA_PILOTCLK

VSS6

NOA_PILOTCLKVSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

X_XDP_CONN

62R

62R

62R

62R

62R

62RR328

49R9_1%R173

49R9_1%R329

49R9_1%

49R9_1%R333

62R

BPM5BPM4BPM3BPM2BPM1-

BPM0

NC10

NC11

NOA_PILOT0

NOA_PILOT1

NOA_PILOT2

NOA_PILOT3

NOA_PILOT4

NOA_PILOT5

NOA_PILOT6

NOA_PILOT7

VTT1

VTT2

H_BPM-(5)

3

H_BPM-(4)

5

H_BPM-(3)

9

H_BPM-(2)

11

H_BPM-(1)

15

H_BPM-(0)

17

21

NC1

22

NC2

23

NC3

24

NC4

27

NC5

29

NC6

33

NC7

35

NC8

45

NC9

47

55

4

6

10

12

16

18

28

30

34

36

43

44

2

0

4

0

7

3

B

C

VTT_OUT_R

H_BPM-(0:5)

VTT_OUT_R

3,4,5,27

3,5

3,4,5,27

T153

R

USI

Universal Scientific Industrial Co.,Ltd.

TITLE:

Document Number:

Prepared by:

A3

Jamaica

CPU SOCKET(Ground) & XDP

XXXXXXXX

I.J. Shen

Date:

2005/4/12

REV:

3.1

PAGE:SIZE:

OF

305

Page 6

1 43 65 87

H_A-(3:31)

A

3

B

3

H_REQ-(0:4)

3

H_ADSTB0H_ADSTB1-

C

D

3

3

3

3

3

3

3

3

3

3

3

3

3

3,5

3

3

3

3

3

3

3

3

3

3

3

3

3

3

H_DSTBP0-

H_DSTBN0-

H_DBI0-

H_DSTBP1-

H_DSTBN1-

H_DBI1-

H_DSTBP2-

H_DSTBN2-

H_DBI2-

H_DSTBP3-

H_DSTBN3-

H_DBI3-

H_ADSH_BNR-

H_BPRI-

H_BR0-

H_CPURST-

H_DBSY-

H_DEFER-

H_DRDY-

H_HIT-

H_HITM-

H_LOCK-

H_RS0H_RS1H_RS2-

H_A-(3)

H_A-(4)

H_A-(5)

H_A-(6)

H_A-(7)

H_A-(8)

H_A-(9)

H_A-(10)

H_A-(11)

H_A-(12)

H_A-(13)

H_A-(14)

H_A-(15)

H_A-(16)

H_A-(17)

H_A-(18)

H_A-(19)

H_A-(20)

H_A-(21)

H_A-(22)

H_A-(23)

H_A-(24)

H_A-(25)

H_A-(26)

H_A-(27)

H_A-(28)

H_A-(29)

H_A-(30)

H_A-(31)

H_REQ-(0)

H_REQ-(1)

H_REQ-(2)

H_REQ-(3)

H_REQ-(4)

E

FSB_VTT

2

U42

J39

HA3-

K38

HA4-

J42

HA5-

K35

HA6-

J37

HA7-

M34

HA8-

N35

HA9-

R33

HA10-

N32

HA11-

N34

HA12-

M38

HA13-

N42

HA14-

N37

HA15-

N38

HA16-

R32

HA17-

R36

HA18-

U37

HA19-

R35

HA20-

R38

HA21-

V33

HA22-

U34

HA23-

U32

HA24-

V42

HA25-

U35

HA26-

Y36

HA27-

Y38

HA28-

AA37

HA29-

V32

HA30-

Y34

HA31-

E41

HREQ0-

D41

HREQ1-

K36

HREQ2-

G37

HREQ3-

E42

HREQ4-

M36

HADSTB0-

V35

HADSTB1-

K41

HDSTBP0-

L43

HDSTBN0-

K40

HDINV0-

F35

HDSTBP1-

G34

HDSTBN1-

A38

HDINV1-

J27

HDSTBP2-

M26

HDSTBN2-

E29

HDINV2-

E34

HDSTBP3-

B37

HDSTBN3-

B32

HDINV3-

W42

HADS-

U39

HBNR-

D42

HBPRI-

AA41

HBREQ0-

C30

HCPURST-

U42

HDBSY-

P40

HDEFER-

V41

HDRDY-

Y40

HEDRDY-

U41

HHIT-

W41

HHITM-

U40

HLOCK-

F38

HPCREQ-

T40

HRS0-

Y43

HRS1-

T43

HRS2-

W40

HTRDY-

LAKEPORT_1

Host Interface

FSB_VTT

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

HDSWING

HSCOMP

HRCOMP

HDVREF

HACCVREF

HCLKP

HCLKN

P41

HD0

M39

HD1

P42

HD2

M42

HD3

N41

HD4

M40

HD5

L40

HD6

M41

HD7

K42

HD8

G39

HD9

J41

G42

G40

G41

F40

F43

F37

E37

J35

D39

C41

B39

B40

H34

C37

J32

B35

J34

B34

F32

L32

J31

H31

M33

K31

M27

K29

F31

H29

F29

L27

M24

J26

K26

G26

H24

K24

F24

E31

A33

E40

D37

C39

D38

D33

C35

D34

C34

B31

C31

C32

D32

B30

D30

B27

R371 60R4_1%

C27

A28

D27

D28

M31

M29

%

1

_

9

0

7

R

3

6

1

R

H_D-(0)

H_D-(1)

H_D-(2)

H_D-(3)

H_D-(4)

H_D-(5)

H_D-(6)

H_D-(7)

H_D-(8)

H_D-(9)

H_D-(10)

H_D-(11)

H_D-(12)

H_D-(13)

H_D-(14)

H_D-(15)

H_D-(16)

H_D-(17)

H_D-(18)

H_D-(19)

H_D-(20)

H_D-(21)

H_D-(22)

H_D-(23)

H_D-(24)

H_D-(25)

H_D-(26)

H_D-(27)

H_D-(28)

H_D-(29)

H_D-(30)

H_D-(31)

H_D-(32)

H_D-(33)

H_D-(34)

H_D-(35)

H_D-(36)

H_D-(37)

H_D-(38)

H_D-(39)

H_D-(40)

H_D-(41)

H_D-(42)

H_D-(43)

H_D-(44)

H_D-(45)

H_D-(46)

H_D-(47)

H_D-(48)

H_D-(49)

H_D-(50)

H_D-(51)

H_D-(52)

H_D-(53)

H_D-(54)

H_D-(55)

H_D-(56)

H_D-(57)

H_D-(58)

H_D-(59)

H_D-(60)

H_D-(61)

H_D-(62)

H_D-(63)

F

P

2

.

2

3

2

C

HXSWING

X

H_D-(0:63)

FSB_VTT

0 : GMCH's PCI Express lane numbers are reversed.

1 : Normal operation. (for ATX)

CPU_GMCH_GTLREF

CLK_HOST_GMCH

CLK_HOST_GMCH-

3,6

18

18

3

28

SDVO_CTRL_DATA

28

SDVO_CTRL_CLK

3,18

3,18

3,18

EXP_RXP_0

28

EXP_RXN_0

28

EXP_RXP_1

28

EXP_RXN_1

28

EXP_RXP_2

28

EXP_RXN_2

28

28

EXP_RXP_3

EXP_RXN_3

28

EXP_RXP_4

28

EXP_RXN_4

28

28

EXP_RXP_5

EXP_RXN_5

28

28

EXP_RXP_6

EXP_RXN_6

28

EXP_RXP_7

28

EXP_RXN_7

28

EXP_RXP_8

28

EXP_RXN_8

28

EXP_RXP_9

28

EXP_RXN_9

28

28

EXP_RXP_10

EXP_RXN_10

28

EXP_RXP_11

28

EXP_RXN_11

28

EXP_RXP_12

28

EXP_RXN_12

28

EXP_RXP_13

28

EXP_RXN_13

28

EXP_RXP_14

28

28

EXP_RXN_14

EXP_RXP_15

28

EXP_RXN_15

28

DMI_RXP_0

16

16

DMI_RXN_0

DMI_RXP_1

16

DMI_RXN_1

16

16

DMI_RXP_2

16

DMI_RXN_2

16

DMI_RXP_3

16

DMI_RXN_3

18

CLK_PE_100M_GMCH

CLK_PE_100M_GMCH-

18

FSB_SEL0

FSB_SEL1

FSB_SEL2

R373

3K

EXP_EN

28

VCC3

R79 X

R446 100R

R447

T144

T145

T146

T9

T10

100R

AA10

G12

F12

D11

D12

J13

H13

E10

F10

J9

H10

F7

F9

C4

D3

G6

J6

K9

K8

F4

G4

M6

M7

K2

L1

U11

U10

R8

R7

P4

N3

Y10

Y11

Y7

Y8

AA9

AA6

AA7

AC9

AC8

B14

B16

F15

E15

F21

H21

L20

K18

H20

L18

K21

L21

F20

N21

U42

EXP_RXP0

EXP_RXN0

EXP_RXP1

EXP_RXN1

EXP_RXP2

EXP_RXN2

EXP_RXP3

EXP_RXN3

EXP_RXP4

EXP_RXN4

EXP_RXP5

EXP_RXN5

EXP_RXP6

EXP_RXN6

EXP_RXP7

EXP_RXN7

EXP_RXP8

EXP_RXN8

EXP_RXP9

EXP_RXN9

EXP_RXP10

EXP_RXN10

EXP_RXP11

EXP_RXN11

EXP_RXP12

EXP_RXN12

EXP_RXP13

EXP_RXN13

EXP_RXP14

EXP_RXN14

EXP_RXP15

EXP_RXN15

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

GCLKP

GCLKN

SDVO_CTRLDATA

SDVO_CTRLCLK

BSEL0

BSEL1

BSEL2

ALLZTEST

XORTEST

RSV_TP5

EXP_SLR

RSV_TP4

EXP_EN

RSV_TP6

6

7

6

2

2

2

2

2

2

B

B

0

2

_

2

C

N

2

5

V

W

V

W

4

A

3

A

E

C

A

A

B

A

5

2

9

9

6

6

0

_

_

1

_

1

_

1

2

2

_

2

_

2

_

2

2

2

C

C

C

C

C

C

C

N

N

N

N

N

N

N

3

3

2

4

4

2

1

4

1

1

2

B

C

4

C

C

C

4

B

5

1

_

2

C

N

B

B

B

B

B

B

B

B

4

8

8

7

3

4

_

1

_

1

1

1

2

_

2

_

_

_

2

2

2

2

C

C

C

C

C

C

N

N

N

N

N

N

PCI Express Interface

3

2

3

2

4

C

B

B

B

3

7

2

1

1

_

_

1

1

_

2

2

_

_

2

2

2

C

C

C

C

C

N

N

N

N

N

EXP_TXP0

EXP_TXN0

EXP_TXP1

EXP_TXN1

EXP_TXP2

EXP_TXN2

EXP_TXP3

EXP_TXN3

EXP_TXP4

EXP_TXN4

EXP_TXP5

EXP_TXN5

EXP_TXP6

EXP_TXN6

EXP_TXP7

EXP_TXN7

EXP_TXP8

EXP_TXN8

EXP_TXP9

EXP_TXN9

EXP_TXP10

EXP_TXN10

EXP_TXP11

EXP_TXN11

EXP_TXP12

EXP_TXN12

EXP_TXP13

EXP_TXN13

EXP_TXP14

EXP_TXN14

EXP_TXP15

EXP_TXN15

D14

C13

A13

B12

A11

B10

C10

C9

A9

B7

D7

D6

A6

B5

E2

F1

G2

J1

J3

K4

L4

M4

M2

N1

P2

T1

T4

U4

U2

V1

V3

W4

EXP_TXP_0

EXP_TXN_0

EXP_TXP_1

EXP_TXN_1

EXP_TXP_2

EXP_TXN_2

EXP_TXP_3

EXP_TXN_3

EXP_TXP_4

EXP_TXN_4

EXP_TXP_5

EXP_TXN_5

EXP_TXP_6

EXP_TXN_6

EXP_TXP_7

EXP_TXN_7

EXP_TXP_8

EXP_TXN_8

EXP_TXP_9

EXP_TXN_9

EXP_TXP_10

EXP_TXN_10

EXP_TXP_11

EXP_TXN_11

EXP_TXP_12

EXP_TXN_12

EXP_TXP_13

EXP_TXN_13

EXP_TXP_14

EXP_TXN_14

EXP_TXP_15

EXP_TXN_15

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

28

A

B

LAKEPORT_2

DMI Interface

Analog Display Port

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

EXP_COMPO

EXP_COMPI

CRTHSYNC

CRTVSYNC

CRTRED

CRTGREEN

CRTBLUE

CRTRED-

CRTGREEN-

CRTBLUE-

CRTDDC_DATA

CRTDDC_CLK

DREFCLKP

DREFCLKN

CRTREFSET

EXTTSRSVRD55

RSVRD56

RSTIN-

PWROK

ICH_SYNC-

NC30

W2

Y1

AA2

AB1

Y4

AA4

AB3

AC4

AC12

AC11

39R R383

D17

C17

F17

K17

H18

G17

J17

J18

N18

N20

J15

H15

A20

J20

M11

V30

AJ12

AJ9

M18

A42

R421

255R_1%

T49

T45

R385

24R9_1%

R386

10K

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

R38439R

VGA_RED

VGA_GREEN

VGA_BLUE

VGA_DDC_DA_3V

VGA_DDC_CLK_3V

CLK_96M_DOT

CLK_96M_DOT-

PRST_GMCH-H_TRDYPWR_GD

ICH_SYNC-

PCI_EXP_1.5V

VGA_HSYNC

VGA_VSYNC

V

5

.

2

C

C

V

16

16

16

16

16

16

16

16

14

14

14

19

15,19

15

14

14

6,19

6,19

18

18

C

7

D

E

VCC3

%

1

_

7

R

6

1

3

0

3

R

R64

62R

F

2

0

%

4

1

0

_

7

5

8

P

6

R

C

3

4

8

R

HXSWING

2345

%

1

_

9

R

6

4

3

2

R

1

R626

10R

3

%

0

4

6

1

0

6

_

0

R

M

2

0

4

C

1

2

R

5

8

1

X

C

CPU_GMCH_GTLREF

)

2

0

T

4

P

0

O

_

_

P

F

A

P

C

0

2

2

(

3,6

VGA_DDC_CLK_3V

6,19

VGA_DDC_DA_3V

6,19

1

2

8

8

3

3

K

K

3

3

R

R

9

8

2

2

K

K

6

6

0

0

1

1

R

R

61

R

USI

Universal Scientific Industrial Co.,Ltd.

TITLE:

GMCH(Host Bus,DMI,PCI_EXP Bus,VGA signals)

Document Number:

Prepared by:

A3

Jamaica

XXXXXXXX

I.J. Shen

Date:

2005/4/12

7

REV:

3.1

PAGE:SIZE:

OF

306

F

8

Page 7

VCC1.5V

6

L45

0R

PCI_EXP_1.5V

5

X

7

E

C

L44

1UH_300MA

LB2012T1R0M

L40

600R_200MA

L41

10UH_100MA

LB2012T100MR

L42

10UH_100MA

LB2012T100MR

L43

600R_200MA

REV:

730

OF

VCC1.5V

3.1

VCC1.5V

R423

3

0

6

0

2005/4/12

9

1

M

C

2

0

4

0

2

0

4

0

2

0

4

0

3

0

6

0

L5

FB_180R

0R51_1%

6

F

8

U

C

0

1

4

8

1

B

C

V

5

6

6

8

1

7

1

_

E

F

B

C

C

U

0

2

2

V

6

6

7

8

1

7

1

_

E

F

B

C

C

U

0

2

2

1

2

M

C

PAGE:SIZE:

VCCA_GPLL

5

8

6

5

7

1

0

4

7

2

2

2

5

5

U42

W21

VSSNCTF1

V29

VSSNCTF2

V26

VSSNCTF3

V24

VSSNCTF4

U29

VSSNCTF5

R29

VSSNCTF6

R26

VSSNCTF7

D43

VSSNCTF8

D1

VSSNCTF9

A40

VSSNCTF10

A4

VSSNCTF11

AE21

VSSNCTF12

AE23

VSSNCTF13

AE25

VSSNCTF14

AF18

VSSNCTF15

AF20

VSSNCTF16

AF22

VSSNCTF17

AF24

VSSNCTF18

W23

VSSNCTF19

W25

VSSNCTF20

Y20

VSSNCTF21

Y22

VSSNCTF22

Y24

VSSNCTF23

Y26

VSSNCTF24

Y29

VSSNCTF25

AA25

VSSNCTF26

AA27

VSSNCTF27

AA29

VSSNCTF28

AY1

VSSNCTF29

AC19

VSSNCTF30

AC25

VSSNCTF31

AC29

VSSNCTF32

AD18

VSSNCTF33

AD20

VSSNCTF34

AD22

VSSNCTF35

AD24

VSSNCTF36

AD27

VSSNCTF37

AD29

VSSNCTF38

AE19

VSSNCTF39

BC4

VSSNCTF40

AD4

VCC_EXP1

AD5

VCC_EXP2

AD6

VCC_EXP3

AD8

VCC_EXP4

AD10

VCC_EXP5

AD12

VCC_EXP6

N5

VCC_EXP7

N7

VCC_EXP8

N9

VCC_EXP9

N10

VCC_EXP10

N12

VCC_EXP11

R5

VCC_EXP12

R10

VCC_EXP13

AE2

VCC_EXP14

R11

VCC_EXP15

R13

VCC_EXP16

U6

VCC_EXP17

U7

VCC_EXP18

U8

VCC_EXP19

U13

VCC_EXP20

V5

VCC_EXP21

V6

VCC_EXP22

V7

VCC_EXP23

V9

VCC_EXP24

AE3

VCC_EXP25

V10

VCC_EXP26

V13

VCC_EXP27

Y13

VCC_EXP28

AA5

VCC_EXP29

AA13

VCC_EXP30

AC5

VCC_EXP31

AC6

VCC_EXP32

AC13

VCC_EXP33

AD1

VCC_EXP34

AD2

VCC_EXP35

AE4

VCC_EXP36

N11

VCC_EXP37

4

5

F

F

8

8

U

U

C

C

0

0

1

1

1

1

M

L

5

6

2

2

D

D

R

R

V

V

S

S

R

R

3

2

1

0

5

4

6

6

6

6

6

6

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

1

3

4

5

7

0

2

2

2

1

1

2

R

R

R

R

U

U

1

1

9

8

2

2

G

G

J

G

A

A

A

A

9

0

7

8

2

3

2

2

D

D

D

D

R

R

R

R

V

V

V

V

S

S

S

S

R

R

R

R

9

8

7

6

6

6

6

6

C

C

C

C

C

C

C

C

V

V

V

V

5

7

9

8

1

1

2

1

F

R

R

R

A

7

F

F

J

F

F

F

A

A

A

A

A

A

2

1

1

3

4

5

3

C

C

C

C

C

D

C

C

C

C

C

R

V

V

V

V

V

V

S

R

6

5

1

1

F

F

T

T

C

C

4

3

2

1

0

N

7

7

7

7

7

N

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

2

6

4

3

1

0

5

1

2

2

2

2

2

2

F

U

U

U

U

U

U

A

2

4

3

2

1

2

5

2

1

2

2

2

2

6

B

C

F

D

A

A

A

A

9

8

6

7

C

C

C

C

C

C

C

C

V

V

V

V

0

9

8

7

2

1

1

1

F

F

F

F

T

T

T

T

C

C

C

C

N

N

N

N

C

C

C

C

C

C

C

C

V

V

V

V

5

7

8

5

2

1

1

1

F

V

V

V

A

1

8

1

0

J

A

B

B

1

2

2

P

A

P

P

A

A

A

5

3

4

2

1

0

6

1

1

1

1

1

1

1

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

6

5

4

3

2

1

7

2

2

2

2

2

2

2

F

F

F

F

F

F

F

T

T

T

T

T

T

T

C

C

C

C

C

C

C

N

N

N

N

N

N

N

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

4

9

7

6

2

0

1

2

1

2

2

2

2

2

F

F

G

V

U

V

V

A

A

A

VCC1.5V

7

0

9

3

2

1

8

1

1

1

2

1

2

2

2

1

G

B

G

G

G

G

G

G

G

A

A

A

A

A

A

A

A

A

7

8

1

1

C

C

C

C

V

V

5

4

2

3

0

1

9

2

2

2

2

2

2

1

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

0

7

6

4

8

7

9

8

9

7

5

2

2

1

1

2

2

W

W

Y

Y

Y

Y

0

1

9

8

7

6

3

3

2

2

2

2

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

5

7

2

1

1

1

J

H

1

U

N

W

U

A

P

A

4

3

2

8

6

7

5

3

3

3

3

3

3

3

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

LAKEPORT_3

6

5

4

3

2

1

0

9

8

3

3

3

3

2

2

F

F

F

F

F

F

T

T

T

T

T

T

C

C

C

C

C

C

N

N

N

N

N

N

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

9

7

8

5

7

2

3

1

1

1

2

2

2

2

V

V

V

V

W

W

W

0

9

8

7

3

3

3

4

3

3

3

F

F

F

F

F

F

F

T

T

T

C

N

C

C

V

T

T

T

T

C

C

C

C

C

C

N

N

N

N

N

N

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

4

5

2

3

5

7

1

2

1

2

2

1

1

2

A

Y

Y

Y

Y

W

W

A

7

6

5

4

3

2

1

4

4

F

F

T

T

C

C

N

N

C

C

C

C

V

V

7

8

1

1

A

A

A

A

9

8

4

4

4

4

4

4

4

F

F

F

F

F

F

F

T

T

T

T

T

T

T

C

C

C

C

C

C

C

N

N

N

N

N

N

N

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

4

6

9

0

9

7

2

2

1

2

1

1

B

B

A

A

A

A

A

A

A

A

A

A

4

0

5

0

4

3

1

3

2

2

4

K

A

9

3

C

C

V

0

5

F

T

C

N

C

C

V

0

2

B

A

1

3

1

1

K

J

K

K

K

F

K

J

A

A

A

A

A

A

A

A

4

2

3

1

0

4

C

C

V

1

5

F

T

C

N

C

C

V

5

4

2

2

B

B

A

A

7

6

5

4

4

4

4

4

4

4

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

8

7

6

5

4

3

2

5

5

5

5

5

5

5

F

F

F

F

F

F

F

T

T

T

T

T

T

T

C

C

C

C

C

C

C

N

N

N

N

N

N

N

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

8

7

5

7

6

0

1

1

1

2

2

2

C

C

C

B

B

C

A

A

A

A

A

A

0

2

1

4

3

1

1

1

2

1

G

G

G

H

H

A

A

A

A

A

2

0

1

8

9

5

5

5

4

4

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

3

2

1

0

9

6

6

6

6

5

F

F

F

F

F

T

T

T

T

T

C

C

C

C

C

N

N

N

N

N

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

5

7

7

6

4

1

1

2

2

2

C

C

C

D

D

A

A

A

A

A

3

4

1

1

3

2

9

1

1

G

G

F

F

G

G

G

A

A

A

A

A

A

A

4

3

9

8

6

7

5

5

5

5

5

5

5

5

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V

V

V

V

V

V

V

8

7

6

5

4

6

F

T

C